Datasheet SN54LS365A, SN74LS365A, SN54LS366A, SN74LS366A, SN54LS367A Datasheet (MOTOROLA)

...

SN54/74LS365A

SN54/74LS366A

3-STATE HEX BUFFERS

These devices are high speed hex buffers with 3-state outputs. They are

organized as single 6-bit or 2-bit/4-bit, with inverting or non-inverting data (D)

paths. The outputs are designed to drive 15 TTL Unit Loads or 60 Low Power

Schottky loads when the Enable (E) is LOW.

When the Output Enable (E) is HIGH, the outputs are forced to a high

impedance “off” state. If the outputs of the 3-state devices are tied together,

all but one device must be in the high impedance state to avoid high currents

that would exceed the maximum ratings. Designers should ensure that Output

Enable signals to 3-state devices whose outputs are tied together are

designed so there is no overlap.

SN54/74LS367A

SN54/74LS368A

3-ST ATE HEX BUFFERS

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

16

1

16

1

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

D SUFFIX

16

1

SOIC

CASE 751B-03

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

T

I

I

CC

A

OH

OL

Supply Voltage 54

74

Operating Ambient Temperature Range 54

74

Output Current — High 54

74

Output Current — Low 54

74

4.5

4.75

–55

0

5.0

5.0

25

25

5.5

5.25

125

70

–1.0

–2.6

12

24

V

°C

mA

mA

FAST AND LS TTL DAT A

5-1

SN54/74LS365A • SN54/74LS366A

SN54/74LS367A • SN54/74LS368A

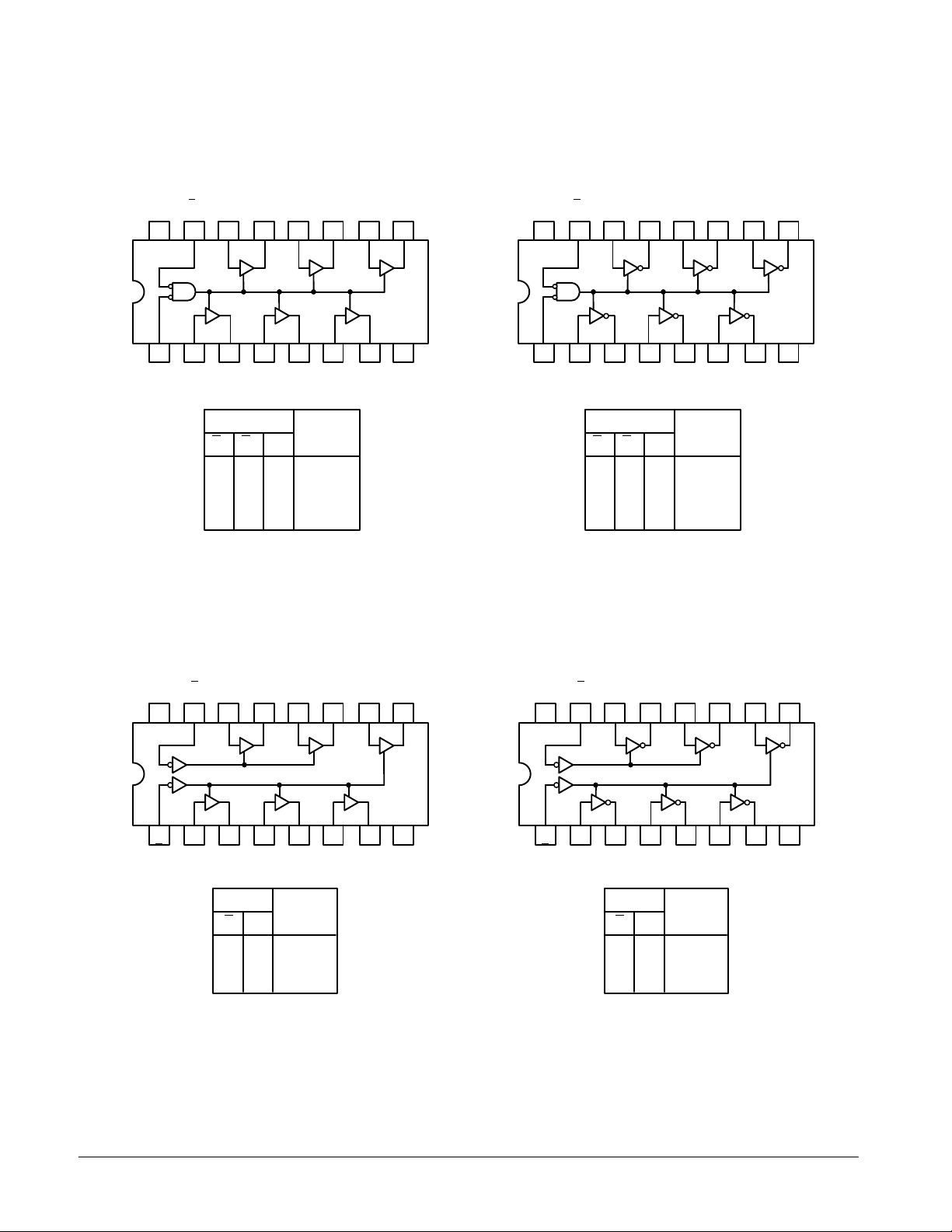

SN54/74LS365A

HEX 3-STATE BUFFER WITH

COMMON 2-INPUT NOR ENABLE

V

E

CC

2

16 15

123456

E

1

14 13 12 11 10 9

TRUTH TABLE

INPUTS

E1E2D

L

L

L

L

H

X

X

H

L

H

X

X

OUTPUT

L

H

(Z)

(Z)

7

GND

SN54/74LS366A

HEX 3-STATE INVERTER BUFFER

WITH COMMON 2-INPUT NOR ENABLE

V

E

CC

2

16 15

8

123456

E

1

14 13 12 11 10 9

7

GND

8

TRUTH TABLE

INPUTS

E1E2D

L

L

L

L

H

X

X

H

L

H

X

X

OUTPUT

H

L

(Z)

(Z)

SN54/74LS367A

HEX 3-STATE BUFFER

SEPARATE 2-BIT AND 4-BIT SECTIONS

E

V

CC

16 15

123456

E

14 13 12 11 10 9

7

GND

TRUTH TABLE

INPUTS

E D

L

L

H

L

H

X

OUTPUT

L

H

(Z)

SN54/74LS368A

HEX 3-STATE INVERTER BUFFER

SEPARATE 2-BIT AND 4-BIT SECTIONS

E

V

CC

16 15

8

123456

E

14 13 12 11 10 9

7

GND

8

TRUTH TABLE

INPUTS

E D

L

L

H

L

H

X

OUTPUT

H

L

(Z)

FAST AND LS TTL DATA

5-2

SN54/74LS365A • SN54/74LS366A

VILI

LOW Volt

V

pg

VOHOutput HIGH Volt

CC

,

OH

,

IN IH

VOLOutput LOW Volt

V

V

V

IIHI

HIGH C

t

CC

CC

L

p,

SN54/74LS367A • SN54/74LS368A

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol Parameter

V

IH

V

IK

I

OZH

I

OZL

I

IL

I

OS

I

CC

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

Input HIGH Voltage 2.0 V

nput

Input Clamp Diode Voltage –0.65 –1.5 V VCC = MIN, IIN = –18 mA

Output Off Current HIGH 20 µA VCC = MAX, V

Output Off Current LOW –20 µA VCC = MAX, V

nput

Input LOW Current

E

Inputs

D Inputs –20 µA

Short Circuit Current (Note 1) –40 –225 mA VCC = MAX

Power Supply Current

LS365A, 367A

LS366A, 368A 21

age

age

age

urren

54 0.7

74 0.8

54 2.4 3.4 V

74 2.4 3.1 V

54, 74 0.25 0.4 V IOL = 12 mA

74 0.35 0.5 V IOL = 24 mA

Min Typ Max

20 µA VCC = MAX, VIN = 2.7 V

0.1 mA VCC = MAX, VIN = 7.0 V

–0.4 mA VCC = MAX, VIN = 0.4 V

–0.4 mA

24

Unit Test Conditions

Guaranteed Input HIGH Voltage for

All Inputs

Guaranteed Input LOW Voltage for

All Inputs

VCC = MIN, IOH = MAX, VIN = V

or VIL per Truth Table

VCC = MAX, VIN = 0.5 V

Either E Input at 2.0 V

VCC = MAX, VIN = 0.4 V

Both E

Inputs at 0.4 V

mA VCC = MAX

VCC = VCC MIN,

=

IN

per Truth Table

= 2.7 V

OUT

= 0.4 V

OUT

IH

or

IL

IH

AC CHARACTERISTICS (T

= 25°C, VCC = 5.0 V)

A

Symbol Parameter

t

PLH

t

PHL

t

PZH

t

PZL

t

PHZ

t

PLZ

Propagation Delay

Output Enable Time

Output Disable Time

Limits

LS365A/LS367A LS366A/LS368A

Min Typ Max Min Typ Max

10

9.01622

192435

40

30

35

7.01215

182835

FAST AND LS TTL DATA

5-3

Unit Test Conditions

ns

18

ns

45

32

ns CL = 5.0 pF

35

CL = 45 pF,

RL = 667 Ω

Loading...

Loading...