NCP1232

Microprocessor Monitor

The NCP1232 is a fully–integrated processor supervisor. It provides

three important functions to safeguard processor functionality:

precision power on/off reset control, watchdog timer and external

reset override.

On power–up, the NCP1232 holds the processor in the reset state for

a minimum of 250 msec after VCC is within tolerance to ensure a

stable system start–up.

Microprocessor functionality is monitored by the on–board

watchdog circuit. The microprocessor must provide a periodic

low–going signal on the ST

this signal within the selected time–out period (150 msec, 600 msec or

1200 msec), an out–of–control processor is indicated and the

NCP1232 issues a processor reset as a result.

The outputs of the NCP1232 are immediately driven active when

the PB input is brought low by an external push–button switch or other

electronic signal. When connected to a push–button switch, the

NCP1232 provides contact debounce.

The NCP1232 is packaged in a space–saving 8–pin plastic SOIC

package and requires no external components.

input. Should the processor fail to supply

http://onsemi.com

SO–8

8

1

YY, Y = Year

WW = Work Week

X = Assembly ID Code

Z = Subcontractor ID Code

D SUFFIX

CASE 751

MARKING

DIAGRAM

8

NCP

1232

YWWXZ

1

Features

• Precision Voltage Monitor

(Adjustable +4.5 V or +4.75 V)

• Reset Pulse Width (250 msec Min)

• No External Components

• Adjustable Watchdog Timer

(150 msec, 600 msec or 1.2 sec)

• Debounced Manual Reset Input for External Override

Applications

• Computers

• Controllers

• Intelligent Instruments

• Automotive Systems

• Critical µP Power Monitoring

PIN CONNECTIONS

8–Pin SOIC

TD

TOL

1

2

3

4

(Top View)

PB RST

ORDERING INFORMATION

Device Package Shipping

NCP1232DR2 SO–8 2500 Tape & Reel

8

V

CC

7

ST

6

RST

NCP1232D

5

RSTGND

Semiconductor Components Industries, LLC, 2000

May, 2000 – Rev. 0

1 Publication Order Number:

NCP1232/D

NCP1232

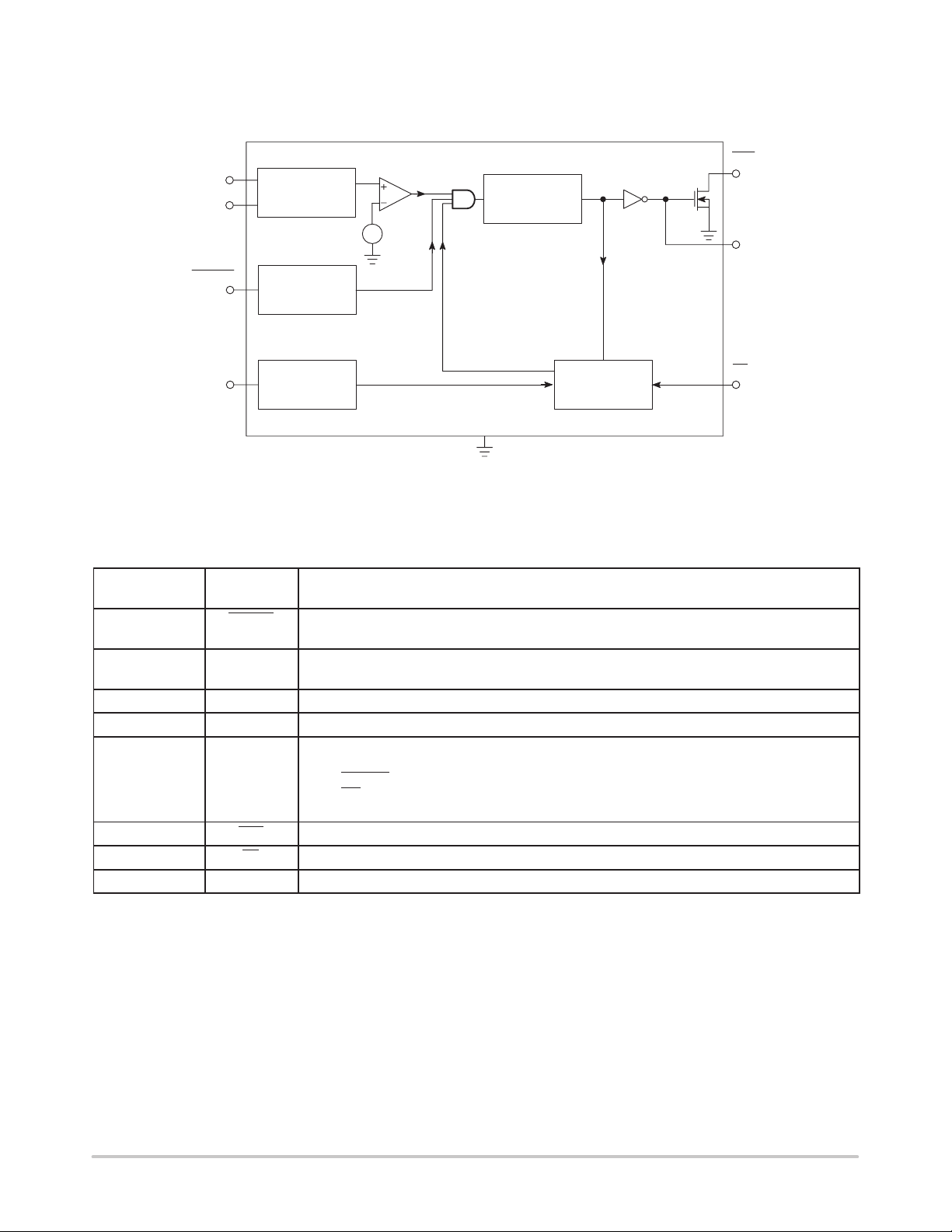

FUNCTIONAL BLOCK DIAGRAM

VD

CC

TOL

PB RST

TD

5%/10%

TOLERANCE

SELECT

DEBOUNCE

WATCHDOG

TIMEBASE

SELECT

REF

GND

RESET

GENERATOR

NCP1232

WATCHDOG

TIMER

RST

RST

ST

PIN DESCRIPTION

Pin No.

(8–Pin SOIC)

1 PB RST Push–button Reset Input. A debounced active–low input that ignores pulses less than 1 msec in

2 TD Time Delay Set. The watchdog time–out select input (tTD = 150 msec for

3 TOL Tolerance Input. Connect to GND for 5% tolerance or to VCC for 10% tolerance.

4 GND Ground.

5 RST Reset Output (Active High) – goes active:

6 RST Reset Output (Active Low, Open Drain) – see RST.

7 ST Strobe Input. Input for watchdog timer.

8 V

Symbol Description

duration and is guaranteed to recognize inputs of 20 msec or greater.

TD = 0 V, tTD = 600 msec for TD = open, tTD = 1.2 sec for TD = VCC.)

CC

1. If VCC falls below the selected reset voltage threshold

2. If PB RST

3. If ST

4. During power–up

The +5 V Power Supply Input.

is forced low

is not strobed within the minimum time–out period

http://onsemi.com

2

NCP1232

ABSOLUTE MAXIMUM RATINGS* Voltage on any pin (with respect to GND) –0.3 V to +5.8 V

Rating

Operating Temperature Range –40 to +85 °C

Storage Temperature Range, T

Lead Temperature (Soldering, 10 sec) +300 °C

*Stresses beyond those listed under “Absolute Maximum Ratings’’ may cause permanent damage to the device. These are stress ratings only ,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications

is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability .

stg

Value Unit

–65 to +150

°C

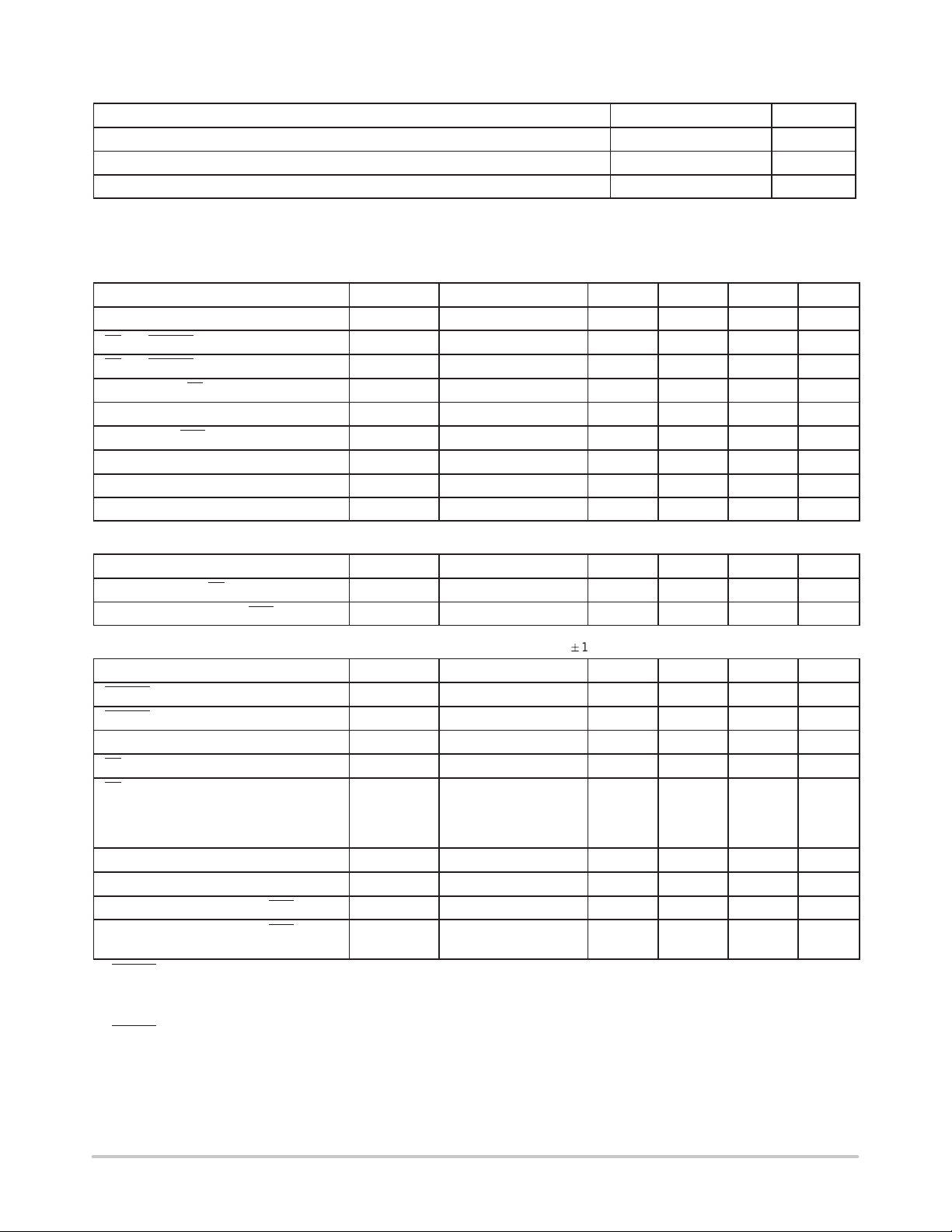

DC ELECTRICAL CHARACTERISTICS (T

Characteristic

Supply Voltage V

ST and PB RST Input High Level V

ST and PB RST Input Low Level V

Input Leakage ST, TOL I

Output Current RST I

Current RST, RST I

Operating Current I

VCC 5% Trip Point (Note 3.) V

VCC 10% Trip Point (Note 3.) V

CAPACITANCE (Note 4.) (T

Characteristic

Input Capacitance ST, TOL C

Output Capacitance RST, RST C

= +25°C)

A

AC ELECTRICAL CHARACTERISTICS (T

Characteristic

PB RST (Note 5.) t

PB RST Delay t

Reset Active Time t

ST Pulse Width t

ST Time–out Period t

VCC Fall Time (Note 4.) t

VCC Rise Time (Note 4.) t

VCC Detect to RST High and RST Low t

VCC Detect to RST High and RST Open

(Note 6.)

1. PB RST is internally pulled up to VCC with an internal impedance of typically 40 kΩ.

2. Measured with outputs open.

3. All voltages references to GND.

4. Guaranteed by design.

5. PB RST

6. tR = 5 µsec.

must be held low for a minimum of 20 msec to guarantee a reset.

= T

A

A

to T

MIN

Symbol Test Conditions Min Typ Max Unit

CC

IH

IL

L

OH

OL

CC

CCTP

CCTP

Symbol Test Conditions Min Typ Max Unit

IN

OUT

= T

to T

MIN

Symbol Test Conditions Min Typ Max Unit

PB

PBD

RST

ST

TD

F

R

RPD

t

RPU

; VCC = +4.5 V to 5.5 V, unless otherwise specified.)

MAX

– 4.5 5.0 5.5 V

Note 1. 2.0 – VCC +0.3 V

– –0.3 – +0.8 V

– –1.0 – +1.0 µA

VOH = 2.4 V –1.0 –12 – mA

VOL = 0.4 V 2.0 10 – mA

Note 2. – 50 200 µA

TOL = GND 4.50 4.62 4.74 V

TOL = V

; VCC = +5.0 V to "10%, unless otherwise specified.)

MAX

TD Pin = 0 V

TD Pin = Open

TD Pin = V

Figure 7, VCC Falling – – 100 nsec

Figure 8, VCC Rising 250 610 1000 msec

CC

– – – 5.0 pF

– – – 7.0 pF

Figure 3 20 – – msec

Figure 3 1.0 4.0 20 msec

– 250 610 1000 msec

Figure 4 20 – – nsec

Figure 4

CC

Figure 5 10 – – µsec

Figure 6 0 – – µsec

4.25 4.37 4.49 V

62.5

250

500

150

600

1200

250

1000

2000

msec

http://onsemi.com

3

Loading...

Loading...