Page 1

MVME1X7P Single-Board Computer

Programmer’s Reference

Guide

V1X7PA/PG1

Edition of October 2000

Page 2

© Copyright 2000 Motorola, Inc.

All rights reserved.

Printed in the United States of America.

®

Motorola

and the Motorola logo are registered t r ademarks of Motorola, Inc.

MC68040™ and MC68060™ are trademarks of Motorola, Inc.

All other products ment io ned i n this document are trade marks or registered trade marks of

their respective holders.

Page 3

Safety Summary

The following general safety precautions must be observed during all phases of operation, service, and repair of this

equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result

in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user

of the product, shoul d foll ow these warni ngs and al l other sa fety pr ecauti ons nece ssary fo r the safe ope ration of the

equipment in your operating environment.

Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the

equipment is su pplied wi th a three-c onductor A C power ca ble, the po wer cable m ust be plug ged into an a pproved

three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground

(safety ground) at the power outlet. The power jack and mating plug of the power cable meet International

Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes.

Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other

qualified service personnel may remove equipment covers for internal subassembly or component replacement or any

internal adjust ment. Service pe rsonnel should n ot replace compon ents with power c able connected. Under certain

conditions, dangero us voltages may exist even with the power cable remo ved. T o avoid inju ries, such pers onnel should

always disconnect power and discharge circuits before touching components.

Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent

CRT implosion, do not handl e the CRT and avoid rough handling o r jarring of t he equipment . Handling o f a CRT

should be done only by qualified service personnel using approved safety mask and gloves.

Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local

Motorola representative for service and repair to ensure that all safety features are maintained.

Observe Warnings in Manual.

W arn ings , such as th e exa mple be low, prece de po tent ially danger ous p roce dures th roug hout th is manu al . Instr uction s

contained in the warnings m ust be follow ed. You should also employ all ot her safety precautions w hich you dee m

necessary for the operation of the equi pment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme

caution when handling, testing, and adjusting this equipment and its

Warning

components.

Page 4

Flammability

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating

of 94V-0 by UL-recognized manufacturers.

EMI Caution

This equipment ge ner ates, uses a nd can radi ate el ectro magne tic energy . It

!

Caution

This product contains a lithium battery to power the clock and calendar circuitry.

!

Caution

may cause or be susceptible to electromagnetic interference (EMI) if not

installed and used with adequate EMI protection.

Lithium Battery Caution

Danger of explosion if battery is re placed incorrect ly. Replace battery only

with the same or equivalent type recommended by the equipment

manufacturer. Dispose of used batteries according to the manufacturer’s

instructions.

!

Attention

!

Vorsicht

Il y a danger d’explosion s’il y a remplacement incorrect de la batterie.

Remplacer uniquement avec une batterie du même type ou d’un type

équivalent recommandé par le constructeur. Mettre au rebut les batteries

usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur

durch denselben ode r einen vom Herstel ler empfohle nen Typ. Entsorgu ng

gebrauchter Batterien nach Angaben des Herstellers.

Page 5

CE Notice (European Community)

Motorola Compute r Group pro ducts wi th the CE mar king co mply with the EMC Dir ective

(89/336/EEC). Compliance with this directive implies conformity to the following

European Norms:

EN55022 “Limits and Methods of Meas urement of Radio Int erferen ce Chara cteri stic s

of Information Technology Equipment”; this product tested to Equipment Class B

EN50082-1:1997 “Electromag netic Compatibi lit y—Gener ic Im munity St andard , Part

1. Residential, Commercial and Light Industry”

System products al so fulf ill EN60950 ( product saf ety) which i s essenti ally the r equirement

for the Low Voltage Directive (73/23/EEC).

Board products are tested in a representative system to show compliance with the above

mentioned requirements. A proper installation in a CE-marked system will maintain the

required EMC /safety performance.

In accordance with European Community directives, a “Declaration of Conformity” has

been made and is on file within the European Union. The “Declaration of Conformity” is

available on request. Please contact your sales representative.

Notice

While reasonable efforts have been made to assure the accuracy of this document,

Motorola, Inc. a ssumes n o lia bility r esulti ng from any omissio ns in this docu ment, or from

the use of the information obtained therein. Motorola reserves the right to revise this

document and to ma ke c hanges from time to time in the conten t he reof without obliga ti on

of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or

referenced in another document as a URL to the Motorola Computer Group website. The

text itself may not b e published commerci ally in print o r electronic for m, edited, transla ted,

or otherwise altered without the permission of Motorola, Inc.

It is possible th at t hi s publication may contain reference to or infor m at ion about Motorola

products (machines and pr ograms), progra mming, or services that are not av ailable in your

country. Such references or information must not be construed to mean that Motorola

intends to announce such Motorola products, programming, or services in your country.

Page 6

Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S.

Government, the following notice shall apply unless otherwise agreed to in writing by

Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in

subparagraph (b)(3) of t he Rig hts i n Technical Data clause a t DFARS 252.227-7013 (Nov.

1995) and of the Rights in Noncommerc ial Computer Software and Docume ntation c lause

at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc.

Computer Group

2900 South Diablo Way

Tempe, Arizona 85282

Page 7

Contents

About This Manual

Overview of Contents...............................................................................................xxii

Comments and Suggestions......................................................................................xxii

Conventions Used in This Manual...........................................................................xxiii

CHAPTER 1 Programming Issues

Introduction................................................................................................................1-1

The Petra ASIC and Second-Generation MVME1X7 Boards............................1-1

Features...............................................................................................................1-3

Applicable Industry Standards............................................................................1-4

Block Diagram....................................................................................................1-4

Programming Interfaces.............................................................................................1-7

MC680X0 MPU..................................................................................................1-7

Data Bus Structure..............................................................................................1-7

EEPROMs on the MVME1X7P.........................................................................1-8

MVME167...................................................................................................1-8

MVME177...................................................................................................1-9

Flash Memory on the MVME177.......................................................................1-9

SRAM...............................................................................................................1-10

Onboard SDRAM.............................................................................................1-11

Battery-Backed-Up RAM and Clock................................................................1-12

VMEbus Interface............................................................. ................................1-12

I/O Interfaces ....................................................................................................1-12

Serial Port Interface...................................................................................1-13

Parallel (Printer) Interface.........................................................................1-14

Ethernet Interface ......................................................................................1-15

SCSI Interface............................................................................................1-16

Local Resources................................................................................................1-16

Programmable Tick Timers.......................................................................1-16

Watchdog Timer........................................................................................1-17

Software-Programmable Hardware Interrupts...........................................1-17

Local Bus Timeout ....................................................................................1-17

vii

Page 8

Functional Description ............................................................................................ 1-17

VMEbus Interface and VMEchip2...................................................................1-18

VMEchip2 General-Purpose I/O...............................................................1-18

Petra/VMEchip2 Redundant Logic...........................................................1-18

Memory Maps....................................... ...................................................................1-20

Local Bus Memory Map...................................................................................1-20

Normal Address Range.............................................................................1-20

Detailed I/O Memory Maps...................................................................... 1-25

BBRAM/TOD Clock Memory Map .........................................................1-41

Interrupt Acknowledge Map.....................................................................1-46

VMEbus Memory Map .................................. ..... ...... .......................................1-46

VMEbus Accesses to the Local Bus.........................................................1-46

VMEbus Short I/O Memory Map.............................................................1-46

Interrupt Handling ...................................................................................................1-47

Example: VMEchip2 Tick Timer 1 Periodic Interrupt.....................................1-47

Cache Coherency (MVME167P).............................................................................1-49

Cache Coherency (MVME177P).............................................................................1-50

Using Bus Timers....................................................................................................1-51

Indivisible Cycles....................................................................................................1-52

Supervisor Stack Pointer (MC68060)......................................................................1-53

Sources of Local Bus Errors....................................................................................1-54

Local Bus Timeout...........................................................................................1-54

VMEbus Access Timeout..................................................... ...... ...... ..... ........... 1-54

VMEbus BERR*........................... ..... ...... ........................................................1-54

VMEchip2 ....................................................................... ..... ...... ...... ................1-55

Bus Error Processing........................................................................................ 1-55

Error Conditions........................ ..... ...... ..... ..............................................................1-55

MPU Parity Error .............................................................................................1-56

MPU Offboard Error........................................................................................1-56

MPU TEA - Cause Unidentified......................................................................1-56

MPU Local Bus Time-out................................................................................1-57

DMAC VMEbus Error....................... ...... ...... ..... .............................................1-57

DMAC Parity Error......................................................... ..... ...... ...... ..... ........... 1-57

DMAC Offboard Error................................... ..... ...... ...... .................................1-58

DMAC LTO Error ........................................................... .................................1-58

DMAC TEA - Cause Unidentified...................................................................1-59

SCC Retry Error...............................................................................................1-59

SCC Parity Error ..............................................................................................1-60

SCC Offboard Error.........................................................................................1-60

SCC LTO Error.................................................................................................1-61

LAN Parity Error..............................................................................................1-61

viii

Page 9

LAN Offboard Error.........................................................................................1-61

LAN LTO Error ................................................................................................1-62

SCSI Parity Error..............................................................................................1-62

SCSI Offboard Error.........................................................................................1-62

SCSI LTO Error ................................................................................................1-63

CHAPTER 2 VMEchip2

Introduction................................................................................................................2-1

Functional Blocks ......................................................................................................2-4

Local-Bus-to-VMEbus Interface........................................................................2-4

Local-Bus-to-VMEbus Requester...............................................................2-7

VMEbus-to-Local-Bus Interface........................................................................2-9

Local-Bus-to-VMEbus DMA Controller..........................................................2-10

No-Address-Increment DMA Transfers.......................... ...... ..... ...............2-12

DMAC VMEbus Requester............................ ...... .....................................2-13

Tick and Watchdog Timers........................................................... ..... ...............2-14

Prescaler................................................................ ..... ...... ..........................2-14

Tick Timers................................................................................................2-15

Watchdog Timer........................................................................................2-15

VMEbus Interrupter........................ ...... ...... ......................................................2-16

VMEbus System Controller.................................................... ..........................2-17

Arbiter.............................................................................. ...... ..... ...............2-17

IACK Daisy-Chain Driver.........................................................................2-17

Bus Timer..................................................................................................2-17

Reset Driver...............................................................................................2-18

Local Bus Interrupter and Interrupt Handler....................................................2-18

Global Control and Status Registers.................................................................2-20

LCSR Programming Model.....................................................................................2-20

Programming the VMEbus Slave Map Decoders.............................................2-26

VMEbus Slave Ending Address Register 1 ..............................................2-28

VMEbus Slave Starting Address Register 1 .............................................2-28

VMEbus Slave Ending Address Register 2 ..............................................2-29

VMEbus Slave Starting Address Register 2 .............................................2-29

VMEbus Slave Address Translation Address Offset Register 1 .............. 2-29

VMEbus Slave Address Translation Select Register 1 ............................2-30

VMEbus Slave Address Translation Address Offset Register 2...............2-31

VMEbus Slave Address Translation Select Register 2 ............................2-31

VMEbus Slave Write Post and Snoop Control Register 2 ........................2-32

VMEbus Slave Address Modifier Select Register 2.................................2-33

VMEbus Slave Write Post and Snoop Control Register 1 ........................2-35

ix

Page 10

VMEbus Slave Address Modifier Select Register 1.................................2-36

Programming the Local-Bus-to-VMEbus Map Decoders................................2-37

Local Bus Slave (VMEbus Master) Ending Address Register 1 ..............2-39

Local Bus Slave (VMEbus Master) Starting Address Register 1.............2-40

Local Bus Slave (VMEbus Master) Ending Address Register 2 ..............2-40

Local Bus Slave (VMEbus Master) Starting Address Register 2.............2-40

Local Bus Slave (VMEbus Master) Ending Address Register 3 .............2-41

Local Bus Slave (VMEbus Master) Starting Address Register 3 ............2-41

Local Bus Slave (VMEbus Master) Ending Address Register 4 .............2-41

Local Bus Slave (VMEbus Master) Starting Address Register 4 ............2-42

Local Bus Slave (VMEbus Master)

Address Translation Address Register 4 .......................................... 2-42

Local Bus Slave (VMEbus Master)

Address Translation Select Register 4 .............................................2-42

Local Bus Slave (VMEbus Master) Attribute Register 4 .........................2-43

Local Bus Slave (VMEbus Master) Attribute Register 3 .........................2-44

Local Bus Slave (VMEbus Master) Attribute Register 2 .........................2-45

Local Bus Slave (VMEbus Master) Attribute Register 1 .........................2-46

VMEbus Slave GCSR Group Address Register ......................................2-47

VMEbus Slave GCSR Board Address Register .......................................2-48

Local-Bus-to-VMEbus Enable Control Register .....................................2-49

Local-Bus-to-VMEbus I/O Control Register ...........................................2-50

ROM Control Register ................................ .................................. ...... .....2-51

Programming the VMEchip2 DMA Controller................................................2-51

DMAC Registers........................... ...................................................................2-53

EPROM Decoder, SRAM and DMA Control Register ...........................2-53

Local-Bus-to-VMEbus Requester Control Register ................................2-54

DMAC Control Register 1 (bits 0-7) .......................................................2-55

DMAC Control Register 2 (bits 8-15) .....................................................2-57

DMAC Control Register 2 (bits 0-7) .......................................................2-58

DMAC Local Bus Address Counter ............................. ............................2-59

DMAC VMEbus Address Counter ..........................................................2-60

DMAC Byte Counter ......................................................... ...... ..... ...........2-60

Table Address Counter .............................................................................2-60

VMEbus Interrupter Control Register ................................................. .....2-61

VMEbus Interrupter Vector Register .......................................................2-62

MPU Status and DMA Interrupt Count Register .....................................2-62

DMAC Status Register ............................................................. ................2-63

Programming the Tick and Watchdog Timers..................................................2-64

VMEbus Arbiter Time-Out Control Register ..........................................2-64

DMAC Ton/Toff Timers and VMEbus

Global Time-out Control Register.....................................................2-65

x

Page 11

VME Access, Local Bus, and Watchdog Time-out Control Register ......2-66

Prescaler Control Register ........................................................................2-67

Tick Timer 1 Compare Register ...............................................................2-68

Tick Timer 1 Counter ...............................................................................2-68

Tick Timer 2 Compare Register ...............................................................2-69

Tick Timer 2 Counter ...............................................................................2-69

Board Control Register .............................................................................2-70

Watchdog Timer Control Register ...........................................................2-71

Tick Timer 2 Control Register ..................................................................2-72

Tick Timer 1 Control Register ..................................................................2-73

Prescaler Counter ......................................................................................2-73

Programming the Local Bus Interrupter...........................................................2-74

Local Bus Interrupter Status Register (bits 24-31) ...................................2-77

Local Bus Interrupter Status Register (bits 16-23) ...................................2-78

Local Bus Interrupter Status Register (bits 8-15) .....................................2-79

Local Bus Interrupter Status Register (bits 0-7) .......................................2-80

Local Bus Interrupter Enable Register (bits 24-31) ..................................2-81

Local Bus Interrupter Enable Register (bits 16-23) ..................................2-82

Local Bus Interrupter Enable Register (bits 8-15) ....................................2-83

Local Bus Interrupter Enable Register (bits 0-7) ......................................2-84

Software Interrupt Set Register (bits 8-15) ...............................................2-85

Interrupt Clear Register (bits 24-31) ........................................................2-85

Interrupt Clear Register (bits 16-23) ........................................................2-86

Interrupt Clear Register (bits 8-15) ..........................................................2-87

Interrupt Level Register 1 (bits 24-31) .....................................................2-87

Interrupt Level Register 1 (bits 16-23) .....................................................2-88

Interrupt Level Register 1 (bits 8-15) .......................................................2-88

Interrupt Level Register 1 (bits 0-7) .........................................................2-89

Interrupt Level Register 2 (bits 24-31) .....................................................2-89

Interrupt Level Register 2 (bits 16-23) .....................................................2-90

Interrupt Level Register 2 (bits 8-15) .......................................................2-90

Interrupt Level Register 2 (bits 0-7) .........................................................2-91

Interrupt Level Register 3 (bits 24-31) .....................................................2-91

Interrupt Level Register 3 (bits 16-23) .....................................................2-92

Interrupt Level Register 3 (bits 8-15) .......................................................2-92

Interrupt Level Register 3 (bits 0-7) .........................................................2-93

Interrupt Level Register 4 (bits 24-31) .....................................................2-93

Interrupt Level Register 4 (bits 16-23) .....................................................2-94

Interrupt Level Register 4 (bits 8-15) .......................................................2-94

Interrupt Level Register 4 (bits 0-7) .........................................................2-95

Vector Base Register ................................................................................2-95

I/O Control Register 1 ..............................................................................2-96

xi

Page 12

I/O Control Register 2 ..............................................................................2-97

I/O Control Register 3 ..............................................................................2-97

Miscellaneous Control Register ...............................................................2-98

GCSR Programming Model..................................................................................2-100

Programming the GCSR.................................................................................2-102

VMEchip2 Revision Register ................................................................2-103

VMEchip2 ID Register ...........................................................................2-104

VMEchip2 LM/SIG Register .................................................................2-104

VMEchip2 Board Status/Control Register .............................................2-106

General Purpose Register 0 ....................................................................2-107

General Purpose Register 1 ....................................................................2-107

General Purpose Register 2 ....................................................................2-107

General Purpose Register 3 ....................................................................2-108

General Purpose Register 4 ....................................................................2-108

General Purpose Register 5 ....................................................................2-108

CHAPTER 3 PCCchip2

Introduction ...............................................................................................................3-1

Summary of Major Features...............................................................................3-1

Functional Description .............................................................................................. 3-2

General Description............................................................................................3-2

BBRAM Interface ............................................... ...... ...... ...................................3-3

82596CA LAN Controller Interface...................................................................3-3

MPU Port and MPU Channel Attention......................................................3-3

MC68040-Bus Master Support for 82596CA.............................................3-4

LANC Bus Error .......................................... .................................. ...... ...... .3-4

LANC Interrupt....................................... ..... ...............................................3-5

53C710 SCSI Controller Interface.................................. .................................. .3-6

Parallel Port Interface.........................................................................................3-6

General Purpose I/O Pin.....................................................................................3-7

CD2401 SCC Interface.......................................................................................3-7

Tick Timer............................... ...... ..... ................................................................3-9

Overall Memory Map........................... ..... ...... .................................. ...... ..... ...........3-10

Programming Model................................................................................................3-11

Chip ID Register...............................................................................................3-14

Chip Revision Register.....................................................................................3-14

General Control Register..................................................................................3-15

Vector Base Register ........................................................................................3-16

xii

Page 13

Programming the Tick Timers..........................................................................3-18

Tick Timer 1 Compare Register................................................................3-18

Tick Timer 1 Counter................................................................................3-19

Tick Timer 2 Compare Register................................................................3-19

Tick Timer 2 Counter................................................................................3-20

Prescaler Count Register ...........................................................................3-20

Prescaler Clock Adjust Register................................................................3-20

Tick Timer 2 Control Register...................................................................3-22

Tick Timer 1 Control Register...................................................................3-23

General Purpose Input Interrupt Control Register.....................................3-24

General Purpose Input/Output Pin Control Register.................................3-25

Tick Timer 2 Interrupt Control Register....................................................3-25

Tick Timer 1 Interrupt Control Register....................................................3-26

SCC Error Status and Interrupt Control Registers............................................3-27

SCC Error Status Register.........................................................................3-27

SCC Modem Interrupt Control Register....................................................3-28

SCC Transmit Interrupt Control Register..................................................3-29

SCC Receive Interrupt Control Register...................................................3-30

Modem PIACK Register ...........................................................................3-31

Transmit PIACK Register .......................................................... ...............3-32

Receive PIACK Register...........................................................................3-33

LANC Error Status and Interrupt Control Registers ........................................3-34

LANC Error Status Register........................... ...... ..... ...... ..........................3-34

82596CA LANC Interrupt Control Register.............................................3-35

LANC Bus Error Interrupt Control Register.............................................3-36

Programming the SCSI Error Status and Interrupt Registers...........................3-37

SCSI Error Status Register........................................................................3-37

SCSI Interrupt Control Register................................................................3-38

Programming the Printer Port...........................................................................3-39

Printer ACK Interrupt Control Register....................................................3-39

Printer FAULT Interrupt Control Register................................................3-40

Printer SEL Interrupt Control Register......................................................3-41

Printer PE Interrupt Control Register........................................................3-42

Printer BUSY Interrupt Control Register..................................................3-43

Printer Input Status Register......................................................................3-44

Printer Port Control Register.....................................................................3-45

Chip Speed Register..................................................................................3-46

Printer Data Register ............................................................. ..... ...... ...... ...3-47

Interrupt Priority Level Register................................................................3-48

Interrupt Mask Level Register...................................................................3-49

xiii

Page 14

CHAPTER 4 MCECC Functions

Introduction ...............................................................................................................4-1

Features......................................................................................................................4-2

Functional Description .............................................................................................. 4-3

General Description............................................................................................4-3

Performance........................................................................................................4-3

Cache Coherency................................................................................................4-4

ECC....................................................................................................................4-5

Cycle Types.................................................................................................4-5

Error Reporting .................................................. .........................................4-5

Single Bit Error (Cycle Type = Burst Read or Non-Burst Read) ...............4-5

Double Bit Error (Cycle Type = Burst Read or Non-Burst Read) .............. 4-6

Triple (or Greater) Bit Error

(Cycle Type = Burst Read or Non-Burst Read)..................................4-6

Cycle Type = Burst Write...........................................................................4-6

Single Bit Error (Cycle Type = Non-Burst Write)......................................4-6

Double Bit Error (Cycle Type = Non-Burst Write)....................................4-6

Triple (or Greater) Bit Error (Cycle Type = Non-Burst Write)..................4-7

Single Bit Error (Cycle Type = Scrub) .......................................................4-7

Double Bit Error (Cycle Type = Scrub)......................................................4-7

Triple (or Greater) Bit Error (Cycle Type = Scrub).................................... 4-7

Error Logging................................................. .................................. ..... ...... ....... 4-8

Scrub...................................................................................................................4-8

Refresh..................................... ...... .................................. ..... ...... ........................4-8

Arbitration..................................... ..... ................................................................4-9

Chip Defaults......................................................................................................4-9

Programming Model................................................................................................4-10

Chip ID Register...............................................................................................4-13

Chip Revision Register.....................................................................................4-13

Memory Configuration Register ......................................................................4-14

Base Address Register......................................................................................4-15

DRAM Control Register ..................................................................................4-15

BCLK Frequency Register...............................................................................4-16

Data Control Register.......................................................................................4-17

Scrub Control Register.....................................................................................4-19

Scrub Period Register Bits 15-8.......................................................................4-20

Scrub Period Register Bits 7-0.........................................................................4-20

Chip Prescaler Counter.....................................................................................4-21

Scrub Time On/Time Off Register ...................................................................4-21

Scrub Prescaler Counter (Bits 21-16)...............................................................4-23

Scrub Prescaler Counter (Bits 15-8).................................................................4-23

xiv

Page 15

Scrub Prescaler Counter (Bits 7-0)...................................................................4-24

Scrub Timer Counter (Bits 15-8)......................................................................4-24

Scrub Timer Counter (Bits 7-0)........................................................................4-25

Scrub Address Counter (Bits 26-24).................................................................4-25

Scrub Address Counter (Bits 23-16).................................................................4-26

Scrub Address Counter (Bits 15-8)...................................................................4-26

Scrub Address Counter (Bits 7-4).....................................................................4-26

Error Logger Register....................................................... ...... ...... ....................4-27

Error Address (Bits 31-24)...............................................................................4-28

Error Address (Bits 23-16)...............................................................................4-28

Error Address (Bits 15-8).................................................................................4-29

Error Address (Bits 7-4)...................................................................................4-29

Error Syndrome Register............................ ......................................................4-30

Defaults Register 1............................................................................................4-30

Defaults Register 2............................................................................................4-32

SDRAM Configuration Register .....................................................................4-33

Initialization......................................................................................................4-34

Syndrome Decoding.................................................................................................4-36

APPENDIX A Summary of Changes

Introduction...............................................................................................................A-1

APPENDIX B Printer and Serial Port Connections

Introduction...............................................................................................................B-1

Connection Diagrams................................................................................................B-1

APPENDIX C Related Documentation

MCG Documents ......................................... .............................................................C-1

Manufacturers’ Documents.......................................................................................C-2

Related Specifications...............................................................................................C-3

xv

Page 16

xvi

Page 17

List of Figures

Figure 1-1. MVME167P Block Diagram...................................................................1-5

Figure 1-2. MVME177P Block Diagram...................................................................1-6

Figure 1-3. MVME177 Flash and EPROM Memory Mapping Schemes................1-10

Figure 2-1. VMEchip2 Block Diagram .....................................................................2-5

Figure 3-1. PCCchip2 Block Diagram.......................................................................3-2

Figure B-1. MVME1X7P Printer Port with MVME712M ......................................B-2

Figure B-2. MVME1X7P Serial Port 1 Configured as DCE ...................................B-3

Figure B-3. MVME1X7P Serial Port 2 Configured as DCE ...................................B-4

Figure B-4. MVME1X7P Serial Port 3 Configured as DCE ...................................B-5

Figure B-5. MVME1X7P Serial Port 4 Configured as DCE ...................................B-6

Figure B-6. MVME1X7P Serial Port 1 Configured as DTE ...................................B-7

Figure B-7. MVME1X7P Serial Port 2 Configured as DTE ...................................B-8

Figure B-8. MVME1X7P Serial Port 3 Configured as DTE ...................................B-9

Figure B-9. MVME1X7P Serial Port 4 Configured as DTE .................................B-10

xvii

Page 18

xviii

Page 19

List of T ables

Table 1-1. MVME1X7P Features Summary..............................................................1-3

T ab le 1-2. Functions Duplicated in VMEchip2 and Petra ASICs............................1-19

Table 1-3. Local Bus Memory Map.........................................................................1-21

Table 1-4. Local I/O Devices Memory Map............................................................1-22

Table 1-5. VMEchip2 Memory Map (Sheet 1 of 3).................................................1-26

Table 1-6. Printer Memory Map ..............................................................................1-31

T ab le 1-7. PCCchip2 Memory Map............................................... ...... ....................1-32

T ab le 1-8. MCECC Internal Register Memory Map............................................. ...1-34

Table 1-9. Cirrus Logic CD2401 Serial Port Memory Map ....................................1-36

T ab le 1-10. 82596CA Ethernet LAN Memory Map ................................................1-40

Table 1-11. 53C710 SCSI Memory Map..................................................................1-41

Table 1-12. M48T58 BBRAM,TOD Clock Memory Map......................................1-42

Table 1-13. BBRAM Configuration Area Memory Map.........................................1-42

Table 1-14. TOD Clock Memory Map.....................................................................1-43

T ab le 1-15. Single-Cycle Instructions.................................................. ..... ...............1-52

Table 2-1. Features of the VMEchip2 ASIC..............................................................2-1

Table 2-2. VMEchip2 Memory Map—LCSR Summary (Sheet 1 of 2)..................2-22

Table 2-3. DMAC Command Packet Format...........................................................2-53

Table 2-4. Local Bus Interrupter Summary.............................................................2-75

Table 2-5. VMEchip2 Memory Map (GCSR Summary).......................................2-103

T ab le 3-1. PCCchip2 Devices Memory Map................................. ..........................3-10

Table 3-2. PCCchip2 Memory Map - Control and Status Registers........................3-12

Table 4-1. MCECC Functions on the Petra ASIC.....................................................4-2

Table 4-2. Memory System Cycle Timing.................................................................4-4

Table 4-3. MCECC Sector Internal Register Memory Map ....................................4-11

T ab le 4-4. Syndrome Bit Encoding..................................... ..... ...... ..........................4-36

Table 4-5. Identifying SDRAM Bank in Error........................................................4-37

Table A-1. List of Changes ......................................................................................A-1

Table C-1. Motorola Computer Group Documents .................................................C-1

Table C-2. Manufacturers’ Documents ....................................................................C-2

Table C-3. Related Specifications ............................................................................C-3

xix

Page 20

xx

Page 21

About This Manual

This manual provides board-level information and detailed ASIC

information, including register bit descriptions, for the MVME167PAxxSE and MVME177PA-xxSE series of VME single-board computers,

known collectively as the ‘‘MVME1X7P’’.

The “Petra” chip that distinguishes MVME167P and MVME177P single-

board computers is an application-specific integrated circuit (ASIC) used

on various Motorola VME boards which combines a va riety of functions

previously implemented in other ASICs (among them the MC2 chip, the

IP2 chip, and the MCECC chip) in a single ASIC. On the MVME1X7P,

the “Petra” chip repl aces the MCECC ASIC. As of the public ation date, the

information presented in this manual applies to the following

MVME1X7P models:

Model Number Characteristics

MVME167PA-24SE 25MHz MC68040, 16MB SDRAM, SCSI and Ethernet

MVME167PA-25SE 25MHz MC68040, 32MB SDRAM, SCSI and Ethernet

MVME167PA-34SE 33MHz MC68040, 16MB SDRAM, SCSI and Ethernet

MVME167PA-35SE 33MHz MC68040, 32MB SDRAM, SCSI and Ethernet

MVME167PA-36SE 33MHz MC68040, 64MB SDRAM, SCSI and Ethernet

MVME177PA-54SE 50MHz MC68060, 16MB SDRAM, SCSI and Ethernet

MVME177PA-55SE 50MHz MC68060, 32MB SDRAM, SCSI and Ethernet

MVME177PA-56SE 50MHz MC68060, 64MB SDRAM, SCSI and Ethernet

MVME177PA-64SE 60MHz MC68060, 16MB SDRAM, SCSI and Ethernet

MVME177PA-65SE 60MHz MC68060, 32MB SDRAM, SCSI and Ethernet

MVME177PA-66SE 60MHz MC68060, 64MB SDRAM, SCSI and Ethernet

MVME177PA-67SE 60MHz MC68060, 128MB SDRAM, SCSI and Ethernet

This manual is intended for anyone who designs OEM systems, adds

capability to an existing compatible system, or works in a lab environment

for experimental purposes. A basic knowledge of computers and digital

logic is assumed. To use this manual, you may also wish to become

familiar with the publications listed in Appendix C, Related

Documentation.

xxi

Page 22

Overview of Contents

Chapter 1, Programming Issues, describes the board-level hardware

features of MVME1X7P single-board computers. It includes memory

maps and a discussion of some general software considerations such as

cache coherency, interrupts, and bus errors.

Chapter 2, VMEchip2, describes the VMEchip2 ASIC, the local

bus/VMEbus interface chip on MVME1X7P boards.

Chapter 3, PCCchip2, describes the PCCchip2 ASIC. The PCChip2 is a

peripheral channel controller designed to interface an MC680x0compatible local bus to va rious on -board periph eral de vices s uch as SCSI

and LAN controllers.

Chapter 4, MCECC Functions, desc ribes the ECC DRAM controlle r ASIC

(MCECC). On the MVME1X7P boa rds, i t sup plies th e interf ace t o a 144 bit wide DRAM memory system.

Appendix A, Summary of Changes, lists the modifications that

accompanied the introduction of the Petra ASIC on the MVME167P and

MVME177P.

Appendix B, Printer and Serial Port Connections, contains drawings of

the printer and serial port interface connections available with the

MVME167P/MVME177P and MVME712 series transition board.

Appendix C, Related Documenta tion, lists all documentation related to the

MVME167P and MVME177P.

Comments and Suggestions

Motorola welcomes and appreciates your comments on its doc umentation.

We want to know what y ou think about our manuals and how we can make

them better. Mail comments to:

Motorola Computer Group

Reader Comments DW164

2900 S. Diablo Way

Tempe, Arizona 85282

xxii

Page 23

You can also submit comments to the following e-mail address:

reader-comments@mcg.mot.com

In all your corres pondence , plea se li st your name, po siti on, and c ompan y.

Be sure to include the title and par t number of the manual and tell how you

used it. Then tell us your feelings about its strengths and weaknesses and

any recommendations for improvements.

Conventions Used in This Manual

The following typographical conventions are used in this document:

$ dollar specifies a hexadecimal number

% percent specifies a binary number

& ampersand specifies a decimal number

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (*) following the signal name for signals which are level

significant denotes that the signal is true or valid when the signal is low.

An asterisk (*) following the signal name for signals which are edge

significant deno tes that the a ctions init iated by th at signal occu r on high to

low transitio n.

xxiii

Page 24

bold

is used for user inpu t that you t ype just as i t appears ; it is al so used for

commands, options and arguments to commands, and names of

programs, directories and files.

italic

is used for names of variables to which you assign values. Italic is also

used for comments in screen dis plays and examples, and to introduce

new terms.

courier

is used for system output (for example, screen displays, reports),

examples, and system prompts.

<Enter>, <Return> or <CR>

<CR> represents the carriage return or Enter key.

CTRL

represents the Control key. Execute control character s by pressing the

Ctrl key and the letter simultaneously, for example, Ctrl-d.

In this manual, assertion and negation are used to specify forcing a signal

to a particular stat e. In parti cular, a ssertion and asser t refe r to a signal tha t

is active or true; negation and negate indicate a signal that is inactive or

false. These terms ar e used independently of the vo ltage level (high or l ow)

that they represent.

xxiv

Data and address sizes are defined as follows:

❏ A byte i s eight bits, numb ered 0 through 7, wit h bit 0 being the leas t

significant.

❏ A word is 16 bits, numbered 0 th rough 15, wit h bit 0 bei ng the le ast

significant.

❏ A longword is 32 bi ts, numbered 0 through 31, with bit 0 being the

least significant.

Page 25

The terms control bit, status bit, true, and false are used ext ensively in this

document. The term control bit is used to describe a bit in a register that

can be set and cleared under software control. The term true is use d to

indicate that a bit is in the state that enables the function it controls. The

term false is used to indicate that the bit is in the state that disables the

function it controls. In all tables, the terms 0 and 1 are used to describe the

actual value that sh ould be written to the bit, or the value that it yields when

read. The term status bit is used to describe a bit in a regi ster that reflects

a specific condition. The status bit can be read by software to determine

operational or exception conditions.

xxv

Page 26

xxvi

Page 27

Introduction

The MVME167P and MVME177P single-board computers are complex

boards that interface both to the VMEbus and the SCSI bus. From a

programming standpoint, their multiple-bus interfaces raise issues of

cache coherency and support of indivisible cycles. There are also various

potential sources of bus error.

This chapter discusses those topics in addition to interrupt handling, the

use of bus timers, and the programming interface to each device on the

board. Programmable regist ers that reside in ASICs (Applicati on-Specific

Integrated Circuit s) on the MVME1X7P boards are covered in the chapters

devoted to those devices.

Note The MVME1X7P’s new ’‘Petra’’ ASIC performs the functions

1Programming Issues

1

previously implemented in the MCECC chip. For ease of use in

conjunction with programming models and documentation

developed for earlier boards, however, the structure of this

manual preserves the functional distinctions that formerly

characterized the MCECC ASIC.

The Petra ASIC and Second-Generation MVME1X7 Boards

Due to rapid changes in tec hnology, the productio n of certain ASI Cs used

on various Motorola first- and second-generation VME embedded

controllers and single-board computers has ended. The Petra chip was

developed to replace these discontinued ASICs. In the case of

MVME167/177 series boards, the di scontinue d ASIC is the MCECC chip.

The Petra chip now suppl ies the functi ons formerly implemented in the

MCECC chip.

1-1

Page 28

1

Programming Issues

The Petra ASIC is functionally compatible with each of the components

that it replaces. In cases where functionality between ASICs is exclusive,

configuration switches or jumpers are provided to let you select the

desired functionality.

In several areas of functionality, the configuration switches provide

backward compatibilit y with earl ier MVME167/17 7 implement ations, but

you can override their settings in software if you wish. A “R/W” by the

corresponding regi ster table entry in this manual denotes inst ances where

this override capability is present.

Where the older technology supported “fast page” or “EDO” DRAM

chips, the Petra memory controllers support SDRAM devices. The two

memory controllers modeled in Petra duplicate the functionality of the

“parity” memory control ler f ound i n the MC ASICs used o n cert ain ot her

boards as well as th at of the “single-bit error correcting/double-bit er ror

detecting” memory controller found in the MCECC ASICs used on the

MVME167/177.

This Programmer’s Reference Guide describes the MCECC model (in

Chapter 4). In the MVME167/177 application, there is logic on the Petra

chip to prevent you from in advertently enabling the MC memory controller

model.

The same SDRAM memory array serves both controller models. The

SDRAM array is 32 data bits wi de with 7 checkbits. Th e array architecture

is a non-interleaved single bank for sizes below 32MB. For array sizes

above 32MB, additional physical memory banks are added but the

architecture remains non-interleaved.

A final note on the SDRAM implementation: The bandwidth between the

SDRAM and local bus is greater than it was wit h the earlier DRAM array.

As a result, software takes less time to execute. Applicatio ns that

incorporate elapsed-time functions which are dependent on code

execution may have problems.

For readers who need to know the ASIC-specific differences between the

previous MCECC and Petra/MCECC programming models in detail,

certain areas of the text in this manual are printed in italics and marked

with change bars (as is done her e). Readers should compare those sections

to the corresp onding se ctions o f the first - and s econd-g eneration manuals.

1-2 Computer Group Literature Center Web Site

Page 29

Introduction

Features

The “Petra” ASIC supplants the MCECC memory controller ASIC on

MVME1X7P boards, performin g the memory control func tions previously

carried out by the MCECC chip: It supplies the programmable int erface for

the ECC-protected 16/32/64/128MB DRAM emulation.

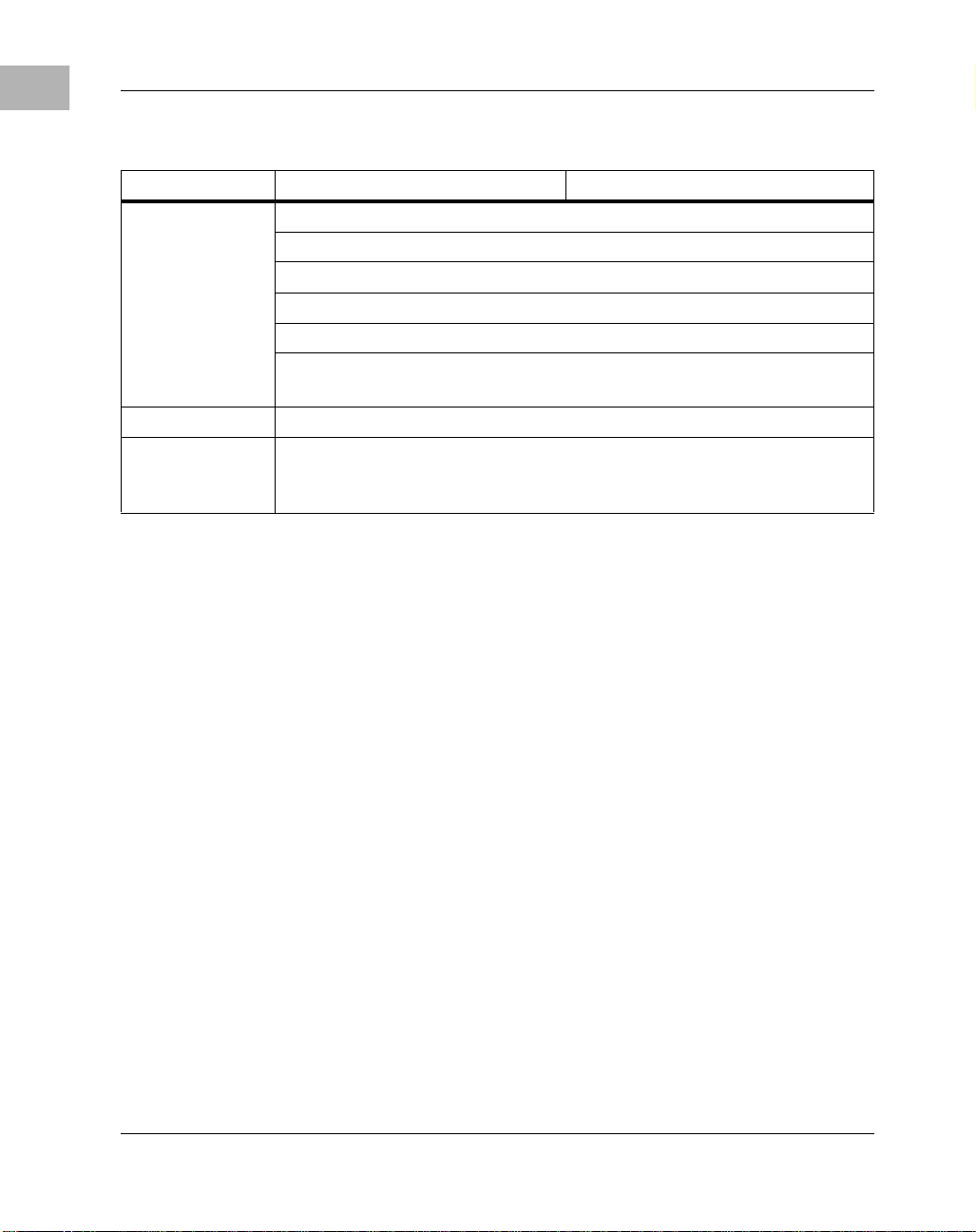

The following table summarizes the features of the MVME167P and

MVME177P single-board computers.

Table 1-1. MVME1X7P Features Summary

Feature MVME167P MVME177P

Processor 25/33MHz 32-bit MC68040

microprocessor

DRAM 16/32/64/128MB synchro nous DRAM (SDRAM). Configu rable to emulate

4/8/16/32/64/128MB ECC-protected DRAM

MVME1X7P boards use SDRAM (Synchr onous DRAM ) in place of DRAM.

Up to 64MB SDRAM is available on MVME167P boards; up to 128MB is

available on MVME177P boards.

SRAM 128KB SRAM with battery backup

EPROM Four 44-pin JEDEC standard PLCC

EPROM sockets

Flash Not available Four Intel 28F008SA Flash memory

NVRAM and

RTC

Timers Four 32-bit tick timers and watchd og timer in Petra ASIC

Software

Interrupts

I/O Four EIA-232-D configurable serial ports via P2 and transition module

8K by 8 Non-Volatile RAM (NVRAM) and Real-Time Clock (RTC) with

battery backup and watchdog function (SGS-Thomson M48T58)

Two 32-bit tick timers and watchdog timer in VMEchip2 ASIC

Eight software interrupts (including those in the VMEchip2 ASIC)

Parallel (printer) interface via P2 and transition module

SCSI interface with DMA via P2 or LCP2 adapter board

Ethernet transceiver interface via DB15 connector on transition module

50/60MHz 32-bit MC68060

microprocessor

Two 44-pin JEDEC standard PLCC

EPROM sockets

devices with optional write protection

1

http://www.motorola.com/computer/literature 1-3

Page 30

1

Programming Issues

Table 1-1. MVME1X7P Features Summary (Continued)

Feature MVME167P MVME177P

VMEbus

interface

Switches Two pushbutton switches

Status Indicators Eight LEDs: Board Fail (FAIL), CPU Status (STAT), CPU Activity (RUN),

VMEbus system controller functions

VMEbus-to-local-bus interface (A32/A24, D32/D16/D8)

Local-bus-to-VMEbus interface (A16/A24/A32, D8/D16/D32)

Programmable interrupter and interrupt handler

Global Control/Status register for interprocessor communications

DMA capability for fast local-memory/VMEbus trans f ers (A16/A24/A32,

D16/D32 (D16/D32/D64 BLT)

(ABORT and RESET)

System Controller (

Activity

(SCSI), VME Activity (VME)

SCON), LAN Activity (LAN), LAN Pow er ( +12V), SCSI

Applicable Industry Standards

These boards conform to the requirements of the following documents:

❏ VMEbus Specification (IEEE 1014-87)

❏ EIA-232-D Serial Interface Specification, EIA

❏ SCSI Specification, ANSI

Block Diagram

Figure 1-1 and Figure 1- 2 ar e ge neral block diagrams of the MVME167P

and MVME177P single-board computers.

1-4 Computer Group Literature Center Web Site

Page 31

Introduction

1

Memory Array

ECC SDRAM

16-64MB

Up to 128MB ECC DRAM

Battery Optio n

MPU

SRAM

MC68040

PETRA

Connectors

Mezzanine

VMEchip 2

Interface

128KB

25/33MHZ

PCCCHIP 2

VMEbus

4 44-pin

PLCC

Controller

Ethernet

Compressor

SCSI

I/O Controller

Quad Serial

EPROM

i82696CA

53C710

CD2401

P1

P2

8KB RAM/Clock

Battery Backed

M48T58

Compatible

Parallel I/O

Centronics

Port

2816 0800

Figure 1-1. MVME167P Block Diagram

http://www.motorola.com/computer/literature 1-5

Page 32

1

Programming Issues

Memory Array

ECC SDRAM

16-128MB

Up to 128MB ECC DRAM

Battery Optio n

MPU

SRAM

4MB FLASH PETRA

MC68040

Connectors

Mezzanine

VMEchip 2

Interface

128KB

50/60MHZ

PCCCHIP 2

VMEbus

2 44-pin

PLCC

Controller

Ethernet

Compressor

SCSI

I/O Controller

Quad Serial

EPROM

i82696CA

53C710

CD2401

P1

P2

8KB RAM/Clock

Battery Backed

M48T58

Compatible

Parallel I/O

Centronics

Port

2816 0800

Figure 1-2. MVME177P Block Diagram

1-6 Computer Group Literature Center Web Site

Page 33

Programming Interfaces

The following sections describe the programming interface to devices on

the MVME167P and MVME177P single-board computers. Unless the

section specifies a particular board type, the discussion applies to both

models.

MC680X0 MPU

The MVME167P is based on the MC68040 microprocessor. The

MVME177P is based on the MC68060 microprocessor. Both processors

have on-chip instruction and data caches and a floating-point processor

(refer to the MC68040 and MC68060 user’s manuals for more

information).

Both models are available in various versions with the features listed in

Table 1-1 on page 1-3.

Data Bus Structure

Programming Interfaces

1

The local bus for all si ngl e-board computers described in this manual is a

32-bit synchronous bus, which is based on an MC68040-compatible bus

and which supports burst transfers. Throughout this manual this bus is

referred to as the Local Bus. The various Local Bus master and slave

devices use the Local Bus to c ommunicate. Th e Local Bus is arbi trated b y

priority type a rbiter. The pr iority o f the Loca l Bus ma sters fr om highe st to

lowest is:

Highest priority 82596CA LAN

CD2401 serial (through the PCCchip2)

53C710 SCSI

VMEbus

Lowest priority MPU

http://www.motorola.com/computer/literature 1-7

Page 34

1

Programming Issues

As a general rule, any master can access any slave; not all combinations

pass the common sense test, h owever. Refer to the device- specific sectio ns

of this manual and t o the us er’s guide for eac h de vice t o deter min e its port

size, data bus connection, and any restrictions that apply when accessing

the device.

EEPROMs on the MVME1X7P

Both boards include 44-pin PLCC/CLCC sockets for EEPROMs,

organized as follows:

Model Sockets Banks

MVME167 4 2

MVME177 2 1

The MVME167P boards use 27C102JK or 27C202JK type EEPROMs.

The MVME177 boards use SGS-Thompson M27C4002 (256K x 16) or

AMD 27C4096 type EEPROMs.

The EEPROMs are organized as 32-bit wide banks that support 8-, 16-,

and 32-bit read accesses. (The MVME177 has Flash memory in addition

to EEPROM.)

MVME167

The EEPROMs are mapped to Local Bus addres s 0 following a Local Bus

reset. This allows t he MC6 8040 to access the stack pointer and exec uti on

address following a reset. The EEPROMs are contr olled by the VMEchip2

ASIC. The map decoder, the access time, and the time they appear at

address 0 are programmable parameters. Refer to Chapter 2, VMEchip2 for

more detail.

1-8 Computer Group Literature Center Web Site

Page 35

MVME177

The EEPROMs on the MVME177 share 2MB of memory with the first

2MB of Flash memory. The EEPROM can co-exist with 2MB of Flash, or

you may wish to program all 4MB as Flash memory. The Flash and

EEPROM configuration is jointly controlled by a configuration switch

(S4) as described in Chapters 1 and 4 of MVME177P Single Board

Computer Installation and Use, and by control bit GPIO2 in the

VMEchip2 ASIC, as described in Chapter 2, VMEchip2.

The EPROMs are mapped to Local Bus address 0 following a Local Bus

reset.This allows the MC68060 processor to access the reset vector and

execution address following a reset.

Flash Memory on the MVME177

The MVME177 includes four 28F008SA Flash memory devices. The 32bit wide Flash can support 8-, 16-, and 32-bit accesses. The Flash can be

used for the onboard debugger firmware, which can be downloaded from

I/O resources such as Ether net, SCSI, serial port, or VMEbus . Flash writeprotection is programmable by setting a control bit (GPIO bit 1) in the

VMEchip2 GPIO register after downloading.

Programming Interfaces

1

When the Flash memory is used with EEPROM, only the top or bottom

2MB of Flash memory is visible at any one time. For access to the

shadowed area of Flash, the 177Bug firmware provides the SFLASH

command.

The MVME177 is shipped with the top 2MB of Flash memory and

EEPROM mapped as illustrated by Map 2 in Figure 1-3.

The 177Bug is shipped in EEPROM. To map all 4MB of Flash and retain

access to the 177Bug, perform the following steps:

1. Map Flash and EEPROM as shown in Map 3 in Figure 1-3.

2. Copy the 177Bug into the bottom 2MB of Flash memory.

3. Remap Flash memory as shown in Map 1 in Figure 1-3.

http://www.motorola.com/computer/literature 1-9

Page 36

1

Programming Issues

MAP 1

FFBFFFFF

FLASH

MEMORY

4MB

FF800000

NO EPROM

IN MAP

MAP 2

(as shipped)

FLASH

TOP 2MB

1MB EPROM

DUPLICATED:

READABLE

NOT WRITABLE

1MB EPROM

(BUG)

MAP 3

FLASH

BOTTOM

2MB

1MB EPROM

DUPLICATED:

READABLE

NOT WRITABLE

1MB EPROM

FFBFFFFF

FFA00000

FF900000

FF800000

1534 9408

Figure 1-3. MVME177 Flash and EPROM Memory Mapping Schem es

SRAM

The MVME167P and MVME177P single-board computers include

128KB of 32-bit wide 100ns static RAM (SRAM) that supports 8-, 16-,

and 32-bit wide accesses. The SRAM allows the debugger to operate and

limited diagnostics to execute without using the on-board SDRAM or

mezzanines. The SRAM is under t he cont rol o f the VMEchip2 ASI C, and

the access time is progr ammable. Refer to Chapter 2, VMEchip2 for more

detail.

The MVME177P provides for SRAM battery bac kup. The battery backup

function is supplied by a Dallas DS1210S nonvolatile controller chip and

Panasonic 2032 (or equivalent) battery.

1-10 Computer Group Literature Center Web Site

Page 37

The MVME177P implements primary a nd secondary backup sources. You

can select from +5V standby power, the onboard battery, or both.

The jumpers and configuration switches for the MVME167P and

MVME177P are described in Chapter 1 of the Installation and Use manual

for the respective boards.

Onboard SDRAM

MVME167P boards are built with 16MB-64MB synchronous DRAM

(SDRAM). MVME177P boards are built with 16MB-128MB SDRAM.

The MVME1X7P may have the SDRAM configured to model 4MB, 8MB,

16MB, 32MB, 64MB, or 128MB of ECC-protected DRAM.

In addition to the onboard SDRAM, an additional mezzanine (of the type

used on previous MVME1X7 boards) can be plugged in to provide up to

128MB of additional DRAM. All DRAM has ECC protection.

The SDRAM map decoder can be pr ogrammed to acc ommodate di ffer ent

base address(es) and sizes of mezzanine boards. The onboard SDRAM is

disabled by a Local Bus reset; it must be programmed in order for you to

access it.

Programming Interfaces

1

Most DRAM devices require some number of access cycles before the

DRAMs are fully operational. Normally this requirement is met by the

onboard refresh circuitry and normal DRAM initialization. However,

software should insure a minimum of 10 initialization cycles are

performed to each bank of RAM.

Detailed pro gramming informa tion is availab le in the chapte rs on the

memory options.

http://www.motorola.com/computer/literature 1-11

Page 38

1

Programming Issues

Battery-Backed-Up RAM and Clock

Although the M48T58-70 RAM and clock chip is an 8-bit device, the

interface provided by the PCCchip2 supports 8-, 16-, and 32-bit accesses

to the M48T58. No interrupts are generated by the clock. Refer to Chapter

3, PCCchip2 and to the M48T58 data sheet for detailed programming

guidance and battery life information.

VMEbus Interface

The VMEbus interface is implemented with an ASIC called the

VMEchip2. The VMEchip2 includes:

❏ Two tick timers

❏ A watchdog timer

❏ Programmable map decoders for the master and slave interfaces

❏ A VMEbus to/from local bus DMA controller

❏ A VMEbus to/from local bus non-DMA programmed access

interface

❏ A VMEbus interrupter, a VMEbus system controller, a VMEbus

interrupt handler, and a VMEbus requester

Processor-to-VMEbus tra nsfers can be D8, D16, or D32. VMEchip2 DMA

transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT,

or D64/MBLT.

Refer to Chapter 2, VMEchip2 for detailed programming information.

I/O Interfaces

The MVME167P and MVME177P single-board computers provide

onboard I/O for many syst em applications. The I/O func tions include serial

ports, parallel (printer) port , Ethernet trans ceiver interf ace, and SCSI mass

storage interface.

1-12 Computer Group Literature Center Web Site

Page 39

Serial Port Interface

The CD2401 serial controller chip (SCC) is used to implement the four

serial ports. The ser ial port s support th e standar d baud rate s (110 to 3 8.4K

baud). The four serial ports differ in function because of the limited

number of pins on the P2 I/O connector:

❏ Serial port 1 is a minimum-function asynchronous port. It uses

❏ Serial ports 2 and 3 are full-function asynchronous ports. They use

❏ Serial port 4 is a ful l-functio n asynchron ous or synch ronous port . It

All four serial ports use EIA-232-D drivers and receivers located on the

main board, and all the signal lines are routed to the I/O connector. The

configuration headers are located on the main board and may be on some

transition boar ds. An external I/O transition board is nec ess ary to convert

the I/O connector pinout to industry-standard connectors.

Programming Interfaces

1

RXD, CTS, TXD, and RTS.

RXD, CTS, DCD, TXD, RTS, and DTR.

can operate at synchronous bit rates up to 64 k bits per second. It

uses RXD, CTS, DCD, TXD, RTS, and DTR. It also interfaces to

the synchronous clock signal lines. Refer to Appendix C, Related

Documentation for drawings of the serial port interface

connections.

Note The MVME1X7P board hardware ties the DTR signal from the

CD2401 to the pin labeled RTS at connector P2. Likewise , RTS

from the CD2401 is tied to DTR on P2. Therefore, when

programming the CD2401, assert DTR when you want RTS, and

RTS when you want DTR.

On both MVME167P and MVME177P boards, the interface provided by

the PCCchip2 allows t he 16-b it CD2401 ser ial cont roll er chip t o appear at

contiguous addresses. Acce ss es to the CD2401, howeve r, must be 8 or 16

bits. 32-bit acces ses are not permitted. Ref er to the CD24 01 data sheet and

to Chapter 3, PCCchip2 for detailed pro gramming information.

http://www.motorola.com/computer/literature 1-13

Page 40

1

Programming Issues

The CD2401 supports DMA operations to local memory. Because the

CD2401 does not support a retry operation necessary to break VMEbus

lockup conditions, the CD2401 DMA controllers should not be

programmed to access the VMEbus. The hardware does not restrict the

CD2401 to onboard DRAM.

Parallel (Printer) Interface

The PCCchip2 ASIC provides an 8-bit bidirectional parall el port. All eight

bits of the port must be either inputs or outputs (no individual selection).

In addition to the 8 bits of data, there are two control pins and five status

pins. Each of the status pins can generate an interrupt to the MPU in any

of the following programmable conditions: high level, low level,

high-to-low transit ion, or low-to-h igh transi tion. This po rt may be used as

a Centronics-compatible parallel printer port or as a general parallel I/O

port.

When used as a para llel printer por t, the five stat us pins function as : Printer

Acknowledge (ACK), Printer Fault (FAULT∗), Printer Busy (BSY),

Printer Select (SELECT), and Printer Paper Error (PE), while the control

pins act as P rinter Strobe (STROBE∗), and Input Prime (INP∗).

The PCCchip2 provides an auto-strobe feature similar to that of the

MVME147 PCC. In auto-strobe mode, after a write to the Printer Data

Register, the PCCchip2 automatically asserts the STROBE∗ pin for a

selected time specified by the Printer Fast Strobe control bit. I n manual

mode, the Printer Strobe control bit directly controls the state of the

STROBE∗ pin.

Refer to Chapter 3, PCCchip2 for detailed programming information.

Refer to Appendix C, Relate d Documenta tion for drawings of the printer

port interface connections.

1-14 Computer Group Literature Center Web Site

Page 41

Ethernet Interface

The MVME1X7P uses the Intel 82596CA LAN co processor to implement

the Ethernet transceiver interface. The 82596CA accesses local RAM

using DMA operations to perform its normal functions. Because the

82596CA has small internal buffers and the VMEbus has an undefined

latency period, buffer overrun may occur if the DMA is programmed to

access the VMEbus. Therefore, the 82596CA should not be programmed

to access the VMEbus.

Every MVME1X7P that is built with an Ethernet interface is assigned an

Ethernet Station Addre ss. The add ress i s $0001AFxxxxxx where x xxx xx is

the unique 6-nibble n umber assigned to the board (i.e., every MVME1X7P

has a different value for xxxxxx).

Each board has an Ethernet Station Address displa yed on a label attached