Page 1

MVME172

VME Embedded Controller

Programmer’s

Reference Guide

VME172A/PG2

Edition of February 1999

Page 2

Notice

While reasonable efforts have been made to assure the accuracy of this document,

Motorola, Inc. a ssumes n o lia bility r esulti ng from any omissio ns in this docu ment, or from

the use of the information ob tained therein. Motorola reserv es the right to r evise this

document and to ma ke c hanges from time to ti me in t he content hereof witho ut o bligation

of Motorola to notify any person of such revision or changes.

No part of this material may be reproduce d or copied in any tangi ble medium, or stored in

a retrieval system, or transmitted in any form, or by any means, radio, electronic,

mechanical, photocopying, recording or facsimile, or otherwise, without the prior written

permission of Motorola, Inc.

It is possible that this pu blicati on ma y cont ain r eferenc e to, or i nformat ion a bout Mot oro la

products (machines and programs), programming, or services that are not announced in

your country. Such refere nces or informat ion must not be construed to mean that Moto rola

intends to announce such Motorola products, programming, or services in your country.

Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S.

Government, the following notice shall apply unless otherwise agreed to in writing by

Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in

subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at

DFARS 252.227-7013.

Motorola, Inc.

Computer Group

2900 South Diablo Way

Tempe, Arizona 85282

Page 3

Preface

This manual provides board level information and detailed ASIC chip information

including register bit descriptions for the MVME172 Embedded Controller. The

information contained in this manual applies to the following MVME172 models:

MVME172-303

MVME172-213 MVME172-313 MVME172-413 MVME172-513

MVME172-223 MVME172-323

MVME172-233 MVME172-333 MVME172-433

MVME172-243 MVME172-343

MVME172-253 MVME172-353 MVME172-453

MVME172-263 MVME172-363

MVME172-373

This manual is intended for anyone who wants to program these boards in order to design

OEM systems, supply addi ti ona l capability to an exi st ing compa ti bl e s yst em, or work in a

lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in Related

Documentation below.

Manual Terminology

Throughout this manual , a convention i s used which pr ecedes dat a and addres s parameters

by a character identifying the numeric format as follows:

$ dollar specifies a hexadecimal character

% percent specifies a binary number

& ampersand specifies a decimal number

For example, “12” is the decimal number twelve, and “$12” is the decimal number

eighteen.

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (*) foll owing the signal name for sign als which are le vel significant denote s that

the signal is true or valid when the signal is low.

An asterisk (*) foll owing the signal name for sign als which are edge significant denote s that

the actions initiated by that signal occur on high to low transition.

Page 4

In this manual, assertion and negation are used to specify forcing a signal to a particular

state. In particular, assertion and assert refer to a signal th at is ac tive or true ; negat ion a nd

negate indicate a sign al tha t is in activ e or fal se. These te rms are u sed i ndepend ently of the

voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

❏ A byte is eight b it s, numbe red 0 through 7, with bi t 0 being the least si gni fi ca nt.

❏ A word is 16 bits, numbered 0 thr ough 15, with bit 0 being the least si gni fi can t.

❏ A longword is 32 bits, numbered 0 through 31, with bit 0 being the least

significant.

The terms contr ol bi t, sta tus bit, true, and false a re use d exte nsivel y in t his do cument. Th e

term control bit is used to describe a bit in a register that can be set and cleared under

software con trol. The term tr ue is used to indicate that a bit is in the state that enables the

function it controls. The term false is used to indi cate that th e bit is in the state tha t disables

the function it cont rols. In all tables, th e terms 0 and 1 are used to descri be the actua l value

that should be writt en to the bi t, or t he val ue tha t it yield s when r ead. The term stat us b it is

used to describe a bit in a register that reflects a specific condition. The status bit can be

read by software to determine operational or exception conditions.

Recent Updates

This edition of the MVME172 VME Embedded Controller Programmer’ s Reference Guid e

incorporates the following changes:

❏ The ‘‘MVME172 Version Register ‘‘ s ectio n has an improved descr iptio n of th e

function of bit V6.

❏ The ‘‘PROM Access Time Cont rol Reg ist er ’’ and ‘‘Flash Access Time Control

Register’’ have clarification relating to bus speed s and access times with the

MVME172’s MC68060 processor.

❏ In accordance with re cent MCG practi ce, the ‘‘Re lated Documentat ion’’ secti on

has been moved from the front of the document to a separate appendix.

Page 5

The computer programs stored in the Read Only Memory of this device contain material

copyrighted by Motorola Inc., first published 1990, and may be used only under a license

such as the License f or Computer Progra ms (Article 14) contained in Moto rola’s T erms and

Conditions of Sale, Rev. 1/79.

This equipment generates , uses, and can radiate elec tro- magneti c

!

WARNING

Motorola and the Motorola symbol are registered trademarks of Motorola, Inc.

All other products ment io ned i n this document are trademarks or re gi st ered trademarks of

their respective holders.

energy. It may cause or be susceptible to electro-magnetic

interference (EMI) if not in stalled and used in a cabinet with

adequate EMI protection.

© Copyright Motorola, Inc. 1999

All Rights Reserved

Printed in the United States of America

February 1999

Page 6

Place holder

Page 7

Contents

CHAPTER 1 Board Description and Memory Maps

Introduction................................................................................................................1-1

Overview....................................................................................................................1-1

Requirements .............................................................................................................1-4

Block Diagrams .........................................................................................................1-5

Functional Description ...............................................................................................1-5

No-VMEbus-Interface Option............................................................................1-5

VMEbus Interface and VMEchip2.....................................................................1-9

Memory Maps............................................................................................................1-9

Local Bus Memory Map.....................................................................................1-9

Normal Address Range................................................................................1-9

Detailed I/O Memory Maps.......................................................................1-21

BBRAM/TOD Clock Memory Map..........................................................1-40

Interrupt Acknowledge Map......................................................................1-46

VMEbus Memory Map.................................... ...... ...........................................1-46

VMEbus Accesses to the Local Bus..........................................................1-47

VMEbus Short I/O Memory Map..............................................................1-47

Software Support Considerations ............................................................................1-47

Interrupts...........................................................................................................1-47

Cache Coherency..............................................................................................1-48

Sources of Local BERR*..................................................................................1-48

Local Bus Time-out...................................................................................1-48

VMEbus Access Time-out.............................. ...... ..... ................................1-49

VMEbus BERR* ................................. ..... .................................................1-49

Local DRAM Parity Error.........................................................................1-49

VMEchip2 .................................................................................................1-49

Bus Error Processing.................................................................................1-49

Description of Error Conditions on the MVME172.........................................1-50

MPU Parity Error.......................................................................................1-50

MPU Off-board Error................................................................................1-51

MPU TEA - Cause Unidentified ...............................................................1-51

MPU Local Bus Time-out.........................................................................1-51

DMAC VMEbus Error ............................. ...... ...... .....................................1-52

DMAC Parity Error................. ...... ...... ......................................................1-52

DMAC Off-board Error.............................................................. ...............1-53

DMAC LTO Error..................................................... ...... ...... ....................1-53

vii

Page 8

DMAC TEA - Cause Unidentified............................................................1-54

LAN Parity Error.......................................................................................1-54

LAN Off-Board Error ...............................................................................1-55

LAN LTO Error ........................................................................................1-55

SCSI Parity Error ......................................................................................1-56

SCSI Off-Board Error...............................................................................1-56

SCSI LTO Error........................................................................................1-56

Example of the Proper Use of Bus Timers.......................................................1-57

MVME172 MC68060 Indivisible Cycles........................................................1-58

Illegal Access to IP Modules from External VMEbus Masters .......................1-59

CHAPTER 2 VMEchip2

Introduction ...............................................................................................................2-1

Summary of Major Features...............................................................................2-1

Functional Blocks......................................................................................................2-4

Local Bus to VMEbus Interface.........................................................................2-4

Local Bus to VMEbus Requester................................................................2-7

VMEbus to Local Bus Interface........................................... ..............................2-9

Local Bus to VMEbus DMA Controller..........................................................2-10

No Address Increment DMA Transfers....................................................2-12

DMAC VMEbus Requester .......................................... ...... ......................2-13

Tick and Watchdog Ti mers............................................................... ..... ...... .....2-14

Prescaler................ ....................................................................................2-14

Tick Timers...............................................................................................2-15

Watchdog Timer........................................................................................2-15

VMEbus Interrupter ............................................ ...... ...... .................................2-16

VMEbus System Controller ................................ ...... .......................................2-17

Arbiter................... ....................................................................................2-17

IACK Daisy-Chain Driver ........................................................................ 2-17

Bus Timer..................................................................................................2-17

Reset Driver ..............................................................................................2-18

Local Bus Interrupter and Interrupt Handler....................................................2-18

Global Control and Status Registers ................................................................2-20

LCSR Programming Model.....................................................................................2-20

Programming the VMEbus Slave Map Decoders............................................2-26

VMEbus Slave Ending Address Register 1 .............................................2-28

VMEbus Slave Starting Address Register 1 ............................................2-28

VMEbus Slave Ending Address Register 2 .............................................2-29

VMEbus Slave Starting Address Register 2 ............................................2-29

VMEbus Slave Address Translation Address Offset Register 1 ..............2-29

viii

Page 9

VMEbus Slave Address Translation Select Register 1 ............................2-30

VMEbus Slave Address Translation Address Offset Register 2...............2-31

VMEbus Slave Address Translation Select Register 2 ............................2-31

VMEbus Slave Write Post and Snoop Control Register 2 ........................2-32

VMEbus Slave Address Modifier Select Register 2.................................2-33

VMEbus Slave Write Post and Snoop Control Register 1 ........................2-35

VMEbus Slave Address Modifier Select Register 1.................................2-36

Programming the Local Bus to VMEbus Map Decoders.................................2-37

Local Bus Slave (VMEbus Master) Ending Address Register 1...............2-39

Local Bus Slave (VMEbus Master) Starting Address Register 1..............2-40

Local Bus Slave (VMEbus Master) Ending Address Register 2...............2-40

Local Bus Slave (VMEbus Master) Starting Address Register 2..............2-40

Local Bus Slave (VMEbus Master) Ending Address Register 3 ..............2-41

Local Bus Slave (VMEbus Master) Starting Address Register 3 .............2-41

Local Bus Slave (VMEbus Master) Ending Address Register 4 ..............2-41

Local Bus Slave (VMEbus Master) Starting Address Register 4 .............2-42

Local Bus Slave (VMEbus Master)

Address Translation Address Register 4 ..........................................2-42

Local Bus Slave (VMEbus Master)

Address Translation Select Register 4 ..............................................2-42

Local Bus Slave (VMEbus Master) Attribute Register 4 .........................2-43

Local Bus Slave (VMEbus Master) Attribute Register 3 .........................2-44

Local Bus Slave (VMEbus Master) Attribute Register 2 .........................2-45

Local Bus Slave (VMEbus Master) Attribute Register 1 .........................2-46

VMEbus Slave GCSR Group Address Register .......................................2-47

VMEbus Slave GCSR Board Address Register .......................................2-48

Local Bus to VMEbus Enable Control Register .......................................2-49

Local Bus to VMEbus I/O Control Register ............................................2-50

ROM Control Register ................................... ...........................................2-51

Programming the VMEchip2 DMA Controller ................................................2-52

DMAC Registers ................................. ......................................................2-53

PROM Decoder, SRAM and DMA Control Register ..............................2-54

Local Bus to VMEbus Requester Control Register ..................................2-55

DMAC Control Register 1 (bits 0-7) ........................................................2-56

DMAC Control Register 2 (bits 8-15) ......................................................2-57

DMAC Control Register 2 (bits 0-7) ........................................................2-59

DMAC Local Bus Address Counter...................................... ..... ...............2-60

DMAC VMEbus Address Counter ...........................................................2-60

DMAC Byte Counter ............................... ...... ...........................................2-61

Table Address Counter .............................................................................2-61

VMEbus Interrupter Control Register ......................................................2-61

VMEbus Interrupter Vector Register .............................................. .........2-63

ix

Page 10

MPU Status and DMA Interrupt Count Register .....................................2-63

DMAC Status Register ............................................................. ................2-64

Programming the Tick and Watchdog Timers..................................................2-65

VMEbus Arbiter Time-out Control Register ...........................................2-65

DMAC Ton/Toff Timers

and VMEbus Global Time-out Control Register..............................2-66

VME Access, Local Bus, and Watchdog Time-out Control Register ......2-67

Prescaler Control Register ........................................................................2-68

Tick Timer 1 Compare Register ...............................................................2-69

Tick Timer 1 Counter ...............................................................................2-69

Tick Timer 2 Compare Register ...............................................................2-70

Tick Timer 2 Counter ...............................................................................2-70

Board Control Register ............................................................................2-71

Watchdog Timer Control Register ...........................................................2-72

Tick Timer 2 Control Register .................................................................2-73

Tick Timer 1 Control Register .................................................................2-74

Prescaler Counter .....................................................................................2-74

Programming the Local Bus Interrupter...........................................................2-75

Local Bus Interrupter Status Register (bits 24-31) ..................................2-78

Local Bus Interrupter Status Register (bits 16-23) ..................................2-79

Local Bus Interrupter Status Register (bits 8-15) ....................................2-80

Local Bus Interrupter Status Register (bits 0-7) ......................................2-81

Local Bus Interrupter Enable Register (bits 24-31) .................................2-82

Local Bus Interrupter Enable Register (bits 16-23) .................................2-83

Local Bus Interrupter Enable Register (bits 8-15) ...................................2-84

Local Bus Interrupter Enable Register (bits 0-7) .....................................2-85

Software Interrupt Set Register (bits 8-15) ..............................................2-86

Interrupt Clear Register (bits 24-31) ........................................................2-86

Interrupt Clear Register (bits 16-23) ........................................................2-87

Interrupt Clear Register (bits 8-15) ..........................................................2-88

Interrupt Level Register 1 (bits 24-31) ..................................................... 2-88

Interrupt Level Register 1 (bits 16-23) ..................................................... 2-89

Interrupt Level Register 1 (bits 8-15) .......................................................2-89

Interrupt Level Register 1 (bits 0-7) .........................................................2-90

Interrupt Level Register 2 (bits 24-31) ..................................................... 2-90

Interrupt Level Register 2 (bits 16-23) ..................................................... 2-91

Interrupt Level Register 2 (bits 8-15) .......................................................2-91

Interrupt Level Register 2 (bits 0-7) .........................................................2-92

Interrupt Level Register 3 (bits 24-31) ..................................................... 2-92

Interrupt Level Register 3 (bits 16-23) ..................................................... 2-93

Interrupt Level Register 3 (bits 8-15) .......................................................2-93

Interrupt Level Register 3 (bits 0-7) .........................................................2-94

x

Page 11

Interrupt Level Register 4 (bits 24-31) .....................................................2-94

Interrupt Level Register 4 (bits 16-23) .....................................................2-95

Interrupt Level Register 4 (bits 8-15) .......................................................2-95

Interrupt Level Register 4 (bits 0-7) .........................................................2-96

Vector Base Register ................................................................................2-96

I/O Control Register 1 ..............................................................................2-97

I/O Control Register 2 ..............................................................................2-98

I/O Control Register 3 ..............................................................................2-98

Miscellaneous Control Register ................................................................2-99

GCSR Programming Model...................................................................................2-101

Programming the GCSR.................................................................................2-103

VMEchip2 Revision Register .................................................................2-105

VMEchip2 ID Register ............................................................................2-105

VMEchip2 LM/SIG Register ..................................................................2-105

VMEchip2 Board Status/Control Register .............................................2-107

General Purpose Register 0 ....................................................................2-108

General Purpose Register 1 ....................................................................2-108

General Purpose Register 2 ....................................................................2-109

General Purpose Register 3 ....................................................................2-109

General Purpose Register 4 ....................................................................2-110

General Purpose Register 5 ....................................................................2-110

CHAPTER 3 MC2 Chip

Introduction................................................................................................................3-1

Summary of Major Features...............................................................................3-1

Functional Description ...............................................................................................3-2

MC2 Chip Initialization......................................................................................3-2

Flash and PROM Interface .................................................................................3-2

BBRAM Interface............................................................. ...... ............................3-3

82596CA LAN Interface ....................................................................................3-3

MPU Port and MPU Channel Attention......................................................3-3

MC68060-Bus Master Support for 82596CA .............................................3-4

LANC Bus Error................................................... .......................................3-4

LANC Interrupt ....................... ...... ..............................................................3-5

53C710 SCSI Controller Interface......................................................................3-5

SRAM Memory Controller.................................................................................3-5

NON-ECC DRAM Memory Controller .............................................................3-5

Z85230 SCC Interface........................................................................................3-6

Tick Timers............................................................ ........................................ .....3-7

Watchdog Timer..................................................................................................3-8

xi

Page 12

Local Bus Timer.................................................................................................3-8

Memory Map of the MC2 Chip Registers.................................................................3-8

Programming Model................................................................................................3-10

MC2 Chip ID Register .....................................................................................3-11

MC2 Chip Revision Register ........................................................................... 3-11

General Control Register .................................................................................3-12

Interrupt Vector Base Register .........................................................................3-13

Programming the Tick Timers..........................................................................3-15

Tick Timer 1 and 2 Compare and Counter Registers................................3-15

LSB Prescaler Count Register........................................................ ...... .....3-17

Prescaler Clock Adjust Register................................................................3-18

Tick Timer 1 and 2 Control Registers.......................................................3-18

Tick Timer Interrupt Control Registers.....................................................3-20

DRAM Parity Error Interrupt Control Register ...............................................3-22

SCC Interrupt Control Register........................................................................3-23

Tick Timer 3 and 4 Control Registers.............................................................. 3-24

DRAM and SRAM Memory Controller Registers...........................................3-25

DRAM Space Base Address Register.......................................................3-25

SRAM Space Base Address Register........................................................3-26

DRAM Space Size Register........ ...... ...... ..................................................3-26

DRAM/SRAM Options Register ..............................................................3-27

SRAM Space Size Register.......................................................................3-29

LANC Error Status Register............................................ ..... ............................3-30

82596CA LANC Interrupt Control Register....................................................3-31

LANC Bus Error Interrupt Control Register....................................................3-32

SCSI Error Status Register...............................................................................3-33

General Purpose Inputs Register........ ...... ........................................................3-33

MVME172 Version Register............................................................................3-35

SCSI Interrupt Control Register.......................................................................3-36

Tick Timer 3 and 4 Compare and Counter Registers.......................................3-37

Bus Clock Register ...........................................................................................3-38

PROM Access Time Control Register .............................................................3-39

Flash Access Time Control Register................................................................3-40

ABORT Switch Interrupt Control Register......................................................3-41

RESET Switch Control Register......................................................................3-42

Watchdog Timer Control Register....................................................................3-43

Access and Watchdog Time Base Select Register............................................3-44

DRAM Control Register ................................................. ..... ............................3-45

MPU Status Register........................................................................................3-46

32-bit Prescaler Count Register........................................................................3-48

xii

Page 13

CHAPTER 4 IP2 Chip

Introduction................................................................................................................4-1

Summary of Major Features...............................................................................4-1

Functional Description ...............................................................................................4-2

General Description............................................................................................4-2

Cache Coherency................................................................................................4-2

Local Bus to IndustryPack DMA Controllers.....................................................4-3

Clocking Environments and Performance..........................................................4-5

Programmable Clock..........................................................................................4-7

Error Reporting...................................................................................................4-7

Error Reporting as a Local Bus Slave .................................................... .....4-7

Error Reporting as a Local Bus Master .......................................................4-7

IndustryPack Error Reporting......................................................................4-8

Interrupts.............................................................................................................4-8

Overall Memory Map ................................................................................................4-9

Programming Model................................................................................................4-10

Chip ID Register...............................................................................................4-17

Chip Revision Register.....................................................................................4-17

Vector Base Register.........................................................................................4-18

IP_a, IP_b, IP_c, IP_d Memory Base Address Registers.................................4-19

IP_a or Double Size IP_ab Memory Base Address Registers ..................4-20

IP_b Memory Base Address Registers......................................................4-20

IP_c or Double Size IP_cd Memory Base Address Registers...................4-21

IP_d Memory Base Address Registers......................................................4-21

IP_a, IP_b, IP_c, IP_d Memory Size Registers................................................4-21

IP_a, IP_b, IP_c, and IP_d; IRQ0 and IRQ1 Interrupt Control Registers........4-23

IP_a, IP_b, IP_c, and IP_d; General Control Registers....................................4-24

IP Clock Register..............................................................................................4-28

DMA Arbitration Control Register...................................................................4-29

IP RESET Register ..........................................................................................4-30

Programming the DMA Controllers.................................................................4-31

DMA Enable Function...............................................................................4-33

DMA Control and Status Register Set Definition.....................................4-33

Programming the Programmable Clock....................................................4-43

Local Bus to IndustryPack Addressing....................................................................4-46

8-Bit Memory Space .........................................................................................4-46

16-Bit Memory Space.......................................................................................4-47

32-Bit Memory Space.......................................................................................4-48

IP_a I/O Space..................................................................................................4-49

IP_ab I/O Space................................................................................................4-50

IP_a ID Space ...................................................................................................4-51

xiii

Page 14

IP to Local Bus Data Routing..................................................................................4-52

Memory Space Accesses...................................................... ...... ...... ................4-52

I/O and ID Space Accesses ..............................................................................4-54

CHAPTER 5 MCECC

Introduction ...............................................................................................................5-1

Features......................................................................................................................5-1

Functional Description ..............................................................................................5-2

General Description............................................................................................5-2

Performance........................................................................................................5-2

Cache Coherency................................................................................................5-3

ECC....................................................................................................................5-4

Cycle Types.................................................................................................5-4

Error Reporting ................................. ..........................................................5-5

Single Bit Error (Cycle Type = Burst Read or Non-Burst Read) ...............5-5

Double Bit Error (Cycle Type = Burst Read or Non-Burst Read)..............5-5

Triple (or Greater) Bit Error

(Cycle Type = Burst Read or Non-Burst Read)..................................5-6

Cycle Type = Burst Write...........................................................................5-6

Single Bit Error (Cycle Type = Non-Burst Write)......................................5-6

Double Bit Error (Cycle Type = Non-Burst Write)....................................5-6

Triple (or Greater) Bit Error (Cycle Type = Non-Burst Write) ..................5-6

Single Bit Error (Cycle Type = Scrub) .......................................................5-6

Double Bit Error (Cycle Type = Scrub)......................................................5-7

Triple (or Greater) Bit Error (Cycle Type = Scrub)....................................5-7

Error Logging.....................................................................................................5-7

Scrub...................................................................................................................5-7

Refresh..................................... ...... .....................................................................5-8

Arbitration.................... ...... ................................................................................5-8

Chip Defaults......................................................................................................5-8

Programming Model..................................................................................................5 -9

Chip ID Register...............................................................................................5-14

Chip Revision Register.....................................................................................5-14

Memory Configuration Register .......................................... ............................5-15

Dummy Register 0............................................................................................5-16

Dummy Register 1............................................................................................5-17

Base Address Register......................................................................................5-17

DRAM Control Register ................................................. ..... ............................5-18

BCLK Frequency Register...............................................................................5-20

Data Control Register.......................................................................................5-21

xiv

Page 15

Scrub Control Register......................................................................................5-23

Scrub Period Register Bits 15-8........................................................................5-24

Scrub Period Register Bits 7-0..........................................................................5-24

Chip Prescaler Counter.....................................................................................5-25

Scrub Time On/Time Off Register....................................................................5-25

Scrub Prescaler Counter (Bits 21-16)...............................................................5-27

Scrub Prescaler Counter (Bits 15-8).................................................................5-28

Scrub Prescaler Counter (Bits 7-0)...................................................................5-28

Scrub Timer Counter (Bits 15-8)......................................................................5-28

Scrub Timer Counter (Bits 7-0)........................................................................5-29

Scrub Address Counter (Bits 26-24).................................................................5-29

Scrub Address Counter (Bits 23-16).................................................................5-30

Scrub Address Counter (Bits 15-8)...................................................................5-30

Scrub Address Counter (Bits 7-4).....................................................................5-31

Error Logger Register....................................................... ................................5-31

Error Address (Bits 31-24)...............................................................................5-32

Error Address (Bits 23-16)...............................................................................5-33

Error Address Bits (15-8).................................................................................5-33

Error Address Bits (7-4)...................................................................................5-33

Error Syndrome Register........... .......................................................................5-34

Defaults Register 1............................................................................................5-34

Defaults Register 2............................................................................................5-36

Initialization......................................................................................................5-37

Syndrome Decode....................................................................................................5-39

APPENDIX A Related Documentation

Motorola Computer Group Documents....................................................................A-1

Literature Updates..............................................................................................A-2

Manufacturers’ Documents.......................................................................................A-2

APPENDIX B Using Interrupts on the MVME172

Introduction...............................................................................................................B-1

VMEchip2 Tick Timer 1 Periodic Interrupt Example..............................................B-1

INDEX

xv

Page 16

FIGURES

Figure 1-1. 200/300-Series MVME172 Block Diagram...........................................1-6

Figure 1-2. 400/500-Series MVME172 Block Diagram ...........................................1-7

Figure 2-1. VMEchip2 Block Diagram.....................................................................2-5

TABLES

Table 1-1. MVME172 Features Summary.................................................................1 -3

Table 1-2. Redundant Functions in the VMEchip2 and MC2 Chip .........................1-8

Table 1-3. 200/300-Series MVME172 Local Bus Memory Map............................1-10

Table 1-4. 400/500-Series MVME172 Local Bus Memory Map............................1-12

Table 1-5. 200/300-Series MVME172 Local I/O Devices Memory Map...............1-14

Table 1-6. 400/500-Series MVME172 Local I/O Devices Memory Map...............1-18

Table 1-7. VMEchip2 Memory Map (Sheet 1 of 3)................................................1-22

Table 1-8. MC2 Chip Register Map........................................................................1-27

Table 1-9. IP2 Chip Overall Memory Map..............................................................1-28

Table 1-10. IP2 Chip Memory Map - Control and Status Registers .......................1-29

Table 1-11. MCECC Internal Register Memory Map ............................................1-35

Table 1-12. Z85230 SCC Register Addresses .........................................................1-37

T ab le 1-13. 82596CA Ethernet LAN Memory Map.......................... ......................1-38

Table 1-14. 53C710 SCSI Memory Map ...............................................................1-39

Table 1-15. MK48T58 BBRAM/TOD Clock Memory Map...................................1-40

T ab le 1-16. BBRAM Configuration Area Memory Map .......................................1-41

Table 1-17. TOD Clock Memory Map ....................................................................1-42

Table 2-1. VMEchip2 Memory Map - LCSR Summary (Sheet 1 of 2) ..................2-22

Table 2-2. DMAC Command Table Format............................................................2-53

Table 2-3. Local Bus Interrupter Summary ............................................................2-76

Table 2-4. VMEchip2 Memory Map (GCSR Summary) ......................................2-104

Table 3-1. DRAM Performance.................................................................................3 -6

Table 3-2. MC2 Chip Register Map .........................................................................3-9

Table 3-3. Interrupt Vector Base Register Encoding and Priority...........................3-14

Table 3-4. DRAM Size Control Bit Encoding.........................................................3-27

Table 3-5. DRAM Size Control Bit Encoding.........................................................3-28

Table 3-6. SRAM Size Control Bit Encoding .........................................................3-28

Table 3-7. SRAM Size Control Bit Encoding .........................................................3-29

Table 4-1. IP2 Chip Clock Cycles.............................................................................4-6

Table 4-2. IP2 Chip Overall Memory Map ...............................................................4-9

Table 4-3. IP2 Chip Memory Map - Control and Status Registers .........................4-11

xvi

Page 17

Table 5-1. MCECC Specifications.............................................................................5-3

Table 5-2. MCECC Internal Register Memory Map, Part 1....................................5-10

Table 5-3. MCECC Internal Register Memory Map, Part 2 ...................................5-12

T ab le A-1. Motorola Computer Gr oup Documents..................................................A-1

Table A-2. Manufacturers’ Documents....................................................................A-2

xvii

Page 18

xviii

Page 19

1Board Description

Introduction

This manual provides programming information for the MVME172

Embedded Controller. Ex tensive programming in formation is provide d for

the Application-Specific Integrated Circuit (ASIC) devices used on the

board. Reference information is included for the Large Scale Integration

(LSI) devices us ed on the boa rd and sourc es for a dditional information are

provided.

This chapter briefly describes the board level hardware features of the

MVME172 Embedded Controller. The chapter begins with a board level

overview and featur es l ist. Memory maps are next, and the chapter close s

with some general software considerations such as cache coherency,

interrupts, and bus errors.

All programmable registers in the MVME172 that reside in ASICs are

covered in the chapters on those ASICs. Chapte r 2 cover s the VMEchi p2,

Chapter 3 covers the MC2 chip, an d Chapter 4 covers the IP2 chip. Chapter

5 covers the MCECC chip, used only on 200/300-Series MVME172.

Appendix A describes using interrupts. For those interested in

programmable register bit definitions and less interested in hardware

functionality, focus on Chapters 2, 3, 4, and 5. In some cases, however,

Chapter 1 gives related background information.

and Memory Maps

1

Overview

The MVME172 is based on the MC68060 or MC68LC060

microprocessor. The MVME172 is available in various versions with the

features listed in Table 1-1 on page 1-3. A “No VMEbus” option is also

available.

The I/O connection fo r the 200/300-Seri es MVME172 is provided thr ough

four RJ-45 front panel connectors.

1-1

Page 20

1

Board Description and Memory Maps

The I/O connection for t he 4 00/500-Series serial ports is p rovided by two

DB-25 front panel I/O connectors. The I/O is connected to t he VMEbus P2

connector. The main boar d is connect ed through a P2 t ransiti on board and

cables to transition boards. The Series 400/500 MVME172 supports the

transition boards MVME712-12, MVME712-13, MVME712M,

MVME712A, MVME712AM, and MVME712B (referred to in this

manual as MVME712x, unless separately specified). These transition

boards provide configuration headers, serial port drivers and industry

standard connectors for the I/O devices. The MVME712 series transition

boards were designed to support the MVME167 boards, but can be used

on the MVME172 by following some special precautions. (Refer to the

section on the Serial Communications Interface in the MVME172

installation and use manual furnished with your 400/500-Series

MVME172, for more informat ion.)

The VMEbus interface is provi ded by an ASIC called th e VMEchip2. The

VMEchip2 includes two tick timers, a watchdo g timer, programmable map

decoders for the master and sl ave inter faces, and a VMEbus to/ from loc al

bus DMA controller, a VMEbus to/ from local bus non-DMA programmed

access interface, a VMEbus interrupter, a VMEbus system controller, a

VMEbus interrupt handler, and a VMEbus requester.

Processor-to-VMEbus tra nsfers can be D8, D16, or D32. VMEchip2 DMA

transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT,

or D64/MBLT.

The MC2 chip ASIC provides four tick timers, the interface to the LAN

chip, SCSI chip, seri al port chip , BBRAM, the progra mmable interfac e for

the DRAM and/or SRAM mezzanine board, and Flash write enable.

The IndustryPack Interface Controller (IP2 chip) ASIC provides control

and status information, including DMA control, for up to four single size

IndustryPacks (IPs) or up to two double size IPs that can be plugged into

the MVME172 main module.

1-2 Computer Group Literature Center Web Site

Page 21

Overview

The MCECC chip Memory Controller ASIC on the 200/300-Series

MVME172 provides the programmable interface for the ECC-protected

16 MB DRAM mezzanine board.

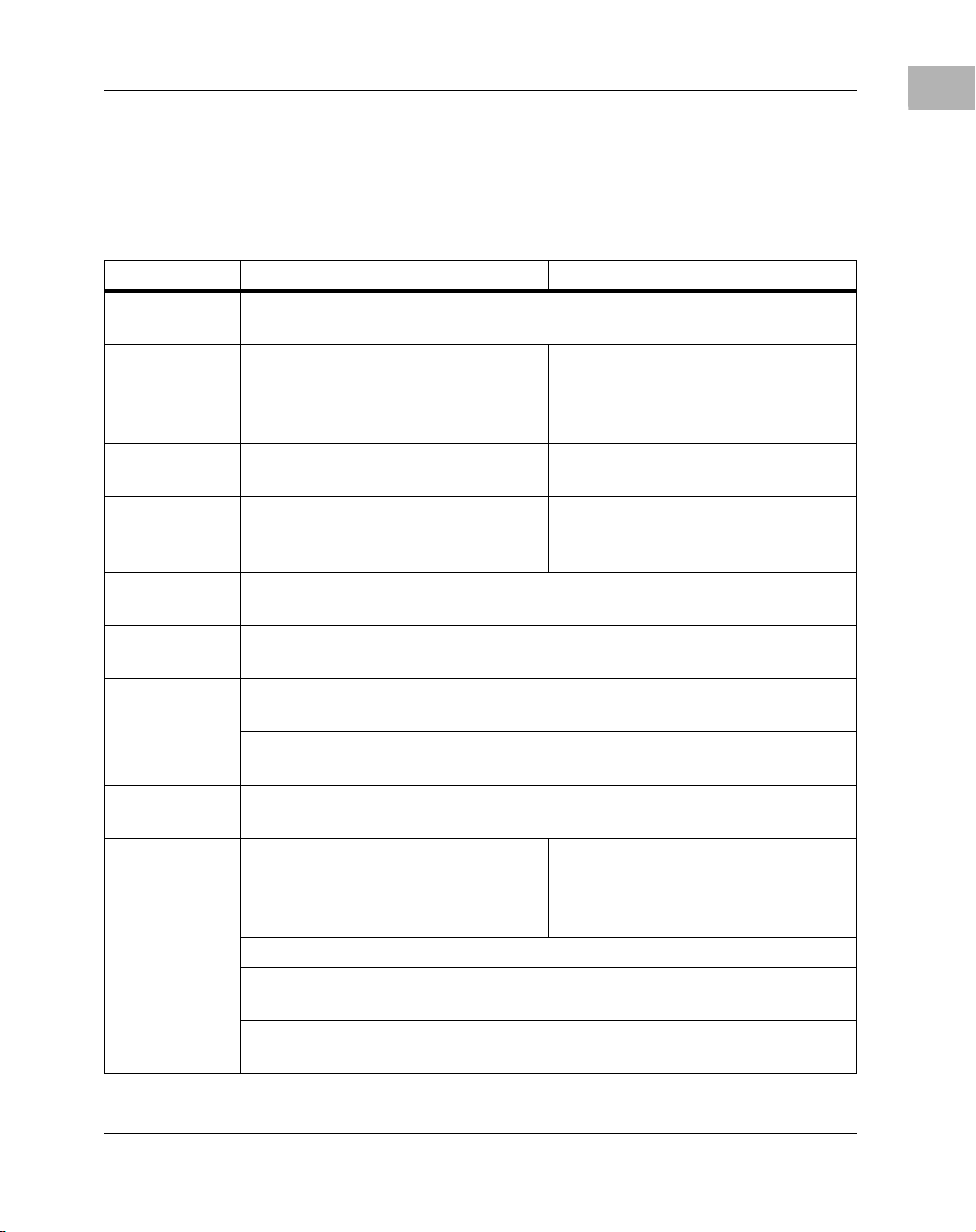

Table 1-1. MVME172 Features Summary

Feature 200/300-Series 400/500-Series

Processor 6

0 MHz 32-bit MC68060 microprocessor, or 64 MHz 32-bit

MC68LC060 microprocessor

DRAM 4MB, 8 MB, or 16 MB of shared

DRAM with parity protection on a

mezzanine module, or up to 64 MB of

ECC-protected DRAM

SRAM 128 K

B of SRAM with battery

4MB, 8 MB, or 16 MB of shared

DRAM with no protection

512KB of SRAM with battery backup

backup

PROM/

EPROM

Sockets

Flash One Intel 28F016SA 2M x 8 Flash memory device (2MB Flash memory

NVRAM and

TOD

Timers Four 32-bit Tick Timers and Watchdog Timer (in the MC2 Chip ASIC) for

Software

Interrupts

I/O Four serial ports, both EIA-232-D RJ-45Tw

Two JEDEC standard 32-p in DIP

PROM sockets

total) with write protection (optional)

8K by 8 Non-Volatile RAM (NVRAM) and Time-of-Day (TOD) clock with

battery backup

periodic interrupts

Two 32-bit Tick Timers and Watchdog Timer in the VMEchip2 ASIC) for

periodic interrupts

Eight software interrupts (for MVME172 versions that have the VMEchip2)

Serial port controller

Optional Small Computer Systems Interface (SCSI) bus interface with 32-bit

local bus burst Direct Memory Access (DMA) (NCR 53C710 controller)

Optional LAN Ethernet transceiver interface with 32- bit lo cal b us DMA (In ter

82596CA controller)

s (Zilog Z85230)

ne JEDEC standard 32-pin

O

PLCC EPROM socket (EPROMs

may

be shipped separately)

o serial ports; one EIA-232-D

DCE, one EIA-232-D DCE/DTE or

EIA-530 DCE/DTE or EIA-42

DCE/DTE or EIA-485

1

http://www.mcg.mot.com/literature 1-3

Page 22

1

Board Description and Memory Maps

Table 1-1. MVME172 Features Summary

Feature 200/300-Series 400/500-Series

Two MVIP IndustryPack

interfaces with DMA

VMEbus

interface

(boards may be

special ordered

without the

VMEbus

interface)

Switches Two pushbutton switches

Light-Emitting

Diodes (LEDs)

VMEbus system controller functions

VMEbus interface to local bus (A24/A32,

D8/D16/D32 (D8/D16/D32/D64 BLT) (BLT = Block Transfer)

Local bus to VMEbus interface (A16/A24/A32, D8/D16/D32)

VMEbus interrupter

VMEbus interrupt handler

Global CSR for interprocessor communications

DMA for fast local memory - VMEbus transfers (A16/A24/A32, D16/D32

(D16/D32/D64 BLT)

Four LEDs: FAIL, RUN, SCON,

FUSES (LAN power)

(ABORT and RESET)

Four MVIP IndustryPack

interfaces with DMA

Eight LEDs: FAIL, STAT, RUN,

SCON, LAN, FUSE (LAN power),

SCSI, and VME

Requirements

These boards are desi gned to conform t o the requirements of the followin g

documents:

❏ VMEbus Specification (IEEE 1014-87)

❏ EIA-232-D Serial Interface Specification, EIA

❏ SCSI Specification, ANSI

❏ IndustryPack Specification, GreenSpring

1-4 Computer Group Literature Center Web Site

Page 23

Block Diagrams

Figure 1-2 on page 1-7 is a general block diagram of the 200/300-Series

MVME172. Figure 1-2 on page 1-7 is a general block diagram of the

400/500-Series MVME172.

Functional Description

This section covers only a few specific features of the MVME172.

A complete functional description of the major blocks of the MVME172

Embedded Controller is provided in your MVME172 installation and use

manual.

No-VMEbus-Interface Option

The MVME172 can be operated as an embedded controller without the

VMEbus interface. For this option, the VMEchip2 and the VMEbus

buffers are not populat ed. Also, the bu s grant daisy ch ain an d the i nterrupt

acknowledge daisy chain have zero-ohm bypass resistors installed.

Block Diagrams

1

To support this fea ture, certain l ogic in the VMEchip2 h as been duplic ated

in the MC2 chip. Table 1-2 on page 1-8 defines the location of the

redundant logic. This logic is inhibited in the MC2 chip if the VMEchip2

is present. The enables for these functions are controlled by software and

MC2 chip hardware initialization.

Note that an MVME172 ordered witho ut the VMEbus i nterface is shipped

with Flash memory blank (the factory uses the VMEbus to program the

Flash memory with debugger code). To use the 172Bug package,

MVME172Bug, in such models, be sure that the General Purpose

Readable Jumpers Header is configured for the EPROM memory map.

Refer to Chapters 3 and 4 of your MVME172 installat ion and use manual

for further details.

http://www.mcg.mot.com/literature 1-5

Page 24

1

Board Description and Memory Maps

4 Serial Ports

Optional

RJ-45 Front

Panel

SCSI

Ethernet

2MB

Flash

Optional

EIA-232

Transceivers

Connector

Peripherals

Panel SCSI

68-pin Front

Panel

Connector

Transceiver

DB-15 Front

Serial

Dual 85230

I/O Controllers

MC2 chip

Sockets

EPROM

Two 32-p in

SCSI

53C710

Coprocessor

Ethernet

Controller

i82596CA

M48T58

Battery Backed

8KB RAM/Clock

128KB SRAM

Memory Array

ECC DRAM

Memory Array

4,8,16,32,64MB

Array

DRAM Memory

4,8,16MB Parity

21009702

w/Battery

Configuration Dependent

A32/D32

I/O

2 Channels

IndustryPack

Optional

VMEbus

Master/Slave

IP2

Interface

IndustryPack

MPU

Optional

MC68LC060

VMEbus

Interface

VMEchip2

MC68060

A32/24:D64/32/16/08

Figure 1-1. 200/300-Series MVME172 Block Diagram

1-6 Computer Group Literature Center Web Site

Page 25

Functional Description

1

2MB

Flash

Optional

or

Via P2 and

2 Serial Ports

Transition Module

DB-25 Front Panel

SCSI

Optional

Ethernet

Peripherals

Transceiver

Via P2 and

connections are

Via P2 and

connections are

EIA-232

Transceivers

Transition Modules

Transition Modules

Serial

Dual 85230

I/O Controllers

MC2 chip

Socket

1 PLCC

SCSI

53C710

Coprocessor

Ethernet

Controller

i82596CA

M48T58

Battery Backed

8KB RAM/Clock

512KB SRAM

Memory Array

Array

DRAM Memory

4,8,16MB Parity

2038 9706

w/Battery

Configuration Dependent

A32/D32

Optional

I/O

4 Channels

IndustryPack

VMEbus

Master/Slave

A32/24:D64/32/16/08

IP2

Interface

IndustryPack

MPU

Optional

MC68LC060

VMEbus

Interface

VMEchip2

MC68060

Figure 1-2. 400/500-Series MVME172 Block Diagram

http://www.mcg.mot.com/literature 1-7

Page 26

1

Board Description and Memory Maps

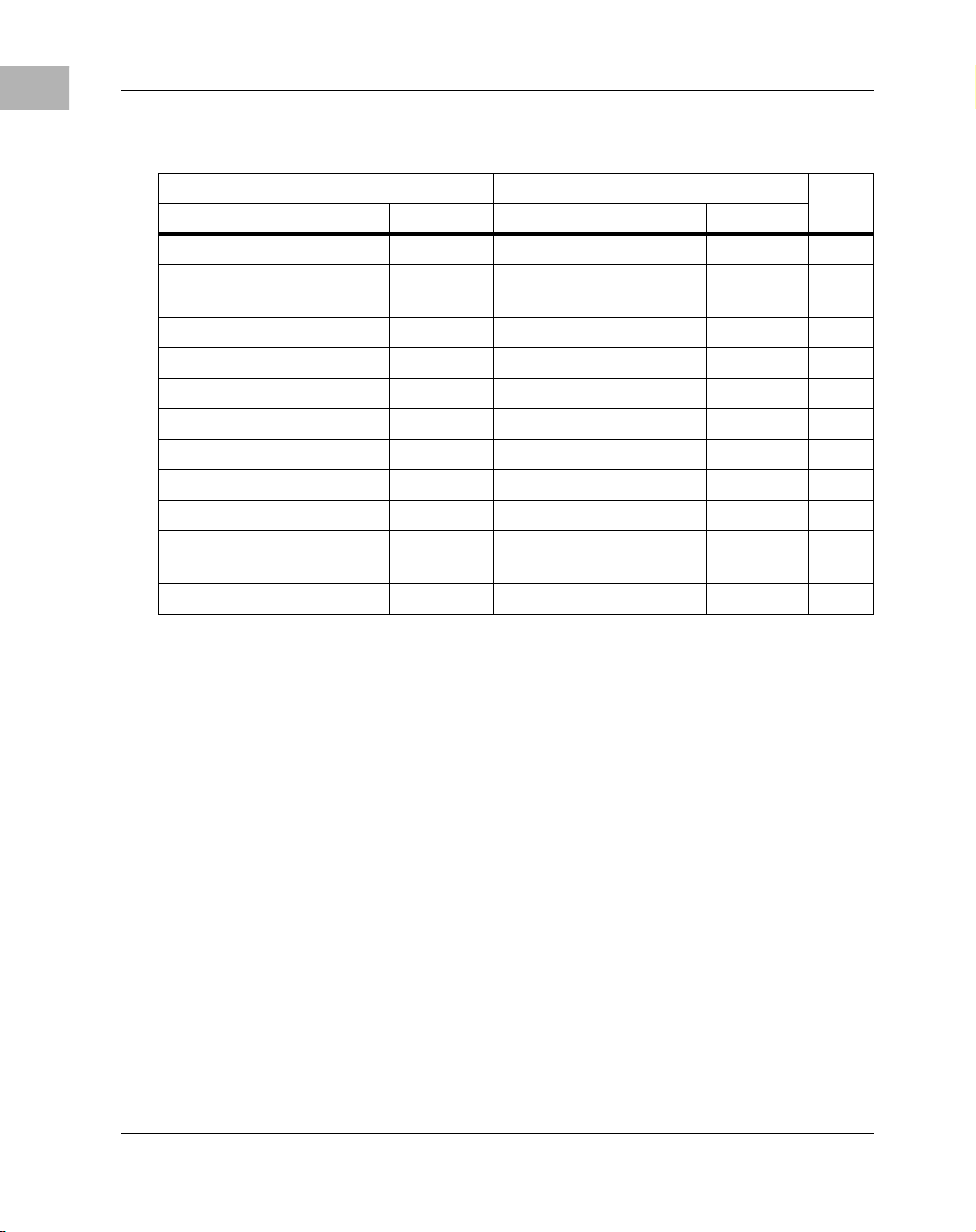

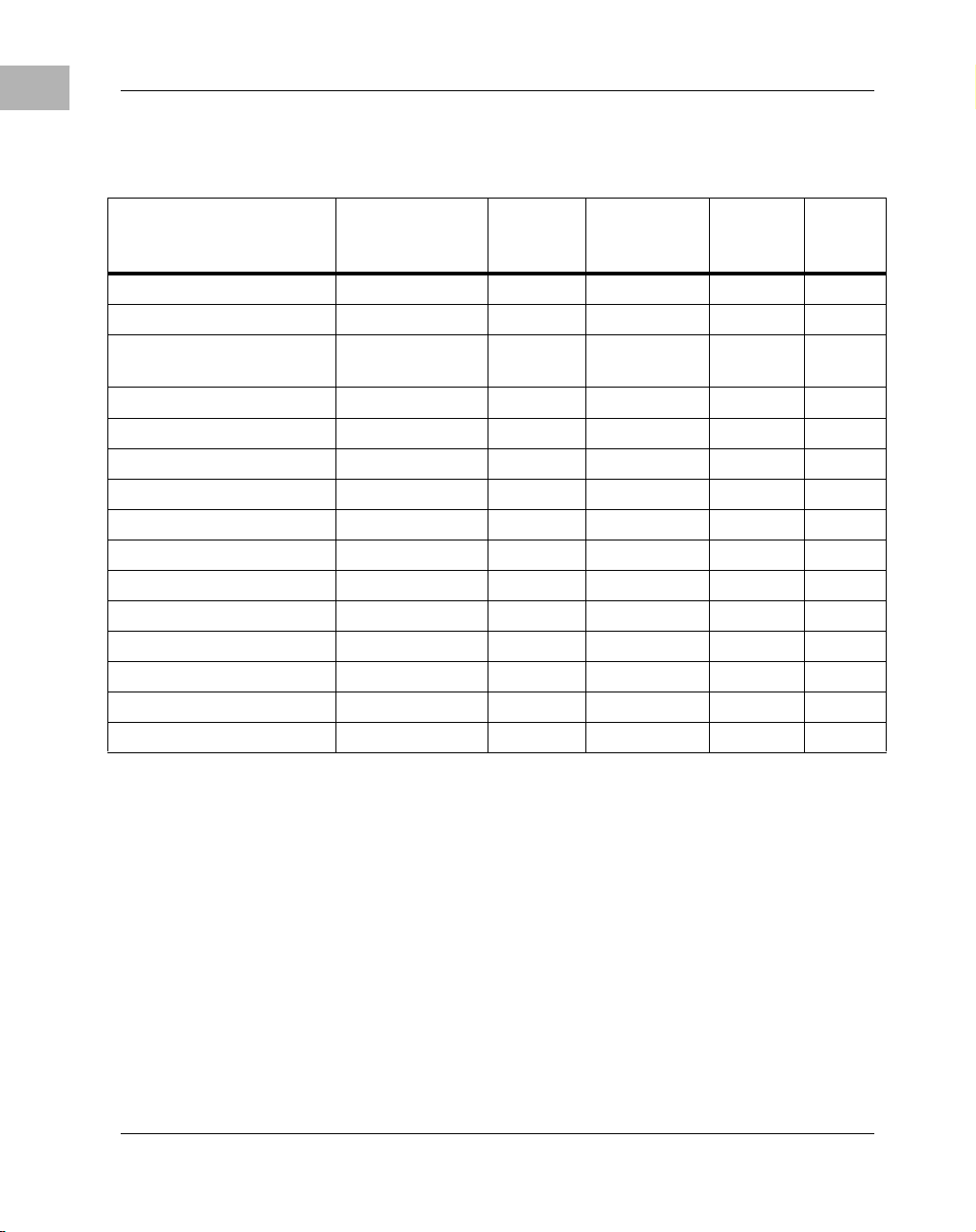

Table 1-2. Redundant Functions in the VMEchip2 and MC2 Chip

VMEchip2 MC2 Chip

Address Bit # Address Bit #

$FFF40060 28 - 24 $FFF42044 28 - 24 1,5

$FFF40060 22 -

19,17,16

$FFF4004C 13 - 8 $FFF42044 13 - 8 3,5

$FFF40048 7 $FFF42048 8 4

$FFF40048 9 $FFF42048 9 4,5

$FFF40048 10 $FFF42048 10 4,5

$FFF40048 11 $FFF42048 11 4,5

$FFF40064 31 - 0 $FFF4204C 31 - 0 8

$FF800000-$FFBFFFFF 31 - 0 $FF800000-

$FFE00000-$FFEFFFFF 31 - 0 Programmable 31 - 0 7

$FFF42044 22 -

19,17,16

$FFF42040 6 - 0 6

31 - 0 7

$FFBFFFFF

Notes

2,5

Notes 1. RESET switch control.

2. Watchdog ti mer control.

3. Access and watchdog timer parameters.

4. MPU TEA (bus error) status

5. Bit numbering for VMEchip2 and MC2 chip has a one-toone correspondence.

ABORT switch interrupt control. Implemented also in the

6.

VMEchip2, but with a di ffer ent bit organi zati on (r efer to the

VMEchip2 description i n Ch apt er 2) . I n the MVME172, the

ABORT switch is wired to the MC2 chip, not the VMEchip2.

7. The SRAM and PROM decoder in the VMEchip2 (versi on

2) must be disabled by software before any accesses are made

to these address spaces.

8. 32-bit prescaler. The prescaler can also be accessed at

$FFF40064 when the optional VMEbus is not enabled.

1-8 Computer Group Literature Center Web Site

Page 27

VMEbus Interface and VMEchip2

The local bus to VMEb us interf ace an d the VMEbus to local b us interf ace

are provided by the VMEchip2. The VMEchip2 can also provide the

VMEbus system controller functions. Refe r to the VMEchip2 i n Chapter 2

for detailed programming information.

Memory Maps

1

Note that the

inputs to the VMEchip2 which are located at $FFF40088 bits 7-0 are not

used. The

MC2 chip ASIC at locatio n $FFF42043. The GPI i nputs are integrate d into

the MC2 chip ASIC at location $FFF4202C bits 23-16.

ABORT switch logic in the VMEchip2 is not used. The GPI

ABORT switch interrupt is integrated into the

Memory Maps

There are two points of view for memory maps: 1) the mapping of all

resources as viewed by local bus maste rs (lo cal bus memor y map), and 2)

the mapping of onboard resources as viewed by VMEbus masters

(VMEbus memory map).

The memory and I/O maps wh ich are describe d in the followi ng table s are

correct for all local bus masters. There is some address translation

capability in the VMEchip2. This allo ws multiple MVME172 modules on

the same VMEbus with different virtual local bus maps as viewed by

different VMEbus masters.

Local Bus Memory Map

The local b us memory map is split into different address spaces by the

transfer type (TT) signals. The local resources respond to the normal

access and interrupt acknowledge codes.

Normal Address Range

The memory map of devices that respond to the normal address range is

shown in the following tables. The normal address range is defined by the

Transfer Type (TT) signa ls on t he l ocal bus. On the MVME172, Transfer

Types 0, 1, and 2 define the normal address range. Table 1-2 is the entire

http://www.mcg.mot.com/literature 1-9

Page 28

1

Board Description and Memory Maps

map from $00000000 to $FFFFFFFF. Many areas of the map are

user-programmable, and sugg ested uses ar e shown in the ta ble. The cache

inhibit function is programmable in the MC68xx060 MMU. The onboard

I/O space must be marked cache inhibit and serialized in its page table.

Table 1-3 on page 1-10 further defines the map for the local I/O devices

for the 200/300-Series MVME172, and Table 1-4 on page 1-12 further

defines the map for the local I/O devices for the 400/500-Series

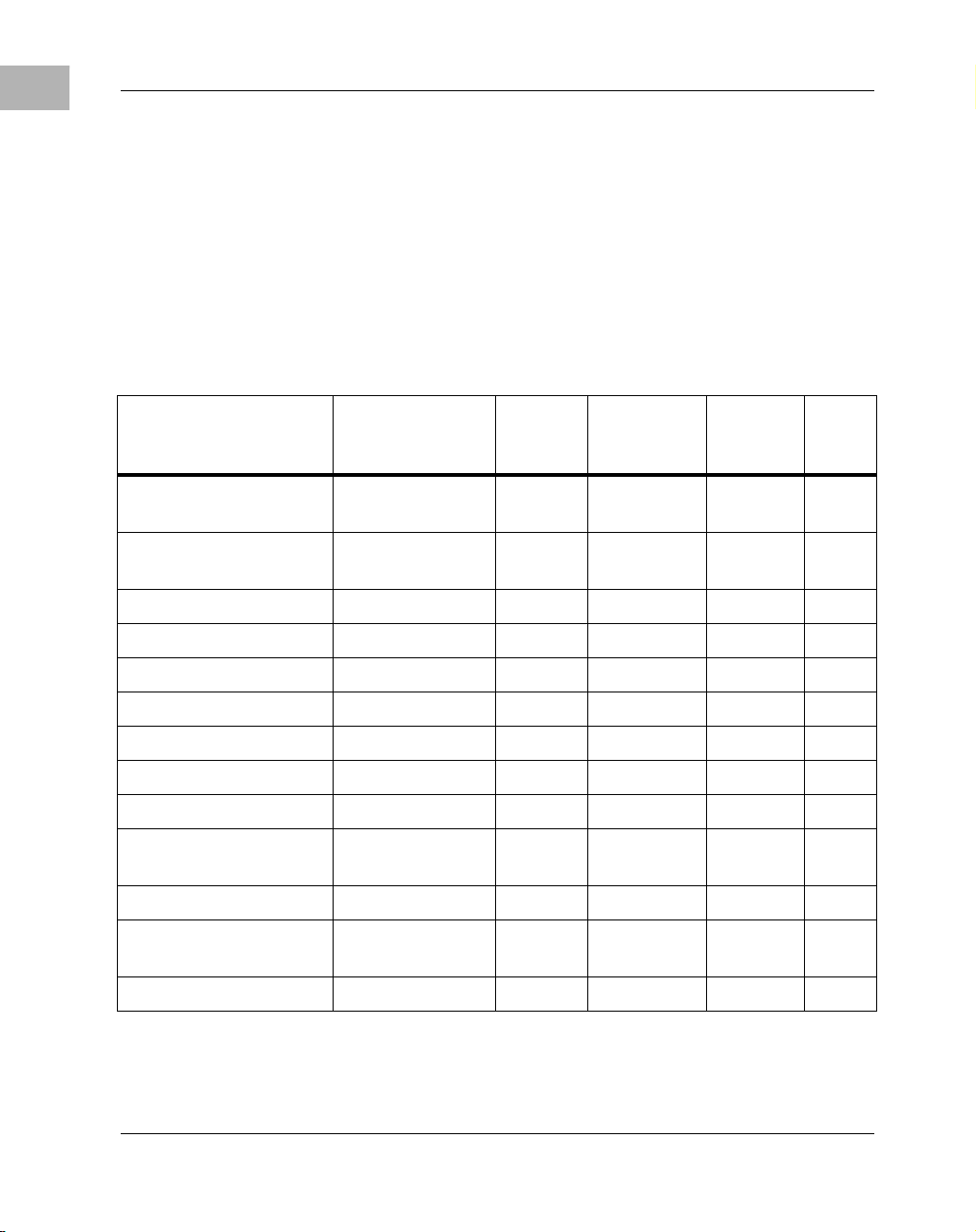

Table 1-3. 200/300-Series MVME172 Local Bus Memory Map

MVME172.

Address Range Devices Accessed

Programmable DRAM on parity

mezzanine

Programmable DRAM on ECC

mezzanine

Programmable Onboard SRAM D32 1 28KB N 2

Programmable VMEbus A32/A24 D32-D16 -- ? 4

Programmable IP_a memory D32-D8 64KB-8MB ? 2, 4

Programmable IP_b memory D32-D8 64KB-8MB ? 2, 4

$FF800000-$FF9FFFFF Flash/EPROM D32 2MB N 1, 5

$FFA00000-$FFBFFFFF EPROM/Flash D32 2MB N 5

$FFC00000-$FFDFF F FF Not decoded D32 2MB N

$FFE00000-$FFE1FFFF Onboard

SRAM default

$FFE80000-$FFEFFFFF Not decoded -- 512KB N 6

$FFF00000-$FFFEFFFF Local I/O devices

(see next table)

Port

Width

D32 4MB-16MB N 2

D32 4MB-64MB N 2

D32 128KB N

D32-D8 878KB Y 3

Size

Software

Cache

Inhibit

Notes

$FFFF0000-$FFFFFFFF VMEbus A16 D32/D16 64KB ? 2, 4

1-10 Computer Group Literature Center Web Site

Page 29

Memory Maps

Notes 1. Devices mapped at $FFF80000-$FFF9FF FF also appear at

$00000000- $001FFFFF when the ROM0 bit in the MC2

chip EPROM control register is high (ROM0=1). ROM0 is

set to 1 after each r eset. The ROM0 bit must be clea red before

other resources (DRAM or SRAM) can be mapped in this

range ($00000000 - $001FFFFF).

The EPROM/Flash memory map is also controlled by the

EPROM size and by control bit V11 in the MC2 chip ASIC.

Refer to th e EPROM/Flash configuration tables in your

MVME172 installation manual for further details.

2. This area is user-programmable. The DRAM and SRAM

decoder is programmed in the MC2 chip, the local-toVMEbus decoders are programmed in the VMEchip2, and

the IP memory space is programmed in the IP2.

3. Size is approximate.

4. Cache inhibit depends on the devices in the area mapped.

5. The EPROM and Flash are dynamicall y sized by the MC2

chip ASIC from an 8-bi t privat e b us to the 32- bit MPU lo cal

bus.

1

6. These areas are not decoded unless one of the

programmable decoder s is in itiali zed to de code t his spac e. If

they are not decoded an d the local timer is enabled, an ac cess

to this address range will generate a local bus time-out.

http://www.mcg.mot.com/literature 1-11

Page 30

1

Board Description and Memory Maps

Table 1-4. 400/500-Series MVME172 Local Bus Memory Map

Address Range

Programmable DRAM on board D32 4MB-16 MB N 2

Programmable SRAM D32 128KB-2MB N 2

Programmable VMEbus

Programmable IP_a Memory D32-D8 64KB-8MB ? 2, 4

Programmable IP_b Memory D32-D8 64KB-8MB ? 2, 4

Programmable IP_c Memory D32-D8 64KB-8MB ? 2, 4

Programmable IP_d Memory D32-D8 64KB-8MB ? 2, 4

$FF800000 - $FF9FFFFF Flash/PROM D32 2MB N 1, 5

$FFA00000 - $FFBFFFFF PROM/Flash D32 2MB N 6

$FFC00000 - $FFCFFFFF Not decoded -- 1MB N 7

$FFD00000 - $FFDFFFFF Not decoded -- 1MB N 7

$FFE00000 - $FFE7FFFF SRAM default D32 512KB N -$FFE80000 - $FFEFFFFF Not decoded - - 512KB N 7

$FFF00000 - $FFFEFFFF Local I/O D32-D8 878KB Y 3

$FFFF0000 - $FFFFFFFF VMEbus A16 D32/D16 64KB ? 2, 4

Devices

Accessed

A32/A24

Port

Width

D32/D16 -- ? 4

Size

Software

Cache

Inhibit

Note(s)

Notes 1. Reset enables the decoder for this space of the memory

map so that it will decode address spaces

$FF800000-$FF9FFFFF and $00000000-$003FFFFF. The

decode at 0 must be disabled in the MC2 chip befor e DRAM

is enabled. DRAM is enabled with the DRAM Control

1-12 Computer Group Literature Center Web Site

Page 31

Memory Maps

Register at address $FFF42048, bit 24. PROM/Flash is

disabled at the low address space with PROM Control

Register at address $FFF42040, bit 20.

2. This area is user-programmable. The DRAM and SRAM

decoder is programmed in the MC2 chip, the

local-to-VMEbus decoders are programmed in the

VMEchip2, and the IP memory space is programmed in the

IP2 chip.

3. Size is approximate.

4. Cache inhibit depends on devices in area mapped.

5. The PROM and Flash are sized by the MC2 chip ASIC

from an 8-bit private bus to the 32-bit MPU local bus.

Because the device size is less than the allocated memory

map size for some entries, the device c ontents repeat for

those entries.

If jumper GPI3 is installed, the Flash device is accessed. If

GPI3 is not installed, the PROM is accessed.

1

6. The Flash and PROM are sized by the MC2 chip ASIC

from an 8-bit private bus to the 32-bit MPU local bus.

Because the device size is less than the allocated memory

map size for some entries, the device c ontents repeat for

those entries.

If jumper GPI3 is inst alled, the PROM is accessed. If GPI3 i s

not installed, the Flash device is accessed.

7. These areas are not decoded unless one of the

programmable decoders are initialized to decode this space.

If they are not decoded, an access to this address range will

generate a local bus time-o ut. The local bus timer must be

enabled.

http://www.mcg.mot.com/literature 1-13

Page 32

1

Board Description and Memory Maps

Table 1-5 below and Table 1-6 on page 1-18 describe the "Local I/O

Devices" portion of t he local bus main memory map fo r the 200/300-Series

and 400/500-Series MVME172, respectively.

Table 1-5. 200/300-Series MVME172 Local I/O Devices Memory Map

Address Range Devices Accessed Port

Width

$FFF00000 - $FFF3FFFF Reserved - - 256K

$FFF40000 - $FFF400FF V MEchip2 (LCSR) D32 256B 1, 3

$FFF40100 - $FFF401FF VMEchip2 (GCSR) D32-D8 256B 1, 3

$FFF40200 - $FFF40FFF Reserved - - 3.5KB 4, 5

$FFF41000 - $FFF41FFF Reserved - - 4KB 4

$FFF42000 - $FFF42FFF MC2 chip D32-D8 4KB 1

$FFF43000 - $FFF430FF MCECC #1 D8 256B 1, 8

$FFF43100 - $FFF431FF MCECC #2 D8 256B 1, 8

$FFF43200 - $FFF43FFF MCECCs (repeated) - - 3.5KB 1, 5, 8

$FFF44000 - $FFF44FFF Reserved - - 8KB 4

$FFF45000 - $FFF45800 SCC #1 (Z85230) D8 2KB 1, 2

$FFF45801 - $FFF45FFF SCC #2 (Z85230) D8 2KB 1, 2

$FFF46000 - $FFF46FFF LAN (82596CA) D32 4KB 1, 6

$FFF47000 - $FFF47FFF SCSI (53C710) D32-D8 4KB 1

Size Notes

4

B

$FFF48000 - $FFF57FFF Reserved - - 64KB 4

$FFF58000 - $FFF5807F IP2 IP_a I/O D16 128B 1

$FFF58080 - $FFF580FF IP2 IP_a ID D16 128B 1

$FFF58100 - $FFF5817F IP2 IP_b I/O D16 128B 1

$FFF58180 - $FFF581FF IP2 IP_b ID Read D16 128B 1

$FFF58200 - $FFF5827F IP2 IP_c I/O D16 128B 7

1-14 Computer Group Literature Center Web Site

Page 33

Memory Maps

Table 1-5. 200/300-Series MVME172 Local I/O Devices Memory Map

(Continued)

1

Address Range Devices Accessed Port

Width

$FFF58280 - $FFF582FF IP2 IP_c ID D16 128B 7

$FFF58300 - $FFF5837F IP2 IP_d I/O D16 128B 7

$FFF58380 - $FFF583FF IP2 IP_d ID Read D16 128B 7

$FFF58400 - $FFF584FF IP2 IP_ab I/O D32-D16 256B 1

$FFF58500 - $FFF585FF IP2 IP_cd I/O D32-D16 256B 7

$FFF58600 - $FFF586FF IP2 IP_ab I/O Repeated D32-D16 256B 1

$FFF58700 - $FFF587FF IP2 IP_cd I/O Repeated D32-D16 256B 7

$FFF58800 - $FFF5887F Reserve d - - 128B 1

$FFF58880 - $FFF588FF Reserved - - 128B 1

$FFF58900 - $FFF5897F Reserve d - - 128B 1

$FFF58980 - $FFF589FF Reserved - - 128B 1

$FFF58A00 - $FFF58A7F Reserved - - 128B 1

$FFF58A80 - $FFF58AFF Reserved - - 128B 1

$FFF58B00 - $FFF58B7F Reserved - - 128B 1

$FFF58B80 - $FFF58BFF Reserved - - 128B 1

Size Notes

$FFF58C00 - $FFF58CFF Reserved - - 256B 1

$FFF58D00 - $FFF58DFF Reserved - - 256B 1

$FFF58E00 - $ FFF58EFF Reserved - - 256B 1

$FFF58F00 - $FFF58FFF Reserved - - 256B 1

$FFFBC000 - $FFFBC01F IP2 Registers D32-D8 2KB 1

http://www.mcg.mot.com/literature 1-15

Page 34

1

Board Description and Memory Maps

Table 1-5. 200/300-Series MVME172 Local I/O Devices Memory Map

(Continued)

Address Range Devices Accessed Port

Width

$FFFBC800 - $FFFBC81F Reserved - - 2KB 1

$FFFBD000 - $FFFBFFFF Reserved - - 12KB 4

$FFFC0000 - $FFFCFFFF M48T58 (BBRAM, TOD Clock) D32-D8 64KB 1, 9

$FFFD0000 - $FFFEFFFF Reserved - - 128K

Size Notes

4

B

1-16 Computer Group Literature Center Web Site

Page 35

Memory Maps

Notes 1. For a complete description of the regist er bits , refe r to the

data sheet for th e specific chip. For a m ore detailed memory

map, refer to the following detailed peripheral device

memory maps.

2. The SCC is an 8-bit device located on an MC2 chip pr ivate

data bus. Byte access is required.

3. Writes to the LCSR in the VMEchip2 must be 32 bits.

LCSR writes of 8 or 16 bits terminate with a TEA signal.

Writes to the GCSR may be 8, 16 or 32 bits. Reads to the

LCSR and GCSR may be 8, 16 or 32 bits. Byte reads should

be used to r ead the interrupt vector.

4. This area does not return an acknowledge signal. If the

local bus timer is enabled, the access times out and is

terminated by a TEA signal.

5. Size is approximate.

6. Port commands to the 82596CA must be writt en as two 16bit writes: upper word first and lower word second.

1

7. Not used.

8. To use this area, the ECC mezzanine board must be

installed. If it is not installed, no acknowledge signal is

returned; if the local bus timer is enabled, the access times

out and is terminated by a TEA signal.

9.Repeats on 8KB boundaries.

http://www.mcg.mot.com/literature 1-17

Page 36

1

Board Description and Memory Maps

Table 1-6. 400/500-Series MVME172 Local I/O Devices Memory Map

Address Range Device

Port

Width

Size Note(s)

$FFF00000 - $FFF3FFFF Reserved -- 256KB 4

$FFF40000 - $FFF400FF V MEchip2 (LCSR) D32 256B 1, 3

$FFF40100 - $FFF401FF V MEchip2 (GCSR) registers D32-D8 256B 1, 3

$FFF40200 - $FFF40FFF Reserved -- 3.5KB 4, 5

$FFF41000 - $FFF41FFF Reserved -- 4KB 4

$FFF42000 - $FFF42FFF MC2 chip D32-D8 4KB 1

$FFF43000 - $FFF44FFF Reserved -- 8KB 4

$FFF45000 - $FFF45FFF SCC (Z85230) D8 4KB 1, 2

$FFF46000 - $FFF46FFF LAN (82596CA) D32 4KB 1, 6

$FFF47000 - $FFF47FFF SCSI (53C710) D32-D8 4KB 1

$FFF48000 - $FFF57FFF Reserved -- 64KB 4

$FFF58000 - $FFF5807F IP2 chip IP_a I/O D16 128B 1

$FFF58080 - $FFF580FF IP2 chip IP_a ID D16 128B 1

$FFF58100 - $FFF5817F IP2 chip IP_b I/O D16 128B 1

$FFF58180 - $FFF581FF IP2 chip IP_b ID Read D16 128B 1

$FFF58200 - $FFF5827F IP2 chip IP_c I/O D16 128B 1

$FFF58280 - $FFF582FF IP2 chip IP_c ID D16 128B 1

$FFF58300 - $FFF5837F IP2 chip IP_d I/O D16 128B 1

$FFF58380 - $FFF583FF IP2 chip IP_d ID Read D16 128B 1

$FFF58400 - $FFF584FF IP2 chip IP_ab I/O D32-D16 256B 1

$FFF58500 - $FFF585FF IP2 chip IP_cd I/O D32-D16 256B 1

$FFF58600 - $FFF586FF IP2 chip IP_ab I/O repeated D32-D16 256B 1

$FFF58700 - $FFF587FF IP2 chip IP_cd I/O repeated D32-D16 256B 1

$FFF58800 - $FFF5887F Reserved -- 128B 1

$FFF58880 - $FFF588FF Reserved -- 128B 1

$FFF58900 - $FFF5897F Reserved -- 128B 1

1-18 Computer Group Literature Center Web Site

Page 37

Memory Maps

Table 1-6. 400/500-Series MVME172 Local I/O Devices Memory Map

(Continued)

1

Address Range Device

$FFF58980 - $FFF589FF Reserved -- 128B 1

$FFF58A00 - $FFF58A7F Reserved -- 128B 1

$FFF58A80 - $FFF58AFF Reserved -- 128B 1

$FFF58B00 - $FFF58B7F Reserved -- 128B 1

$FFF58B80 - $FFF58BFF Reserved -- 128B 1

$FFF58C00 - $FFF58CFF Reserved -- 256B 1

$FFF58D00 - $FFF58DFF Reserved -- 256B 1

$FFF58E00 - $FFF58EFF Reserved -- 256B 1

$FFF58F00 - $FFF58FFF Reserved -- 256B 1

$FFFBC000 - $FFFBC01F IP2 chip registers D32-D8 2KB 1

$FFFBC800 - $FFFBC81F Reserved -- 2KB 1

$FFFBD000 -

$FFFBFFFF

$FFFC0000 - $FFFC7FFF MK48T58

$FFFC8000 - $FFFCBFFF MK48T58 D32-D8 16KB 1, 7

$FFFCC000 - $FFFCFFFF MK48T58 D32-D8 16KB 1, 7

$FFFD0000 - $FFFEFFFF Reserved -- 128KB 4

Reserved -- 12KB 4

(BBRAM, TOD clock)

Port

Width

D32-D8 32KB 1

Size Note(s)

http://www.mcg.mot.com/literature 1-19

Page 38

1

Board Description and Memory Maps

Notes 1. For a complete description of the regist er bits , refe r to the

data sheet for th e specific chip. For a m ore detailed memory

map, refer to the following detailed peripheral device

memory maps.

2. The SCC is an 8-bit device located on an MC2 chip pr ivate

data bus. Byte access is required.

The data register of the Zilog Z85230 device which is

interfaced by the MC2 chip ASIC cannot be accessed. The

Zilog Z85230 has an indirect access mode to the data

registers which is functional and must be used.

3. Writes to the LCSR in the VMEchip2 must be 32 bits.

LCSR writes of 8 or 16 bits terminate with a TEA signal.

Writes to the GCSR may be 8, 16 or 32 bits. Reads to the

LCSR and GCSR may be 8, 16 or 32 bits. Byte reads should

be used to r ead the interrupt vector.

4. This area does not return an acknowledge signal. If the

local bus timer is enabled, the access times out and is

terminated by a TEA signal.

5. Size is approximate.

6. Port commands to the 82596CA must be written as two

16-bit writes: upper word first and lower word second.

7. Refer to the Fl ash and PROM Interf ace section in t he MC2

chip description in Chapter 3.

1-20 Computer Group Literature Center Web Site

Page 39

Detailed I/O Memory Maps

Tables 1-7 through 1-17 give the detailed memory maps for:

VMEchip2 Table 1-7

MC2 chip Table 1-8

IP2 chip Table 1-9

IP2 chip Control and Status Register s Table 1-10

MCECC chip Table 1-11

Z85230 SCC Register addresses Table 1-12

82596CA Ethernet LAN chip Table 1-13

53C710 SCSI chip Table 1-14

MK48T58 BBRAM/TOD clock Table 1-15

BBRAM configuration area Table 1-16

TOD clock Table 1-17

Memory Maps

1

Note Manufacturers’ errata sheets for the various chips are

available by contacting your local Motorola sales

representative. A no n-disclo sure agr eement may be require d.

http://www.mcg.mot.com/literature 1-21

Page 40

1

Board Description and Memory Maps

Table 1-7. VMEchip2 Memory Map (Sheet 1 of 3)

VMEchip2 LCSR Base Address = $FFF40000

OFFSET:

16171819202122232425262728293031

0

SLAVE ENDING ADDRESS 1

10

14

18

1C

20

24

28

2C

30

34

38

4

8

C

ADDER

2

SLAVE ENDING ADDRESS 2

SLAVE ADDRESS TRANSLATION ADDRESS 1

SLAVE ADDRESS TRANSLATION ADDRESS 2

SNP

WP2SUP2USR2A322A24

2

BLK

BLK2PRGM2DATA

D64

2

2

2

16171819202122232425262728293031

MASTER ENDING ADDRESS 1

MASTER ENDING ADDRESS 2

MASTER ENDING ADDRESS 3

MASTER ENDING ADDRESS 4