Page 1

Artisan Technology Group is your source for quality

new and certied-used/pre-owned equipment

• FAST SHIPPING AND

DELIVERY

• TENS OF THOUSANDS OF

IN-STOCK ITEMS

• EQUIPMENT DEMOS

• HUNDREDS OF

MANUFACTURERS

SUPPORTED

• LEASING/MONTHLY

RENTALS

• ITAR CERTIFIED

SECURE ASSET SOLUTIONS

SERVICE CENTER REPAIRS

Experienced engineers and technicians on staff

at our full-service, in-house repair center

Instra

Remotely inspect equipment before purchasing with

our interactive website at www.instraview.com

Contact us: (888) 88-SOURCE | sales@artisantg.com | www.artisantg.com

SM

REMOTE INSPECTION

View

WE BUY USED EQUIPMENT

Sell your excess, underutilized, and idle used equipment

We also offer credit for buy-backs and trade-ins

www.artisantg.com/WeBuyEquipment

LOOKING FOR MORE INFORMATION?

Visit us on the web at www.artisantg.com for more

information on price quotations, drivers, technical

specications, manuals, and documentation

Page 2

®MOTOFlOLA

MVME120/D2

MVME120, MVME121, MVME122, MVME123

VMEbus

Microprocessor

User's

Manual

Module

ICR

QUALITY • PEOPLE • PERFORMANCE

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 3

(f!jMOTOROLA

MVME120jD2

MVMEI20,

VMEbus

MVMEI21,

MICROPROCESSOR

USER'S

The

information in

be

entirely

Furthermore, Motorola reserves the

herein to

any

described herein;

or the

VERSAdos

liability

improve

rights

is

reliable.

of

a trademark of Motorola Inc.

this

reliability,

arising

neither

others.

document

However,

out of the

no

function, or design. Motorola does not

does

has

responsibility

application

it

MVMEI22,

MANUAL

been

right

convey

MVME123

MODULE

carefully

to

make

or

use

any

license

checked

is

assumed

of

and

changes

any

product or

under

JUNE

is

believed to

for

inaccuracies.

to

any

its

patent

1985

products

assume

circuit

rights

THIS

FREQUENCY

ACCORDANCE

INTERFERENCE

AND

COMPUTING

RULES,

AGAINST

ENVIRONMENT.

AREA

USER,

WHATEVER

EQUIPMENT

ENERGY

WITH

TO

FOUND

TO

DEVICE

WHICH

ARE

SUCH

INTERFERENCE

OPERATION

IS

LIKELY

AT

HIS

MEASURES

Copyright

First

WARNING

GENERATES,

AND

THE

RADIO

COMPLY

IF

INSTRUCTIONS

COMMUNICATIONS.

WITH

PURSUANT

DESIGNED

TO

OWN

TO

OF

THIS

CAUSE

EXPENSE,

NECESSARY

Second

1985

Edition September

USES,

NOT

AND

CAN

INSTALLED

MANUAL,

IT

HAS

THE

TO

PROVIDE

WHEN

INTERFERENCE

TO

Edition

by

LIMITS

SUBPART J OF

REASONABLE

OPERATED

EQUIPMENT

IN A RESIDENTIAL

IN

WILL

CORRECT

Motorola Inc.

BE

REQUIRED

THE

1984

FOR A CLASS

IN A COMMERCIAL

INTERFERENCE.

RADIATE

AND

MAY

BEEN

PART

RADIO

USED

CAUSE

TESTED

15

OF

PROTECTION

WHICH

CASE

TO

IN

A

FCC

THE

TAKE

MICROSYSTEMS

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 4

SAFETY

SUMMARY

The

following

repair

of

in this

Motorola

safety precautions listed

the user

the safe operation

manual

GROUND

To

minimize

ground.

be

plugged

adapter,

power

Commission

DO

Do

equipment

NOT

not

outlet.

operate

KEEP AWAY

Operating

other

qualified

component

connected.

To

avoid

general

this equipment. Failure to

violates safety standards

Inc. assumes no liability for the customer's failure to

of

the product, should follow these warnings

THE

INSTRUMENT.

shock

The

equipment

into

with

the

The

(IEC)

safety precautions must be observed

of

the

hazard,

an

approved

grounding

power

safety

OPERATE IN AN EXPLOSIVE

the

equipment

in

such

an

environment

FROM

personnel

replacement

Under

injuries,

LIVE

must

maintenance

certai n conditions,

always

SAFETY

below

equipment

is

jack

represent warnings

the

equipment

supplied

th

ree-contact

wire

and

standards.

in

CIRCUITS.

not

remove

personnel

or

any

disconnect

DEPENDS

comply

in

with a three-conductor

(green)

mating

the

presence

constitutes a definite

internal

with these

of

design, manufacture,

your

operating environment.

chassis

electrical

firmly

connected

plug

of

the

ATMOSPHERE.

of

flammable

equipment

may

adjustment.

dangerous

power

remove

and

covers.

voltages

discharge

ON

during

precautions

of

certain dangers

and

all

other

and

enclosure

ac

power

outlet

or

used

to

an

electrical

power

cable

gases

safety

Only

Factory

equipment

Do

not

replace

may

exist

circuits

YOU

all phases

or

with specific warnings elsewhere

and

intended use

comply

safety precautions necessary for

must

cable.

with a three-contact

meet

or

fumes.

hazard.

Authorized

covers

even

before

of

operation, service,

of

the equipment.

with these requirements. The

of

which we are aware. You, as

be

connected

The

power

ground

International

Operation

for

internal

components

with

the

power

touching

to

an

cable

to

two-contact

(safety

Service

ground)

Electrotechnical

of

any

Personnel

subassembly

with

power

cable

them.

electrical

must

either

at

electrical

cable

removed.

and

the

or

or

DO

NOT

SERVICE OR

Do

not

attempt

resuscitation,

USE

CAUTION

Breakage

sion).

CRT

DO

Because

unauthorized

service

of

To

prevent

should

NOT

SUBSTITUTE

of

and

the

be

the

repair

DANGEROUS

Warnings,

manual.

safety

environment.

such

Instructions

precautions

Dangerous

caution when handling, testing, and adjusting.

ADJUST

internal

is present.

WHEN

Cathode-Ray

done

EXPOSING

CRT

only

service

implosion,

PARTS OR

danger

modification

to

of

ensure

PROCEDURE

as

the

example

contained

which

voltages, capable of causing death, are present in this equipment. Use

ALONE.

or

adjustment

OR

Tube

avoid

by

qualified

introducing

of

the

equipment.

that

safety

WARNINGS.

below,

in

the

you

deem

HANDLING

(CRT)

causes a

rough

maintenance

MODIFY

additional

features

precede

warnings

necessary

unless

another

THE

high-velocity

handling

personnel

CRT.

or

EQUIPMENT.

hazards,

Contact

WARNING

Motorola

are

maintained.

potentially

must

be

for

the

operation

person,

jarring

using

do

not

install

Microsystems

dangerous

followed.

capable

scattering

of

the

approved

substitute

procedures

You

should

of

the

equipment

of

rendering

of

glass

equipment.

safety

parts

Warranty

also

first

fragments

Handling

mask

and gloves.

or

perform

and

Repair

throughout

employ

in

your

extreme

aid

and

(implo-

of

the

any

for

this

all

other

operating

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 5

®

MOTOROLA

PREFACE

Unless otherwise

this

throughout

An

asterisk

significant

An

asterisk

significant

low

to

transition.

manual.

(*)

denotes

(*)

denotes

specified,

following the signal

that

the signal

following the signal

that

the actions

all

address references are in hexadecimal

is

true

initiated

name

or valid

name

for

for

by

signals

when

signals

that

which

the signal

which

signal occur

are level

is

low.

are

edge

on

a high

MICROSYSTEMS

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 6

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 7

®

MOTOROL.A

CHAPTER

CHAPTER

1

1.1

1.2

1.3

1.4

1.5

1.

6

2

2.1

2.2

2.3

2.3.1

2.3.2

2.3.3

2.3.4

2.3.5

2.3.6

2.3.7

2.3.8

2.3.9

2.3.10

2.3.11

2.3.12

2.3.13

2.3.13.1

2.3.13.2

2.4

2.4.1

2.4.2

TABLE

GENERAL

INTRODUCTION

FEATURES

SPECIFICATIONS.......................................

GENERAL

MVME120

RELATED

HARDWARE

INTRODUCTION

UNPACKING

HARDWARE

ACFAIL*/SYSFAIL*

VMEbus

ABORT

RESET

VMEbus

ROM/EPROM

Cache

MSR

MSR

ROM

Reset Vector

Local

RAM

INSTALLATION

Module

Terminal

INFORMATION

.........................................

.............................................

DESCRIPTION

FAMILY

DOCUMENTATION

PREPARATION

.........................................

INSTRUCTIONS

PREPARATION

Request

Switch

Switch

Interrupt Connection Select

Device

Configuration Select

Bit 1

Bit 0

Access

Dual

.Factory Configured

Changi

Source

Source

Time

Time-out

Port

ng

U28

.........................................

Installation

Connection

OF

CONTENTS

....

,.............................

CONFIGURATIONS

................................

AND

....

.................................

Select

Level

Disable Select

Disable Select

Fetch

Select

Address

.....................................

Select

Configuration Select

Select

Select

Select

Header

Mode

Header

Select

RAM

................................

................................

...................

INSTALLATION

......................

Header

Header

Header

Select

Dual

(J2)

Headers

Header

Header

Headers

(J20)

(J21)

(J22)

Header

(J25)

PAL

Port

(J5)

(J6)

Header

(J9,

.................

(U28)

Base

INSTRUCTIONS

................

(J3, J4)

.......

.......

(J7)

Header

J17)

...............

...............

................

(J24)

.............

Address

.....

.....

..

.....

.....

.....

.....

(J8)

.......

........

....

..

1

1

3

4

4

4

5

5

5

7

8

9

9

10

10

14

15

16

17

17

19

19

19

21

21

21

22

CHAPTER

3

3.1

3.2

3.2.1

3.2.2

3.2.3

3.2.4

3.2.5

3.2.6

3.3

3.3.1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

OPERATING

INTRODUCTION

CONTROLS

RESET

ABORT

MODE

FAIL

HALT

RUN

MPU

MODULE

MPU

INSTRUCTIONS

.........................................

AND

INDICATORS

Swi

tch

.......................................

Swi

tch

.....................

Swi

tch

........................................

Indicator

Indicator

Indicator

MEMORYMAP

Module

Memory

.................•............

"

...

" ~ . . . . . . . . . . . . . .

.....................................

.....................................

........

..............................

................................

Map

as

Viewed

from

the

VMEbus

MICROSYSTEMS

....

23

23

23

23

23

23

24

24

25

28

Page 8

®

MOTOROLA

CHAPTER

4

4.1

4.2

4.3

4.3.1

4.3.2

4.3.3

4.3.3.1

4.3.3.2

4.3.4

4.3.4.1

4.3.4.2

4.3.4.3

4.3.5

4.3.6

4.3.7

4.3.7.1

4.3.7.2

4.3.7.3

4.3.7;4

4.3.7.5

4.3.8

4.3.9

4.3.9.1

4.3.9.2

4.3.9.3

4.3.10

4.3.11

4.3.11.1

4.3.11.2

4.3.11.3

4.3.11.4

4.3.11.5

TABLE

FUNCTIONAL

INTRODUCTION

GENERAL

BLOCK

MPU

MMU

Cache

DESCRIPTION

DIAGRAM

.................................................

.................................................

...............................................

Cache

Cache

RAM

.................•.......••.••........•..•...•...

Refresh

Local

Accesses

OF

CONTENTS

DESCRIPTION

..........................................

DESCRIPTION

Organization................................

Operat

ion

...........................................

Accesses

From

The

Multi-Port Controller

Bus

Requester

Interrupt

VMEbus

ABORT

Switch Interrupts

MC68901

Interrupt

.......................................

Handl

er

Interrupts

Interrupts

Source

Enabling Interrupts

VMEbus

I/O

Module

Module

Timers

ROM

Source

VMEbus

Onboard

Dual

MMU

Local

Interface

and

Control

Status

Control Register

............................................

.................................................

of

Bus

Error

BERR

.......................................

Parity Error

Port

Lock

Faul t .........................................

Bus

Time-out

(cont'd)

...................................

.............................

...................................

....................................

VMEbus

..........................

...............................

...................................

.~

...............................

...........................

................................

and

Vectors

......................

...............................

....................................

.....................................

...... ~ ..............................

...........................

Except

ions

......................

..............................

on

TAS

Error

.......................

......•.........................

29

29

30

30

30

31

31

33

37

38

38

38

38

39

39

39

39

40

40

41

41

42

43

44

45

46

46

46

47

47

47

47

CHAPTER

5

5.1

5.2

5.2.1

5.2.2

5.3

APPENDIX

APPENDIX

A

B

INDEX

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

SUPPORT

INTRODUCTION

INTERCONNECT

Connector

Terminal

PARTS

RS-232C

PROGRAMMABLE

INFORMATION

................•.........................

SIGNALS

PI

Interconnect Signals

..................................

Port Connector

LIST

............................................

INTERCONNECTIONS

ARRAY

LOGIC

...................

Jl

Interconnect Signals

.....

.......................................................

i i

MICROSYSTEMS

51

51

51

56

57

95

101

115

Page 9

@MOTOROLA

FIGURE

TABLE

I-I.

2-I.

4-I.

5-I.

5-2.

I-I.

3-I.

4-I.

5-I.

5-2.

5-3.

TABLE

LIST

Typical

MPU

MPU

MPU

MPU

MPU

MPU

Module

Module

Module

Module

Module

Module....................................

Option Locations

Block

Parts Location

Schematic

Specifications

Interpretation

Modul

Connector

Connector

MPU

e Status

Jl

Module

PI

Parts List

OF

CONTENTS

OF

ILLUSTRATIONS

(cont'd)

............

Diagram

..............................

.............................

LIST

Diagram

OF

TABLES

..........................

..............................

of Front

Panel

Indicators

..........................................

Interconnect Signals

Interconnect Signals

......................

......................

..................................

...............

...............

2

6

49

63

65

3

24

43

51

56

57

iii

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 10

®MOTOROLA

THIS

PAGE

INTENTIONALLY

LEFT

BLANK.

iv

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROS

YS

TEMS

Page 11

([!jMOTOROLA

GENERAL

INFORMATION

1.1

This

instructions,

information for the

Microprocessor

module

1.

The

INTRODUCTION

manual

is

2

FEATURES

features

MC68010

MC68451

4Kb

provides general information, preparation for

shown

of

MPU

MMU

logical

operating

Modules

in Figure 1-1.

the

MPU

(optional)

instruction

CHAPTER

GENERAL

instructions,

MVMEI20,

(hereinafter

module

include:

cache (optional)

1

INFORMATION

functional

MVMEI21, MVMEI22,

referred to

description,

as

MPU

module). A typical

use

and

and

installation

and

MVME123

I

support

VMEbus

MPU

Two,

Onboard

Mode

HALT

28-pin

dual-port

Interrupt

Status

Programmable

RS-232C

Bus

requester

A24,

016

Local

Local

switch

FAIL

indicator

handler

and

serial

VMEbus

RESET

software

indicator

ROM/EPROM

RAM

control

timer

switch

registers

debug

ABORT

port

interface

switch

sockets

with byte

parity

RUN

indicator

1

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 12

®MOTOROLA

GENERAL

INFORMATION

r-

n:l

U

......

I

......

2

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 13

@MOTOROLA

1.3

SPECIFICATIONS

The

MPU

module

specifications

are

identified

in Table 1-1.

GENERAL

INFORMATION

I

TABLE

=============================================================================

CHARACTERISTICS

=============================================================================

Microprocessor

Clock

Memory

Interrupt

User

Temperature

signal

size

RAM

EPROM/ROM

handler

input/output signals

Operating

1-1.

MPU

Module

SPECIFICATIONS

MC68010

12.5

128Kb/512Kb

Two

8,

All

RS-232C

Specifications

MHz

(or 10.0

sockets for user supplied

16K

x 8,

onboard plus seven

serial

o degrees C to

required)

32K

MHz)

x 8, or

debug

50

degrees C (forced

64K

VMEbus

port (terminal only)

4K

x 8,

x 8 devices

interrupts

air

8K

x

is

Storage

Relative humidity

Physical

Width

Thickness

Power

=============================================================================

characteristics

x height

requirements

-40

degrees

0%

to

90%

7.40 in.

o .

83

in. (

+5

Vdc

120

121

122

123

-12

Vdc @ 12

+12

Vdc @ 17

to

85

degrees C

(noncondensing)

(188

mm)

x 10.20 in.

21

mm)

typical

4.2 A

4.0 A

3.2 A

4.3 A

current

rnA

(typical),

rnA

(typical),

(261

maximum

4.65 A

4.45 A

3.55 A

4.65 A

14

rnA

(maximum)

20

rnA

(maximum)

mm)

current

3

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 14

I

®MOTOROLA

1.4

GENERAL

The

offers

private

via the

system requirements ranging

MPU,

a solution for

applications.

instruction

(such

applications to

1.5

as

MVME120

DESCRIPTION

module

cache, a

ROM,

VMEbus.

the

FAMILY

is

The

and

MVME050

complex

a

high

high

module

serial

a large

The

CONFIGURATIONS

dynamic

MPU

system

multiprocessor system

performance,

speed data processing,

contains

debug

module,

controller

from

an

terminal

dual port

when

simple, high speed single processor

VMEbus,

MC68010

RAM

used

or the

architectures.

GENERAL

microprocessor

management,

MPU,

port,

that

with a system

MVMEIIO

MC68451

programmable

may

be

CPU

INFORMATION

module

and

MMU,

tick

loaded

controller

module),

that

control

logical

timer,

externally

module

satisfies

Four

Modules.

1.6

The

shipped with

Distribution

(602)

==============================================================================

=============================================================================

configurations are available for the

The

configurations are

MVME120

MVME121

MVMEl22

MVMEl23

RELATED

following publications

994-6561.

DOCUMENT

10

MHz

10

MHz

12.5

12.5

The

DOCUMENTATION

this

Center,

TITLE

MC68010,

MC68010,

MHz

MC68010,

MHz

MC68010,

MC68451

product, they

MMU

may

616

listed

128K

512K

128K

512K

does

provide additional helpful information.

West

24th

MVME120

below:

dynamic

dynamic

dynamic

dynamic

not function

may

RAM,

RAM,

be

Street,

obtained

cache,

cache,

RAM,

RAM,

at

Tempe,

Family

no

cache,

cache,

12.5

from

Arizona

of Microprocessor

MMU

MMU

no

MMU

no

MMU

MHz.

Motorola Literature

85282;

MOTOROLA

PUBLICATION

If

not

telephone

NUMBER

Data

MVMEbus

=============================================================================

Book

Specification

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Manual

4

MC68901

MVMEBS

MICROSYSTEMS

Page 15

@MOTOROLA

HARDWARE

PREPARATION

HARDWARE

2.1

This chapter provides unpacking

2.2

Unpack

all

equipment.

INTRODUCTION

installation

UNPACKING

equipment

items are present.

instructions

INSTRUCTIONS

If

the shipping carton

request

unpacking

PREPARATION

for the

carrier's

and

inspection of equipment.

from

shipping carton. Refer to packing

Save

packing material for storing

CHAPTER

AND

instructions,

MPU

agent

2

INSTALLATION

module.

is

damaged

be

INSTRUCTIONS

hardware preparation,

upon

present during

receipt,

list

and

and

and

verify

reshipping of

that

I

2.3

For

be

degrees centigrade.

To

module,

modifications are

headers. Figure

the

factory-installed

The

necessary to

HARDWARE

reliable

enough

select

MPU

MPU

cond

it

ions:

ACFAIL*/SYSFAIL*

a.

b.

VMEbus

c.

ABORT

d.

PREPARATION

operation, forced

to maintain the temperature

the desired configuration

certain

2-1

module.

module

make

request level

switch disable

RESET

switch disable

air

cooling should

at

modifications

made

The

jumper configurations

is

through

illustrates

MPU

module

operational with the

changes in the

select

select

select

select

may

jumper

the location of the headers

has

(J2)

(J3,J4)

(J5)

(J6)

be

used.

the

back

and

ensure proper operation of the

be

made

or wire-wrap arrangements

been

factory

that

jumper

of the

before

tested

are also

factory-installed

arrangements for the following

The

MC68010

installation.

and

and

is

shown

jumpers.

cooling should

case

below

connectors

shipped with

in Figure 2-1.

MPU

These

on

the

It

80

on

is

5

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 16

..

P1

zO

J4

Z

"0"

280

1

12

11

00

00

00

J3

J2

5 1

Igg

6 2

z)

88

2

001

10-00)

3

1

J25

J7

~

160015

"~"

0-0

0-0

0-0

20-01

~

0-0

0-0

0-0

~z

00

2

0-01

J20

~~

J21

00

8~~7

00

2

001

J22

@

!

0

a

~

~

3 1

J910

0-0)

~3

LQJ1

J17

FIGURE

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

2-1.

MPU

Module

Option locations

J1

Page 17

@MOTOROLA

e.

VMEbus

f.

ROM/EPROM

g.

Cache

interrupt

device configuration

configuration

connection

select

select

select

(J9, Jl7)

(J7)

(J8)

HARDWARE

PREPARATION

h.

SWI

source

i.

SW2

source

j.

ROM

access time

k.

Reset vector fetch

1.

Local

2.3.1

Bit 7

the Alternating Current Failure

the

the jumper

monitored

ACFAIL*/SYSFAIl*

of

System

time-out

the

Failure

when

select

select

Module

(SYSFAIL*)

is

positioned

the

jumper

+-----------+

I 0

+-----------+

321

(J20)

(J21)

select

select

Select

Status Register

J2

0---0

(J22)

mode

select

(J25)

Header

signal

between

is

positioned

I

(J24)

(J2)

(MSR)

(ACFAIL*)

on

can

the

pins 1

between

be

configured to monitor

signal

VMEbus.

on

and 2 on

pins 2

+-----------+

+-----------+

the

ACFAIL*

header J2.

and

J2

0---0

I

3 2 1

VMEbus

is

monitored

3.

0 I

either

or to monitor

when

SYSFAIL*

is

I

ACFAIL*

7

SYSFAIL*

MICROSYSTEMS

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Page 18

®MOTOROLA

HARDWARE

PREPARATION

I

2.3.2

The

four

J3

and

12

10

12

10

VMEbus

MPU

8 0

module

levels.

J4 as

J4

+-------+

0

0

6 0

I I

4 0

2 0

+-------+

J3

+-------+

I 0

I

I 0

I

8

I 0

I

6

I 0

I I

4

I 0

I

2

I 0

+-------+

Request

can

The

desired level

shown

o

III

below:

12

I

9

o I

10

I

7 8

o I

I

5 6

o I

I I I

3

o I

I

1

o I

9

12

10

o

III

I

I

o I

I

7 8

o I

I I

5 6

o I

I

3 4

o I

I

I

1

o I

Level

be

Select

configured

J4

+-------+

I 0

I

I 0 o I

I

I 0

I

I 0

4

I 0

I

2

I 0

+-------+

J3

+-------+

I 0 o

I I

I 0 o I

I

I 0

I I

I 0

I I

I 0

I

I

2

I 0

+-------+

Headers (J3, J4)

to

request

is

selected

+-------+

o

III

12

I 0 o

I I I

9

10

I 0

o I

I

7 8

I I

I 0 o I

I I

5 6

o I

I 0

I I I I

3 4

o I

I 0 o I

I I

1 2

o I

III

I 0

+-------+

+-------+

12

I 0

I I

9

10

I 0

I

o I

7 8

I I

I 0

I I

5 6

o I

o I

o I

I

3

I

1 2

I 0 o I

I

4

I 0 o I

I I

I 0

+-------+

VMEbus

by

jumper configuration

J4

III

mastership

+-------+

12

I 0

I I I

9

o I

10

I 0

I I

7 8

I 0

I I I I

o I

5

6

I 0 o I

I I

3 4

I 0

I I I I

1 2

J3

o I

o

III

I 0

+-------+

+-------+

12

I 0

I I

9

o I

10

I 0 o I

I I

7 8

o I

I 0

I I

I

5 6

I

I I I I I

3

4

I 0

I 0

I I

1 2

o I

I 0

+-------+

J4

J3

on

o

III

I

o I

o I

I

I I

o I

I

o I

o

III

o I

o I

o I

o I

anyone

on

9

7

5

3

1

I

9

7

I

5

3

1

of

headers

LEVEL

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

0

LEVEL

1

8

LEVEL

2

LEVEL

3

MICROSYSTEMS

Page 19

®

MOTOROL.A

HARDWARE

PREPARATION

2.3.3

The

switch

is

ABORT

front

Switch Disable Select

panel

is

disabled

software

when

ABORT

the

shipped with the switch enabled

J5

+---+

2 I 0 I

I I I

1 I 0 I

+---+

ABORT

SWITCH

ENABLED

2.3.4

The

disabled

module

RESET

front

is

Switch Disable Select

panel

when

RESET

the

jumper

switch

shipped with the switch enabled.

jumper

on

is

removed

Header

switch

is

as

Header

the

MPU

(JS)

on

the

removed

shown

(J6)

module

from

header J6.

MPU

from

below.

can

module

header J5.

+---+

2

101

I I

1

101

+---+

ABORT

SWITCH

DISABLED

be

disabled.

As

can

J5

shown

be

disabled.

The

The

below,

MPU

switch

the

The

module

is

MPU

2

J6

+---+

2

101

I I I

1

101

+---+

RESET

SWITCH

ENABLED

J6

+---+

2

101

I I

1 I 0 I

+---+

RESET

SWITCH

DISABLED

9

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 20

@MOTOROLA

HARDWARE

PREPARATION

I

2.3.5

Each

request to the

VMEbus

they drive the corresponding

requests level 1 to the

VMEbus

VMEbus

IRQ*

Interrupt

Interrupt

MPU.

signal

J7

Connection Select

Request

Jumpers

lines

are connected.

MPU,

+-------+ +-------+

14

0---0

I

13

IRQ7*

I I

12

0---0

I

11

IRQ6*

I I

10

0---0

I

9

IRQ5*

I

8

0---0

I

7

IRQ4*

I I

0---0

6

I

5

IRQ3*

I

0---0

4

I

3

IRQ2*

I

0---0

2

I

1

IRQl*

+-------+ +-------+

(IRQ*)

on

interrupt

IRQ2*

requests level 2 to the

Header

signal

header

14

12

10

J7

J7

request levels to the

J7

0 0

I

0 0

I

0 0 9

I

(J7)

can

be

connected

determine which,

connects the

13

11

I

8

6

I

I

0

0

0 0 5

7

I

4

0 0 3

I

I

2

0 0 1

I

MPU,

IRQ7*

IRQ6*

IRQ5*

IRQ4*

IRQ3*

IRQ2*

IRQl*

as

IRQ*

MPU

an

interrupt

if

any, of the

lines

(i.e.,

etc.).

so

IRQl*

that

CONNECTED

2.3.6

There are several types of

and

figures

When

must

into

be

ROM/EPROM

XU52.

below

inserting

be

inserted into

XU52.

used

as

Header

Even

shown

28

Device

show

devices into

below:

27

Configuration Select

J8

must

configurations of J8 for the

XU44

though

XU44

26 25

+--------+-----------------------------------------------+

I I I

I I I

I I I

+--------+-----------------------~-----------------------+

1 2 3 4 5 6 7 8 9

I I

I I

I

I

DISCONNECTED

ROM/EPROM

be

XU44

and

the device containing

and

24

PIN

PIN

devices

configured to

and

XU52,

XU52

23

ONE

ONE

are 28-pin sockets, 24-pin devices

22

21

OF

24-PIN

OF

28-PIN

Header

that

the device containing

20

(J8)

can

match

most

odd

19

18

10

11

DEVICE

DEVICE

be

used

the devices used.

commonly

data

must

17

16

12 13

in sockets

used

devices.

even

be

inserted

15

14

XU44

The

data

may

10

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 21

®

MOTOROLA

HARDWARE

PREPARATION

Header

shown

Header

shown

configuration

below:

configuration for

below:

for

4K

16

14

12

10

8K

8

6

4

2

x 8

x 8

EPROM

J8

+-------+

I 0

o

I

I 0

o

I I

0---0

I

I

0---0

I

I I

I 0 o I

I I

I 0

o I

I I I

I 0

o I

I I

I 0 o I

+-------+

EPROM

memory

115

I

113

III

I

9

I

7

5

3

1

memory

devices

devices

(AM2732,

(MCM68764,

INT2732)

MCM68766)

is

I

is

+-------+

16

I 0

I

14

I

I I I

12

I

I I I

10

I

I I

8

I

I I

6

I

I

4

I

I I

2

I

+-------+

J8

o

o

0

o

0

0

o I

0 o I

0 o I

I I

0

o I

0 o I

115

I

113

III

9

7

5

3

1

11

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 22

(f!jMOTOROLA

HARDWARE

PREPARATION

I

Header

shown

Header

shown

configuration

below:

configuration for

below:

for

8K

16

14

12

10

8

6

4

2

16K

+-------+

+-------+

x 8

x 8

I 0

EPROM

J8

o

I

0---0

I

I I

I

0---0

III

I

0---0

I

I I

I 0 o I

I I I

I 0

o I

I I

I 0 o I

I I

I

0---0

EPROM

memory

115

I

113

I

9

I

7

5

3

1

I

memory

devices

devices

(AM2764,

(AM27128,

INT2764)

INT27128)

is

is

+-------+

16

I 0

I I

14

I

I I

12

I

I I

10

I

I I

8

I 0 o I

I I I

6

I 0 o I

I I

4

I 0 o I

I

2

I

+-------+

J8

0---0

0---0

0---0

0---0

o

115

113

III

9

I

7

5

3

I

1

I

12

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 23

(f!jMOTOROLA

HARDWARE

PREPARATION

Header

below:

Header

below:

configuration for

configuration for

32K

+-------+

16

14

12

10

8

6

4

2

+-------+

64K

x 8

0 0

0---0

0---0

0---0

0---0

0 0 5

0 0 3

0---0

x 8

EPROM

J8

15

13

11

9

7

1

EPROM

memory

memory

devices

devices

(AM27256)

(AM27512)

is

is

shown

I

shown

J8

+-------+

16

0---0

115

I

14

0---0

113

I

0---0

12

111

I

0---0

10

I

9

I

0---0

8

I

7

I

6 o-X-o<---------THE

I

I

4

0 0

3'

I

2

0---0

+-------+

I 1

CIRCUIT

BACK

BE

OF

CUT

TRACK

THE

MODULE

ON

THE

MUST

13

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 24

®

MOTOROl-A

HARDWARE

PREPARATION

I

2.3.7

The

4Kb.

2Kb

what

Cache

cache

The

supervisor

mode

Configuration Select Headers (J9, J17)

can

modes

is

selected,

be

configured for

are user only, supervisor only,

and

2Kb

user.

as

shown

J9

+-----------+

0---0

I

+-----------+

3 2 1

J9

+-----------+

I

0---0

+-----------+

321

0

ALL

0 I

4KB

Jumper

below:

I

OF

one

of

position

CACHE

four

ARE

USER

modes.

mixed

on

headers

ONLY

The

user

+---+

3

I 0 I

I I

2

I 0 I

I I I

1

I

+---+

+---+

3

I 0 I

I I I

2

I 0 I

I I

1

I 0 I

+---+

cache

and

J9

J17

0

J17

has a total

supervisor,

and

J17

I

of

and

determine

ALL

J9

+-----------+

I

0---0

+-----------+

321

ALL

4KB

OF

4KB

OF

0 I

CACHE

CACHE

ARE

ARE

MIXED

SUPERVISOR

USER

AND

ONLY

SUPERVISOR

J17

+---+

3

101

I I

2

101

I I

1 I 0 I

+---+

14

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 25

®

MOTOROI.A

HARDWARE

PREPARATION

2.3.8

Bit 1 of the

when

(CACHERR*)

CACHERR*

is

monitored but

switch

MSR

Bit 1 Source Select

section 1

is

disabled.

settings

can

J9

+-----------+

I 0 0---0 I

+-----------+

3 2 1

2KB

OF

CACHE

2KB

OF

CACHE

MSR

is

always

is

open

also

connected through header

When

this

are

be

section 1

is

not a useful configuration.

shown

connected to section 1 of switch

and

connected to

below:

ARE

Header

low

is

when

ARE

USER

ONLY

SUPERVISOR

(J20)

closed.

bit

1 of the

J20

and

section 1

open,

the signal

+---+

3 I 0 I

2 I 0 I

1

+---+

ONLY

The

signal

MSR

Header

J17

I I

I I

101

S3.

line

and

section 1.

is

closed, then

line

CACHERR*

configurations

It

is

Cache

high

Error

When

cache

can

and

I

be

S3

+--------+

111X

I

121

I

131 101

I

141

I N I

+--------+

MSR

BIT

101

FI

I F I

II

PI

I E I

1=0

J20

+---+

2 I 0 I

I I

1

101

+---+

S3

+--------+

111

XIOI

I F I

121

I

131 101

I

141

I

+--------+

MSR

BIT

I F I

II

PI

lEI

NI

1=1

S3

+--------+

111X

I F I

121

I

131 101

I

141

I

+--------+

CACHE

DISABLED

(MSR

BIT 1 IS

ALWAYS

2 I 0 I

1

101

I F I

II

PI

lEI

NI

LOW)

J20

+---+

I I I

101

+---+

S3

+--------+

111

XIOI

I F I

121

I

131

I

141

I

+--------+

CONFIGURATION

RECOMMENDED

I F I

II

101

PI

lEI

NI

THIS

NOT

15

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 26

@MOTOROLA

HARDWARE

PREPARATION

I

2.3.9

Bit

monitor the signal line

2,

connected to the signal

and

MSR

Bit 0

0 of the

it

is

switch configurations are

high

Source

MSR

can

when

J21

+---+

3

101

I I I

2 I 0 I

I I

1 I 0 I

+---+

SECTION 2 OF

TO

BIT 0 OF

S3

+--------+

III

I

121X

I II

131 101

I

141

I

+--------+

101

FI

I F I

PI

I E I

NI

Select

be

Cache

section 2 is

CACHEHIT*,

Header

configured to monitor section 2 of switch

Hit

shown

(J21)

(CACHEHIT*).

open

it

matches

below:

and

the level of

If

low

it

when

3

is

connected to section

closed.

J21

+---+

101

I I

2

101

I I I

1

101

+---+

S3

CONNECTED

THE

MSR

53

+--------+

III

I

121

I

131

I

I I

I

+--------+

101

FI

XIFI

II

101

PI

lEI

NI

[CACHEHIT*]

TO

BIT 0 OF

CONNECTED

53

If

bit

CACHEHIT*.

THE

MSR

or to

0 is

Header

MSR

BIT

0=0

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MSR

BIT

0=1

16

MICROSYSTEMS

Page 27

@MOTOROLA

HARDWARE

PREPARATION

2.3.10

Header

devices

and

ROM

J22

that

tables

Access

must

below.

valid data or

Note

given

that

ROM

other header configurations

access time.

J22

+-------+

8

I 0 o I

I I

6

I 0 o I

4

2

+-------+

ROM

ACCESS

LESS

I

I 0 o I

I

0---0

I

THAN

EQUAL

I

I I I I

I

TIME

OR

TO

Time

be

are

installed

Access

from

chip enable to valid data

7 8

5 6

3 4

1 2

ROM

LESS

Select

Header

configured to

in sockets

time

is

the longer of the time

J22

+-------+

I

I

I

o I

TIME

OR

TO

7 8

5 6

3 4

1 2

I 0 o I

I

I 0 o I

I

0---0

I

0

I

+-------+

ACCESS

THAN

EQUAL

(J22)

match

XU44

affect

+-------+

+-------+

ROM

ACCESS

LESS

EQUAL

the access time of the

and

XU52

as

shown

from

at

the pins of the

the configuration of

J22

I 0

o I

7

8

I I

0---0

I

I

I 0 o I

5 6

I

I

3 4

I

TIME

OR

TO

1 2

ROM

LESS

I 0 o I

THAN

EPROM/ROM

in

the figures 2

valid address to

ROM

devices.

J22

for

J22

+-------+

I

0---0

7

I

I I

I 0 o I

I

I 0 o I

5

I

3

I I

I 0 o I

+-------+

ACCESS

THAN

EQUAL

1

TIME

OR

TO

any

N/A

200

ns

250

400

2.3.11 Reset Vector Fetch

The

MPU

module

When

modifier

the

code

position of the

shown

below:

MPU

can

fetch the

module

IE

jumper

fetches the

or

16

MVME

ns

ns

Mode

reset

can

on

the header

120, 121,

MVME

Select

vector

be

used.

122

Header

reset

and

123

350

450

from

vectors

The

by

ns

ns

(J24)

onboard

mode

used

section 3

ROM

from

450

500

or

from

the

VMEbus,

is

controlled

and

4 of switch

ns

ns

the

VMEbus.

address

by

the

S3

as

17

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 28

@MOTOROLA

HARDWARE

PREPARATION

I

3

2

1 I 0 I

FETCH

VECTORS

VMEbus

(SWITCH

HAS

J24

+---+

101

II

101

I I

+--

-+

RESET

NO

I

FROM

EFFECT)

SECTION 4 OF

S3

+--------+

11

101

I F I

121

I

131

I

141

I

+--------+

I F I

II

XIOI

PI

X I E I

NI

J24

+---+

3

101

I I

2

101

I I I

1 I 0 I

+---+

CONTROLS

(SEE

MODE

BELOW)

+--------+

+--------+

S3

S3

III

101

I F I

121

I

131

I

141

I

I F I

XI

XI

II

0 I

PI

E I

NI

+---+

3

101

I I

2

101

I I

1 I 0 I

+---+

NEVER

RESET

FROM

(SWITCH

HAS

J24

FETCH

VECTORS

VMEbus

NO

EFFECT)

FETCH

VECTORS

VMEbus

ADDRESS

MODIFIER=lE

S3

+--------+

III

I F I

121

I

131X

I

141

X I E I

I

+--------+

FETCH

VECTORS

VMEbus

ADDRESS

MODIFIER=16

RESET

FROM

101

I F I

II

101

PI

NI

RESET

FROM

FETCH

VECTORS

RESET

FROM

ONBOARD

S3

+--------+

III

101

I F I

1211

I

131X

I

141

F I

II

101

PI

X I E I

I N I

+--------+

FETCH

VECTORS

RESET

ON

BOARD

FROM

18

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 29

®

MOTOROI.A

HARDWARE

PREPARATION

2.3.12

The

Local

local

Time-out

bus

time-out

Select

of

Header (J25)

the

times using jumper positioning

system

controller

module

has the global

J25

+-------+

1 I

0---0

I 2

I I

3 I 0 0 I 4

I I

5 I 0 0 I 6

+-------+

LOCAL

THE

THAN

110

TIME-OUT

= 103-137

MICROSECONDS

VMEbus

BUS

MUST

OR

GLOBAL

TIME-OUT

BE

LESS

EQUAL

TO

MICROSECONDS

LOCAL

THE

THAN

170

MPU

module

on

header J25.

bus

can

time-out

J25

+-------+

1 I 0 0 I 2

I I

3 I

0---0

I 4

I I

5 I 0 0 I 6

+-------+

TIME-OUT

=43-77

MICROSECONDS

VMEbus

BUS

TIME-OUT

MUST

OR

MICROSECONDS

GLOBAL

BE

LESS

EQUAL

TO

be

configured

The

user

set

THE

THAN

200

for

one

must

ensure

correctly.

J25

+-------+

1 I 0 0 I 2

I I

3 I 0 0 I 4

I I

5 I

0---0

+-------+

LOCAL

TIME-OUT

=13-47

MICROSECONDS

VMEbus

BUS

TIME

MUST

BE

OR

MICROSECONDS

I 6

GLOBAL

-OUT

LESS

EQUAL

TO

of

that

three

the I

2.3.13

The

ot~er

the

base address

can,

boundary

RAM.

less

2.3.13.1

RAM

Dual

onboard

VMEbus

VMEbus

RAM

masters.

master

is

be

programmed

for

128K

The

PAL

in socket

than or equal to

Factory Configured

configuration of

figures

128Kb

of

below

onboard

show

Port

of

Base

the

The

is

called

controlled

to· place the

of onboard

U28

35

ns.

U28

places the

the source

RAM

and

for

Address

MPU

Select

Module

lower address

the

RAM

dual

by

the

program

RAM

RAM

or

on

is a PAL16L2

RAM

Dual

RAM

code

512Kb

of

onboard

PAL

(U28)

is

accessible

at

which

port

base address.

in the

dual

any

512Kb

port

by

the onboard

the onboard

PAL

in socket

base address

boundary

for

RAM

The

512K

RAM

U28.

on

with a propagation delay time

Port

dual

Base

port

base address

Address.

at

The

000000.

for the factory configuration

RAM.

MPU

and

appears

dual

The

any

128Kb

of

onboard

that

factory

of

U28

by

for

port

PAL

is

The

for

19

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 30

@MOTOROLA

HARDWARE

PREPARATION

I

PAL16L2

U28-SHEET

PALDP20

A23 A22

AMI

AM3 AM2

DPMATCH = /A23*/A22*/A21*/A20*/AI9*/A18*/A17

DESCRIPTION:

8

A21

A20

AM4

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*AM2*AMI*AMO

+

/A23*/A22*/A21*/A20*/A19*/A18*/A17

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*AM2*/AMI*AMO

+

/A23*/A22*/A21*/A20*/A19*/AI8*/A17

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*/AM2*AM1*/AMO

+

/A23*/A22*/A21*/A20*/AI9*/AI8*/AI7

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*/AM2*/AM1*AMO

MVME120,

A19 A18 A17

15

/DPMATCH

DUAL

SET

PORT

FOR

MVME122

/LWORD

AMO

MAP

DECODER{128KBYTE

VMEBUS

ADDRESSES

/IACK

AM5

GND

VMEAV

VCC

0-lFFFF

ONBOARD

2-17-84

CKSM=

REV

;$OOOOOO-$OIFFFF

;STANDARD

;$OOOOOO-$OlFFFF

;STANDARD

;$OOOOOO-$OlFFFF

;STANDARD

;$OOOOOO-$OlFFFF

;STANDARD

RAM)

PRIV

PRIV

NON-PRIV

NON-PRIV

0744

A

PROG

DATA

PROG

DATA

PAL16L2

U28-SHEET

PALDP21

A23 A22

AMI

AM3

DPMATCH = /A23*/A22*/A21*/A20*/A19

DESCRIPTION:

8

A21

A20 A19

AM2

AM4

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*AM2*AM1*/AMO

+

/A23*/A22*/A21*/A20*/AI9

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*AM2*/AM1*AMO

+

/A23*/A22*/A21*/A20*/A19

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*/AM2*AM1*/AMO

+

/A23*/A22*/A21*/A20*/A19

*/IACK*/LWORD*/VMEAV

*AM5*AM4*AM3*/AM2*/AMI*AMO

MVME121

15

DUAL

SET

PORT

FOR

,MVME123

Al8

A17

/LWORD

/DPMATCH

VMEBUS

AMO

MAP

DECODER(512KBYTE

ADDRESSES

AM5

/IACK

VMEAV

GND

VCC

;$OOOOOO-$07FFFF

;STANDARD

;$OOOOOO-$07FFFF

;STANDARD

;$OOOOOO-$07FFFF

;STANDARD

;$OOOOOO-$07FFFF

;STANDARD

O~7FFFF

PRIV

PRIV

NON-PRIV

NON-PRIV

ONBOARD

7-23-84

CKSM=

REV

PROG

DATA

PROG

DATA

DYNAMIC

RAM)

OlCC

A

20

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 31

@MOTOROLA

HARDWARE

PREPARATION

2.3.13.2

Changing

U28.

propagation delay time of

firmware in

only the

must

remain

ADDRESS

U28

lines

source

requires a

that

intact

lines

and

affect

for proper operation of the

/A23*/A22*/A2l*/A20*/A19*/A18*

/A23*/A22*/A2l*/A20*/A19*

/A23*/A22*/A2l*/A20*/A19*

SAMPLE

ADDRESS

/A23*/A22*/A21*/A20*

/A23*/A22*/A2l*

/A23*/A22*/A21*

2.4

SAMPLE

INSTALLATION

ADDRESS

The

35

ns.

new

PAL16L2.

the

the

resultant

LINES

A19

A20*/A19

A20*

A19

LINES

device

PAL16L2's

ADDRESS

A18*/A17

A18*

FOR

FOR

used

in

U28

is a PAL16L2

with a

are not reprogrammable

When

changing the source

should

be

changed.

module.

The

Below

base addresses.

A17

;ADDRESS=$20000-$3FFFF

;ADDRESS=$40000-$5FFFF

A17

;ADDRESS=$60000-$7FFFF

l28KBYTES

OF

ON

BOARD

RAM

;ADDRESS=$80000-$FFFFF

;ADDRESS=$lOOOOO-$17FFFF

;ADDRESS=$180000-$lFFFFF

1/2MBYTE

OF

ON

BOARD

RAM

so

code

other

are

maximum

the

new

for

U28

lines

sample

2

The

chassis

following paragraphs discuss

and

the connection of

into the

installed

VMEbus

and

configured

chassis ensure

and

that

configured for desired operation.

2.4.1

Now

that

a.

Module

the

Turn

Installation

module

all

is

equipment

ready for

power

INSERTING/REMOVING

APPLIED

COULD

COMPONENTS.

b.

The

module

has a VMEbus

may

be

backplane

installed

on

installation

an

RS-232C

that

all

cable. Before

the desired

other headers, switches,

installation,

OFF.

CAUTION

MODULES

RESULT

into

IN

any

the connector

of the

proceed

WHILE

.DAMAGE

double

PI

POWER

TO

wide

side.

MPU

module

inserting

EPROM/ROM

as

follows:

IS

MODULE

unused

card

into a

the

module

devices are

and

PAL's

slot

which

VME

are

21

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 32

@MOTOROLA

HARDWARE

PREPARATION

I

c. Ensure

backplane.

each connector

(shorted) connection or

use

from

module

then

line's

inserted.

With

shorted

(generally shorting jumpers

do

the daisy-chain signal

backplane. Daisy-chain signal

module

module

the

none

at

the

d. Carefully

properly into connectors

with front panel screws provided.

that

a daisy-chain

that

is

it

IN

these

at

not

have a module

should not

connects

IACKIN*-IACKOUT*

of the daisy-chain signal

slot

the

BG*

Each

line's

inserted.

should automatically provide a

pin

However,

modules

that

where

slide

daisy-chain

on

IN

to

the

connector using the

all

it

module

and

the

line

pin to the

If

OUT

some

the daisy-chain signal

inserted into the

lines

be

shorted

the daisy-chain signal

signal

resides.

on

IACK*

line

PI

backplane. This

an

indirect

automatically provide

the

pin

on

modules

on

be

lines

lines

lines

into card

the

daisy-chains are complete

must

OUT

pin

module

the connector into

a header).

shorted using the

on

the backplane

which

PI

backplane. Fasten

be

connected

(gated) connection.

on

the connector into

does

do

means

that

should

slot.

not

direct

not provide

provided

In

PI

connector, require

are

lines

it

connects

be

from

must

either

an

indirect

use

a daisy-chain

connection

which

direct

line

in question

on

addition,

means

indirectly

at

that

indirectly

directly),

shorted

Be

sure

module

on

IN

to

be a direct

Modules

connection

which

from

the

module

connections.

must

the

PI

backplane

any

slots

that

provided

connected

slot.

on

the backplane

module

The

(except for

so

is

in chassis

the

PI

OUT

at

that

the

line,

that

is

be

that

all

on

the

by

MPU

that

seated

a

e.

Make

locations.

address

modules

must

f.

Ensure

VMEbus.

g. Ensure

priority

controller)

h.

Make

system.

i.

Turn

2.4.2

The

operation only. A 25-pin

connector with the other

Table 5-2 for

Terminal Connection

RS-232C

sure

be

sure

equipment

that

More

and

reside

programmed

that

that

slot

.

that

serial

detailed

all

than

address modifier combination.

on

the

differently

only

one

a system

of

the

forced

power

port

information

devices

one

same

module

controller

PI

air

ON.

on

the front panel

RS-232C

end

connected to a compatible terminal. Refer to

on

the

VMEbus

VMEbus

PI

backplane, the

on

responds

backplane (the

cooling

cable

on

signals supported.

one

may

device

module

to

anyone

module

is

in place for the

be

respond to unique address

may

not respond to the

For

example,

RAM

dual port base address

then

it

is

on

the other.

IRQ

signal

is

present

MPU

connected to the

module

is

configured for terminal

line

at

the highest

is

not a system

modules

front

if

same

two

on

in the

panel

MPU

the

22

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 33

(f!jMOTOROL.A

OPERATING

INSTRUCTIONS

3.1

CHAPTER

OPERATING

INTRODUCTION

3

INSTRUCTIONS

This chapter provides the necessary information to

system configuration.

3.2

The

CONTROLS

MPU

indicator, a

are located

3.2.1

The

level

RESET

reset

reset

operate with the

switch

be

is

completed before entering the

cycling onboard

reset

by

SYSRESET*.

AND

INDICATORS

module

HALT

on

has

indicator,

a

RESET

switch,

and a RUN

the front panel of the

an

ABORT

indicator.

module.

switch, a

All

Switch

performed

is

by

the

performed

MPU

module.

RESET

by

the system

The

switch

MPU

is

a board-level

controller

is

not immediately

depressed, but instead, waits for the current access of the

and

unintentional

reset

VMEbus

state.

accesses.

This sequence prevents short

use

switches

reset

module

The

module

the

MPU

module

mode

switch, a

and

only. A system

that

reset

is

when

is

immediately

in a I

FAIL

indicators

needed

the

to

RESET

MPU

to

3.2.2

A software

aborted with

to

execution of the

3.2.3

The

the

the onboard

Address Modifier

perform

VMEbus

ABORT

be

input to the

Mode

mode

MPU

Switch

switch (section 4 of

to

fetch the

this

accesses of

Switch

ABORT

this

switch

switch. Oepressing

MPU.

STOP

instruction.

reset

ROM/EPROM

(AM)

task.

Section 3 of switch

reset

sockets, or

code

disabled through header J24.

normal

and

or

mode

alternate

mode

switch position

of operation.

is

is

located

"The

ABORT

S3)

stack pointer

IE

or 16.

vector

Header

on

the front panel.

this

switch

switch causes a level 7

does

provides the

and

Program

from a VMEbus

The

MVME050

S3

selects

and

stack pointer.

J24

can

be

configured to force

The

result

not abort the

ability

resource

also readable through the

Programs

may

be

interrupt

MPU

during the

through hardware for

Counter

controller

either

The

that

AM

mode

(PC)

code

from

can

respond to

module

16

or

switch

either

either

can

IE

for

may

be

the

of the header configuration

MSR.

23

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

MICROSYSTEMS

Page 34

®

MOTOROLA

OPERATING

INSTRUCTIONS

II

3.2.4

The

driving the

indicator

module

also drives the

condition

3.2.5

The

(usually the

is

momentarily. Refer to Table

3.2.6

The

the

FAIL

red

HALT

red

being

RUN

green

MPU

Indicator

LED

is

fail

lights

Indicator

LED

Indicator

LED

is

true

TABLE

FAIL

result

reset.

indicator

HALT

bit

line

lit

when

of the

SYSFAIL*

the indicator momentarily. Refer to Table 3-1 for

HALT

and

indicator

of a double

The

RUN

indicator

off

3-1. Interpretation of Front

low

the

MCR

dual

when

is

lit

usually the

MPU

is

is

set

line

is

bus

port lock condition

3-1 for

is

lit

it

is

whenever

being

low

false.

reset.

(whenever

on

lit

whenever

fault).

details.

whenever

the

MPU

enters a halted

result

the

The

Refer to Table 3-1 for

of a double

The

indicator

the

FAIL

VMEbus).

the

MPU

indicator

the

Address

Panel

bit

enters a halted

lights

Indicators

bus

fault).

is

lit

is

set,

The

dual

is

lit

when

the indicator

Strobe

(AS*)

details.

state

the

port lock

details.

(MPU

when

module

state

the

pin of

The

the

MPU

=============================================================================

FAIL

=======================================~=====================================

OFF

HALT

OFF

RUN

OFF

DESCRIPTION

No

power

running but

applied to the

is

not the local

module,

bus

master.

or processor

OFF

ON

ON

ON

ON

OFF

ON

OFF

OFF

ON

ON

OFF

ON

OFF

ON

Normal

Module

the

MPU

MCR

software,

was

time

Bit 0

reset

MPU

Frequency

of

operation.

result

is

is

not cleared to 0

the

in

and

is

halt

is

being

of a double

executing

set

module

running

and

such

the

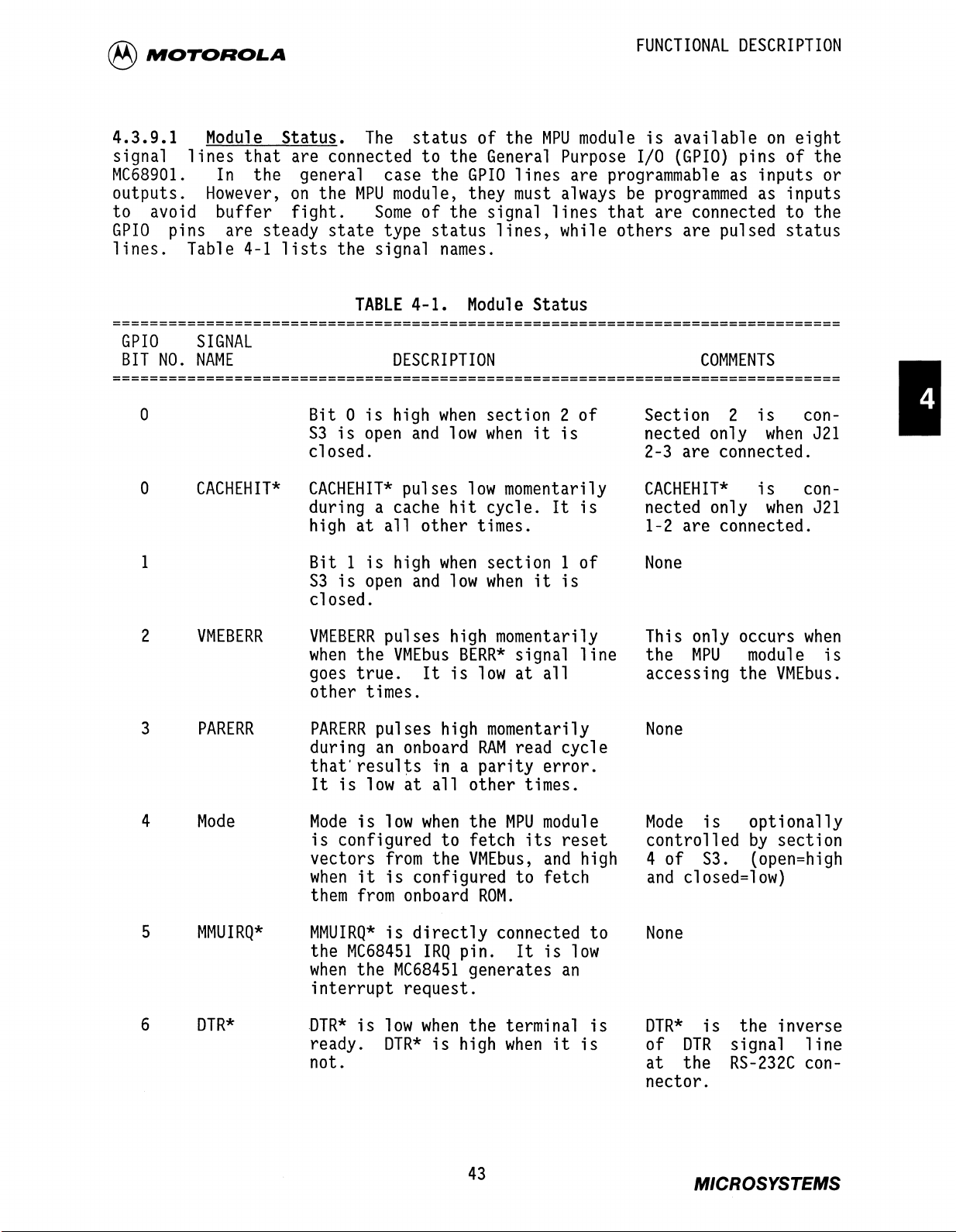

MPU