MOTOROLA MPF102RLRA Datasheet

1

Motorola Small–Signal Transistors, FETs and Diodes Device Data

N–Channel — Depletion

MAXIMUM RATINGS

Rating Symbol Value Unit

Drain–Source Voltage V

DS

25 Vdc

Drain–Gate Voltage V

DG

25 Vdc

Gate–Source Voltage V

GS

–25 Vdc

Gate Current I

G

10 mAdc

Total Device Dissipation @ TA = 25°C

Derate above 25°C

P

D

350

2.8

mW

mW/°C

Junction Temperature Range T

J

125 °C

Storage Temperature Range T

stg

–65 to +150 °C

ELECTRICAL CHARACTERISTICS (T

A

= 25°C unless otherwise noted)

Characteristic Symbol Min Max Unit

OFF CHARACTERISTICS

Gate–Source Breakdown Voltage

(IG = –10 µAdc, VDS = 0)

V

(BR)GSS

–25 — Vdc

Gate Reverse Current

(VGS = –15 Vdc, VDS = 0)

(VGS = –15 Vdc, VDS = 0, TA = 100°C)

I

GSS

—

—

–2.0

–2.0

nAdc

µAdc

Gate–Source Cutoff Voltage

(VDS = 15 Vdc, ID = 2.0 nAdc)

V

GS(off)

— –8.0 Vdc

Gate–Source Voltage

(VDS = 15 Vdc, ID = 0.2 mAdc)

V

GS

–0.5 –7.5 Vdc

ON CHARACTERISTICS

Zero–Gate–Voltage Drain Current

(1)

(VDS = 15 Vdc, VGS = 0 Vdc)

I

DSS

2.0 20 mAdc

SMALL–SIGNAL CHARACTERISTICS

Forward Transfer Admittance

(1)

(VDS = 15 Vdc, VGS = 0, f = 1.0 kHz)

(VDS = 15 Vdc, VGS = 0, f = 100 MHz)

yfs

2000

1600

7500

—

m

mhos

Input Admittance

(VDS = 15 Vdc, VGS = 0, f = 100 MHz)

Re(yis) — 800

m

mhos

Output Conductance

(VDS = 15 Vdc, VGS = 0, f = 100 MHz)

Re(yos) — 200

m

mhos

Input Capacitance

(VDS = 15 Vdc, VGS = 0, f = 1.0 MHz)

C

iss

— 7.0 pF

Reverse Transfer Capacitance

(VDS = 15 Vdc, VGS = 0, f = 1.0 MHz)

C

rss

— 3.0 pF

1. Pulse Test; Pulse Width v 630 ms, Duty Cycle v 10%.

Order this document

by MPF102/D

SEMICONDUCTOR TECHNICAL DATA

CASE 29–04, STYLE 5

TO–92 (TO–226AA)

1

2

3

Motorola, Inc. 1997

1 DRAIN

2 SOURCE

3

GATE

MPF102

2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

P

G

, POWER GAIN (dB)

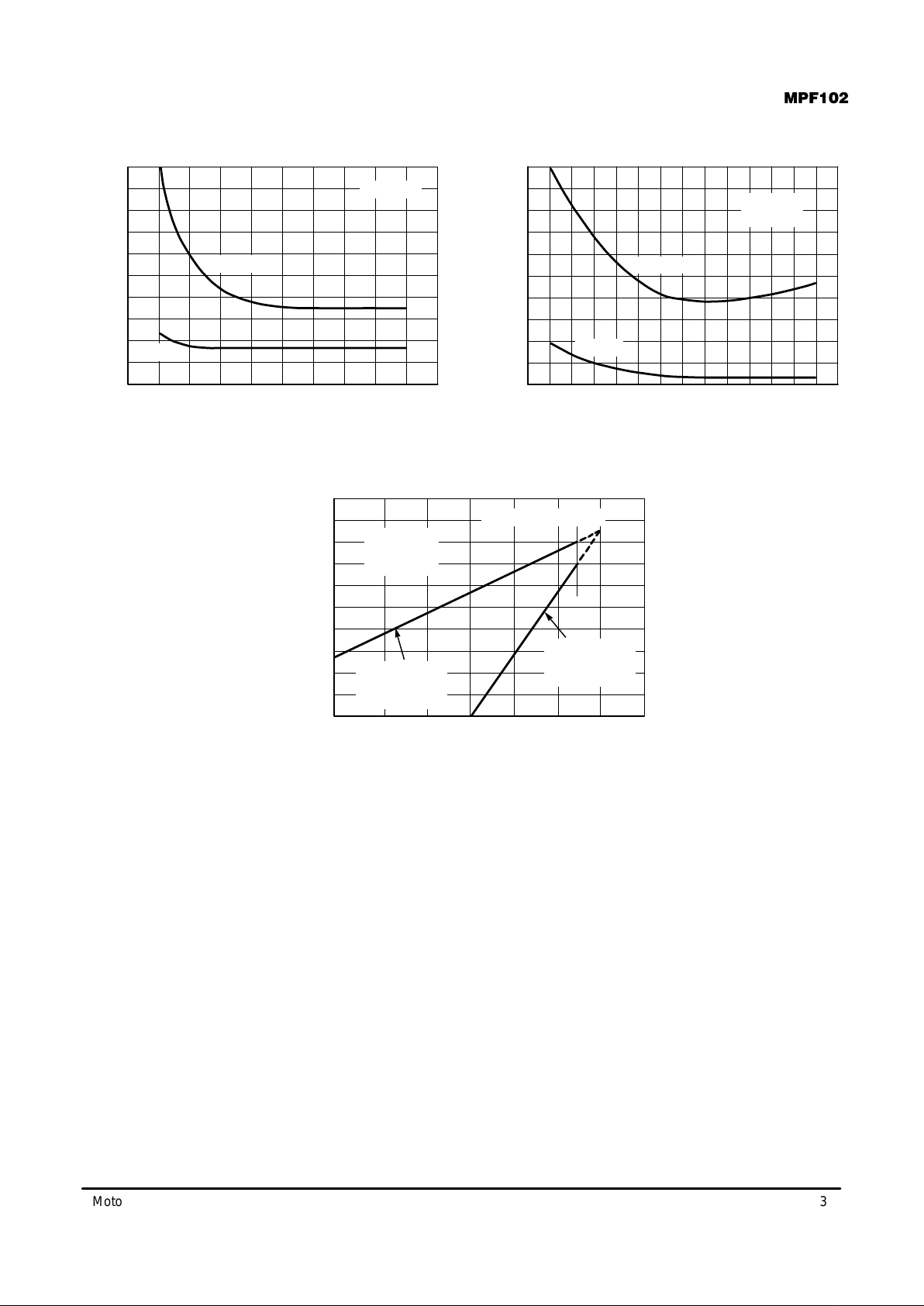

POWER GAIN

2.0

ID, DRAIN CURRENT (mA)

Figure 1. Effects of Drain Current

4.0

24

8.0

12

16

20

0 4.0 6.0 8.0 10 12 14

f = 100 MHz

400 MHz

T

channel

= 25°C

VDS = 15 Vdc

VGS = 0 V

Figure 2. 100 MHz and 400 MHz Neutralized Test Circuit

*L1 17 turns, (approx. — depends upon circuit layout) AWG #28

enameled copper wire, close wound on 9/32″ ceramic coil

form. Tuning provided by a powdered iron slug.

*L2 4–1/2 turns, AWG #18 enameled copper wire, 5/16″ long,

3/8″ I.D. (AIR CORE).

*L3 3–1/2 turns, AWG #18 enameled copper wire, 1/4″ long,

3/8″ I.D. (AIR CORE).

**L1 6 turns, (approx. — depends upon circuit layout) AWG #24

enameled copper wire, close wound on 7/32″ ceramic coil

form. Tuning provided by an aluminum slug.

**L2 1 turn, AWG #16 enameled copper wire, 3/8″ I.D.

(AIR CORE).

**L3 1/2 turn, AWG #16 enameled copper wire, 1/4″ I.D.

(AIR CORE).

Adjust VGS for

ID = 50 mA

VGS < 0 Volts

NOTE: The noise source is a hot–cold body

(AIL type 70 or equivalent) with a

test receiver (AIL type 136 or equivalent).

Reference

Designation

VALUE

100 MHz 400 MHz

C1

7.0 pF 1.8 pF

C2 1000 pF 17 pF

C3 3.0 pF 1.0 pF

C4 1–12 pF 0.8–8.0 pF

C5 1–12 pF 0.8–8.0 pF

C6 0.0015 µF 0.001 µF

C7 0.0015 µF 0.001 µF

L1 3.0 µH* 0.2 µH**

L2 0.15 µH* 0.03 µH**

L3 0.14 µH* 0.022 µH**

INPUT

TO 50

Ω

SOURCE

NEUTRALIZING

COIL

L1

C5

L3R

g

′

C1

C6

C4

L2

C3

TO 500

Ω

LOAD

CASE

C7

COMMON

ID = 5.0 mA

V

GS

V

DS

+15 V

C2

MPF102

3

Motorola Small–Signal Transistors, FETs and Diodes Device Data

NF, NOISE FIGURE (dB)

2.0

VDS, DRAIN–SOURCE VOLTAGE (VOLTS)

0

10

2.0

4.0

6.0

8.0

0 4.0 6.0 8.0 10 12 14

ID = 5.0 mA

100 MHz

VDS = 15 Vdc

f1 = 399 MHz

f2 = 400 MHz

NF, NOISE FIGURE (dB)

2.0

ID, DRAIN CURRENT (mA)

1.5

6.5

2.5

3.5

4.5

5.5

0 4.0 6.0 8.0 10 12 14

Figure 3. Effects of Drain–Source Voltage Figure 4. Effects of Drain Current

NOISE FIGURE

(T

channel

= 25°C)

Pin, INPUT POWER PER TONE (dB)

+40

Figure 5. Third Order Intermodulation Distortion

P , OUTPUT POWER PER TONE (dB)

out

16 18 20

f = 400 MHz

f = 400 MHz

100 MHz

VDS = 15 V

VGS = 0 V

+20

0

–20

–40

–60

–80

–100

–120

–140

–160

–120 –100 –80 –60 –40 –20 0 +20

3RD ORDER INTERCEPT

FUNDAMENT AL

OUTPUT @ I

DSS

,

0.25 I

DSS

3RD ORDER IMD

OUTPUT @ I

DSS

,

0.25 I

DSS

INTERMODULA TION CHARACTERISTICS

Loading...

Loading...