Page 1

MCPN750A CompactPCI

Single Board Computer

Installation and Use

MCPN750A/IH5

September 2001 Edition

Page 2

© Copyright 2001 Motorola, Inc.

All Rights Reserved.

Printed in the United States of America.

Motorola and the stylized M logo are registered trade marks of Motoro la, Inc.

PowerPC is a registered trademark of International Business Machines and is used by

Motorola Inc. under license from IBM Corporation.

CompactPCI is a registered trademark of PCI Industrial Computer Manufacturers Group.

All other product or se rvice names mentioned i n this document are trademarks or registered

trademarks of their respective holders.

Page 3

Safety Summary

The following general safety precautions must be observed during all phases of operation, service, and repair of this

equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result

in personal injury or damage to the equipment.

The safety precaut ions listed be low represent warnings of ce rtain danger s of which Mot orola is awar e. You, as the

user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of

the equipment in your operating environment.

Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the

equipment is su pplied wi th a three-c onductor A C power ca ble, the po wer cable m ust be plug ged into an a pproved

three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground

(safety ground) at the power outlet. The power jack and mating plug of the power cable meet International

Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes.

Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

Keep Away From Live Circuits Inside the Equipment.

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other

qualified service personnel may remove equipment covers for internal subassembly or component replacement or any

internal adjust ment. Service pe rsonnel should n ot replace compon ents with power c able connected. Under certain

conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel

should always disconnect power a nd discharge circuits bef ore touching components.

Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent

CRT implosion, do not handl e the CRT and avoid rough handling o r jarring of t he equipment . Handling o f a CRT

should be done only by qualified service personnel using approved safety mask and gloves.

Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local

Motorola representative for service and repair to ensure that all safety features are maintained.

Observe Warnings in Manual.

W arn ings , such as th e exa mple be low, preced e pote ntia lly da nger ous pro cedure s thro ugh out th is manual . In struc tion s

contained in the warnings m ust be follow ed. You should also employ all ot her safety precautions w hich you dee m

necessary for the operation of the equ ipment in your oper at ing environment.

To prevent serious injury or death from dangerous voltages, use extreme

caution when handling, testing, and adjusting this equipment and its

Warning

components.

Page 4

Flammability

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating

of 94V-0 by UL-recognized manufacturers.

EMI Caution

This equipment ge ner ates, uses a nd can radi ate el ectro magne tic energy . It

!

Caution

This product contains a lithium battery to power the clock and calendar circuitry.

!

Caution

may cause or be susceptible to electromagnetic interference (EMI) if not

installed and used with adequate EMI protection.

Lithium Battery Caution

Danger of explosion if battery is re placed incorrect ly. Replace battery only

with the same or equivalent type recommended by the equipment

manufacturer. Dispose of used batteries according to the manufacturer’s

instructions.

!

Attention

!

Vorsicht

Il y a danger d’explosion s’il y a remplacement incorrect de la batterie.

Remplacer uniquement avec une batterie du même type ou d’un type

équivalent recommandé par le constructeur. Mettre au rebut les batteries

usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Ba tt erie. Ersatz nur

durch denselben ode r einen vom Herstel ler empfohle nen Typ. Entsorgu ng

gebrauchter Batterien nach Angaben des Herstellers.

Page 5

CE Notice (European Community)

This is a Class A product. In a domestic environment, this product may

!

Warning

Motorola Compute r Group pro ducts wi th the CE mar king co mply with the EMC Dir ective

(89/336/EEC). Compliance with this directive implies conformity to the following

European Norms:

EN55022 “Limits and Methods of Meas urement of Radio Int erferen ce Chara cteri stic s

of Information Technology Equipment”; this product tested to Equipment Class A

EN55024 “Information Technology Equipment-Immunity characteristics-Limits and

methods of measurement”

Board products are tested in a representative system to show compliance with the above

mentioned requirements. A proper installation in a CE-marked system will maintain the

required EMC /safety performance.

In accordance with European Community directives, a “Declaration of Conformity” has

been made and is available on request. Please contact your sales representative.

cause radio interference, in which case the user may be required to take

adequate measures.

Notice

While reasonable efforts have been made to assure the accuracy of this document,

Motorola, Inc. a ssumes n o lia bility r esulti ng from any omissio ns in this docu ment, or from

the use of the information obtained therein. Motoro la reserves th e right to revise this

document and to ma ke c hanges from time to ti me in t h e cont ent hereof without obligation

of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or

referenced in another document as a URL to the Motorola Computer Group website. The

text itself may not b e published commerci ally in print o r electronic for m, edited, transla ted,

or otherwise altered without the permiss ion of Motorola, Inc.

It is possible th at t hi s publication may contain r ef erence to or information about Motorola

products (machines and pr ograms), progra mming, or services that are not av ailable in your

country. Such references or information must not be construed to mean that Motorola

intends to announce such Motorola products, programming, or services in your country.

Page 6

Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S.

Government, the following notice shall apply unless otherwise agreed to in writing by

Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in

subparagraph (b)(3) of t he Rig hts i n Tech nical Data clause at DFARS 252.227-7013 (Nov.

1995) and of the Rights in Noncommerc ial Computer Software and Docume ntation clause

at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc.

Computer Group

2900 South Diablo Way

Tempe, Arizona 85282

Page 7

Contents

About This Manual

Summary of Changes...............................................................................................xviii

Overview of Contents..............................................................................................xviii

Comments and Suggestions.....................................................................................xviii

Conventions Used in This Manual.............................................................................xix

CHAPTER 1 Hardware Preparation and Installation

Introduction ................................................................................................................1-1

Product Description............................................................................................1-1

Block Diagram....................................................................................................1-1

Getting Started ..................................................................................... ......................1-3

Overview of Start-up Procedure.........................................................................1-3

Equipment Required...........................................................................................1-4

Unpacking Instructions.......................................................................................1-5

ESD Precautions.................................................................................................1-5

Preparation.................................................................................................................1-6

Hardware Configuration.....................................................................................1-6

MCPN750A Base Board Preparation.................................................................1-6

Flash Bank Selection (J7)............................................................................1-7

Stand-Alone Operating Mode (J8) ..............................................................1-8

System Considerations......................................................................................1-10

TMCPN710 Transition Module Preparation ....................................................1-11

Serial Ports 1 and 2 ....................................................................................1-13

COM3 and COM4 Asynchronous Serial Ports..........................................1-15

TM-PIMC-0001 Transition Module Preparation..............................................1-16

COM 1 and COM 2 Asynchronous Serial Ports........................................1-18

COM3 and COM4 Asynchronous Serial Ports..........................................1-20

Hardware Installation...............................................................................................1-21

Installing PMC Modules on the MCPN750A SBC..........................................1-21

Installing the MCPN750A Baseboard..............................................................1-24

Installing a TMCPN710 or TM-PIMC-0001 Transition Module.....................1-26

Installing PIMs on the TM-PIMC-0001 Transition Module .....................1-26

Installing the Transition Module in the Chassis........................................1-28

MCPN750A Module Power Requirements .............................................................1-31

vii

Page 8

CHAPTER 2 Startup and Operation

Introduction ...............................................................................................................2-1

Applying Power.........................................................................................................2-1

Memory Maps......................................................................... ...................................2-3

Processor Memory Map ....................................................... ...... ........................2-3

Default Processor Memory Map.................................................................2 -3

PCI Local Bus Memory Map.............................................................................2-4

CompactPCI Memory Map................................................................................2-5

Address Decoding with the 21554..............................................................2-5

L2 Cache.............................................................................................................2-6

System Clock Generator.....................................................................................2-6

PPC Bus Arbitration...........................................................................................2-6

PCI Host Bridge .................................................................................................2-6

PCI Arbitration...................................................................................................2-8

Interrupt Handling..............................................................................................2-8

ISA DMA Channels ...........................................................................................2 -9

Sources of Reset.................................................................................................2-9

Power-On Reset ........................................................................................2-11

Undervoltage Reset...................................................................................2-11

Front Panel Push Button Reset..................................................................2-11

CompactPCI Reset (RST#).......................................................................2-11

Watchdog Timer Reset..............................................................................2-11

Software Resets.........................................................................................2-12

Reset Source Identification.......................................................................2-12

Endian Issues....................................................................................................2-12

Processor/Memory Domain ......................................................................2-12

PCI Domain...............................................................................................2-13

CHAPTER 3 PPCBug

PPCBug Overview.....................................................................................................3-1

PPCBug Basics..........................................................................................................3-1

Memory Requirements.............................................. ...... ...................................3-3

PPCBug Implementation....................................................................................3-3

MPU, Hardware, and Firmware Initialization...........................................................3-3

Using PPCBug...........................................................................................................3-5

Debugger Commands.........................................................................................3-6

Diagnostic Tests................................................................................................3-10

viii

Page 9

CHAPTER 4 CNFG and ENV Commands

Overview....................................................................................................................4-1

CNFG - Configure Board Information Block............................................................4-2

ENV - Set Environment.............................................................................................4-3

Configuring the PPCBug Parameters.................................................................4-3

CHAPTER 5 Remote Start Via the PCI Bus

Introduction................................................................................................................5-1

Overview.............................................................................................................5-1

Command/response Register Description...........................................................5-3

Opcode 0x01: Write/Read Virtual Register........................................................5-5

Opcode 0x02: Initialize Memory........................................................................5-5

Opcode 0x03: Write/Read Memory....................................................................5-6

Opcode 0x04: Checksum Memory.....................................................................5-6

Opcode 0x05: Memory Size Query....................................................................5-7

Opcode 0x06: Debugger Query..........................................................................5-7

Opcode 0x07: Execute Code...............................................................................5-7

Command/Response Channel Error Codes.........................................................5-8

Demonstration of the Host Interface...................................................................5-9

Reference Function: srom_crc.c.......................................................................5-12

CHAPTER 6 Functional Description

Introduction................................................................................................................6-1

Features......................................................................................................................6-1

General Description ...................................................................................................6-2

Block Diagram...........................................................................................................6-3

CompactPCI Bus Interface.................................................................................6-5

Ethernet Interface................................................................................................6-6

PCI Mezzanine Interface ....................................................................................6-7

ISA Bus Devices.................................................................................................6-8

Asynchronous Serial Ports...........................................................................6-8

Configuration and Status Registers.............................................................6-8

Serial EEPROM..................................................................................................6-8

PCI Peripheral Bus Controller (PBC).................................................................6-9

ISA Interface................................................................................................6-9

EIDE Interface...........................................................................................6-10

USB Interface............................................................................................6-10

ISA Interrupt Controller............................................................................6-10

ix

Page 10

ISA DMA Channels..................................................................................6-10

Interval Timers..........................................................................................6-11

Real-Time Clock/NVRAM/Watchdog Timer Function...................................6-11

Replacing Lithium Batteries .....................................................................6-12

Hot Swap Control Circuitry .............................................................................6-14

Programmable Timers......................................................................................6-14

Raven General Purpose Timers.................................................................6-14

Raven Watchdog Timers........................................................... ................6-15

M48T559 Watchdog Timer.......................................................................6-15

Interval Timers..........................................................................................6-16

Serial Port Signal Multiplexing........................................................................6-16

I/O Signal Multiplexing (IOMX)..............................................................6-17

Signal Descriptions ...................................................................................6-19

ABORT(ABT)/RESET (RST) Switch (S1)......................................................6-19

Front Panel Indicators (DS1 - DS3)................................................................. 6-20

MPC750 Processor...................................................................................... .....6-20

Raven PCI-Host Bridge...................................... ...... ..... ............................6-20

Flash Memory ...........................................................................................6-20

JTAG/COP................................................................................................6-21

Bank A Flash Programming Enable..........................................................6-21

ECC Memory Controller.................................................................................. 6-22

DRAM Memory ............................................. ..... ........................................ .....6-22

Compact FLASH Memory Card ......................................................................6-22

TMCPN710 Transition Module .......................................................................6-23

TM-PIMC-0001............................................................... .................................6-23

CHAPTER 7 Connector Pin Assignments

MCPN750A and Transition Module Connectors ......................................................7-1

MCPN750A Connector Pin Assignments.................................................................7-2

MCPN750A CompactPCI Bus Connectors (J1/J2)............................................7-2

MCPN750A CompactPCI User I/O Connector J3.............................................7-4

MCPN750A Connector J4..................................................................................7-6

MCPN750A CompactPCI User I/O Connector (J5)..........................................7-7

MCPN750A PCI Mezzanine Card Connectors

(J11/21, J12/22, J13/23, J14/24..........................................................................7-9

MCPN750A 10BaseT/100BaseTx Connector (J18) ........................................7-12

MCPN750A Debug Connector (J19)...............................................................7-12

MCPN750A Processor RISCWatch Debug Connector (J6).............................7-17

TMCPN710 Transition Module....................... ...... ..... ........................................ .....7-18

TMCPN710 Transition Module CompactPCI Connectors (J3/J4/J5)..............7-18

x

Page 11

TMCPN710 Transition Module COM1 Connector (J6)...................................7-19

TMCPN710 Transition Module COM2 Connector (J8)...................................7-20

TMCPN710 Transition Module COM3 Header (J11)......................................7-20

TMCPN710 Transition Module COM4 Header (J14)......................................7-21

TMCPN710 Transition Module 10BaseT/100BaseTx Connector (J13) ..........7-22

TMCPN710 Transition Module USB Connectors (J10, J12)...........................7-23

TMCPN710 Transition Module IDE Compact FLASH Connectors

(J15, J16)...........................................................................................................7-23

TMCPN710 Transition Module PMC I/O Connectors (J1/J2).........................7-25

TM-PIMC-0001 Transition Module ........................................................................7-27

TM-PIMC-0001 CompactPCI User I/O Connector (J3, J4, & J5)...................7-27

TM-PIMC-0001 Transition Module COM1 Connector (J9)............................7-28

TM-PIMC-0001 Transition Module COM2 Connector (J8)............................7-29

TM-PIMC-0001 Transition Module COM3 and COM4 Connectors

(J12 & J13)........................................................................................................7-30

TM-PIMC-0001 Transition Module 10BaseT/100BaseTx Connector (J7)......7-31

TM-PIMC-0001 Transition Module IDE Compact FLASH Connector (J1)....7-31

TM-PIMC-0001 Transition Module PMC I/O Connectors

(J10, J20, and J14/J24)......................................................................................7-33

APPENDIX A Specifications

Specifications............................................................................................................A-1

Cooling Requirements ..............................................................................................A-2

EMC Compliance......................................................................................................A-3

APPENDIX B Related Documentation

Motorola Computer Group Documents....................................................................B-1

Manufacturers’ Documents.......................................................................................B-2

Related Specifications...............................................................................................B-4

xi

Page 12

xii

Page 13

List of Figures

Figure 1-1. MCPN750A Base Board Block Diagram................................................1-2

Figure 1-2. MCPN750A Switches, Headers, Connectors, Fuses, LEDs ................... 1-9

Figure 1-3. TMCPN710 Connector and Header Locations .....................................1-12

Figure 1-4. MCPN750A/TMCPN710 Serial Ports 1 and 2 .....................................1-14

Figure 1-5. TMCPN710 Serial Ports 3 and 4 ...........................................................1-15

Figure 1-6. TM-PIMC-0001 Connector and Header Locations...............................1-17

Figure 1-7. MCPN750A/TM-PIMC-0001 Serial Ports 1 and 2...............................1-19

Figure 1-8. TM-PIMC-0001 Serial Ports 3 and 4....................................................1-20

Figure 1-9. PMC Module Placement on MCPN750A.............................................1-22

Figure 1-10. TMCPN710 or TM-PIMC-0001/MCPN750A Mating Configuration1-30

Figure 2-1. PPCBug System Startup..........................................................................2-2

Figure 6-1. MCPN750A Block Diagram...................................................................6-4

Figure 6-2. Serial Port Signal Multiplexing.............................................................6-17

Figure 6-3. MX Signal Timings...............................................................................6-19

xiii

Page 14

xiv

Page 15

List of T ables

T ab le 1-1. Startup Overview................................................................................. .....1-3

T ab le 1-2. Installing a PIM on the TM-PIMC-0001 T ransi tion Module.................1-27

Table 2-1. Processor Default View of the Memory Map ...........................................2-3

Table 2-2. Classes of Reset and Effectiveness.........................................................2-10

T ab le 3-1. Debugger Command s........................................ .......................................3-7

Table 3-2. Diagnostic Test Groups...........................................................................3-11

Table 5-1. Command/Respond Error Codes..............................................................5-8

T ab le 6-1. MCPN750A Features........................ ..... ...... ........................................ .....6-1

Table 6-2. Multiplexing Sequence of the MX Function..........................................6-18

Table 7-1. MCPN750A J1 CompactPCI Connector..................................................7-2

Table 7-2. MCPN750A J2 CompactPCI Connector..................................................7-3

Table 7-3. MCPN750A J3 User I/O Connector.........................................................7-5

Table 7-4. MCPN750A J5 User I/O Connector.........................................................7-7

T ab le 7-5. MCPN750A PCI Mezzanine Card Connector..........................................7-9

T ab le 7-6. MCPN750A PCI Mezzanine Card Connector........................................7-10

Table 7-7. MCPN750A 10BaseT/100BaseTx Connector J18 .................................7-12

Table 7-8. MCPN750A Debug Connector (J19)......................................................7-13

Table 7-9. MCPN750A RISCWatch Debug Connector (J6)....................................7-17

T ab le 7-10. TMCPN710 COM1 Connector (J6)............................ ...... ....................7-19

T ab le 7-11. TMCPN710 COM2 Connector (J8)...................... ................................7-20

T ab le 7-12. TMCPN710 COM3/COM4 Headers....................................................7-20

Table 7-13. TMCPN710 10BaseT/100BaseTx Connector (J13).............................7-22

Table 7-14. TMCPN710 USB 0 Connector (J10)....................................................7-23

Table 7-15. TMCPN710 USB 1 Connector (J12)....................................................7-23

Table 7-16. TMCPN710 Compact FLASH IDE Connectors...................................7-24

Table 7-17. TMCPN710 PMC 1 and 2 I/O Connector ............................................7-25

Table 7-18. TM-PIMC-0001 COM1 Connector (J9)...............................................7-28

Table 7-19. TM-PIMC-0001 COM2 Connector (J8)...............................................7-29

Table 7-20. TM-PIMC-0001 COM3 and COM4 Headers.......................................7-30

Table 7-21. TM-PIMC-0001 10BaseT/100BaseTx Connector (J7).........................7-31

Table 7-22. TM-PIMC-0001 CompactFLASH IDE Connector (J1) .......................7-32

Table 7-23. TM-PIMC-0001 PMC I/O Module 1 (PIM1) - Host I/O

Connector Pin Assignments.....................................................................................7-33

Table 7-24. TM-PIMC-0001 PMC I/O Module 2 (PIM2) - Host I/O

Connector Pin Assignments.....................................................................................7-34

xv

Page 16

Table 7-25. PMC I/O Modules 1 and 2 (PIM1 a nd PIM2) -

PMC I/O Connector Pin Assignments.....................................................................7-36

Table A-1. MCPN750 Specifications ......................................................................A-1

Table B-1. Motorola Computer Group Documents ................................................. B-1

Table B-2. Manufacturers’ Documents ................................................................... B-2

Table B-3. Related Specifications ........................................................................... B-4

xvi

Page 17

About This Manual

This manual, MCPN750A CompactPCI Single Board Computer

Installation and Use (MCPN750A/IH5) provides general information,

hardware preparati on and installation instr uct i ons, operating instructi ons,

firmware informatio n, functional descriptions, and pin assig nments for the

MCPN750A family of Single Board Computers. In addition, sufficient

information is a lso provided for the two t ransition modules manufactured

by Motorola for use with the MCPN750A (TMCPN710 and TM-PIMC-

0001). The document should be used by anyone who wants general , as well

as technical information about the MCPN750A products.

Note: This revision of the MCPN750A Installation and Use manual

supersedes all previous versions of this document.

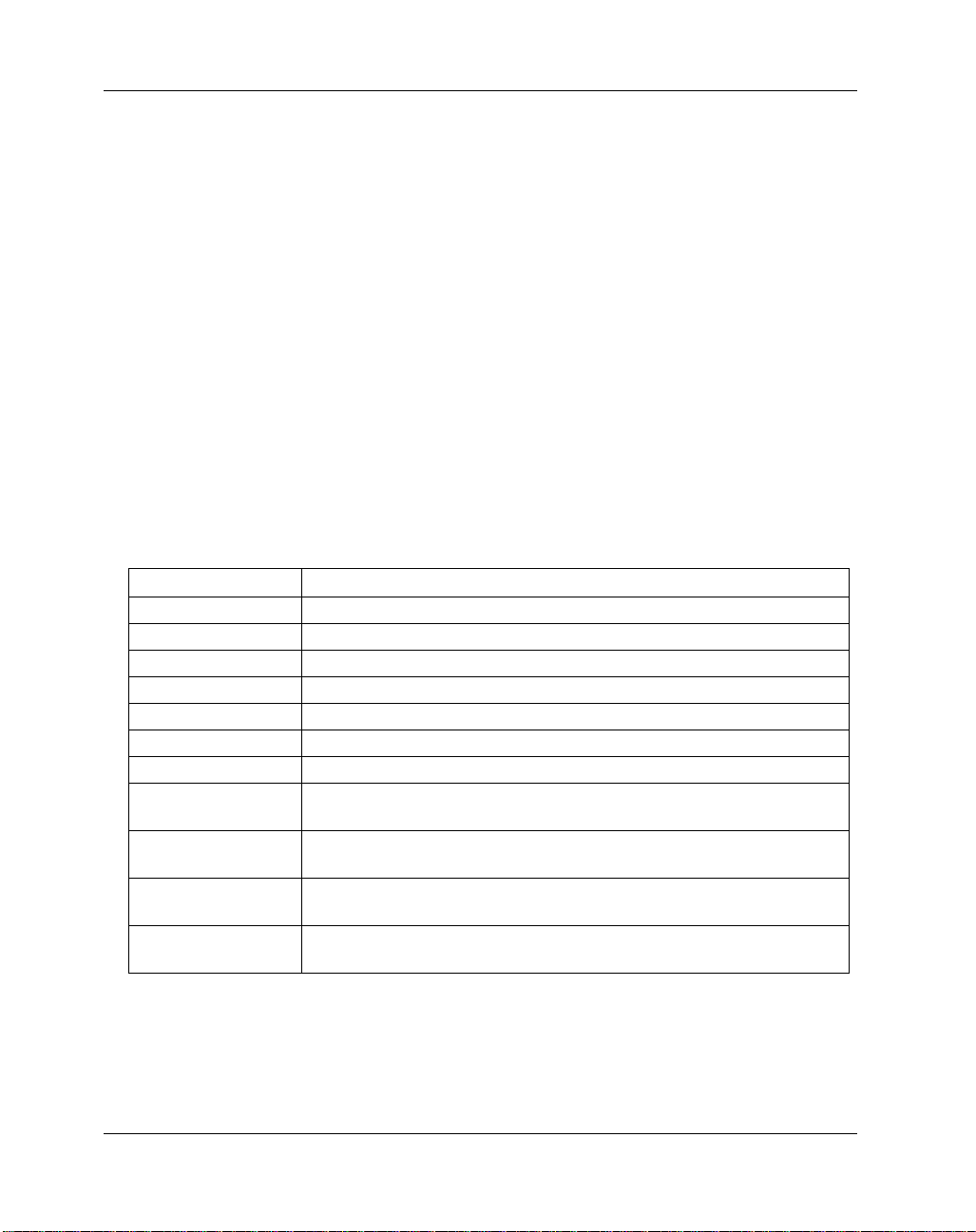

Currently, the boards are provided in the following configurations:

Part Number Description

MCPN750-1222 A MPC750, 266MHz, 16MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1232 A MPC750, 266MHz, 32MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1332 A MPC750, 366MHz, 32MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1342 A/B MPC750, 366MHz, 64MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1352 A/B MPC750, 366MHz, 128MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1362 A MPC750, 366MHz, 256MB ECC DRAM, 5MB FLASH, 1MB L2 Cache

MCPN750-1442 A MCP750, 466MHz, 64MB ECC DRAM, 5MB FLASH, 1M B L2 Cache

MCPN750-2342 A/B MPC750, 366MHz, 64MB ECC DRAM, 5MB FLASH, 1MB L2 Cache,

Transition Module, Ethernet Rear I/O

MCPN750-2352 A/B MPC750, 366MHz, 128MB ECC DRAM, 5MB FLASH, 1MB L2 Cache,

Transition Module, Ethernet Rear I/O

MCPN750-2352 A-F MPC750, 366MHz, 128MB EC C DRAM, 5MB FLASH, 1MB L2 Cache,

Transition Module, Ethernet Rear I/O

MCPN750-2362 A/B MPC750, 366MHz, 256MB ECC DRAM, 5MB FLASH, 1MB L2 Cache,

Transition Module, Ethernet Rear I/O

xvii

Page 18

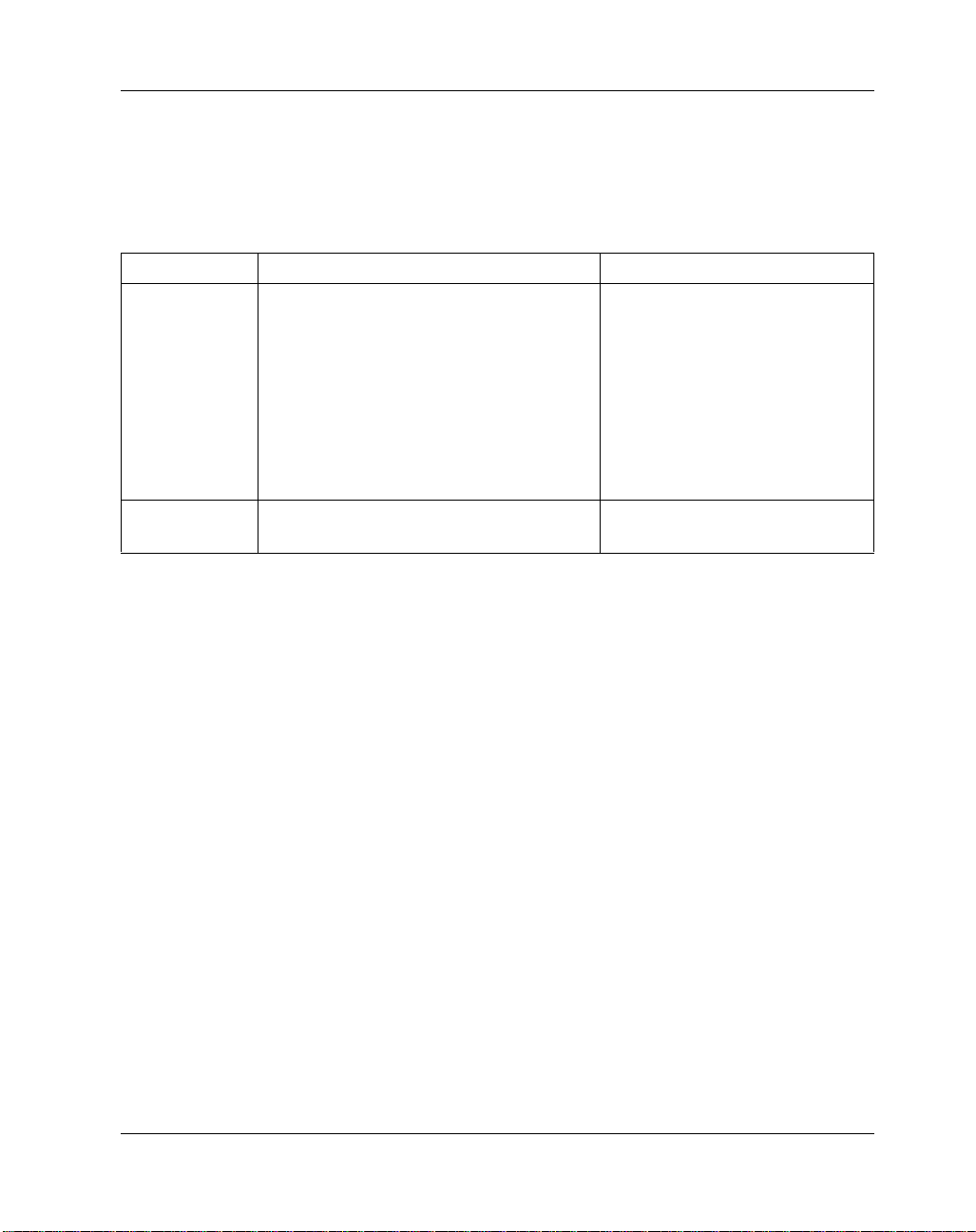

Summary of Changes

The followi ng is a list of cha nges made since the last release of this

manual.

Date Changes Replaces

09/01 Updated table of model numbers

preceeding this section.

Reinserted information left out of IH4

version of manual, which included

information on MCPN750A, the

TMCPN710 and the TM-PIMC-0001,

instead of the earlier MCPN750. Also,

included J8 jumper settings for StandAlone operation.

07/00 68-pin .08 Series Submi nature D PMC I/O

Connector.

Previously listed model numbers.

68-pin .050 Series Subminature

D PMC I/O Connector.

Overview of Contents

This section provides a brief overview of each chapte r and appendix within

this document.

xviii

Chapter 1, Hardware Preparation and Installation, provides a brief

product description and a block diagram. The remainder of the chapter

provides information on hardware preparation and installation

instructions, including peripheral boards such as the TMCPN710 or TMPIMC-0001 Transition Module.

Chapter 2, Startup and Ope ration, provides an o verview of basic oper ating

and configuring issues such as the PPCBug firmware, the memory maps,

interrupts, arbitration, sources of reset and endian issues.

Chapter 3, PPCBug, provides an overview and description of basic

PPCBug use including implement ation issues, a list of the initialization

sequence, a description of basic debugger commands, as well as a list of

diagnostic tests typically run.

Page 19

Chapter 4, CNFG and ENV Commands, provides an ex planation of two of

the more important PPCBug configuration commands: CNFG and ENV.

Includes information on how to configure the VMEbus and PCI bus

environments using the ENV command.

Chapter 5, Remote Start Via the PCI Bus, provides a description of the

remote start capability th at is availabl e via the PCI bu s using PPCBug

commands.

Chapter 6, Functional Description, provides a description of the major

components and functionality of the MCPN750A.

Chapter 7, Connector Pin Assignments, provides a listing of all major

connector pinout information for the MCPN750A, the TMCPN710, and

TM-PIMC-0001.

Appendix A, Specifications, provides basic board specification

information including recommendations on cooli ng and EMC compliance.

Appendix B, Related Documentation, provides a listing of related

motorola and vendor documentation, as well as a list of related industry

standard specifications.

Comments and Suggestions

Motorola welcomes and appreciates your comments on its doc umentation.

We want to know what y ou think about our manuals and how we can make

them better. Mail comments to:

Motorola Computer Group

Reader Comments DW164

2900 S. Diablo Way

Tempe, Arizona 85282

You can also submit comments to the following e-mail address:

reader-comments@mcg.mot.com

xix

Page 20

In all your corres pondence , plea se li st your name, po si tion, a nd compan y.

Be sure to include the title and par t number of the manual and tell how you

used it. Then tell us your feelings about its strengths and weaknesses and

any recommendations for improvements.

Conventions Used in This Manual

The following typographical conventions are used in this document:

bold

is used for user inpu t that you t ype just as i t appears ; it is al so used for

commands, options and arguments to commands, and names of

programs, directories and files.

italic

is used for names of variables to which you assign values. Italic is also

used for comments in screen dis plays and examples, and to intr odu ce

new terms.

courier

is used for system output (for example, screen displays, reports),

examples, and system prompts.

xx

<Enter>, <Return> or <CR>

<CR> represents the carriage return or Enter key.

CTRL

represents the Control key. Execute control characters by pr essing the

Ctrl key and the letter simultaneously, for example, Ctrl-d.

Page 21

1Hardware Preparation and

Introduction

This chapter provides startup and safety instructions related to this

product, hardware preparation instructions - including default jumper

settings, system considerations, and installation instructions for the

baseboard, as well as the PMCs and t ransition modules associate d with this

board.

A fully implemented MCPN750A consists of the baseboard plus:

❏ One or two optional PCI mezzanine cards (PMC) for additional

versatility

❏ One of two different types of optional transition modules: the

TMCPN710 or the TM-PIMC-0001 for added I/O flexibility

Product Description

The MCPN750A is a hot swappa ble CompactP CI, non-sys tem slot, single

board computer based on the PowerPlus architecture. It consists of the

MPC750 processor with L2 cache, the Raven PCI Bridge and Interrupt

Controller, the ECC Memory Controller Falcon chipset , 5MB of linea r

Flash memory, 16MB to 256MB of ECC protecte d DRAM, i nterf ac e t o a

CompactPCI bus, and several I/O peripherals.

Installation

1

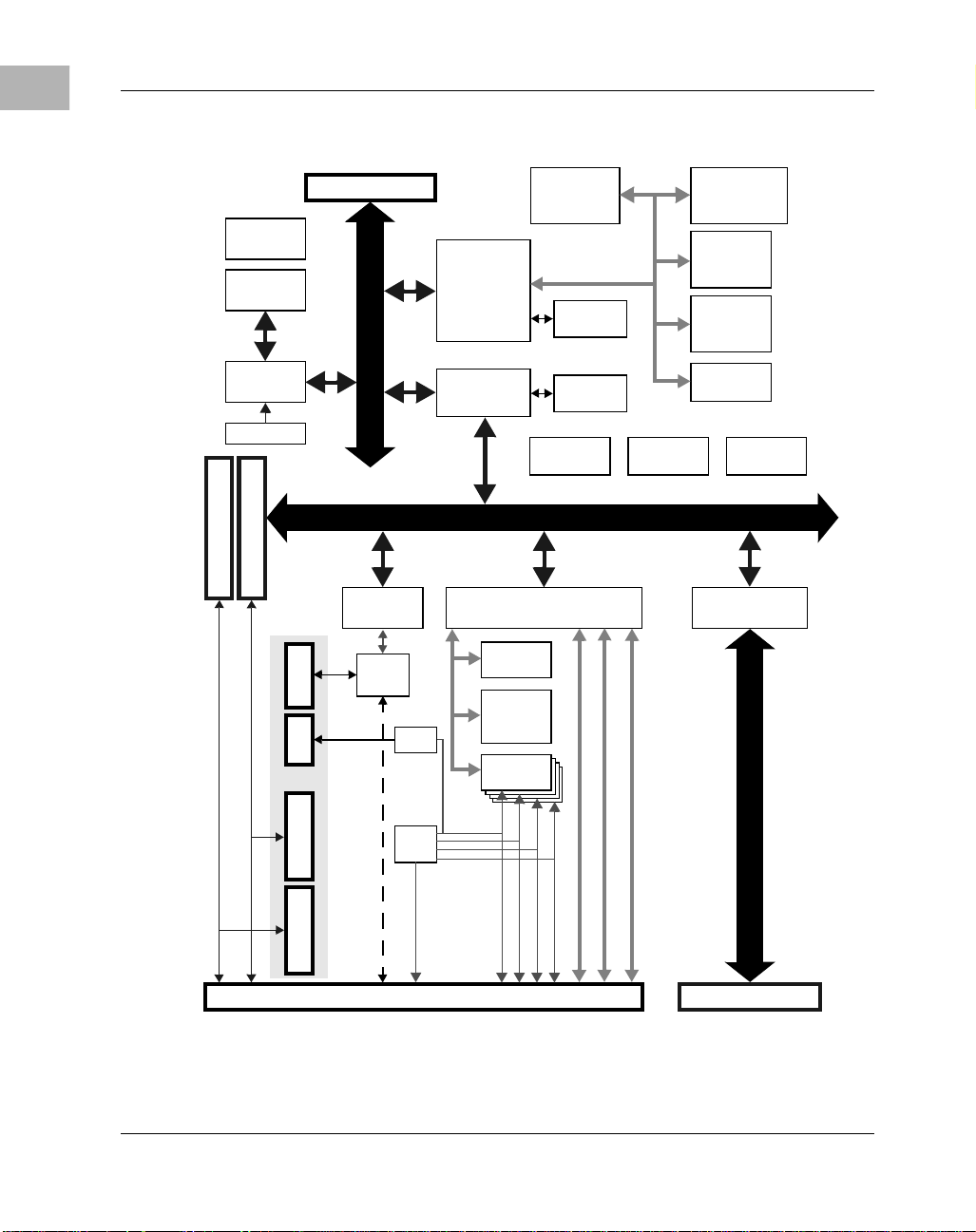

Block Diagram

The block diagram in Figure 1-1 illustrates the architecture of the

MCPN750A baseboard.

1-1

Page 22

1

Hardware Preparation and Installation

Arbitration

Control

L2 Cache

1M

Processor

MPC750

Core Power

32/64-bit PMC Slot 2

32/64-bit PMC Slot 1

Debug Connector

Ethernet

Intel 21143

EthernetSerialPMC Slot 2PMC Slot 1

100BTx

Bus

66MHz PPC603 Processor

10BT/

RS232

16M/64M/128M

Memory

Controller

Falcon 3

Chipset

PCI Bridge

& MPIC

Raven 5 ASIC

33MHz 32/64-bit PCI

PBC

VT82C586B

ISA

Registers

ISA

NVRAM/

WD/RTC

MK48T559

UARTs

16C550C

DRAM

(Bank 1)

SROM

AT24C04

Interrupt

Serializer

Clock

Generator

USB0

Local Bus

USB1

EIDE

Reset

Control

DRAM

(Bank 2)

16M/64M/128M

Flash

(soldered)

4M

Flash

(socketed)

1M

System

Registers

Hot Swap

Control

PCI-PCI BRIDGE

Intel 21554

Bus

IOMX

33MHz 32/64-bit CompactPCI

SERIAL 2

SERIAL 3

SERIAL 4

(OPTIONAL ROUTING TO TM)

SERIAL 1

CompactPCI J1/J2User I/O J3 & J5

Figure 1-1. MCPN750A Baseboard Block Diagram

1-2 Computer Group Literature Center Web Site

Page 23

Getting Started

Getting Started

This section provides an overview of the steps necessary to install and

power up the MCPN750A, any additional equipment requirements, and a

brief section on unpacki ng and ESD precautio ns. As identified in the table

below, several steps can be omitted if your board, for example, has been

shipped with PMCs and Flash already installed

Overview of Start-up Procedure

The following table li sts the th ings you will need to do bef ore you can use

this board and t ells where to find the infor mation you n eed to perform e ach

step. Be sure to rea d this entire c hapter, incl uding all Caution and Warning

notes, before you begin.

Table 1-1. Startup Overview

Task Section or Manual Reference Page

Unpack the hardware. Unpacking Instructions 1-5

Configure the hardware by

setting jumpers on the baseboard

and transition module.

Ensure CompactFlash card is

installed (if required)

Install the PMC Module (if

required)

Install the MCPN750A in the

chassis.

Install the transition module in

the chassis.

Connect any other equipment

you will be using .

Power up the system. Applying Power 2-1

MCPN750A Baseboard Preparation and

TMCPN710 or TM-PIMC-0001 Transition Module

Preparation

Compact Flash Memory Card Installation 1-6

PMC Module Installation 1-21

MCPN750A CompactPCI SBC Installation 1-24

TMCPN710 or TM-PIMC-0001 Transition Module

Installation

Connector Pin Assignments 7-1

For more information on optional devices and

equipment, refer to the d ocumentation provided with

the equipme nt .

1

1-6, 1-11,

and 1-16

1-26

http://www.motorola.com/computer/literature 1-3

Page 24

1

Hardware Preparation and Installation

Table 1-1. Startup Overview (Continued)

Task Section or Manual Reference Page

Note that the debugger in itializes

the MCPN750A

Initialize the system clock. Using the Debugger, Debugger Commands, the

Examine and/or change

environmental parameters.

Program the bo a r d as ne e de d for

your applications.

Using PPCBug 3-5

You may also wish to obtain the PPCBug Firmware

Package User’s Manual, listed in Appendix B,

Related Documentation.

SET command

CNFG and ENV Commands 4-2

MCPN750A CompactPCI Single Board Computer

Programmer’s Reference Guide, listed in Appendix

B, Related Documentation.

B-1

3-6

and 4-3

B-1

Equipment Required

The following equipment is required to complete an MCPN750A system:

❏ CompactPCI system enclosure

❏ System console terminal

❏ Operating system (and/or application software)

❏ Disk drives (and/or other I/O) and controllers

❏ Transition module (TMCPN710 or TM-PIMC-0001) and

connecting cables

MCPN750A baseboards are factory-configured for I/O handling via a

TMCPN710 or TM-PIMC-0001 transition module. There are currently

eight MCPN750A models corresponding to the five separate memory

configurations, t wo p rocessor spee ds and fron t or rea r et hernet I/O. Eith er

one of the aforementioned transition modules support all models of the

baseboard. Refer to the subsections on the MCPN750A and transition

module installation for more information.

1-4 Computer Group Literature Center Web Site

Page 25

Unpacking Instructions

Note If the shipping carton is damaged upon receipt, request that

the carrier’s agent be present during the unpacking and

inspection of the equipment.

Unpack the equipment from the shipping carton. Refer to the packing list

and verify that al l items are present . Sa ve t he packing material for storing

and reshipping of equipment.

Getting Started

1

!

Caution

Avoid touching areas of integrated circuitry; static discharge can damage

circuits.

ESD Precautions

Motorola strongly recommends that you use an antistatic wrist strap and a

conductive foam pad when installing or upgrading a system. Electronic

components, such as di sk driv es, comput er boar ds, and memory mod ules, c an

be extremely sensitive to ESD. After removing the component from the system

or its protective wrapper, place the component flat on a grounded, static-free

surface (and in the case of a board, component side up). Do not slide the

component over any surface.

If an ESD station is not available, you can avoid damage resulting from ESD

by wearing an antistatic wrist strap (available at electronics stores) that is

attached to an unpainted metal part of the system chassis.

Inserting or removing modules with power applied may result in damage

!

Caution

to module components.

Dangerous voltages, capable of causing death, are present in

!

Warning

http://www.motorola.com/computer/literature 1-5

this equipment. Use extreme caution when handling, testing,

and adjusting.

Page 26

1

Hardware Preparation and Installation

Preparation

This section discusses certain hardware and software tasks that may need

to be performed prior to installing the board in a CompactPCI chassis.

Hardware Configuration

To produce the desired configuration and ensure proper operation of the

MCPN750A, you may need to carry out certain hardware modifications

before installing the module.

The MCPN750A provides software control over most options by setting

bits in control registers after installing the module in a system. You can

also modify the board’s configuration by modifying similar control

registers. The MCPN750A control registers are described in the

MCPN750A CompactPCI Single Board Computer Programmer’s

Reference Guide (MCPN750A/ PG), whi ch can be accessed on line i n pd f

or html format through the Moto rola Comput er Group Liter ature web site

(http://www.motorola.c om/comp uter/li tera ture).

Some options, however, are not software-programmable. These options

are controlled by installing or removing header jumpers or interface

modules on the baseboard or the associated transition module.

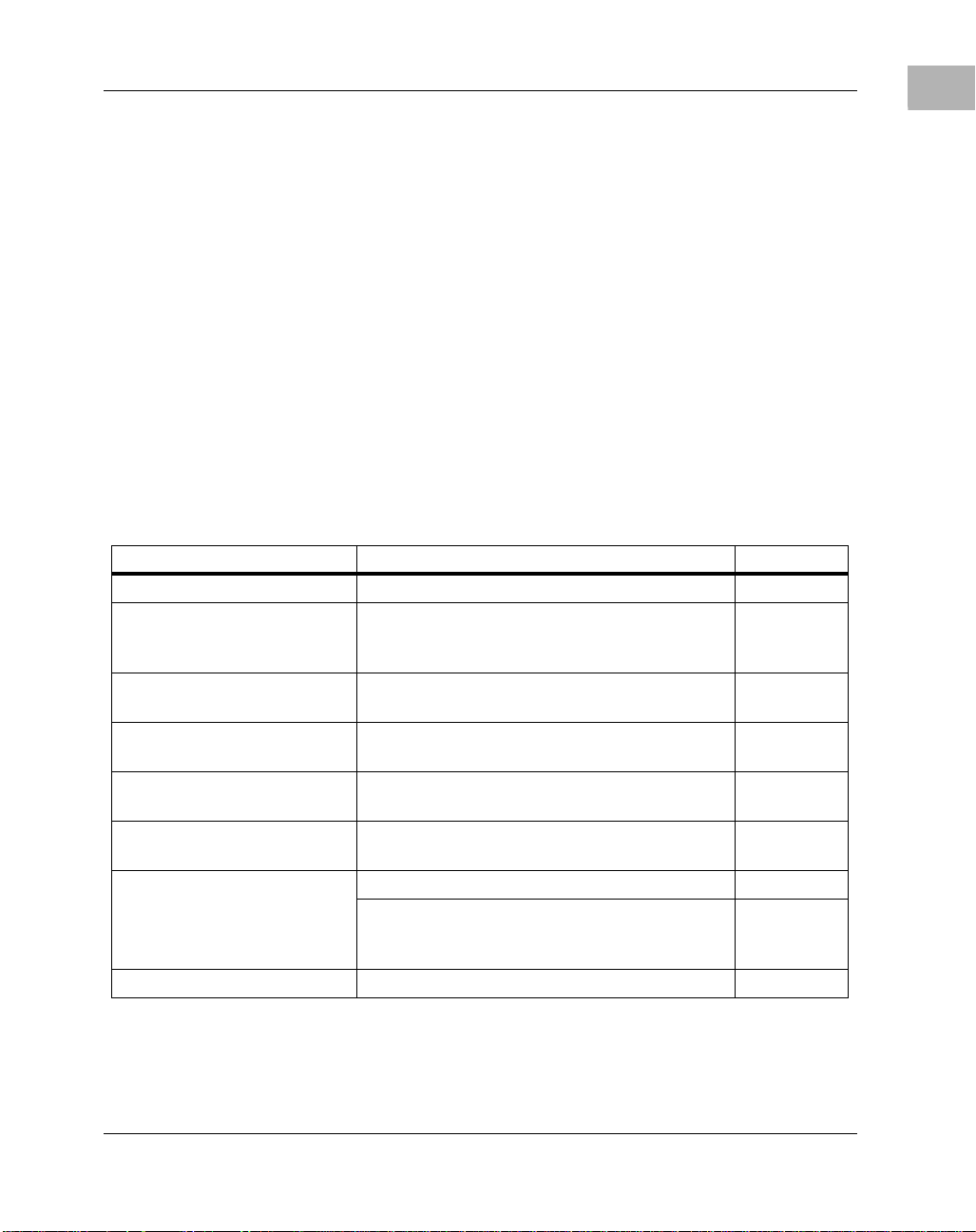

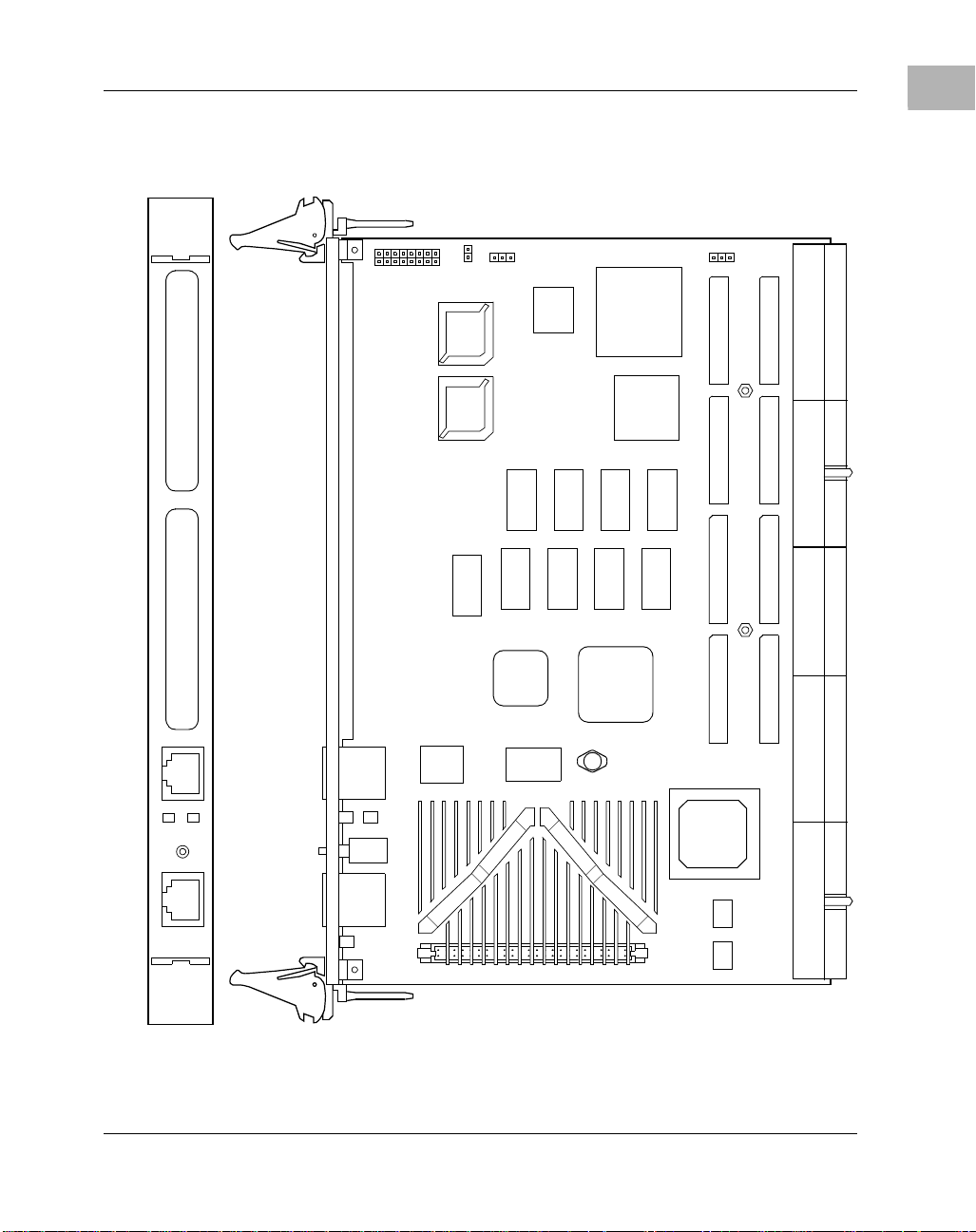

MCPN750A Baseboard Preparation

Figure 1-2 illustrates the placement of the switches, jumper headers,

connectors, and LED indicat ors on the MCPN750A. Manua lly configured

items on the baseboard include:

❏ Flash bank selection (J7)

❏ Stand-Alone Operating Mode (J8)

For a discussion of the configu red ite ms on th e trans itio n module , re fer in

this chapter to the sections titled TMCPN710 Transition Module

Preparation, or to the respec tive user’s manual s for the transit ion modules

(listed in the Related Documentation appendix) as necessary.

1-6 Computer Group Literature Center Web Site

Page 27

The MCPN750A is factory tested and shipped with the configurations

described in the following sections. The MCPN750A’s required and

factory-installed debug monitor, PPCBug, operates with those factory

settings.

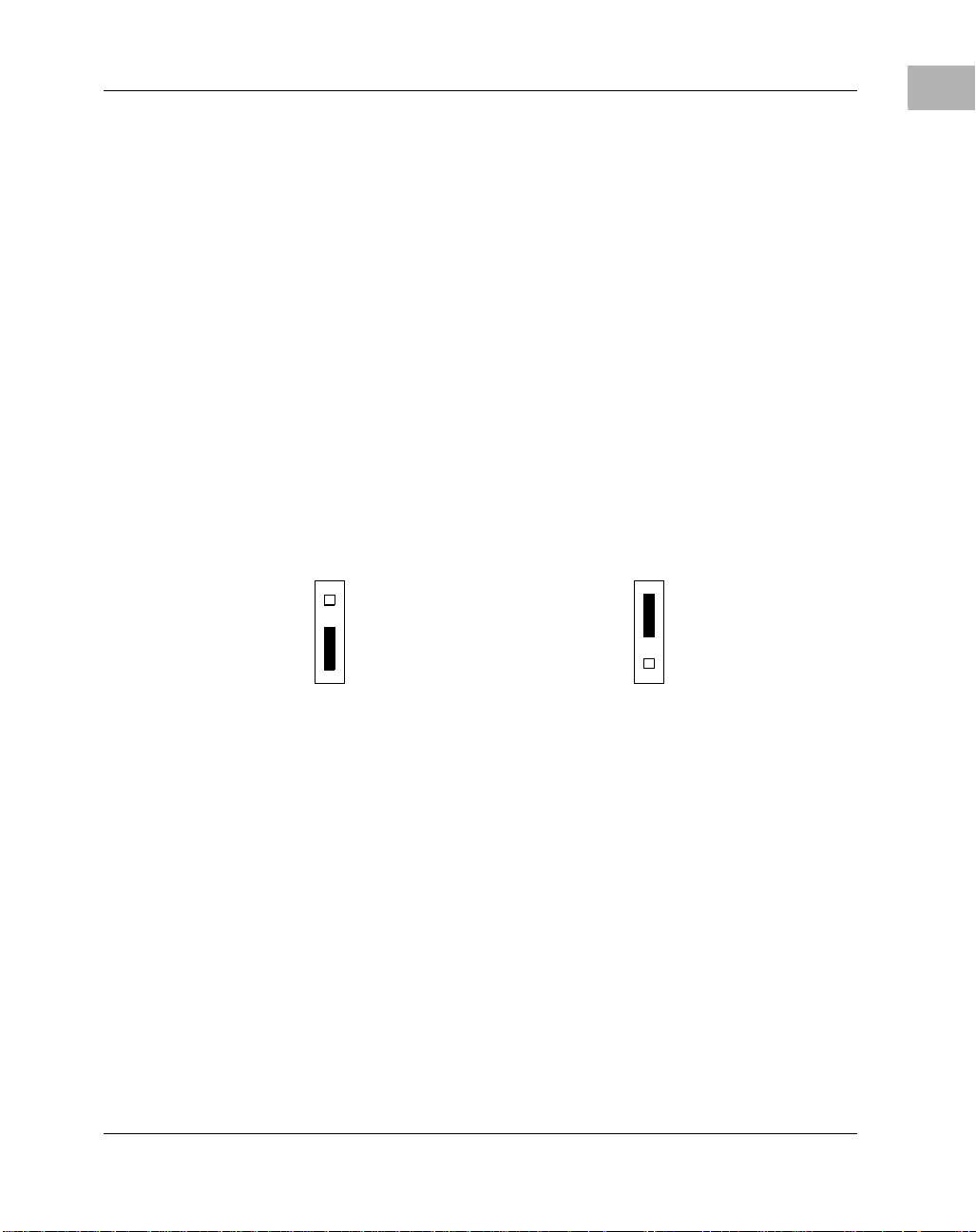

Flash Bank Selection (J7)

The MCPN750A baseboard has provision for 1MB of 16-bit Flash

memory and 4MB of linear Flash memory.

The Flash memory is organized in two banks, Bank A is 64 bits wide and

Bank B is 16 bits wide. Bank B contains the onboard debugger, PPCBug.

To enable Flash Bank A, place a j umper acr oss he ader J 7 pins 1 and 2. T o

enable Fla sh Bank B (1MB of firmware located in sockets on the

baseboard), place a jumper across header J7 pins 2 and 3.

Preparation

1

J7J7

3

2

1

Flash Bank A Enabled (4MB Soldered)

Flash Bank B Enabled (1MB, Sockets)

3

2

1

(Factory Configuratio n)

Note Placing a ju mper on Fl ash pr ogramming header J9 has no aff ect.

The Flash programming for Bank A is permanently ena bled with

onboard resistors.

http://www.motorola.com/computer/literature 1-7

Page 28

1

Hardware Preparation and Installation

Stand-Alone Operating Mode (J8)

The MCPN750A has a stand-alone operating mode that allows the

MCPN750A to function withou t t he clock from the sys tem sl ot con tr oll er

board. Installi ng a jumper across p ins 1 and 2 of J8 enab les the stan d-alone

mode. The J8 jumper must be removed for normal operation.

J8J8

2

1

Enables Stand-Alone mode

Remove jumper for normal operation

2

1

(Factory Configuratio n)

Note An MCPN750A configured for stand-alone mode should not be

installed in a chassis with a system slot con troller board. T his will

result in unpredictable system operation. See the section on

System Considerations for additional information.

1-8 Computer Group Literature Center Web Site

Page 29

Preparation

1

21

3

1

1516

J7

12

J6

PCI MEZZANINE CARD 2

PCI MEZZANINE CARD 1

J8

U2

XU1 XU2

U7

U6

U14

U13

U12

U20

U15

U1

U5

U9

U8

U16

U23

3

1

J9

2

1

63

1

63

1

63

1

2

1

J21

64

2

J23

64

2

J11

64

2

J13

J5 J4 J3 J2 J1

J22

64

63

2

1

J24

64

63

2

1

J12

64

63

2

1

J14

10/100 BASE T

BFL

COM 1

CPU

ABT/RST

63

J18 J19

DS2

DS1

S1

DS3

U35

L2

U31

64

63

Q3 Q4

64

2703 0002

Figure 1-2. MCPN750A Switches, Headers, Connectors, Fuses, LEDs

http://www.motorola.com/computer/literature 1-9

Page 30

1

Hardware Preparation and Installation

System Considerations

The MCPN750A is designed to operat e as a CompactPCI no n-system sl ot

board. Consequently, the MCPN750A must be installed in the subrack

system slot marked with the circle symbol.

The MCPN750A can operate properly, with or without a system slot

controller board. In the standard operating mode (with a system slot

board), the system slot board is used to provide clock and arbitration

signals to the MCPN750A. In t he sta nd-alo ne mode, a j umper mu st be se t

on the MCPN750A, in order to obtain clock signals from other on-board

devices.

Installing a jumper on J8 ro utes an onboard PCI clock to the 21554 pri mary

side clock input. This allows the MCPN750A to operate in a chassis

without a system sl ot c ont roller board instal led. The chassis must pr ovi de

+5V, +3.3V, +12V, -12V and VIO to the MCPN750A, and the BD_SEL

pin (P1-D15) in the chassis must be grounded. In addition, in the standalone mode, the MCPN750A cannot communicate over the CompactPCI

backplane.

On the MCPN750A baseboard, the standard serial console port (

COM1)

serves as the PPCBug debugg er console port. The fir mware console should

be set up as follows:

❏ Eight bits per character

❏ One stop bit per character

❏ Parity disabled (no parity)

❏ Baud rate of 9600 baud

9600 baud is the power-up defaul t for serial p orts o n MCP N750A board s.

After power-up you can reconfigure the baud rate if you wish, using the

PPCBug PF (Port Format) command via the command line interface.

Whatever the baud rate, some type of hardware handshaking — either

XON/OFF or via the RTS/CTS line — is desirable if the system supports

it.

1-10 Computer Group Literature Center Web Site

Page 31

TMCPN710 Transition Module Preparation

The TMCPN710 transition module (Figure 1-3) is used in conjunction

with all models of the MCPN750A baseboard:

The features of the TMCPN710 include:

❏ Two EIA-232-D asynchrono us serial port s (ide ntif ied as COM1 and

COM2

on the transition module panel)

❏ Two USB Series A connectors for USB interface

❏ One 10/100BaseT connector for ethernet connections (requires

MCPN750A Transition module/ethernet option)

❏ Two 68-pin .08 Series Subminiature D connectors for PMC I/O

❏ Two 50-pin on-board connectors for EIDE interface to one or two

Compact Flash plug-in modules

Preparation

1

http://www.motorola.com/computer/literature 1-11

Page 32

1

Hardware Preparation and Installation

2286 9806

82

71

J13

10/100 BASE T

41

J12

41

J10

82

71

J11 J14

13

J7

J3 J5J4

J16

(Slave)

(Master)

J15

J8

82

71

J6

J2J1

USB 1

USB 0

COM 2

COM 1 PMC2 I/O

PMC1 I/O

Figure 1-3. TMCPN710 Connector and Header Locations

1-12 Computer Group Literature Center Web Site

Page 33

Serial Ports 1 and 2

On the TMCPN710, the asynchronous serial ports (Serial Ports 1 and 2)

are configured permanently as data circuit-terminating (Figure 1-4)

equipment (DTE). The COM1 p ort i s a ls o r outed to a RJ-45 connec to r o n

the front panel of the processor board. A terminal for COM1 may be

connected to either the processor board or the transition module, but not

both.

Jumper J7 on the transition module must be configured to enable COM1

on either the transition module or the processor board. To enable the

COM1 port on the transition module, connect pins 2-3 of J7. To enable

COM1 on the processor board, connect pins 1-2 of J7.

Preparation

1

J7

123

Enable COM1 on TMCPN710 Enable COM1 on MCPN750A

J7

1

Serial Port 1 jumper settings

23

(factory configuration)

Note If the J7 jumper is not present on the TMCPN710, the board

automatically enables COM1 on the MCPN750A.

http://www.motorola.com/computer/literature 1-13

Page 34

1

Hardware Preparation and Installation

MCPN750A

RJ45

1

8

7

COM1

(front pa nel)

2

5

4

3

6

16C550

SOUT

16C550

SOUT

SIN

RTS

CTS

DTR

DCD

DSR

DSR

DCD

DTR

CTS

RTS

SIN

TMCPN710

J7

COM1

(rear panel)

4

5

2

7

8

1

J3

RI

IO

MUX

RI

IO

MUX

3

6

COM2

(rear panel)

1

8

7

2

5

4

3

6

2362 9808

Figure 1-4. MCPN750A/TMCPN710 Serial Ports 1 and 2

1-14 Computer Group Literature Center Web Site

Page 35

COM3 and COM4 Asynchronous Serial Ports

The signals for COM3 and COM4 s erial port s are r outed to headers on the

TMCPN710 Transition Module. These headers are intended for debug

purposes only. Figure 1-5 depicts this configuration.

Preparation

1

16C550

SOUT

16C550

SOUT

SIN

RTS

CTS

DTR

DCD

DSR

DSR

DCD

DTR

CTS

RTS

SIN

RI

RI

MCPN750A

IO

MUX

TMCPN710

J11

3

5

7

9

Com3

Header

14

15

J3

IO

MUX

11

18

13

J14

18

11

15

Com4

Header

14

9

7

5

3

13

2363 9808

Figure 1-5. TMCPN710 Serial Ports 3 and 4

http://www.motorola.com/computer/literature 1-15

Page 36

1

Hardware Preparation and Installation

TM-PIMC-0001 Transition Module Preparation

The TM-PIMC-0001 transiti on module (Figure 1-6) is used i n conjunction

with all models of the MCPN750A baseboard. The features of this

transition module include:

❏ Connections for two single wide, or one double wide PIM card.

❏ Two asynchronous serial ports using RJ-45 connectors labeled as

COM1 and COM2.

❏ Two asynchronous serial ports using 10-pin headers labeled as

COM3 and COM4.

❏ One ethernet port using an RJ-45 connector

❏ One IDE Flash connector using a standard 50-pin CompactFlash

socket.

1-16 Computer Group Literature Center Web Site

Page 37

Preparation

1

2694 0001

J16

8

1

J20

63

1

J24

63

1

J10

J3 J5J4

63

1

1

2

64

2

64

2

64

2

J14

63

64

J13

1

9

2

1

9

J12

2

J1

82

71

J7

10/100 BASE T PMC I/O MODULE 1 PMC I/O MODULE 2

82

J11

3

3

J2

71

J8

1

1

82

71

J9

COM 2

COM 1

Figure 1-6. TM-PIMC-0001 Connector and Header Locations

http://www.motorola.com/computer/literature 1-17

Page 38

1

Hardware Preparation and Installation

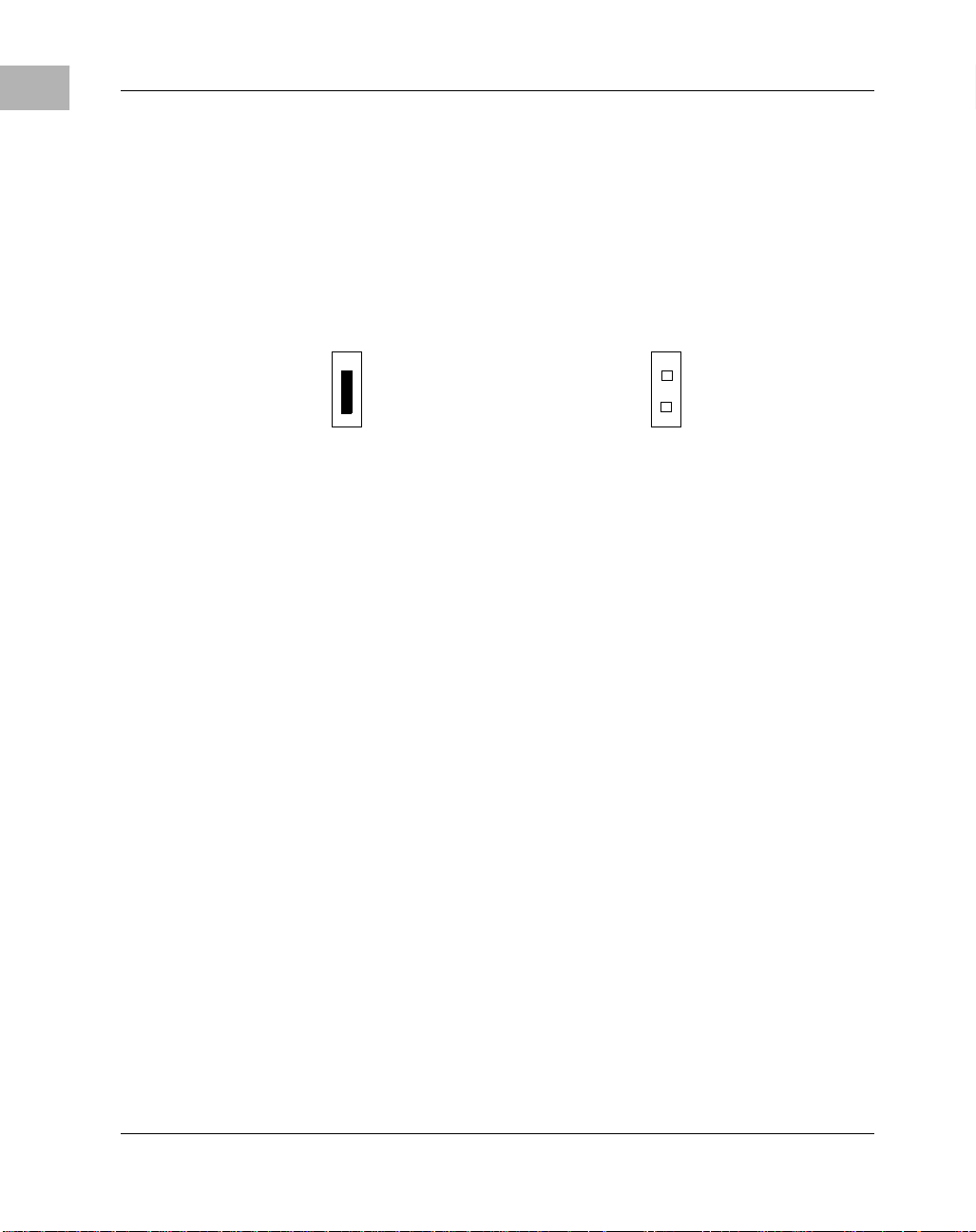

COM1 and COM2 Asynchronous Serial Ports

On the TM-PIMC-0001, the asynchronous serial ports (COM1 and

COM2) are configured permanently as data circuit-terminating

(Figure 1-7) equipment (DTE). The COM1 port is also routed to an RJ45

connector on the front panel of the proce ssor board. A terminal for COM1

may be connected to either the processor board or the transition module,

but not both.

Jumper J11 on the transit ion module must be con figur ed to ena ble COM1

on the processor board. If J11 is not configured, COM1 is automatically

routed to PIM 1 on the transition module. Jumper J2 on the transition

module must be configured in the same way for the COM2 port.

J11

123

Enable COM1 for PIM1 Enable COM1 on MCPN750A

of TM-PIMC-0001

J2

123

Enable COM2 for PIM2 Enable COM2 on MCPN750A

of TM-PIMC-0001

J11

1

J2

1

Serial Port 1 jumper settings

23

Serial Port 2 jumper settings

23

1-18 Computer Group Literature Center Web Site

Page 39

Preparation

1

COM1

(front panel)

RJ45

1

8

7

2

5

4

3

6

16C550

16C550

SOUT

SIN

RTS

CTS

DTR

DCD

DSR

DSR

DCD

DTR

CTS

RTS

SIN

SOUT

MCPN750

RI

RI

IO

MUX

TM-PIMC-0001

PIM 1

J11

COM1

(rear panel)

4

5

IO

MUX

J3

IO

MUX

IO

MUX

J2

2

7

8

1

3

6

COM2

(rear panel)

1

8

7

2

5

4

3

6

PIM 2

2362 0001

Figure 1-7. MCPN750A/TM-PIMC-0001 Serial Ports 1 and 2

http://www.motorola.com/computer/literature 1-19

Page 40

1

Hardware Preparation and Installation

COM3 and COM4 Asynchronous Serial Ports

The signals for COM3 and COM4 serial por ts are routed to 10-pin he aders

on the TM-PIMC-0001 Transition Module (J12 and J13). These headers

function as I/O connectors for the MCPN750A and are permanently

configured as DTE. Figure 1-8 depicts this configuration.

16C550

SOUT

16C550

SOUT

SIN

RTS

CTS

DTR

DCD

DSR

RI

RI

DSR

DCD

DTR

CTS

RTS

SIN

MCPN750A

IO

MUX

TM-PIMC-0001

J12

5

3

4

6

Com3

Header

7

1

J3

IO

MUX

2

8

9

J13

8

2

1

Com4

Header

7

6

4

3

5

9

2363 0001

Figure 1-8. TM-PIMC-0001 Serial Ports 3 and 4

1-20 Computer Group Literature Center Web Site

Page 41

Hardware Installation

The following section s discuss the placement of PMC mez zanine cards on

the MCPN750A baseboard and the installation of the complete

MCPN750A assembly into a CompactPCI chassis. Before installing the

MCPN750A, ensure that all header jumpers are configured as desired.

In most cases, PMC modules ordered with the baseboard are installed on

the MCPN750A at the facto ry and the order is shipped as a si ngle unit. The

user-configured jumpe rs on the PM Cs are a ccess ibl e with the mez zanin es

installed.

If it is necessary to install mezzanines on the baseboard, refer to the

following sections for a brief description of the installation procedure.

Note: the procedure assumes the MCPN750A has already be en installed in

the chassis. If not, begin with Step 4.

Avoid touching areas of integrated circuitry; static discharge can damage

!

Caution

these circuits.

Hardware Installation

1

Installing PMC Modules on the MCPN750A SBC

One dual wide, one single wide or two singl e wide PCI mezzan ine (PMC)

modules can be mounted on top of the MCPN750A baseboard. The

MCPN750A is designed to accept only +5V or Universal PMCs. Due to

pin current limitations, the MCPN750A can supply up to 4.5 amps to a

single PMC on each of the +3.3V and +5V supplies. The MCPN750A can

supply a maximum of 500mA at +12V and -12V t o each PMC. Refer to the

table on page 1-31 for the total current available to PMC’s and transition

modules. To install a PMC module, refer to Figure 1-9 PMC Carrier Board

Placement on MCPN750A, and proceed as follows:

1. Attach an ESD strap to your wri st. Att ach the o ther en d of the ESD

strap to the chassis as a ground. The ESD strap must be secured to

your wrist and to ground throughout the procedure.

2. Perform an operating system shutdown. Turn the AC or DC power

off and remove the AC cord or DC power lines from the system.

http://www.motorola.com/computer/literature 1-21

Page 42

1

Hardware Preparation and Installation

3. Remove chassis or system cover(s) as necessary for access to the

CompactPCI.

2288 9806

Figure 1-9. PMC Module Placement on MCPN750A

Inserting or removing modules in a non-hot swap chassis with power

!

Caution

!

Warning

1-22 Computer Group Literature Center Web Site

applied may result in damage to modul e component s. The MCPN750A is

a hot swappable board and may be inserted in a hot swap chassis, such as

a CPX2000 or a CPX8000 series chassis with power applied.

Dangerous voltages, capable of causing death, are present in

this equipment. Use extreme caution when handling, testing,

and adjusting.

4. Carefully remove the MCPN750A from its CompactPCI card slot

and lay it flat, with connectors J1 through J5 facing you.

Page 43

!

Caution

Hardware Installation

1

Avoid touching areas of integrated circuitry; static discharge can damage

these circuits.

5. Remove the PMC filler from the front panel of the MCPN750A.

6. Slide the edge connector of the PMC module into the front panel

opening from behind and place the PMC module on top of the

baseboard. The four connectors on the underside of the PMC

module should then connect smoothly with the corresponding

connectors (J11/12/13/14) on the MCPN750A.

7. Insert the four short Phillips screws, provided with the PMC,

through the holes on the bottom side of the MCPN750A into the

PMC front bezel and rear standoffs. Tighten the screws.

8. Reinstall the MCPN750A assembly in its proper card slot. Be sure

the module is well seated in the backplane connectors. Do not

damage or bend connector pins.

9. Replace the chassis or syst em cover( s), reco nnect the sys tem to the

AC or DC power source, and turn the equipment power on.

Note If the PMC provides rear I/O, refer to Chapter 7, Connector Pin

Assignments for the pin assignments. Connectors on the

TMCPN710 and TM-PIMC-0001 provide rear panel access to

these signals.

http://www.motorola.com/computer/literature 1-23

Page 44

1

Hardware Preparation and Installation

Installing the MCPN750A Baseboard

With mezzanine board(s) installed (if applicable) and headers properly

configured, proceed as follows to install the MCPN750A in the

CompactPCI chassis:

1. Attach an ESD strap to your wri st. Att ach the o ther en d of the ESD

strap to the chassis as a ground. The ESD strap must be secured to

your wrist and to ground throughout the procedure.

2. In a non-hot swap system, perform an operating system shutdown.

Turn the AC or DC power off and remove the AC cord or DC power

lines from the system. Remove chassis or system cover(s) as

necessary for access to the CompactPCI modules.

Inserting or removing modules in a non-hot swap chassis with power

!

Caution

applied may result in damage to modul e component s. The MCPN750A is

a hot swappable board and may be inse rted in a h ot swap c hassis such as a

CPX2000, or a CPX8000 series chassis with power applied.

Dangerous voltages, capable of causing death, are present in

this equipment. Use extreme caution when handling, testing,

and adjusting.

3. Remove the filler panel from the appropriate non-system card slot.

4. Set the VIO on the backplane to either +3.3V or +5V (the

MCPN750A is a Universal board), depending upon your cPCI

system signaling requirements and ensure the backplane does not

bus J3, or J5 signals.

5. Slide the MCPN750A into the appropriate non-system slot.

Grasping the top and bottom inject or handles, be sure the module is

well seated in the P1 through P5 connectors on the backplane. Do

not damage or bend connector pins.

1-24 Computer Group Literature Center Web Site

Page 45

!

Caution

Hardware Installation

1

Avoid touching areas of integrated circuitry; static discharge can damage

these circuits

6. Secure the MCPN750A in the chassis with the screws provided,

making good contact wi th the transverse mou nting rails to minimize

RF emissions.

7. Replace the chassis or system cover(s), making sure no cables are

pinched. Cable the peripherals to the panel connectors, reconnect

the system to the AC or DC power source, and turn the equipment

power on.

http://www.motorola.com/computer/literature 1-25

Page 46

1

Hardware Preparation and Installation

Installing a TMCPN710 or TM-PIMC-0001 Transition Module

The TMCPN710 or TM-PIMC-0001 Transition Module may be required

to complete the configu ration of your particular MCPN750A system. If so,

perform the foll owi ng in stall steps to instal l th is board. For more detail ed

information on the TMCPN710 or TM-PIMC-0001 Transition Module

refer to the corresponding use rs guide, i.e., TMCPN710 Transition Mod ule

Installation and Use (TMCPN710A/ IH) or TM-PIMC-0001 Transition

Module Installation and Use (TMPIMCA/IH) manual.

Installing PIMs on the TM-PIMC-0001 Transition Module

If PIMs have already been installed on the TM-PIMC-0001, or you are

installing a transition module as it has been shipped from the factory,

disregard this section, and proceed to the main installation section titled

“Installing the Transition Module in the Chassis.” For PIM installation

perform the following steps:

1. Attach an ESD strap to your wri st. Att ach the o ther en d of the ESD

strap to the chassis as a ground. The ESD strap must be secured to

your wrist and to ground throughout the procedure.

2. Perform an operating system shutdown. Turn the AC or DC power

off and remove the AC cord or DC power lines from the system.

3. Remove chassis or system cover(s) as necessary for access to the

CompactPCI.

1-26 Computer Group Literature Center Web Site

Page 47

Hardware Installation

1

2695 0001

Figure 1-10. Installing a PIM on the TM-PIMC-0001 Transition Module

Inserting or removing modules in a non-hot swap chassis with the power

!

Caution

http://www.motorola.com/computer/literature 1-27

applied may result in damage to the module components. The TM-PIMC0001 is not a hot swap board, but it may be in stal led in a hot swap cha ssis

with power applied, if the corresponding MCPN750A is removed before

the TM-PIMC-0001 board is installed.

Page 48

1

Hardware Preparation and Installation

Dangerous voltages, capable of causing death, are present in

!

Warning

this equipment. Use extreme caution when handling, testing,

and adjusting.

4. Carefully remove the TM-PIM C -0001 from its CompactPCI card

slot and lay it flat on a stable surface.

5. Remove the PIM filler from the front panel of the TM-PIMC-0001

transition module.

6. Slide the face plate (front bezel) of the PIM module into the front

panel opening from be hind and p lace the PI M modul e on t op of the

transition module, aligned with the appropriate two PIM

connectors. The two connec tors on the underside of the PIM module

should then connect smoothly with the corresponding connectors

(J10/J14 or J20/J24) on the TM-PIMC-0001.

7. Insert the four short Phillips screws, provided with the PIM, through

the holes on t he bottom side of the TM-PIMC-000 into the PIM

front bezel and rear standoffs. Tighten the screws.

8. Reinstall the TM-PIMC-0001 assembly in its proper card slot. Be

sure the module is well seated in the backplane connectors. Do not

damage or bend connector pins.

9. Replace the chassis or syst em cover( s), reco nnect t he syste m to the

AC or DC power source, and turn the equip ment power on, or if hot

swapping, you may now install the MCPN750A.

Installing the Transition Module in the Chassis

1. Attach an ESD strap to your wri st. At tach t he oth er end of the st rap

to the chassis as a ground. The ESD strap must be secured to your

wrist and to ground throughout the procedure.

2. Perform an operating syst em shut down. Tur n the AC or DC power

off and remove the AC cord or DC power lines from the system.

Remove chassis or system cover(s) as necessary for access to the

chassis backplane.

1-28 Computer Group Literature Center Web Site

Page 49

!

Warning

!

Caution

Hardware Installation

1

Dangerous voltages, capable of causing death, are present in

this equipment. Use extreme caution when handling, testing,

and adjusting.

Avoid touching areas of integrated circuitry; static discharge can damage

these circuits.

3. With the TMCPN710 or TM-PIMC-0001 in the correct vertical

position that matches the pin positioning of the corresponding

MCPN750A board carefully slide the transition module into the

appropriate slot and sea t ti ghtl y into the backpla ne. Ref er to Figure

1-11. TMCPN710 or TM-PIMC-0001/MCPN750A Mating

Configuration for the correct board/connector orientation.

4. Secure in place with the sc rews provided, making good con tact with

the transverse mounting rails to minimize RF emissions.

5. Replace the chassis or system cover(s), making sure no cables are

pinched. Cable the peripherals to the panel connectors, reconnect

the system to the AC or DC power source, and turn the equipment

power on.

http://www.motorola.com/computer/literature 1-29

Page 50

1

Hardware Preparation and Installation

MCPN750A

P5

P4

P3

P2

P1

P5

P4

P3

TMCPN710

or

TM-PIMC-0001

Figure 1-11. TMCPN710 or TM-PIMC-0001/MCPN750A Mating Configuration

1-30 Computer Group Literature Center Web Site

Page 51

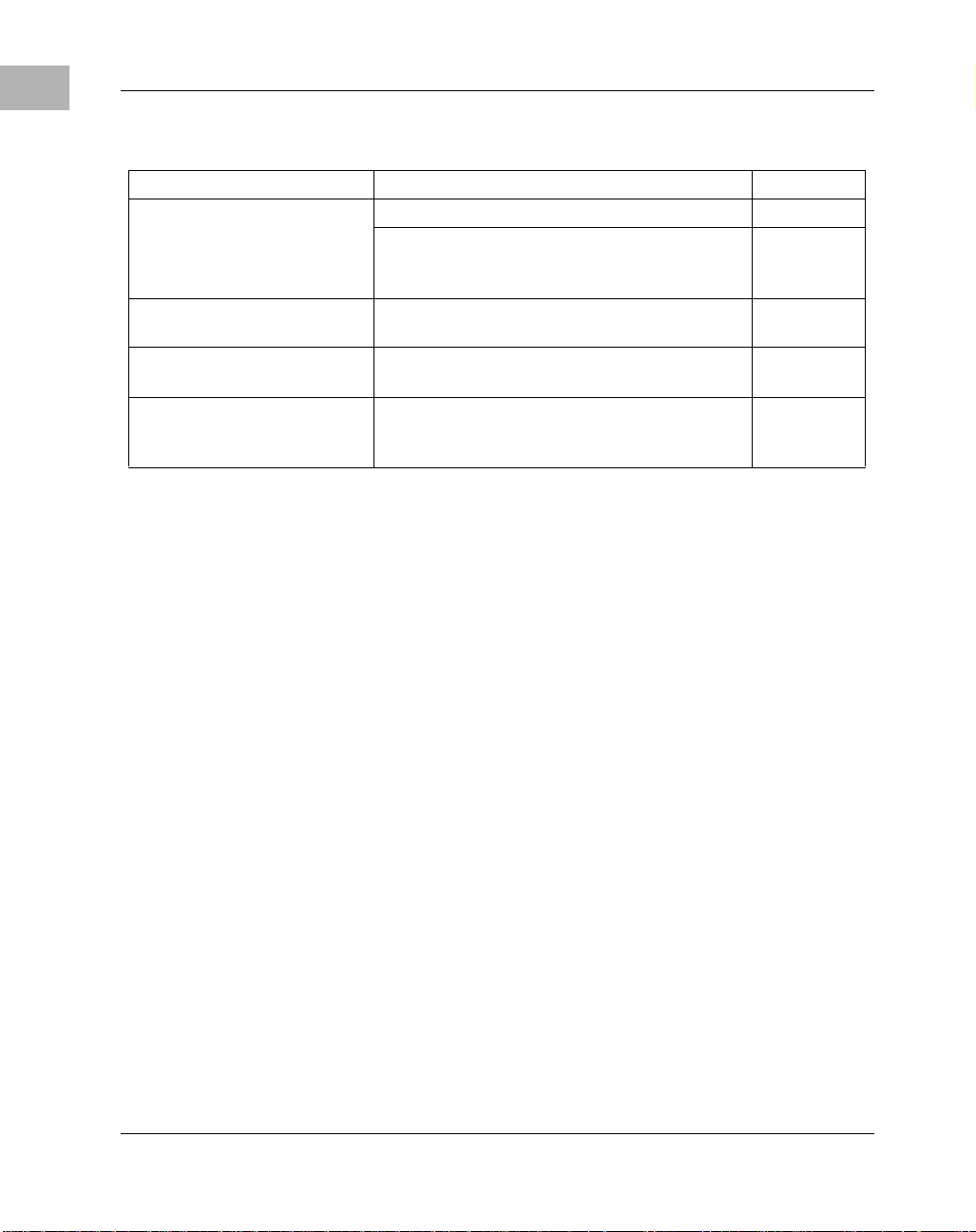

MCPN750A Module Power Requirements

MCPN750A Module Power Requirements

The MCPN750A board draws +5V, +3.3V and VIO power from the J1

connector. The +12V and - 12V voltages are moni tored by the MCPN750A

hot swap controller and provided for use by the PMCs and transition

modules. The MCPN750A contains an elect ronic circuit breaker that limits

the total +5V, +3.3V, +12V and -12V current drawn by the MCPN750A.

Refer to the table below for the electrical current available to the PMCs and

transition modules and Appendix A for other specs.

Voltage Current Available to PMCs & Transition Modules

+5.0V 6 Amps

+3.3V 6 Amps

+12.0V 1 Amp

-12.0V 0.4 Amp

1

http://www.motorola.com/computer/literature 1-31

Page 52

1

Hardware Preparation and Installation

1-32 Computer Group Literature Center Web Site

Page 53

2Startup and Operation

Introduction

This chapter supplies information for use of the MCPN750A family of

Single Board Computers in a s ystem configur ation. Here you will fi nd the

power-up procedure and descriptions of the switches and LEDs, memory

maps, and software initialization.

Applying Power

After you have verified that all necessary hardware preparation has been

done, that all connections have been made correctly, and that the

installation is complete, you can power up the system. The MPU,

hardware, and firmware initialization process is performed by the

PowerPC™ PPCBug power-up or system reset. The firmware initializes

the devices on the SBC module in preparation for booting the operating

system.

2

The firmware is shipped from the factory with an appropriate set of

defaults. In most cases the re is no need to modify the firmware

configuration before you boot the operating system.

The following flowchart shows the basic initialization process that takes

place during PowerPC system startup.

For further information on PPCBug, refer to Chapters 3 and 4 in this

manual, or to the PPCBug Firmware Package User’s Manual.

2-1

Page 54

Startup and Operation

2

STARTUP

SYSTEM

INITIALIZATION

CONSOLE

DETECTION

RUN SELFTESTS

(IF ENABLED)

AUTOBOOT

(IF ENABLED)

OPERATING

SYSTEM

1173 4. 00 9702

Figure 2-1. PPCBug System Startup

The MCPN750A front panel has one

(light-emitti ng diode) status indi cators (

ABORT/RESET switch and three LED

BFL, CPU, and HOT SWAP STATUS).

For more information on front panel operation refer to Chapter 6,

Functional Description.

2-2 Computer Group Literature Center Web Site

Page 55

Memory Maps

Memory Maps

There are three points of view for memory maps:

❏ The mapping of all resou rces as vi ewed by t he proce ssor (MPU bus

memory map)

❏ The mapping of onboard resources as viewed by PCI local bus

masters (PCI bus memory map)

❏ The mapping of onboard resources as viewed by the CompactPCI

bus.

The following sections give a general description of the MCPN750A

memory organization from the above three points of view. Detailed

memory maps can be found in t he MCPN750A CompactPCI Single Board

Computer Programmer’s Reference Guide (MCPN750A/PG).

Processor Memory Map

The processor memory map configuration is under the control of the

Raven bridge control ler ASI C and the Fal con me mory c ont roll er chip set.

The Raven and Falcon devices adjust system mapping to suit a given

application via pro grammable map de coder register s. At system powe r-up

or reset, a default processor memory map takes over.

2

Default Processor Memory Map

The default processor memory map that is valid at power-up or reset

remains in effect until rep rogrammed for specific applications. Table 2-1

defines the entire default memory map ($00000000 to $FFFFFFFF).

Table 2-1. Processor Default View of the Memory Map

Processor Address

Start End

00000000 7FFFFFFF 2GB Not Mapped

80000000 8001FFFF 128KB PCI/ISA I/O Space 1

80020000 FEF7FFFF 2GB-16MB-640KB Not Mapped

FEF80000 FEF8FFFF 64KB Falcon Registers

http://www.motorola.com/computer/literature 2-3

Size Definition Notes

Page 56

Startup and Operation

2