Motorola MC74LCX646SD, MC74LCX646DT, MC74LCX646DW Datasheet

SEMICONDUCTOR TECHNICAL DATA

")" & &

$!%($%&$

$!%($

& " $!& !#'&% ! '&#'&%

&& "!!($&!

The MC74LCX646 is a high performance, non–inverting octal

transceiver/registered transceiver operating from a 2.7 to 3.6V supply.

High impedance TTL compatible inputs significantly reduce current

loading to input drivers while TTL compatible outputs offer improved

switching noise performance. A VI specification of 5.5V allows

MC74LCX646 inputs to be safely driven from 5V devices. The

MC74LCX646 is suitable for memory address driving and all TTL level

bus oriented transceiver applications.

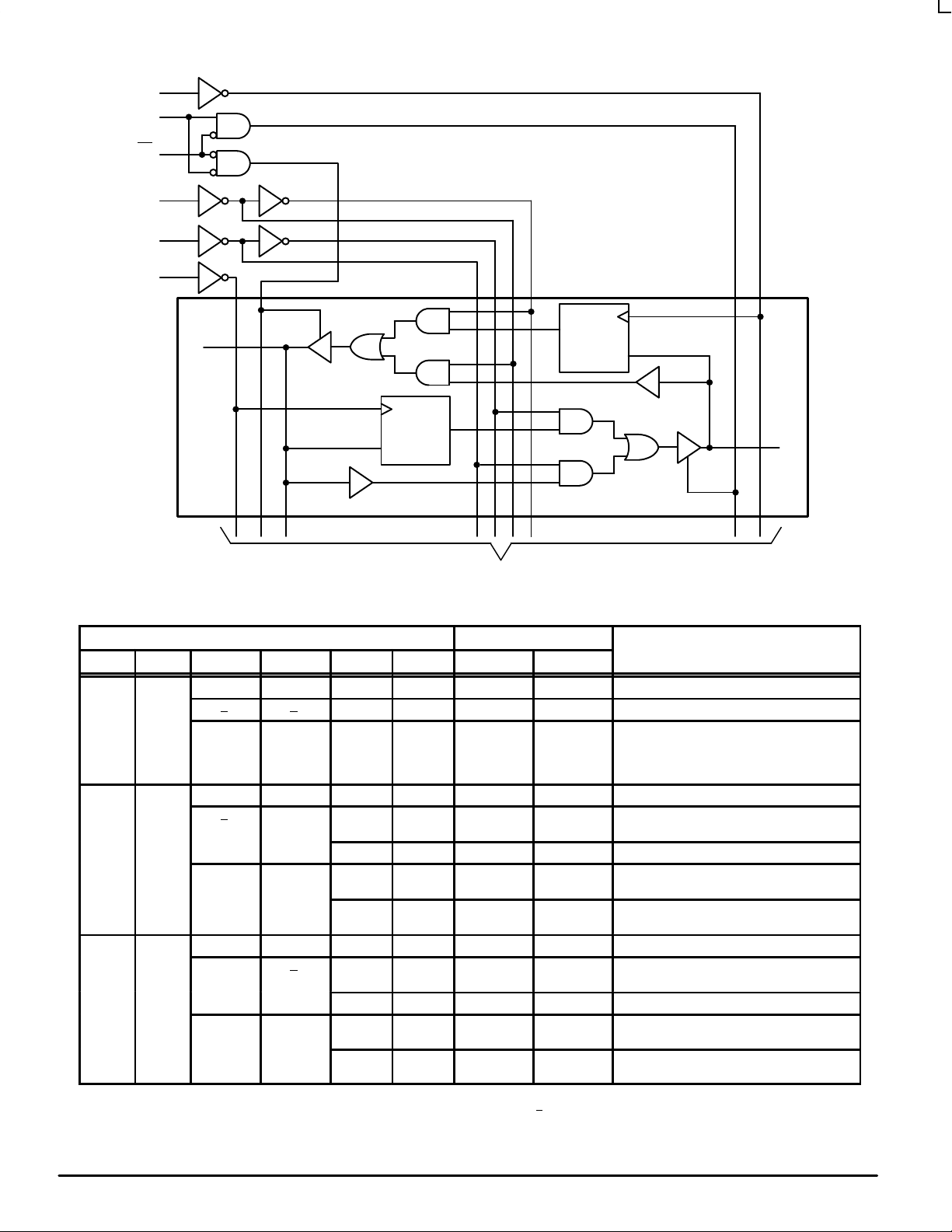

Data on the A or B bus will be clocked into the registers as the

appropriate clock pin goes from a LOW–to–HIGH logic level. Output

Enable (OE

In the transceiver mode, data present at the high impedance port may be

stored in either the A or the B register or in both. The select controls (SBA,

SAB) can multiplex stored and real–time (transparent mode) data. The

direction control (DIR) determines which bus will receive data when the

enable OE

be stored in the B register or B data may be stored in the A register. Only

one of the two buses, A or B, may be driven at one time.

• Designed for 2.7 to 3.6V V

• 5V Tolerant — Interface Capability With 5V TTL Logic

• Supports Live Insertion and Withdrawal

• I

OFF

• LVTTL Compatible

• LVCMOS Compatible

• 24mA Balanced Output Sink and Source Capability

• Near Zero Static Supply Current in All Three Logic States (10µA)

Substantially Reduces System Power Requirements

• Latchup Performance Exceeds 500mA

• ESD Performance: Human Body Model >2000V; Machine Model >200V

) and DIR pins are provided to control the transceiver outputs.

is active LOW. In the isolation mode (OE HIGH), A data may

Operation

CC

Specification Guarantees High Impedance When VCC = 0V

V

CBA SBA OE

CC

2324 22 21 20 19 18

Pinout: 24–Lead Package (Top View)

B0 B1 B2 B3 B4 B5

17

16

15

B6 B7

14

13

LOW–VOLTAGE CMOS

OCTAL TRANSCEIVER/

REGISTERED TRANSCEIVER

DW SUFFIX

24

1

24

24

PIN NAMES

Pins

A0–A7

B0–B7

CAB, CBA

SAB, SBA

DIR, OE

1

1

Function

Side A Inputs/Outputs

Side B Inputs/Outputs

Clock Pulse Inputs

Select Control Inputs

Output Enable Inputs

PLASTIC SOIC

CASE 751E–04

SD SUFFIX

PLASTIC SSOP

CASE 940D–03

DT SUFFIX

PLASTIC TSSOP

CASE 948H–01

21 34567

CAB SAB DIR A0 A1 A2 A3 A4 A5 A6

11/96

Motorola, Inc. 1996

9

8

1

10

11

12

A7 GND

REV 2

MC74LCX646

O

1

CBA

3

DIR

21

OE

22

SBA

2

SAB

23

CAB

A0

1 of 8 Channels

LOGIC DIAGRAM

C

Q

D

C

Q

D

B0

To 7 Other Channels

FUNCTION TABLE

Inputs

OE DIR CAB CBA SAB SBA An Bn

H X Input Input

↑ ↑ X X X X Isolation, Hold Storage

↑ ↑ X X l

L H Input Output

↑ X* L X L

H X X QA Stored A Data to B Bus

↑ X* L X l

H X L

L L Output Input

X* ↑ X L L

X H QB X Stored B Data to A Bus

X* ↑ X L L

X H QB

H = High Voltage Level; h = High Voltage Level One Setup Time Prior to the Low–to–High Clock Transition; L = Low Voltage Level; l = Low Voltage Level One Setup

Time Prior to the Low–to–High Clock T ransition; X = Don’t Care; ↑ = Low–to–High Clock Transition; ↑

QB = B input storage register; * = The clocks are not internally gated with either the Output Enables or the Source Inputs. Therefore, data at the A or B ports may be

clocked into the storage registers, at any time. For ICC reasons, Do Not Float Inputs.

Data Ports

h

X

X

H

h

H

H

H

QB

perating Mode

X

X

l

h

L

H

L

H

QA

QA

L

H

l

h

L

H

= NOT Low–to–High Clock Transition; QA = A input storage register;

Store A and/or B Data

Real Time A Data to B Bus

Real Time A Data to B Bus; Store A Data

Clock A Data to B Bus; Store A Data

Real Time B Data to A Bus

Real Time B Data to A Bus; Store B Data

Clock B Data to A Bus; Store B Data

MOTOROLA LCX DATA

2

BR1339 — REV 3

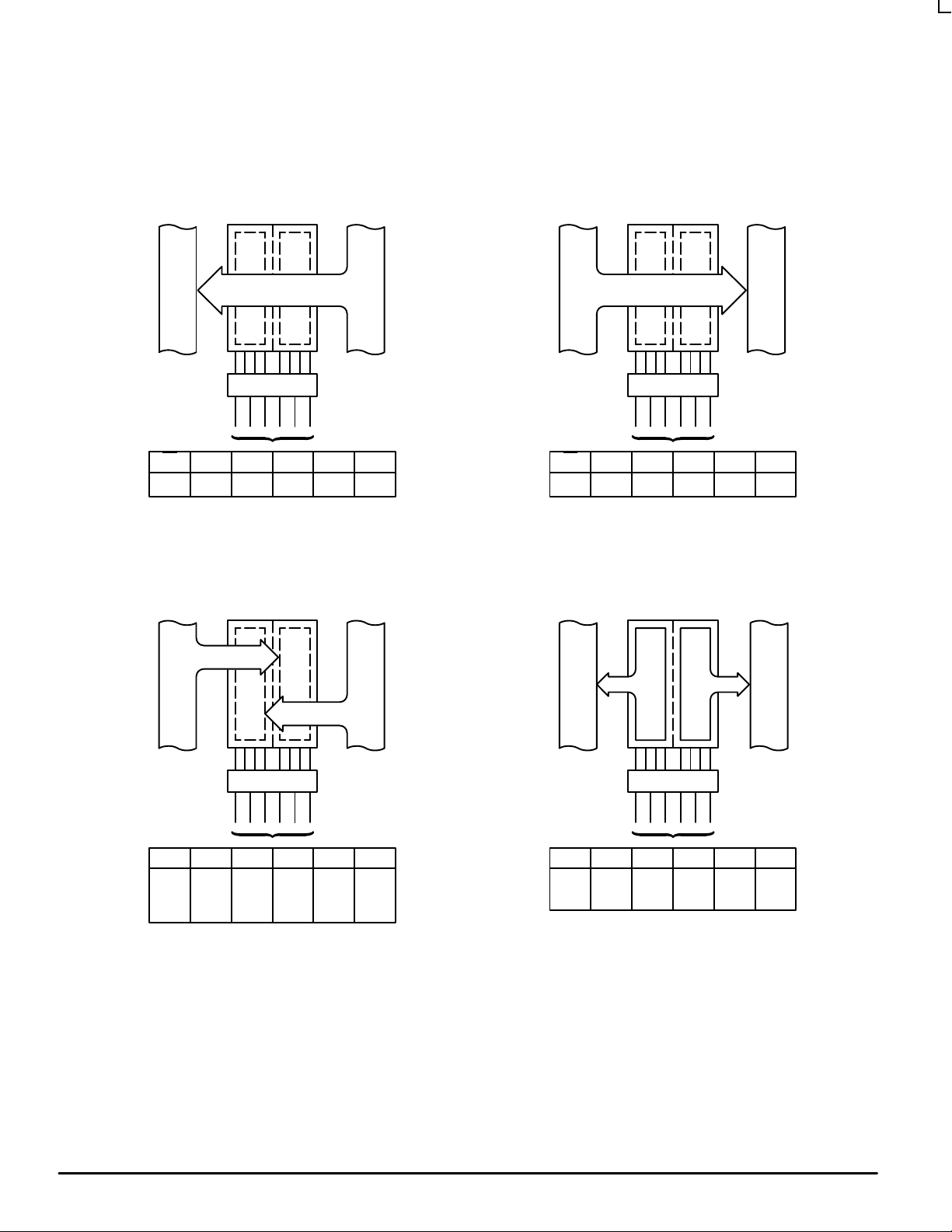

BUS APPLICATIONS

MC74LCX646

Real Time Transfer – Bus B to

Bus A

BUS A

OELDIR

CABXCBAXSABXSBA

L

Store Data from Bus A, Bus B or

Busses A and B

BUS B

L

Real Time Transfer – Bus A to

Bus B

BUS A

OELDIR

CABXCBAXSABLSBA

H

Transfer Storage Data to Bus A

or Bus B

BUS B

X

OE

X

X

H

BUS A

DIR

OE

L

L

BUS A

DIR

BUS B

CAB

CBA

SAB

SBA

L

X

H

H or L

H or L

X

X

H

H

X

BUS B

CAB

CBA

X

↑

X

X

X

X

↑

↑

↑

SAB

X

X

X

SBA

X

X

X

LCX DATA

BR1339 — REV 3

3 MOTOROLA

Loading...

Loading...