4-133

FAST AND LS TTL DATA

8-BIT ADDRESSABLE LATCH

The MC54/74F259 is a high-speed 8-bit addressable latch designed for

general purpose storage applications in digital systems. It is a multifunctional

device capable of storing single line data in eight addressable latches, and

also a 1-of-8 decoder and demultiplexer with active HIGH outputs. The device

also incorporates an active LOW Common Clear for resetting all latches, as

well as an active LOW Enable.

• Serial-to-Parallel Conversion

• Eight Bits of Storage with Output of Each Bit Available

• Random (Addressable) Data Entry

• Active High Demultiplexing or Decoding Capability

• Easily Expandable

• Common Clear

FUNCTIONAL DESCRIPTION

The MC54/74F259 has four modes of operation as shown in the Mode Select Table. In the addressable latch mode, data on the Data line (D) is written

into the addressed latch. The addressed latch will follow the data input with

all non-addressed latches remaining in their previous states in the memory

mode. All the latches remain in their previous state and are unaffected by the

Data or Address inputs.

In the one-of-eight decoding or demultiplexing mode, the addressed output

will follow the state of the D input with all other outputs in the LOW state. In

the clear mode all outputs are LOW and unaffected by the address and data

inputs. When operating the MC54/74F259 as an addressable latch, changing

more than one bit of the address could impose a transient wrong address.

Therefore, this should only be done while in the memory mode. The Truth

Table below summarizes the operations of the MC54/74F259.

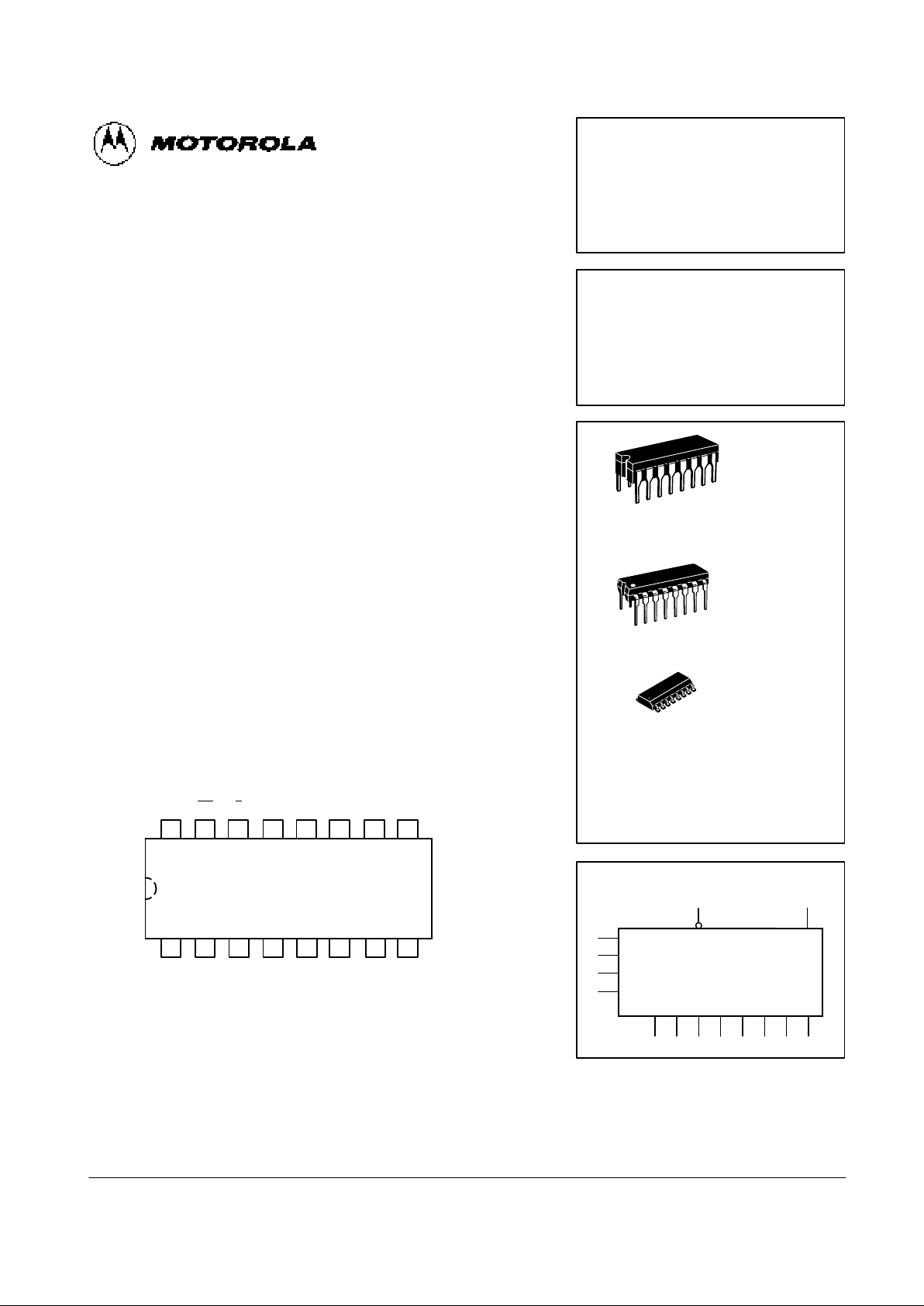

14 13 12 11 10 9

1 2 3 4 5 6

7

16 15

8

V

CC

A

0

MR

E D Q

7

Q

5

Q

6

Q

4

A1A2Q0Q1Q2Q3GND

CONNECTION DIAGRAM

MC54/74F259

8-BIT ADDRESSABLE LATCH

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

MC54FXXXJ Ceramic

MC74FXXXN Plastic

MC74FXXXD SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

FAST SCHOTTKY TTL

LOGIC SYMBOL

E

A

0

A

1

A

2

Q

0

Q2Q3Q4Q5Q6Q

7

Q

1

14

1

2

3

D

13

MR

15

4 5 6 7 9 10 11 12

4-134

FAST AND LS TTL DATA

MC54/74F259

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54, 74 4.5 5.0 5.5 V

54 –55 25 125

TAOperating Ambient Temperature Range

74 0 25 70

°C

I

OH

Output Current — High 54, 74 –1.0 mA

I

OL

Output Current — Low 54, 74 20 mA

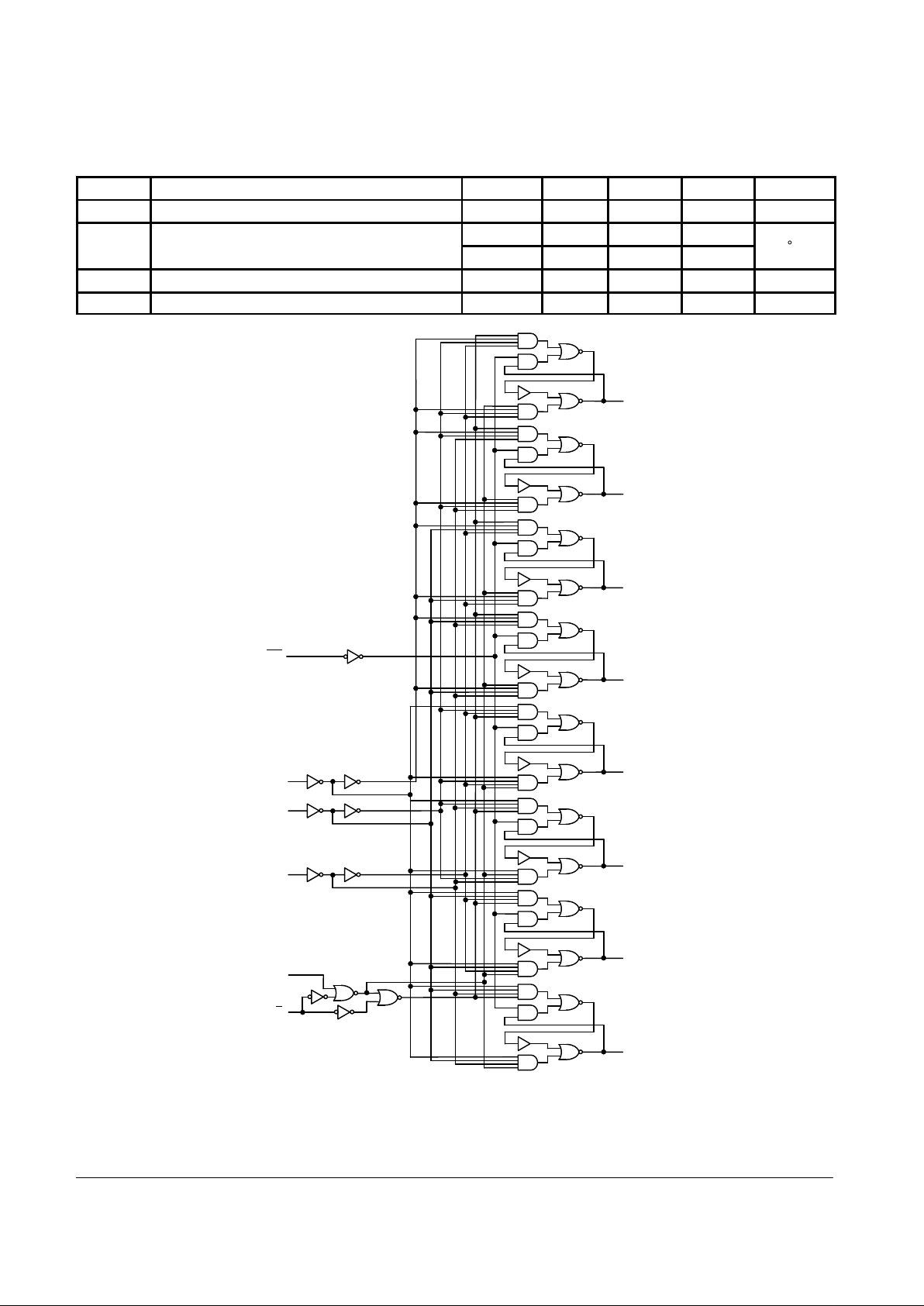

Please note that this diagram is provided only for the understanding of logic

operations and should not be used to estimate propagation delays.

Q

7

Q

6

Q

5

Q

4

Q

3

Q

2

Q

1

Q

0

MR

A

2

A

1

A

0

D

E

4-135

FAST AND LS TTL DATA

MC54/74F259

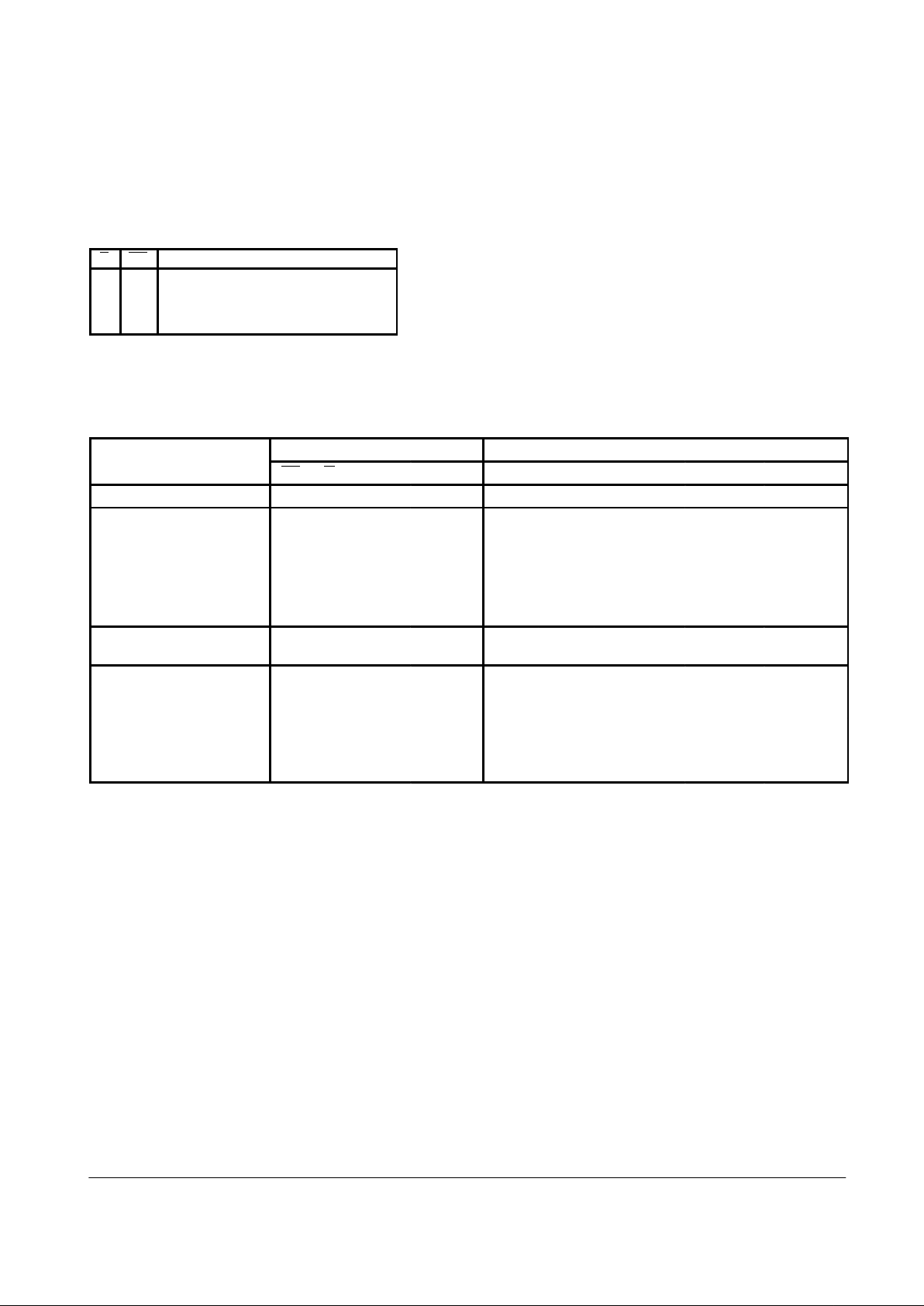

MODE SELECT TABLE

E MR Mode

L H Addressable Latch

H H Memory

L L Active HIGH 8-Channel Demultiplexer

H L Clear

H = HIGH Voltage Level

L = LOW Voltage Level

FUNCTION TABLE

Inputs Outputs

Operating

Mode

MR E D A0A1A

2

Q

0

Q

1

Q

2

Q3Q4Q5Q

6

Q

7

Master Reset L H X X X X L L L L L L L L

L L d L L L Q=d L L L L L L L

Demultiplex L L d H L L L Q=d L L L L L L

(Active HIGH L L d L H L L L Q=d L L L L L

Decoder when • • • • • • • • • • • • • •

D = H) • • • • • • • • • • • • • •

• • • • • • • • • • • • • •

L L d H H H L L L L L L L Q =d

Store

(Do Nothing)

H H X X X X q

0

q

1

q

2

q

3

q

4

q

5q6

q

7

H L d L L L Q=d q

1

q

2

q

3

q

4

q

5q6

q

7

H L d H L L q

0

Q=d q

2

q

3

q

4

q

5q6

q

7

H L d L H L q

0

q

1

Q=d q

3

q

4

q

5q6

q

7

Addressable • • • • • • • • • • • • • •

Latch • • • • • • • • • • • • • •

• • • • • • • • • • • • • •

H L d H H H q

0

q

1

q

2

q

3

q

4

q

5q6

Q=d

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

d = HIGH or LOW Data one setup time prior to the LOW-to-HIGH Enable transition.

q = Lower case letters indicate the state of the referenced output established during the last cycle in which it was addressed or cleared.

4-136

FAST AND LS TTL DATA

MC54/74F259

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

Symbol

Parameter

Min Typ Max

Unit

Test Conditions

V

IH

Input HIGH Voltage 2.0 V Guaranteed Input HIGH Voltage

V

IL

Input LOW Voltage 0.8 V Guaranteed Input LOW Voltage

V

IK

Input Clamp Diode Voltage –1.2 V VCC = MIN, IIN = –18 mA

54, 74 2.5 V IOL = –1.0 mA VCC = MIN

VOHOutput HIGH Voltage

74 2.7 V IOL = –1.0 mA VCC = 4.75 V

V

OL

Output LOW Voltage 0.5 V IOL = 20 mA VCC = MIN

20 µA VCC = MAX, VIN = 2.7 V

IIHInput HIGH Current

0.1 mA VCC = MAX,VIN = 7.0 V

I

IL

Input LOW Current –0.6 mA VCC = MAX, VIN = 0.5 V

I

OS

Output Short Circuit Current

(Note 2)

–60 –150 mA VCC = MAX, V

OUT

= 0 V

Power Supply Current

46 mA VCC = MAX

I

CC

Total, Output HIGH

Total, Output LOW

75 mA VCC = MAX

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

2. Not more then one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS

54/74F 54F 74F

T

= +25°C

T

= –55 to + 125°C

T

= 0 to + 70°C

TA = +25°C

VCC = +5.0 V

TA = –55 to + 125°C

VCC = 5.0 V ±10%

TA = 0 to + 70°C

VCC = 5.0 V ±10%

CC

= +5.0 V

CL = 50 pF

CC

= 5.0 V ±10%

CL = 50 pF

CC

= 5.0 V ±10%

CL = 50 pF

Symbol

Parameter

Min Max Min Max Min Max

Unit

t

PLH

Propagation Delay

4.0

10.5

4.0

13

4.0

12

PLH

t

PHL

E

to Q

n

3.0 7.0 3.0 8.5 3.0 7.0

ns

t

PLH

Propagation Delay 3.5 9.0 3.5 11.5 3.5 10

t

PLH

t

PHL

Propagation Delay

Dn to Q

n

3.5

3.0

9.0

6.5

3.5

2.5

11.5

8.5

3.5

2.5107.0

ns

t

PLH

Propagation Delay 3.5 13 3.5 15.5 3.5 14.5

t

PLH

t

PHL

Propagation Delay

An to Q

n

3.5

4.0139.0

3.5

4.0

15.5113.5

4.0

14.5

9.5

ns

Propagation Delay

t

PHL

Propagation Delay

MR

to Q

n

5.0

9.0

4.5

11.5

4.510ns

4-137

FAST AND LS TTL DATA

MC54/74F259

AC OPERATING REQUIREMENTS

54/74F 54F 74F

TA = +25°C

TA = –55 to +125°C

TA = 0 to +70 °C

TA = +25°C

VCC = +5.0 V

TA = –55 to +125°C

VCC = 5.0 ±10%

TA = 0 to +70 °C

VCC = 5.0 V ±10%

Symbol

Parameter

Min Max Min Max Min Max

Unit

ts(H)

Setup Time, HIGH or LOW

4.0

5.0

4.0

s

(H)

ts(L)

Dn to E 4.0 5.0 4.0

ns

th(H)

Hold Time, HIGH or LOW

2.0

2.0

2.0

h

(H)

th(L)

Dn to E 2.0 2.0 2.0

ns

ts(H)

Setup Time, HIGH or LOW

4.0

4.0

4.0

s

(H)

ts(L)

A to E

(a)

4.0 4.0 4.0

ns

th(H)

Hold Time, HIGH or LOW

0

0

0

h

(H)

th(L)

A to E

(b)

0 0 0

ns

t

W

E Pulse Width 4.0 4.0 4.0 ns

t

W

MR Pulse Width

4.0 4.0 4.0 ns

a. The Address to Enable setup time is the time before the HIGH-to-LOW Enable transition that the Address must be stable so that the correct latch is addressed

and the other latches are not affected.

b. The Address to Enable hold time is the time after the LOW-to-HIGH Enable transition that the Address must be stable so that the correct latch is addressed and

the other latches are not affected.

Loading...

Loading...