MOTOROLA MC74AC175, MC74ACT175 Technical data

5-1

FACT DATA

The MC74AC/ACT175 is a high-speed quad D flip-flop. The device is useful for

general flip-flop requirements where clock and clear inputs are common. The

information on the D inputs is transferred to storage during the LOW-to-HIGH clock

transition. The device has a Master Reset to simultaneously clear all flip-flops, when

MR

is low.

The MC74AC/ACT175 consists of four edge-triggered D flip-flops with individual

D inputs and Q and Q

outputs. The Clock (CP) and Master Reset (MR) are common

to all flip-flops. Each D input’s state is transferred to the corresponding flip-flop’s

output following the LOW-to-HIGH Clock (CP) transition. A LOW input to the Master

Reset (MR

) will force all Q outputs LOW and Q outputs HIGH independent of Clock

or Data inputs. The MC74AC/ACT175 is useful for applications where the Clock and

Master Reset are common to all storage elements.

• Outputs Source/Sink 24 mA

• ′ACT175 Has TTL Compatible Inputs

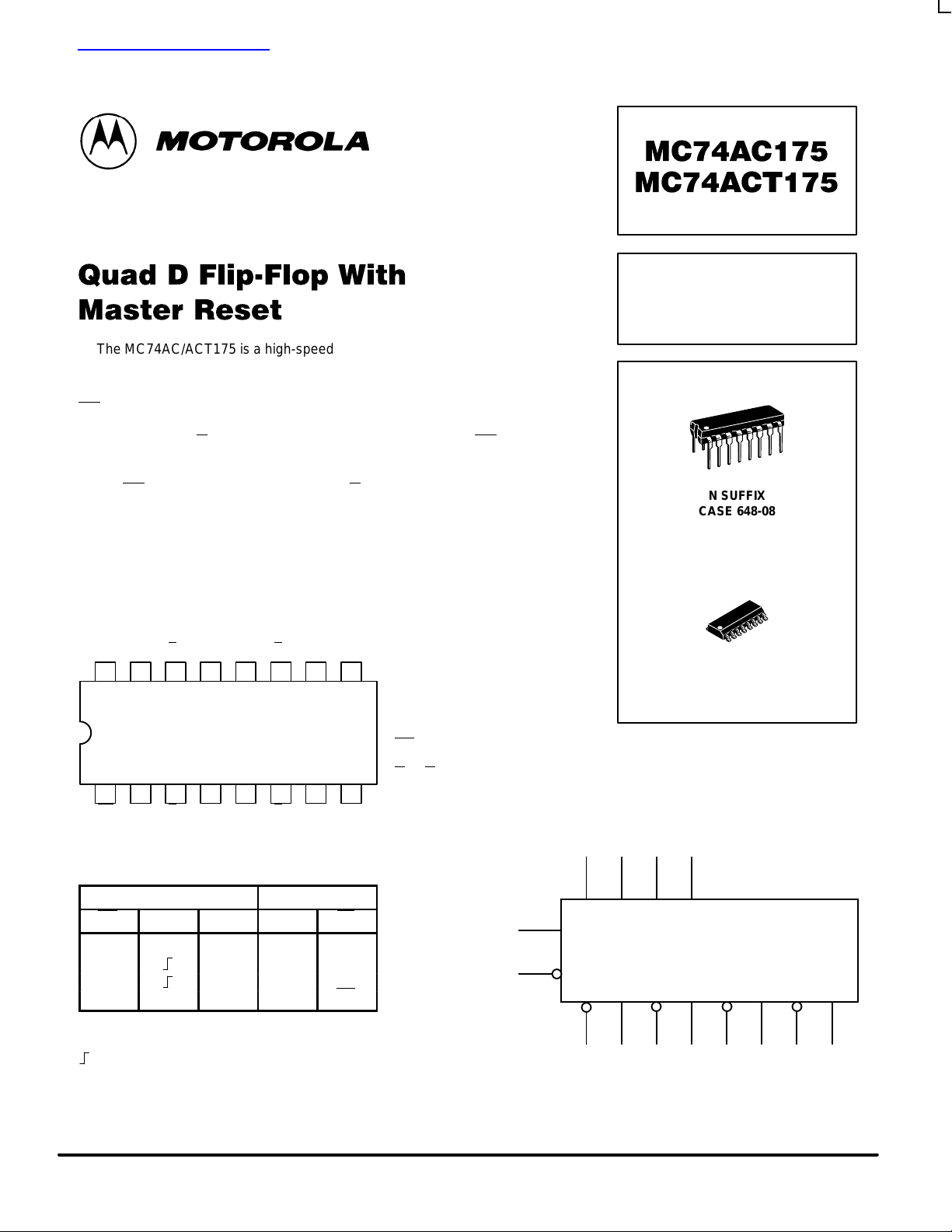

Pinout: 16-Lead Packages (Top View)

1516 14 13 12 11 10

21 3 4 5 6 7

V

CC

9

8

Q3Q

3D3D2Q2Q2

CP

MR

Q0Q

0D0D1Q1Q1

GND

PIN NAMES

Data Inputs

Clock Pulse Input

Master Reset Input

Outputs

Outputs

D0 – D

3

CP

MR

Q0 – Q

3

Q

0

– Q

3

TRUTH TABLE

Inputs Outputs

MR CP D Qn Qn

L X X L H

H H H L

H L L H

H L X Qn Qn

QUAD D FLIP-FLOP

WITH MASTER RESET

N SUFFIX

CASE 648-08

PLASTIC

D SUFFIX

CASE 751B-05

PLASTIC

LOGIC SYMBOL

D0D1D2D

3

Q0Q0Q1Q1Q2Q2Q3Q

3

CP

MR

查询MC74AC175供应商

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Transition of Clock

MC74AC175 MC74ACT175

5-2

FACT DATA

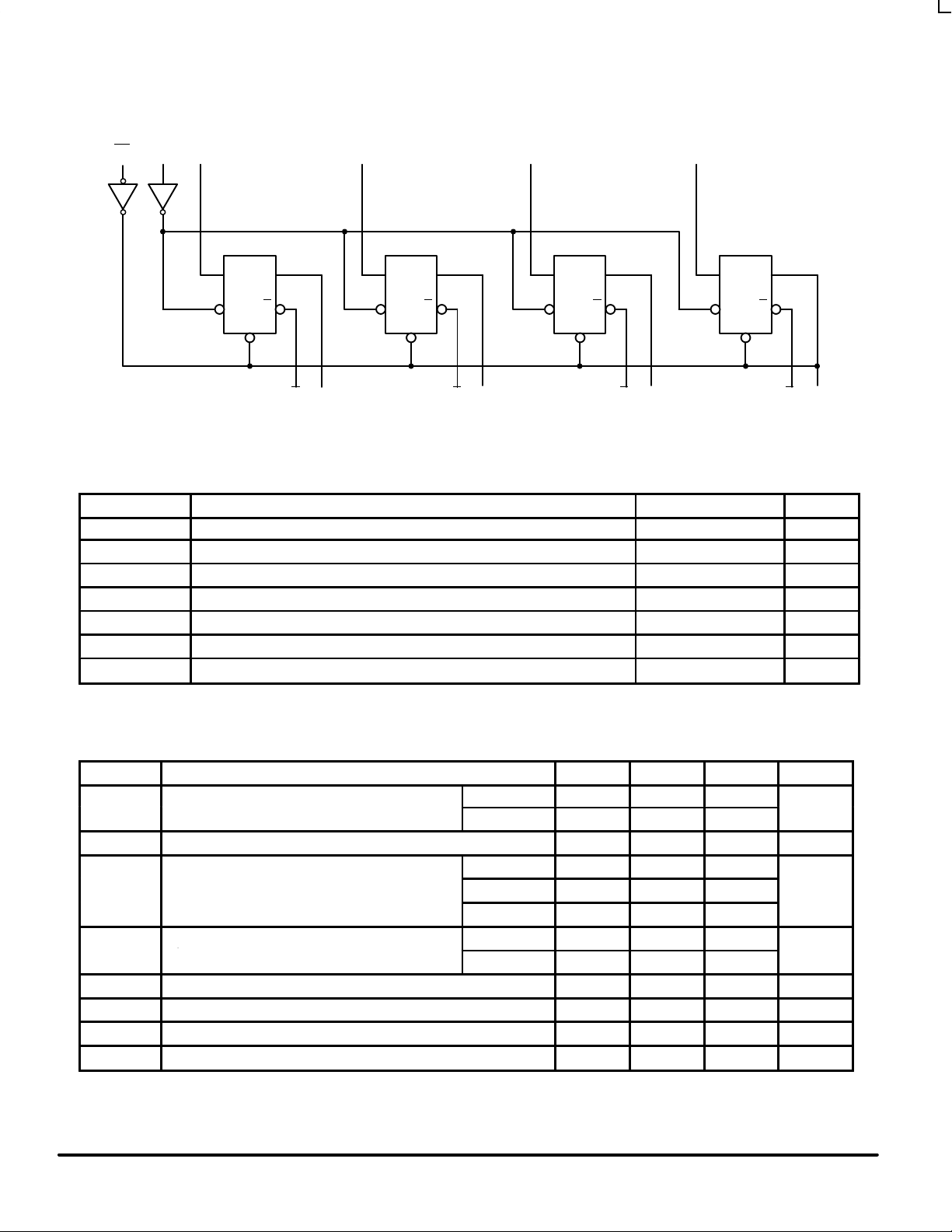

LOGIC DIAGRAM

MR CP D

3

D

2

D

1

D

0

D

CP

CD

Q

Q

3

Q

3

Q

Q

2

Q

2

Q

1Q1

Q

0Q0

D

CP

CD

Q

Q

D

CP

CD

Q

Q

D

CP

CD

Q

Q

Please note that this diagram is provided only for the understanding of logic operations and should not be

used to estimate propagation delays.

MAXIMUM RATINGS*

Symbol Parameter Value Unit

V

CC

DC Supply Voltage (Referenced to GND) –0.5 to +7.0 V

V

in

DC Input Voltage (Referenced to GND) –0.5 to VCC + 0.5 V

V

out

DC Output Voltage (Referenced to GND) –0.5 to VCC + 0.5 V

I

in

DC Input Current, per Pin ± 20 mA

I

out

DC Output Sink/Source Current, per Pin ± 50 mA

I

CC

DC VCC or GND Current per Output Pin ± 50 mA

T

stg

Storage Temperature –65 to +150 °C

* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended

Operating Conditions.

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Typ Min Unit

′AC 2.0 5.0 6.0

VCCSupply Voltage

′ACT 4.5 5.0 5.5

V

Vin, V

out

DC Input Voltage, Output Voltage (Ref. to GND) 0 V

CC

V

VCC @ 3.0 V 150

Input Rise and Fall Time (Note 1)

′AC Devices except Schmitt Inputs

VCC @ 4.5 V 40 ns/V

r

, t

f

′AC Devices except Schmitt Inputs

VCC @ 5.5 V 25

VCC @ 4.5 V 10

tr, t

f

Input Rise and Fall Time (Note 2)

′ACT Devices except Schmitt Inputs

VCC @ 5.5 V 8.0

ns/V

T

J

Junction Temperature (PDIP) 140 °C

T

A

Operating Ambient Temperature Range –40 25 85 °C

I

OH

Output Current — HIGH –24 mA

I

OL

Output Current — LOW 24 mA

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times.

2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

tr, t

f

Input Rise and Fall Time (Note 2)

Loading...

Loading...