MOTOROLA MC74AC112, MC74ACT112 Technical data

5-1

FACT DATA

The MC74AC112/74ACT112 consists of two high-speed completely independent

transition clocked JK flip-flops. The clocking operation is independent of rise and fall

times of the clock waveform. The JK design allows operation as a D flip-flop (refer to

MC74AC74/74ACT74 data sheet) by connecting the J and K inputs together.

Asynchronous Inputs:

LOW input to S

D

(Set) sets Q to HIGH level

LOW input to C

D

(Clear) sets Q to LOW level

Clear and Set are independent of clock

Simultaneous LOW on C

D

and SD makes both Q and Q

HIGH

• Outputs Source/Sink 24 mA

• ′ACT112 Has TTL Compatible Inputs

V

CC

CP

1K1J1SD1Q1Q1

C

D1CD2CP2K2J2SD2

C

D

J

Q

Q

2

S

D

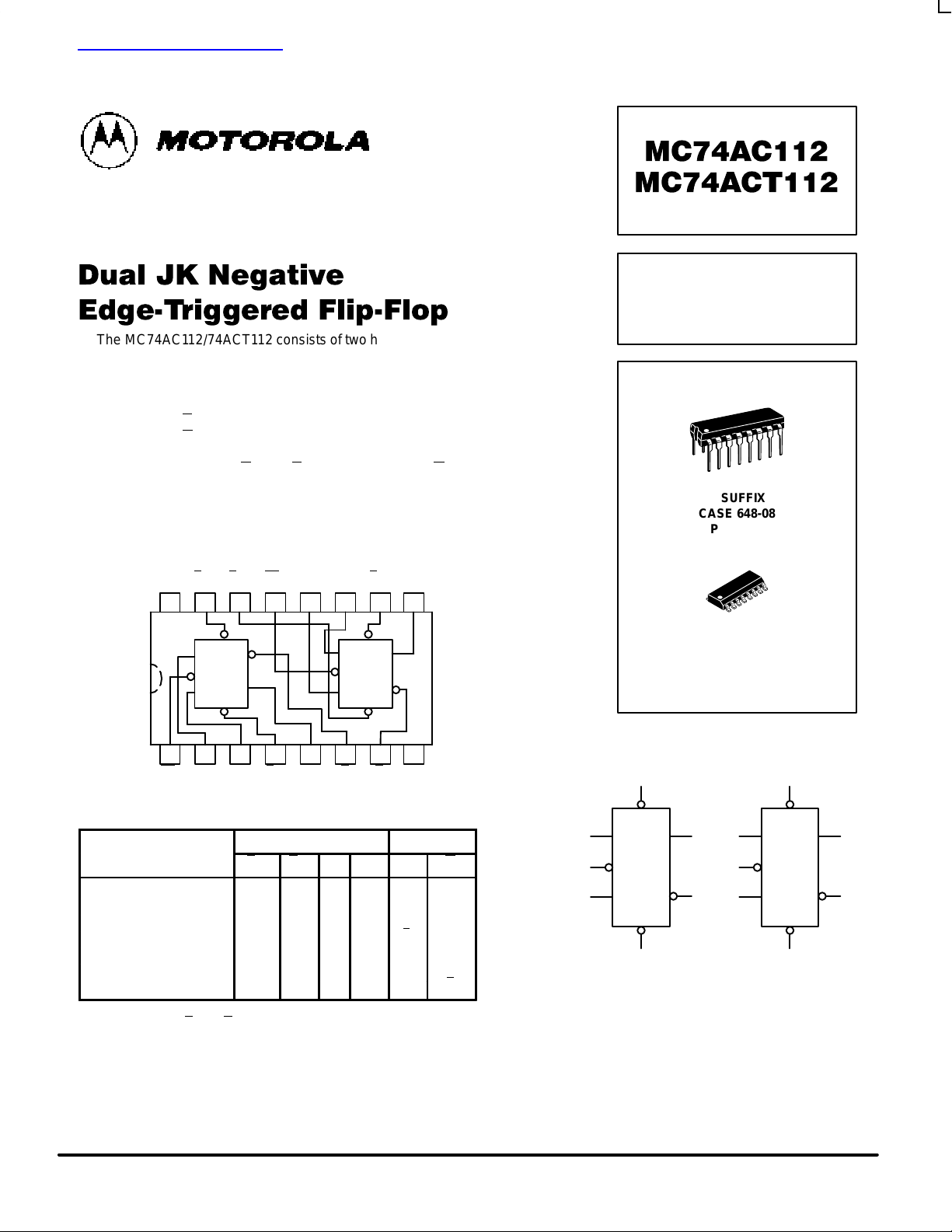

CONNECTION DIAGRAM

Q

2

GND

1 2 3 4 5 6 7 8

910111213141516

K

Q

CP

S

D

K

Q

C

D

J

Q

MODE SELECT — TRUTH TABLE

Inputs Outputs

Operating Mode

S

D

C

D

J K Q Q

Set L H X X H L

Reset (Clear) H L X X L H

*Undetermined L L X X H H

Toggle H H h h q q

Load “0” (Reset) H H l h L H

Load “1” (Set) H H h l H L

Hold H H l l q q

D

and CD are LOW, but the output states

are unpredictable if S

D

and CD go HIGH simultaneously.

DUAL JK NEGATIVE

EDGE-TRIGGERED

FLIP-FLOP

N SUFFIX

CASE 648-08

PLASTIC

D SUFFIX

CASE 751B-05

PLASTIC

LOGIC SYMBOL

S

D

QJ

CP

Q

C

D

VCC = PIN 16

GND = PIN 8

K

3

1

2

15

4

5

6

S

D

QJ

CP

Q

C

D

K

11

13

12

14

10

9

7

查询MC74AC112D供应商

CP

*Both outputs will be HIGH while both S

H, h = HIGH Voltage Level

L, l = LOW Voltage Level

X = Don’t Care

l, h (q) = Lower case letters indicate the state of the referenced input

(or output) one set-up time prior to the HIGH to LOW clock transition.

MC74AC112 MC74ACT112

5-2

FACT DATA

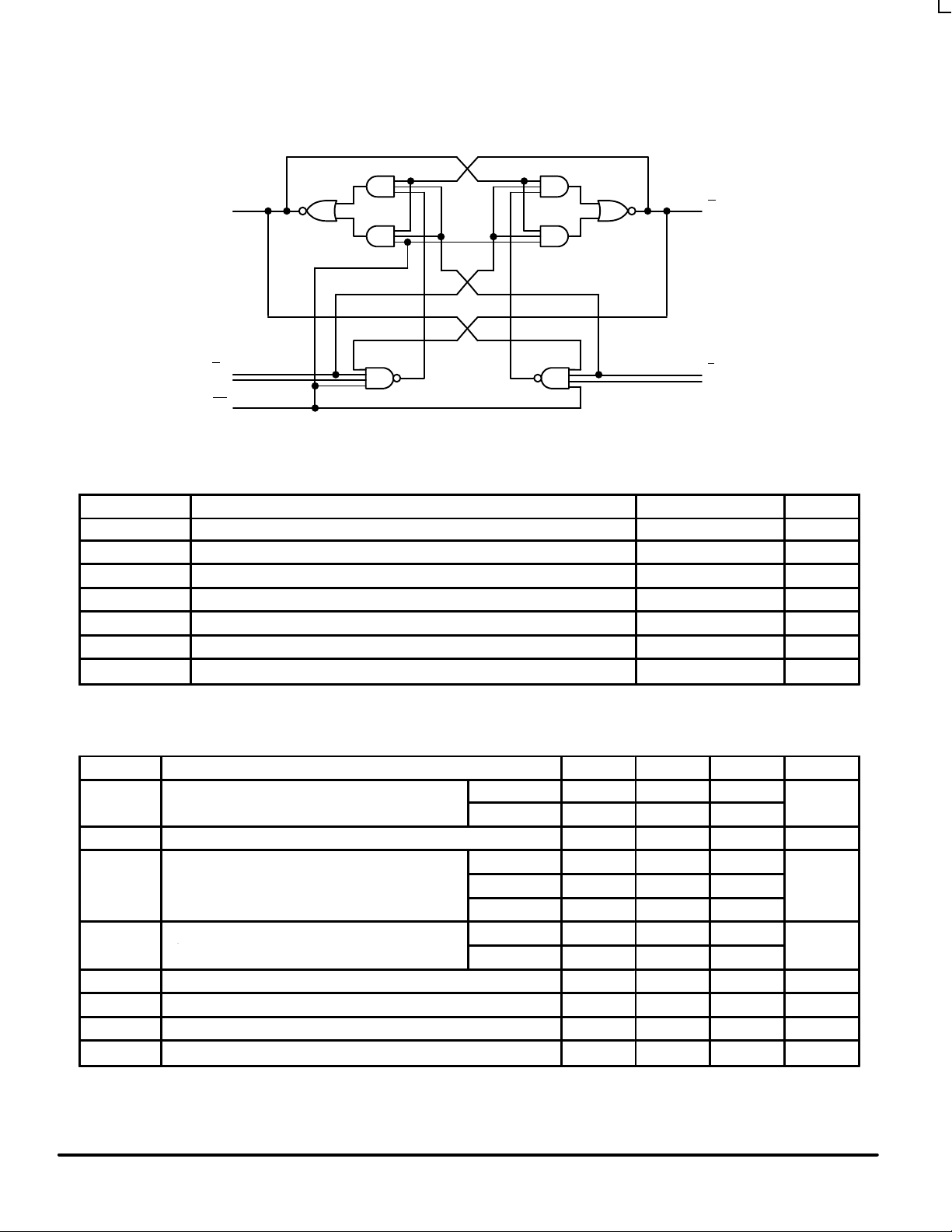

Q

LOGIC DIAGRAM (one half shown)

C

D

J

CP

S

D

J

Q

MAXIMUM RATINGS*

Symbol Parameter Value Unit

V

CC

DC Supply Voltage (Referenced to GND) –0.5 to +7.0 V

V

in

DC Input Voltage (Referenced to GND) –0.5 to VCC +0.5 V

V

out

DC Output Voltage (Referenced to GND) –0.5 to VCC +0.5 V

I

in

DC Input Current, per Pin ±20 mA

I

out

DC Output Sink/Source Current, per Pin ±50 mA

I

CC

DC VCC or GND Current per Output Pin ±50 mA

T

stg

Storage Temperature –65 to +150 °C

* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended

Operating Conditions.

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Typ Max Unit

′AC 2.0 5.0 6.0

VCCSupply Voltage

′ACT 4.5 5.0 5.5

V

Vin, V

out

DC Input Voltage, Output Voltage (Ref. to GND) 0 V

CC

V

VCC @ 3.0 V 150

Input Rise and Fall Time (Note 1)

′AC Devices except Schmitt Inputs

VCC @ 4.5 V 40 ns/V

r

, t

f

′AC Devices except Schmitt Inputs

VCC @ 5.5 V 25

VCC @ 4.5 V 10

tr, t

f

Input Rise and Fall Time (Note 2)

′ACT Devices except Schmitt Inputs

VCC @ 5.5 V 8.0

ns/V

T

J

Junction Temperature (PDIP) 140 °C

T

A

Operating Ambient Temperature Range –40 25 85 °C

I

OH

Output Current — High –24 mA

I

OL

Output Current — Low 24 mA

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times.

2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

tr, t

f

Input Rise and Fall Time (Note 2)

Loading...

Loading...