查询68HC912DG128CPV8供应商

Freescale Semiconductor, Inc.

MC68HC912DG128

nc...

I

Technical Data

cale Semiconductor,

Frees

M68HC12

Microcontrollers

MOTOROLA.COM/SEMICONDUCTORS

MC68HC912DG128/D

Rev. 3, 10/2002

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

MC68HC912DG128

Technical Data — Rev 3.0

nc...

I

cale Semiconductor,

Frees

Motorola reserves the righ t to make changes without further notice to any products

herein. Motorola makes no warranty, representation or guarantee regarding the

suitability of i ts products for any partic ular purpose, nor does Moto rola assume any

liability arising out of the application or use of any prod uct or circuit, and s pecifically

disclaims any an d all liability, including withou t limitation consequential or inc idental

damages. "Typical" parameters which may be provided in Motorola data sheets and/or

specifications can an d do vary in different applications and actua l performance may

vary over time. A ll operating parameters, i ncluding "Typicals" must be validated for

each customer application by customer’s technical experts. Motorola does not convey

any license under i ts patent rights nor the rig hts of others. Motorola prod ucts are not

designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other applicat ion in wh ich the failure of the Mo torola pr oduct could cr eate a

situation where personal injury or death may oc cur. Should Buyer purchase o r use

Motorola products for any such unintended or una uthorized application, Buye r shall

indemnify and hold Motorola and its officers, employees, subsid iaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of personal

injury or death associated with such unintended or unauthorized use, even if such claim

alleges that Motorola was negligent reg arding the design o r manufacture of the p art.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Motorola, Inc., 2002

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA 3

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

Technical Data MC68HC912DG128 — Rev 3.0

4 MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

List of Paragraphs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

List of Paragraphs

nc...

I

cale Semiconductor,

Frees

List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Section 1. General Description . . . . . . . . . . . . . . . . . . . .23

Section 2. Central Processing Unit . . . . . . . . . . . . . . . . .29

Section 3. Pinout and Signal Descriptions . . . . . . . . . . .37

Section 4. Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Section 5. Operating Modes. . . . . . . . . . . . . . . . . . . . . . .75

Section 6. Bus Control and Input/Output . . . . . . . . . . . .95

Section 7. Flash Memory . . . . . . . . . . . . . . . . . . . . . . . .107

Section 8. EEPROM Memory . . . . . . . . . . . . . . . . . . . . .125

Section 9. Resets and Interrupts. . . . . . . . . . . . . . . . . .133

Section 10. I/O Ports with Key Wake-up . . . . . . . . . . . .147

Section 11. Clock Functio ns . . . . . . . . . . . . . . . . . . . . .155

Section 12. Pulse Width Modulator . . . . . . . . . . . . . . . .191

Section 13. Enhanced Capture Timer . . . . . . . . . . . . . .207

Section 14. Multiple Serial Interface . . . . . . . . . . . . . . .249

Section 15. Inter-IC Bus . . . . . . . . . . . . . . . . . . . . . . . . .273

Section 16. Analog-to-Digital Converter . . . . . . . . . . . .297

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA List of Paragraphs 5

For More Information On This Product,

Go to: www.freescale.com

List of Paragraphs

nc...

I

Freescale Semiconductor, Inc.

Section 17. MSCAN Controller. . . . . . . . . . . . . . . . . . . .311

Section 18. Development Support. . . . . . . . . . . . . . . . .355

Section 19. Electrical Specificatio ns. . . . . . . . . . . . . . .385

Section 20. Appendix: CGM Practical Aspects . . . . . .407

Section 21. Appendix: MC68HC912DG128A Flash . . .419

Section 22. Appendix: MC68HC912DG128A EEPROM 427

Section 23. Revision History . . . . . . . . . . . . . . . . . . . . .439

Glossary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .441

cale Semiconductor,

Frees

Technical Data MC68HC912DG128 — Rev 3.0

6 List of Paragraphs MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

Table of Contents

List of Paragraphs

Table of Contents

nc...

I

cale Semiconductor,

Frees

List of Figures

List of Tables

Section 1. General Description

1.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

1.4 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.5 MC68HC912DG128 Block Diagram. . . . . . . . . . . . . . . . . . . . .28

Section 2. Central Processing Unit

2.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

2.4 Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.5 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.6 Indexed Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.7 Opcodes and Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Table of Contents 7

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Freescale Semiconductor, Inc.

Section 3. Pinout and Signal Descriptions

3.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

3.2 Pin Assignments in 112-pin QFP . . . . . . . . . . . . . . . . . . . . . . .37

3.3 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

3.4 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

3.5 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Section 4. Registers

nc...

I

cale Semiconductor,

Frees

4.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.2 Register Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Section 5. Operating Modes

5.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

5.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.3 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

5.4 Background Debug Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

5.5 Internal Resource Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . .81

5.6 Memory Maps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

Section 6. Bus Control and Input/Output

6.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

6.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

6.3 Detecting Access Type from External Signals . . . . . . . . . . . . .95

6.4 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Section 7. Flash Memory

7.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

7.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 07

Technical Data MC68HC912DG128 — Rev 3.0

8 Table of Conten ts MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

7.3 Future Flash EEPROM Support. . . . . . . . . . . . . . . . . . . . . . .108

7.4 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

7.5 Flash EEPROM Control Block . . . . . . . . . . . . . . . . . . . . . . . .109

7.6 Flash EEPROM Arrays. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

7.7 Flash EEPROM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . .110

7.8 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

7.9 Programming the Flash EEPROM . . . . . . . . . . . . . . . . . . . . .118

7.10 Erasing the Flash EEPROM. . . . . . . . . . . . . . . . . . . . . . . . . .120

Table of Contents

nc...

I

cale Semiconductor,

Frees

7.11 Program/Erase Protection Interlocks . . . . . . . . . . . . . . . . . . .122

7.12 Stop or Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

7.13 Test Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Section 8. EEPROM Memory

8.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

8.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 25

8.3 Future EEPROM Support. . . . . . . . . . . . . . . . . . . . . . . . . . . .126

8.4 EEPROM Programmer’s Model . . . . . . . . . . . . . . . . . . . . . . .127

8.5 EEPROM Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . .128

Section 9. Resets and Interrupts

9.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

9.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 33

9.3 Maskable interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

9.4 Latching of Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

9.5 Interrupt Control and Priority Registers . . . . . . . . . . . . . . . . .137

9.6 Interrupt test registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

9.7 Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Table of Contents 9

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Freescale Semiconductor, Inc.

9.8 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

9.9 Register Stacking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

9.10 Important User Information. . . . . . . . . . . . . . . . . . . . . . . . . . .145

Section 10. I/O Ports with Key Wake-up

10.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

10.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 47

10.3 Key Wake-up and Port Registers . . . . . . . . . . . . . . . . . . . . . .148

nc...

I

cale Semiconductor,

Frees

10.4 Key Wake-Up Input Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

Section 11. Clock Functions

11.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

11.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 55

11.3 Clock Sources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156

11.4 Phase-Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . .157

11.5 Acquisition and Tracking Modes. . . . . . . . . . . . . . . . . . . . . . .159

11.6 Limp-Home and Fast STOP Recovery modes. . . . . . . . . . . .161

11.7 System Clock Frequency formulas. . . . . . . . . . . . . . . . . . . . .179

11.8 Clock Divider Chains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

11.9 Computer Operating Properly (COP) . . . . . . . . . . . . . . . . . . .184

11.10 Real-Time Interrupt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

11.11 Clock Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

11.12 Clock Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

Section 12. Pulse Width Modulator

12.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

12.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 91

Technical Data MC68HC912DG128 — Rev 3.0

10 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

12.3 PWM Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . .195

12.4 PWM Boundary Cases. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206

Table of Contents

Section 13. Enhanced Capture Timer

13.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

13.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 07

13.3 Enhanced Capture Timer Modes of Operation. . . . . . . . . . . .214

13.4 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

nc...

I

cale Semiconductor,

Frees

13.5 Timer and Modulus Counter Operation in Different Modes . .247

Section 14. Multiple Serial Interface

14.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .249

14.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 49

14.3 Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .250

14.4 Serial Communication Interface (SCI) . . . . . . . . . . . . . . . . . .250

14.5 Serial Peripheral Interface (SPI). . . . . . . . . . . . . . . . . . . . . . .262

14.6 Port S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .271

Section 15. Inter-IC Bus

15.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .273

15.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 73

15.3 IIC Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274

15.4 IIC System Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 76

15.5 IIC Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .276

15.6 IIC Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . .281

15.7 IIC Programming Examples . . . . . . . . . . . . . . . . . . . . . . . . . .290

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Table of Contents 11

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Freescale Semiconductor, Inc.

Section 16. Analog-to-Digital Converter

16.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .297

16.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 97

16.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298

16.4 ATD Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .299

16.5 ATD Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .310

Section 17. MSCAN Controller

nc...

I

cale Semiconductor,

Frees

17.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .311

17.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 11

17.3 External Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .312

17.4 Message Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .313

17.5 Identifier Acceptance Filter. . . . . . . . . . . . . . . . . . . . . . . . . . .318

17.6 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .322

17.7 Protocol Violation Protection. . . . . . . . . . . . . . . . . . . . . . . . . .324

17.8 Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .325

17.9 Timer Link. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

17.10 Clock System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 29

17.11 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 32

17.12 Programmer’s Model of Message Storage. . . . . . . . . . . . . . .332

17.13 Programmer’s Model of Control Registers . . . . . . . . . . . . . . .338

Section 18. Development Support

18.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

18.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 55

18.3 Instruction Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

18.4 Background Debug Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . .357

Technical Data MC68HC912DG128 — Rev 3.0

12 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

18.5 Breakpoints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .375

18.6 Instruction Tagging. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .382

Table of Contents

Section 19. Electrical Specifications

19.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .385

19.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 85

19.3 Tables of Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .386

Section 20. Appendix: CGM Practical Aspects

nc...

I

cale Semiconductor,

Frees

20.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .407

20.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 07

20.3 A Few Hints For The CGM Crystal Oscillator Applica t ion. . . .407

20.4 Practical Aspects For The PLL Usage . . . . . . . . . . . . . . . . . .410

20.5 Printed Circuit Board Guidelines. . . . . . . . . . . . . . . . . . . . . . .415

Section 21. Appendix: MC68HC912DG128A Flash

21.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .419

21.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 19

21.3 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .420

21.4 Flash EEPROM Control Block . . . . . . . . . . . . . . . . . . . . . . . .420

21.5 Flash EEPROM Arrays. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .420

21.6 Flash EEPROM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . .421

21.7 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .423

21.8 Programming the Flash EEPROM . . . . . . . . . . . . . . . . . . . . .424

21.9 Erasing the Flash EEPROM. . . . . . . . . . . . . . . . . . . . . . . . . .425

21.10 Stop or Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .425

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Table of Contents 13

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

Section 22. Appendix: MC68HC912DG128A EEPROM

22.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .427

22.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 27

22.3 EEPROM Programmer’s Model . . . . . . . . . . . . . . . . . . . . . . .428

22.4 EEPROM Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . .430

22.5 Program/Erase Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . .436

22.6 Shadow Word Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . .436

22.7 Programming EEDIVH and EEDIVL Registers. . . . . . . . . . . .437

Section 23. Revision History

cale Semiconductor,

Frees

Glossary

Technical Data MC68HC912DG128 — Rev 3.0

14 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

Figure Title Page

2-1 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3-1 MC68HC912DG128 Pin Assignments in 112-pin QFP. . . . . . .38

3-2 112-pin QFP Mechanical Dimensions (case no987) . . . . . . . .39

nc...

I

cale Semiconductor,

Frees

3-3 PLL Loop FIlter Connections . . . . . . . . . . . . . . . . . . . . . . . . . .41

3-4 Common Crystal Connections . . . . . . . . . . . . . . . . . . . . . . . . .43

3-5 External Oscillator Connections . . . . . . . . . . . . . . . . . . . . . . . .43

5-1 Memory Map after reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

5-2 Memory Paging. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

6-1 Access Type vsBus Control Pins . . . . . . . . . . . . . . . . . . . . . . .96

7-1 Program Sequence Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

7-2 Erase Sequence Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

10-1 STOP Key Wake-up Filter . . . . . . . . . . . . . . . . . . . . . . . . . . .153

11-1 Internal Clock Relationships. . . . . . . . . . . . . . . . . . . . . . . . . .157

11-2 PLL Functional Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

11-3 Clock Loss during Normal Operation . . . . . . . . . . . . . . . . . . .162

11-4 No Clock at Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . .164

11-5 STOP Exit and Fast STOP Recovery. . . . . . . . . . . . . . . . . . .167

11-6 Clock Generation Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

11-7 Clock Chain for SCI0, SCI1, RTI, COP. . . . . . . . . . . . . . . . . .181

11-8 Clock Chain for ECT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

11-9 Clock Chain for MSCAN, SPI, ATD0, ATD1 and BDM. . . . . .183

12-1 Block Diagram of PWM Left-Aligned Output Channel . . . . . .192

12-2 Block Diagram of PWM Cen ter-Aligned Output Channe l . . . .193

12-3 PWM Clock Sources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194

13-1 Timer Block Diagram in Latch Mode. . . . . . . . . . . . . . . . . . . .209

13-2 Timer Block Diagram in Queue Mode. . . . . . . . . . . . . . . . . . .210

13-3 8-Bit Pulse Accumulators Block Diagram. . . . . . . . . . . . . . . .211

13-4 16-Bit Pulse Accumulators Block Diagram. . . . . . . . . . . . . . .212

List of Figures

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA List of Figures 15

For More Information On This Product,

Go to: www.freescale.com

List of Figures

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

13-5 Block Diagram for Port7 with Output compare / Pulse

13-6 C3F-C0F Interrupt Flag Setting . . . . . . . . . . . . . . . . . . . . . . .213

14-1 Multiple Serial Interface Block Diagram . . . . . . . . . . . . . . . . .250

14-2 Serial Communications Interface Block Diagram. . . . . . . . . .251

14-3 Serial Peripheral Interface Block Diagram . . . . . . . . . . . . . . .263

14-4 SPI Clock Format 0 (CPHA = 0). . . . . . . . . . . . . . . . . . . . . . .264

14-5 SPI Clock Format 1 (CPHA = 1). . . . . . . . . . . . . . . . . . . . . . .265

14-6 Normal Mode and Bidirectional Mode. . . . . . . . . . . . . . . . . . .266

15-1 IIC Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .275

15-2 IIC Transmission Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . .276

15-3 IIC Clock Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . .280

15-4 Flow-Chart of Typical IIC Interrupt Routine . . . . . . . . . . . . . .295

16-1 Analog-to-Digital Converter Block Diagram . . . . . . . . . . . . . .298

17-1 The CAN System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .313

17-2 User Model for Message Buffer Organization. . . . . . . . . . . . .316

17-3 32-bit Maskable Identifier Acceptance Filters. . . . . . . . . . . . .320

17-4 16-bit Maskable Acceptance Filters . . . . . . . . . . . . . . . . . . . .320

17-5 8-bit Maskable Acceptance Filters . . . . . . . . . . . . . . . . . . . . .321

17-6 SLEEP Request / Acknowledge Cycle. . . . . . . . . . . . . . . . . .327

17-7 Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

17-8 Segments within the Bit Time. . . . . . . . . . . . . . . . . . . . . . . . .331

17-9 CAN Standard Compliant Bit Time Segment Settings . . . . . .331

17-10 msCAN12 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

17-11 Message Buffer Organization. . . . . . . . . . . . . . . . . . . . . . . . .333

17-12 Receive/Transmit Message Buffer Extended Identifier. . . . . .334

17-13 Standard Identifier Mapping . . . . . . . . . . . . . . . . . . . . . . . . . .335

17-14 Identifier Acceptance Registers (1st bank). . . . . . . . . . . . . . .351

17-15 Identifier Acceptance Registers (2nd bank) . . . . . . . . . . . . . .351

17-16 Identifier Mask Registers (1st bank). . . . . . . . . . . . . . . . . . . .352

17-17 Identifier Mask Registers (2nd bank) . . . . . . . . . . . . . . . . . . .352

18-1 BDM Host to Target Serial Bit Timing. . . . . . . . . . . . . . . . . . .359

18-2 BDM Target to Host Serial Bit Timing (Logic 1) . . . . . . . . . . .359

18-3 BDM Target to Host Serial Bit Timing (Logic 0) . . . . . . . . . . .360

19-1 VFP Conditioning Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . .393

19-2 VFP Operating Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .394

19-3 Timer Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .395

19-4 POR and External Reset Timing Diagram . . . . . . . . . . . . . . .396

Accumulator A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

Technical Data MC68HC912DG128 — Rev 3.0

16 List of Figures MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

19-5 STOP Recovery Timing Diagram . . . . . . . . . . . . . . . . . . . . . .397

19-6 WAIT Recovery Timing Diagram . . . . . . . . . . . . . . . . . . . . . .398

19-7 Interrupt Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . .399

19-8 Port Read Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . .400

19-9 Port Write Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .400

19-10 Multiplexed Expansion Bus Timing Diagram . . . . . . . . . . . . .402

19-11 SPI Timing Diagram (1 of 2). . . . . . . . . . . . . . . . . . . . . . . . . .404

19-11 A) SPI Slave Timing (CPHA = 0) . . . . . . . . . . . . . . . . . . . . . .405

19-11 B) SPI Slave Timing (CPHA = 1) . . . . . . . . . . . . . . . . . . . . . .405

19-12 SPI Timing Diagram (2 of 2). . . . . . . . . . . . . . . . . . . . . . . . . .405

nc...

I

List of Figures

A) SPI Master Timing (CPHA = 0) . . . . . . . . . . . . . . . . . . . . .4 04

B) SPI Master Timing (CPHA = 1) . . . . . . . . . . . . . . . . . . . . .4 04

cale Semiconductor,

Frees

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA List of Figures 17

For More Information On This Product,

Go to: www.freescale.com

List of Figures

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Technical Data MC68HC912DG128 — Rev 3.0

18 List of Figures MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

Table Title Page

1-1 Device Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . .27

1-2 Development Tools Ordering Information. . . . . . . . . . . . . . . . . 27

2-1 M68HC12 Addressing Mode Summary . . . . . . . . . . . . . . . . . .32

nc...

I

cale Semiconductor,

Frees

2-2 M68HC12 Addressing Mode Summary . . . . . . . . . . . . . . . . . .33

2-3 Summary of Indexed Operations . . . . . . . . . . . . . . . . . . . . . . .34

3-1 Power and Ground Connection Summary . . . . . . . . . . . . . . . .42

3-2 Signal Description Summary . . . . . . . . . . . . . . . . . . . . . . . . . .49

3-3 Port Description Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

3-4 Port Pull-Up, Pull-Down and Reduced Drive Summary . . . . . .60

4-1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

5-1 Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5-2 Mapping Precedence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

5-3 Program space Page Index . . . . . . . . . . . . . . . . . . . . . . . . . . .86

5-4 Flash Register space Page Index. . . . . . . . . . . . . . . . . . . . . . .86

5-5 Test mode program space Page Index. . . . . . . . . . . . . . . . . . .87

5-6 RFSTR Stretch Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . .90

5-7 EXSTR Stretch Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . .91

7-1 Effects of ENPE, LAT and ERAS on Array Reads . . . . . . . . .114

8-1 2K byte EEPROM Block Protection . . . . . . . . . . . . . . . . . . . .129

8-2 Erase Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

9-1 Interrupt Vector Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

9-2 Stacking Order on Entry to Interrupts. . . . . . . . . . . . . . . . . . .1 44

11-1 Summary of STOP Mode Exit Conditions. . . . . . . . . . . . . . . .172

11-2 Summary of Pseudo STOP Mode Exit Conditions . . . . . . . . .173

11-3 Clock Monitor Time-Outs . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

11-4 Real Time Interrupt Rates. . . . . . . . . . . . . . . . . . . . . . . . . . . .186

11-5 COP Watchdog Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

12-1 Clock A and Clock B Prescaler. . . . . . . . . . . . . . . . . . . . . . . .196

12-2 PWM Left-Aligned Boundary Conditions . . . . . . . . . . . . . . . .206

List of Tables

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA List of Tables 19

For More Information On This Product,

Go to: www.freescale.com

List of Tables

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

12-3 PWM Center-Aligned Boundary Conditions . . . . . . . . . . . . . .206

13-1 Compare Result Output Action. . . . . . . . . . . . . . . . . . . . . . . .222

13-2 Edge Detector Circuit Configuration. . . . . . . . . . . . . . . . . . . .223

13-3 Prescaler Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

14-1 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252

14-2 Loop Mode Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255

14-3 SS Output Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265

14-4 SPI Clock Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . .269

15-1 IIC Tap and Prescale Values . . . . . . . . . . . . . . . . . . . . . . . . .282

15-2 IIC Divider and SDA Hold values . . . . . . . . . . . . . . . . . . . . . .283

16-1 ATD Response to Background Debug Enable . . . . . . . . . . . .301

16-2 Final Sample Time Selection . . . . . . . . . . . . . . . . . . . . . . . . .302

16-3 Clock Prescaler Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .303

16-4 Multichannel Mode Result Register Assignment . . . . . . . . . .305

17-1 msCAN12 Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . .324

17-2 msCAN12 vsCPU operating modes . . . . . . . . . . . . . . . . . . . .325

17-3 Data length codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .336

17-4 Synchronization jump width . . . . . . . . . . . . . . . . . . . . . . . . . .341

17-5 Baud rate prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .341

17-6 Time segment syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342

17-7 Time segment values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342

17-8 Identifier Acceptance Mode Settings . . . . . . . . . . . . . . . . . . .349

17-9 Identifier Acceptance Hit Indication . . . . . . . . . . . . . . . . . . . .349

18-1 IPIPE Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .356

18-2 Hardware Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .362

18-3 BDM Firmware Commands . . . . . . . . . . . . . . . . . . . . . . . . . .363

18-4 BDM registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .366

18-5 TTAGO Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .371

18-6 TTAGO Value. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .371

18-7 Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .371

18-8 REGN Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .371

18-9 Breakpoint Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . .378

18-10 Breakpoint Address Range Control . . . . . . . . . . . . . . . . . . . .379

18-11 Breakpoint Read/Write Control. . . . . . . . . . . . . . . . . . . . . . . .380

18-12 Tag Pin Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .383

19-1 Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .386

19-2 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 86

19-3 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . .387

Technical Data MC68HC912DG128 — Rev 3.0

20 List of Tables MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

19-4 Supply Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .389

19-5 ATD DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . .389

19-6 Analog Converter Characteristics (Operating) . . . . . . . . . . . .390

19-7 ATD AC Characteristics (Operating). . . . . . . . . . . . . . . . . . . .391

19-8 ATD Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 91

19-9 EEPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . .392

19-10 Flash EEPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . .392

19-11 Pulse Width Modulator Characteristics. . . . . . . . . . . . . . . . . .394

19-12 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .395

19-13 Peripheral Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .400

19-14 Multiplexed Expansion Bus Timing. . . . . . . . . . . . . . . . . . . . .401

19-15 SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

nc...

I

19-16 CGM Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .406

19-17 Key Wake-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 06

19-18 msCAN12 Wake-up Time from Sleep Mode. . . . . . . . . . . . . .406

20-1 Suggested 8MHz Synthesis PLL Filter Elements

20-2 Suggested 8MHz Synthesis PLL Filter Elements

22-1 EEDIV Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .431

22-2 2K byte EEPROM Block Protection . . . . . . . . . . . . . . . . . . . .433

22-3 Erase Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .434

22-4 Shadow word mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .436

cale Semiconductor,

List of Tables

(Tracking Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .413

(Acquisition Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .414

Frees

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA List of Tables 21

For More Information On This Product,

Go to: www.freescale.com

List of Tables

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Technical Data MC68HC912DG128 — Rev 3.0

22 List of Tables MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

1.1 Contents

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Section 1. General Description

nc...

I

1.2 Introduction

cale Semiconductor,

Frees

1.4 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.5 MC68HC912DG128 Block Diagram. . . . . . . . . . . . . . . . . . . . .28

The MC68HC912DG1 28 microcontroller unit (MCU) is a 16-bit device

composed of standard on-chip peripherals including a 16-bit central

processing un it (CPU12), 128K bytes of flash EEPROM, 8K bytes of

RAM, 2K bytes of EEPROM, two asynchronous seri al comm un ic atio n

interfaces (SCI), a serial peripheral interface (SPI), an inter-IC interface

(I2C), an enhanced capture timer (ECT), two 8- channel,10-bit an alog-todigital converters (ATD), a four-channel pulse-width modulator (PWM),

and two CAN 2.0 A, B software compatible mo dules (MSCAN12).

System resource mapping, clock generation, interrupt control and bus

interfacing are managed by the lite integration module (LIM). The

MC68HC912DG12 8 has full 16- bit data pa ths throug hout, howeve r, the

external bus can operate in an 8-bit narrow mode so single 8-bit wide

memory can be interfaced for l ower cost systems. The inclusion of a PLL

circuit allows pow er consumption and perf ormance to be adjusted to suit

operational requirements. In addition to the I/ O ports available in each

module, 16 I/O po rt pins are availab le with Key-Wake- Up capability from

STOP or WAIT mode.

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA General Description 23

For More Information On This Product,

Go to: www.freescale.com

General Description

1.3 Features

nc...

I

Freescale Semiconductor, Inc.

• 16-bit CPU12

• Multiplexed bus

– Upward compatible with M68HC11 instruction set

– Interrupt stacking and programmer’s model identical to

M68HC11

– 20-bit ALU

– Instruction queue

– Enhanced indexed addressing

– Sin gle chi p or expan ded

cale Semiconductor,

Frees

– 16 address/16 data wide or 16 address/8 data narrow mode

• Memory

– 128K byte flash EEPROM, made of four 32K byte modules

with 8K bytes protected BOOT section in each module

– 2K byte EEPROM

– 8K byte RAM, made of two 4K byte modules with Vstby in each

module.

• Analog-to-digital converters

– 2 times x 8-channels, 10-bit resolution

Technical Data MC68HC912DG128 — Rev 3.0

24 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

• 1M bit per second, CAN 2.0 A, B software compatible modules,

nc...

I

• Enhanced capture timer (ECT)

General Description

Features

two on the MC68HC912DG128, each with:

– Two re ceiv e an d thr ee transm i t buff er s

– Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit or

8x8bit

– Four separate interrupt channels for Rx, Tx, error and wake-up

– Low- pass fi lter wake- up fun cti on

– Loop-back for self test operation

– Programmable link to a timer input capture channel, for time-

stamping and network synchronization.

cale Semiconductor,

Frees

– 16-bit main counter with 7-bit prescaler

– 8 pr og ra m mabl e i npu t ca ptu re or output compare channel s; 4

of the 8 input captures with buffer

– Inpu t capture filters an d buffers, th ree successi ve captures o n

four channels, or two captures on four cha nne l s with a

capture/compare selectable on the remaining four

– Four 8-bit or two 16-bit pulse accumulators

– 16-bit modulus down-counter with 4-bit prescaler

– Four user-selectable delay counters for signal filtering

• 4 PWM channels with programmable period and duty cycle

– 8-bit 4-channel or 16-bit 2-channel

– Separate control for each pulse width and duty cycle

– Center- or left-aligned outputs

– Programmable clock select logic with a wide range of

frequencies

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA General Description 25

For More Information On This Product,

Go to: www.freescale.com

General Description

nc...

I

Freescale Semiconductor, Inc.

• Serial interfaces

• LIM (lite integration module)

– Two asynchronous serial communications interfaces (SCI)

– Inter IC bus interface (I2C)

– Synchronous serial peripheral interface (SPI)

– WCR (windowed COP watchdog, real time interrupt, clock

monitor)

– ROC (reset and clocks)

– MEBI (multiplexed externa l bus interface)

– MBI (internal bus interface and memory map)

cale Semiconductor,

Frees

– INT (interrupt control)

• Two 8-bit ports with key wake-up interrupt

• Clock generation

– Phase-locked loop clock frequency multiplier

– Limp home mode in absence of external clock

– Slow mode divider

– Low power 0.5 to 16 MHz crystal oscillator reference clock

• 112-Pin TQFP package

– Up to 66 general-purpose I/O lines, plus up to 18 input-only

lines

• 8MHz operation at 5V

• Development support

– Single-wire background deb ug™ mode (BDM)

– On-chip hardware breakpoints

Technical Data MC68HC912DG128 — Rev 3.0

26 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

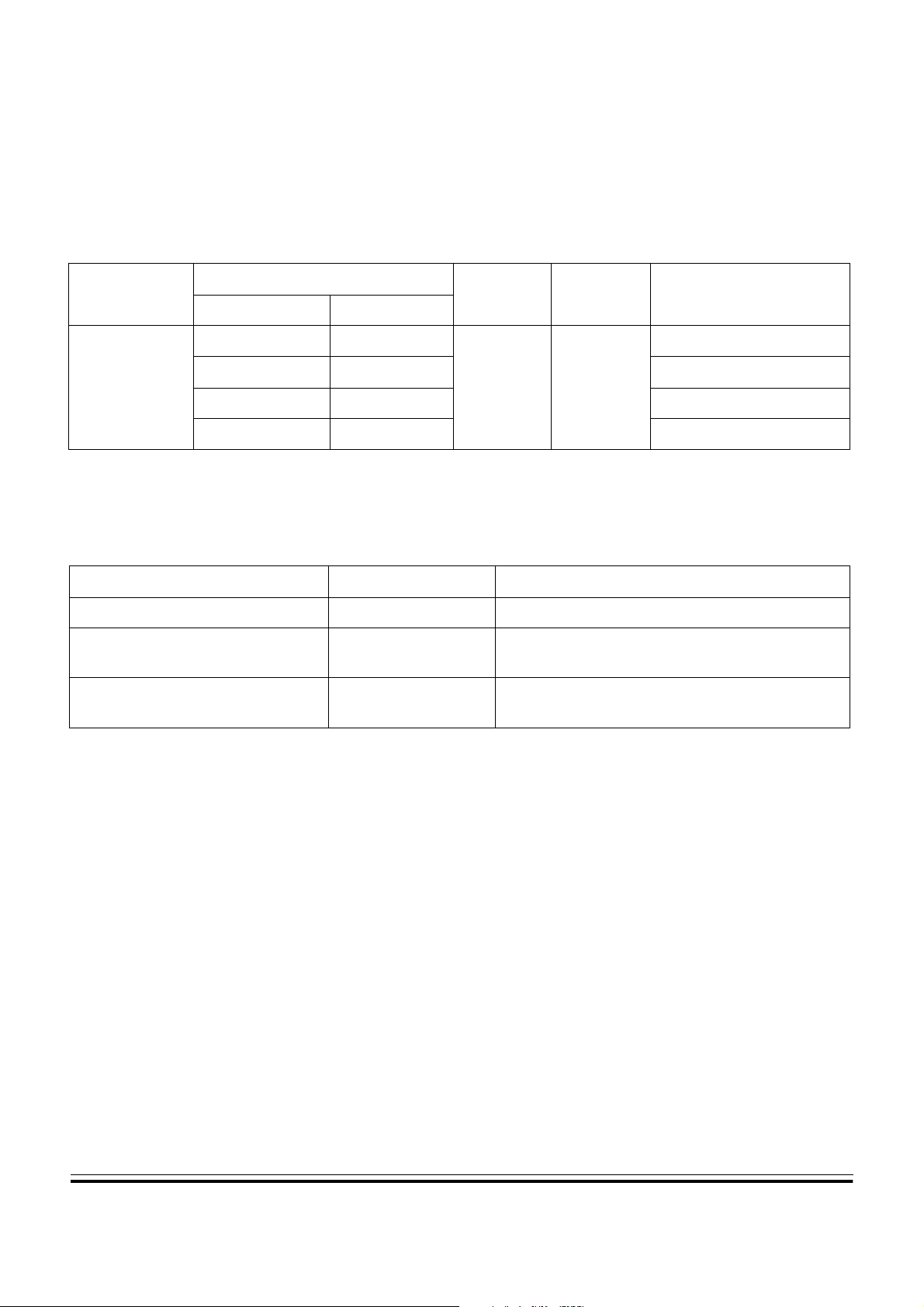

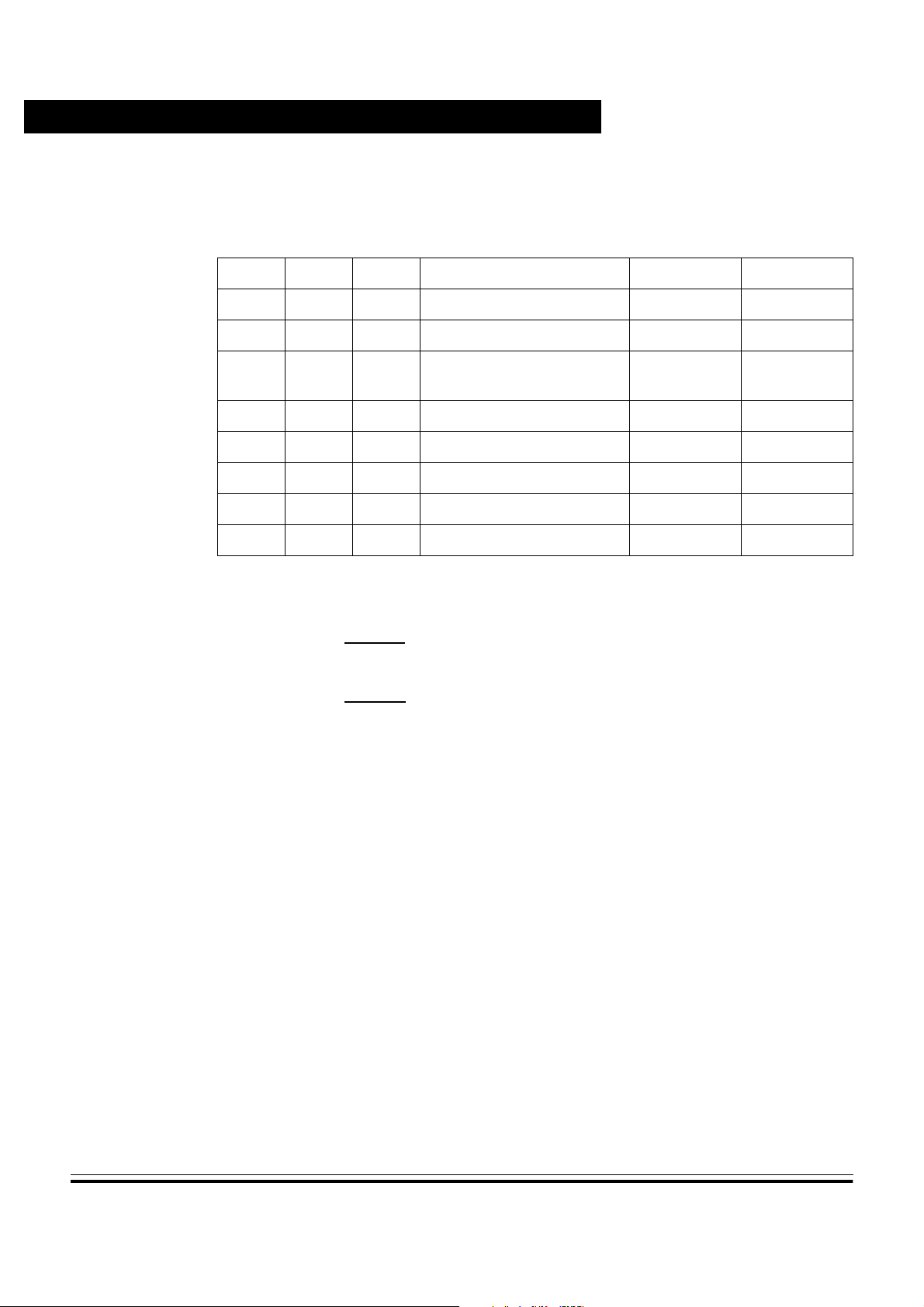

1.4 Ordering Information

Table 1-1. Device Ordering Information

General Description

Ordering Information

Package

0 to +70

112-Pin TQFP

Single Tray

60 Pcs

nc...

I

* Important: M temperature operation is available only for single chip modes

–40 to +85

–40 to +105°C V 68HC91 2DG128VPV8

–40 to +125

Temperature

Voltage Frequency Order Number

Range Designator

°C

°C C 68HC912DG128CPV8

4.5V–5.5V 8 MHz

°C M* 68HC912DG128MPV8

Table 1-2. Development Tools Ordering Information

Description Name Order Numb er

MCUez Free from World Wide Web

Serial Debug Interface SDI

Evaluation board EVB

M68SDIL (3–5V), M68DIL12 (SDIL + MCUez +

SDBUG12)

M68EVB912DG128 (EVB only)

M68KIT912DG128 (EVB + SDIL12)

NOTE: SDBUG12 is a P & E Micro Product. It can be obtained from P & E from

their web site (http://www.pemicro.com) for approximately $100.

cale Semiconductor,

Third party tools: http://www.mcu.motsps.com/dev_tools/3rd/in dex .htm

68HC912DG128PV8

Frees

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA General Description 27

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

General Description

1.5 MC68HC912DG128 Block Diagram

nc...

I

cale Semiconductor,

Frees

VRH1

ATD1

VRL1

VDDA

VSSA

AN10

AN11

AN12

AN13

AN14

AN15

AN16

AN17

DDRT

DDRS

DDRP

DDRK

DDRIB

TxCAN0

RxCAN0

TxCAN1

RxCAN1

VDD ×2

VSS

PORT AD1

PT0

PT1

PT2

PT3

PT4

PT5

PORT T

PT6

PT7

PS0

PS1

PS2

PS3

PS4

PORT S

PS5

PS6

PS7

PP0

PP1

PP2

PP3

PORT P

PK0

PK1

PK2

PK3

PORT K

PK7

PIB7

PIB6

PIB5

PORTIB

PIB4

×2

Power for internal circuitry

VDDX ×2

×2

VSSX

Power for I/O drivers

VRH1

VRL1

VDDA

VSSA

PAD10

PAD11

PAD12

PAD13

PAD14

PAD15

PAD16

PAD17

PORT AD0

SDI/MISO

SDO/MOSI

IIC

DDRH

DDRJ

VRH0

VRL0

IOC0

IOC1

IOC2

IOC3

IOC4

IOC5

IOC6

IOC7

RxD0

TxD0

RxD1

TxD1

SCK

PW0

PW1

PW2

PW3

PIX0

PIX1

PIX2

I/O

ECS

SCL

SDA

PORTH

PORTJ

PAD00

PAD01

PAD02

PAD03

PAD04

PAD05

PAD06

PAD07

SS

I/O

PH7

PH6

PH5

PH4

PH3

PH2

PH1

PH0

PJ7

PJ6

PJ5

PJ4

PJ3

PJ2

PJ1

PJ0

VRH0

ATD0

VFP

VSTBY

BKGD

XFC

VDDPLL

VSSPLL

EXTAL

XTAL

RESET

128K byte flash EEPROM

8K byte RAM

2K byte EEPROM

CPU12

Single-wire

background

debug module

Clock

PLL

Generation

module

Periodic interrupt

COP watchdog

Clock monitor

Breakpoints

VDDA

VSSA

AN00

AN01

AN02

AN03

AN04

AN05

AN06

AN07

Enhanced

capture

timer

SCI0

SCI1

VRL0

SPI

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

XIRQ

IRQ

R/W

LSTRB

ECLK

MODA

PORT E

MODB

DBE/CAL

Lite

integration

module

(LIM)

PWM

PPAGE

Multiplexed Address/Data Bus

KWH7

KWH6

KWH5

KWH4

KWH3

KWH2

KWH1

KWH0

KWU

KWJ7

KWJ6

KWJ5

KWJ4

KWJ3

KWJ2

KWJ1

KWJ0

CAN0

CAN1

Wide

bus

DDRA

PORT A

PA4

PA7

PA6

PA5

5

4

3

2

1

1

1

1

R

R

R

R

D

D

D

D

D

D

D

D

A

A

A

A

DATA15

DATA14

DATA13

DATA12

DATA7

DATA6

DATA5

DATA4

Narrow bus

DDRB

PORT B

PB4

PB3

PB2

PB1

PB7

PB6

PA3

PA2

PA1

PA0

0

1

1

1

9

8

R

R

R

R

D

D

D

D

D

D

D

D

A

A

A

A

DATA11

DATA9

DATA8

DATA10

DATA3

DATA2

DATA1

DATA0

PB5

7

6

5

R

R

R

D

D

D

D

D

D

A

A

A

DATA7

DATA6

DATA5

PB0

4

3

2

1

0

R

R

R

R

R

D

D

D

D

D

D

D

D

D

D

A

A

A

A

A

DATA4

DATA3

DATA2

DATA1

DATA0

Technical Data MC68HC912DG128 — Rev 3.0

28 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

Section 2. Central Processing Unit

2.1 Contents

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

nc...

I

2.2 Introduction

cale Semiconductor,

Frees

2.4 Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.5 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

2.6 Indexed Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.7 Opcodes and Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

The CPU12 is a hi gh-speed, 16-bit processing uni t. It has full 16-b it data

paths and wider internal registers (up to 20 bits) for high-speed extended

math instructions. The instruction set is a proper superset of the

M68HC11instruction set. The CPU12 allows instructions with odd byte

counts, including many single-byte instructions. This provides efficient

use of ROM space. An in struction queue buffers program informatio n so

the CPU always ha s immediate access to at least three bytes of machine

code at the start of every instruction. The CPU12 also offers an

extensive set of indexed addressing cap ab ilities.

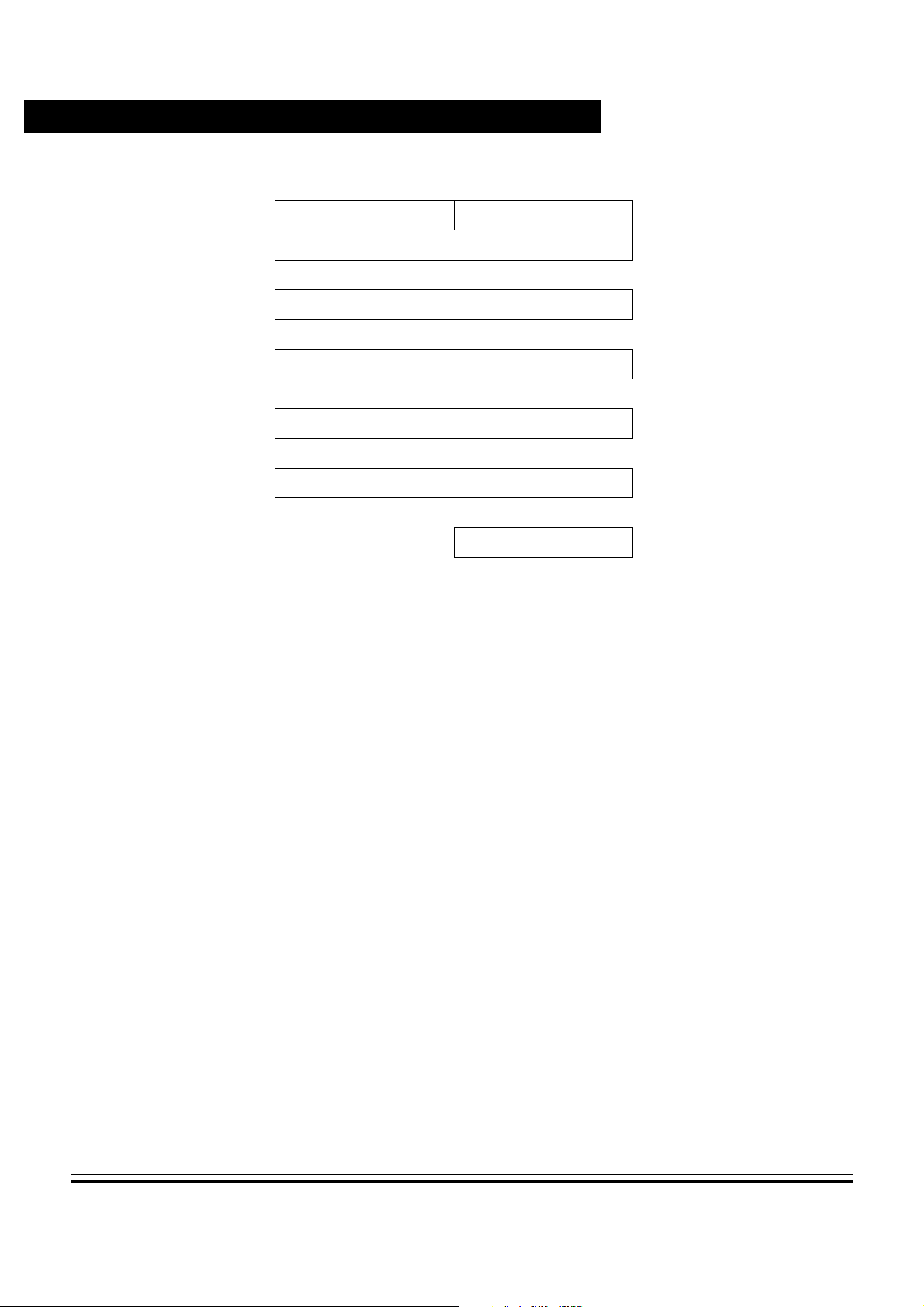

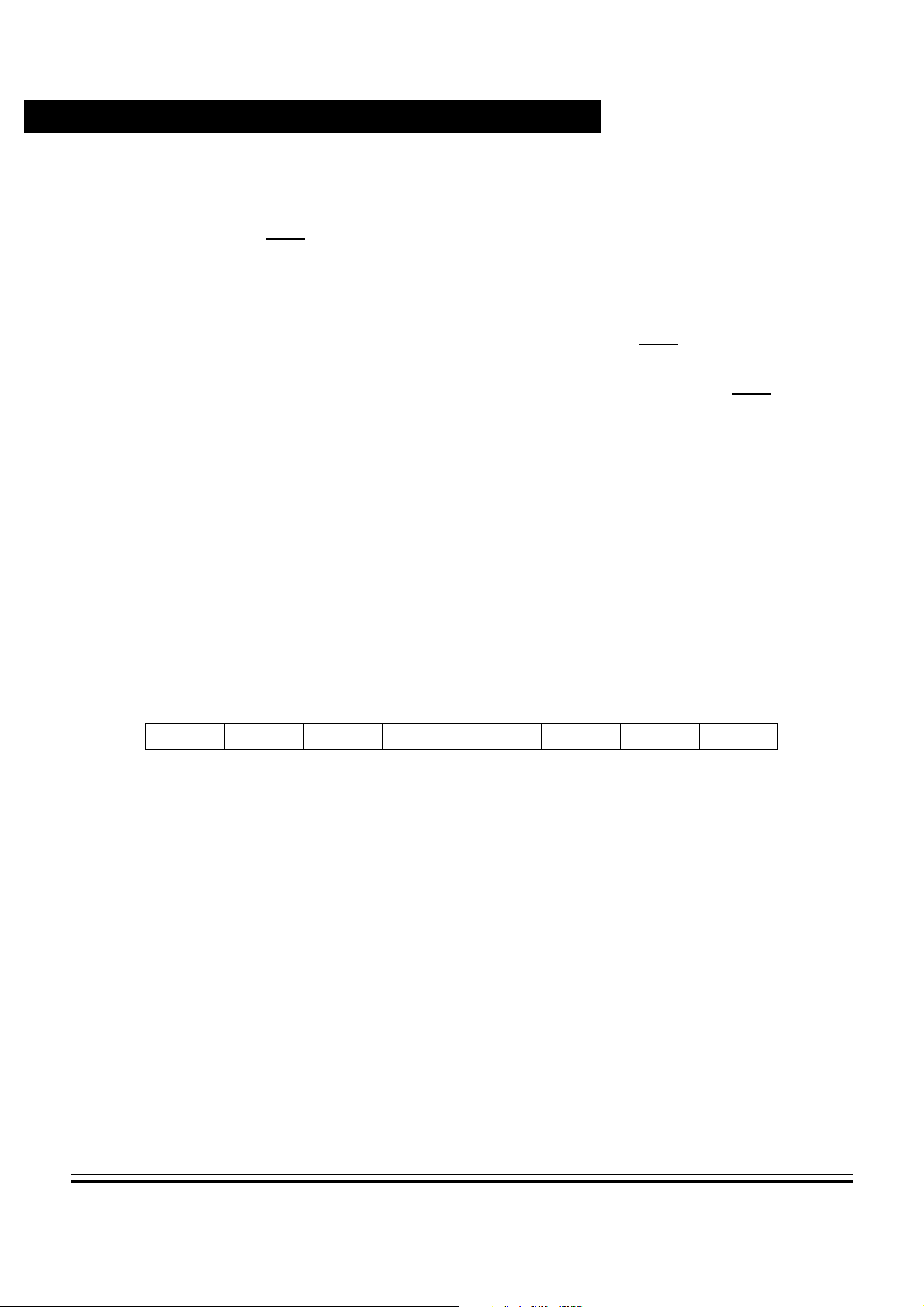

2.3 Programming Model

CPU12 registers are a n inte gral pa rt of t he CPU a nd ar e not ad dressed

as if they were memory locations.

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Central Processing Unit 29

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Central Processing Unit

7

15

15

15

15

nc...

I

15

AB

70

D

IX

IY

SP

PC

NSXHI ZVC

0

8-BIT ACCUMULATORS A & B

OR

0

16-BIT DOUBLE ACCUMULATOR D

0

INDEX REGISTER X

0

INDEX REGISTER Y

0

STACK POINTER

0

PROGRAM COUNTER

CONDITION CODE REGISTER

Figure 2-1. Programming Model

Accumulators A and B are genera l-purpose 8-bit a ccumulators used to

hold operands and results of arithmetic calculations or data

manipulations. Some instructions treat the combination of these two 8bit accumulators as a 16-bit double accumulator (accumulator D).

Index registers X and Y are used for indexed addressing mode. In the

cale Semiconductor,

indexed addressing mode, the contents of a 16-bit index register are

added to 5-bit, 9-bit, or 16-bit constants or the content of an accumulator

to form the effective addr ess of the operand to be used in the i nstruction.

Frees

Stack pointer (SP) points to the last stack location used. The CPU12

supports an automatic program stack that is used to save system

context during su br ou tine calls and interrupts, and can also be u s ed fo r

temporary storage of data. The stack pointer can also be used in all

indexed addressing modes.

Program counter is a 16-bit register that holds the address of the next

instruction to be executed. The program counter can be used in all

indexed addr essing modes except autoinc rement/decrement.

Technical Data MC68HC912DG128 — Rev 3.0

30 Central Processing Unit MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

2.4 Data Types

Freescale Semiconductor, Inc.

Condition Code Register (CCR) contains five status indicators, two

interrupt masking bits, and a STOP disable bit. The five flags are half

carry (H), negative (N), zero (Z), overflow (V), and carry/borrow (C). The

half-carry flag is use d only for BCD arithmetic operations. The N, Z, V,

and C status bits allow for branchin g based on the results of a pr evious

operation.

After a reset, the CPU fetches a vector from the appropriate address and

begins executing instructions. The X and I interrupt mask bits are set to

mask any interrupt requests. The S bit is also set to inhibit the STOP

instruction.

Central Processing Unit

Data Types

cale Semiconductor,

2.5 Addressing Modes

Frees

The CPU12 supports the following data types:

• Bit data

• 8-bit and 16-bit signed and unsigned integers

• 16-bit unsigned fractions

• 16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A

word is composed of two consecutive bytes with the most significant

byte at the lower value address. There are no special requirements for

alignment of instructions or operands.

Addressing modes determine how the CPU accesses memory locations

to be operated upon. The CPU12 includes all of the addressing modes

of the M68HC11 CPU as well as several new forms of indexed

addressing. Table 2-1 is a summary of the available addressing modes.

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Central Processing Unit 31

For More Information On This Product,

Go to: www.freescale.com

Central Processing Unit

Addressing Mode Source Format Abbreviation Description

Inherent

Immediate

Direct INST opr8a DIR

Extended INST opr16a EXT Operand is a 16-bit address

Relative

nc...

I

Indexed

(5-bit offset)

Indexed

(auto pre-decrement)

Indexed

(auto pre-increment)

Indexed

(auto post-

decrement)

Indexed

(auto post-increment)

Indexed

(accumulator offset)

Indexed

(9-bit offset)

Indexed

(16-bit offset)

cale Semiconductor,

Indexed-Indirect

(16-bit offset)

Indexed-Indirect

Frees

(D accumulator

offset)

Freescale Semiconductor, Inc.

Table 2-1. M68HC12 A ddressing Mode Summary

INST

(no externally supplied

operands)

INST #opr8i

or

INST #opr16i

INST rel8

or

INST rel16

INST oprx5,xysp IDX 5-bit signed constant offset from x, y, sp, or pc

INST oprx3,–xys IDX Auto pre-decrement x, y, or sp by 1 ~ 8

INST oprx3,+xys IDX Auto pre-increment x, y, or sp by 1 ~ 8

INST oprx3,xys– IDX Auto post-decrement x, y, or sp by 1 ~ 8

INST oprx3,xys+ IDX Auto post-increment x, y, or sp by 1 ~ 8

INST abd,xysp IDX

INST oprx9,xysp IDX1

INST oprx16,xysp IDX2

INST [oprx16,xysp] [IDX2]

INST [D,xysp] [D,IDX]

INH Operands (if any) are in CPU registers

IMM

REL

Operand is included in instruction stream

8- or 16-bit size implied by context

Operand is the lower 8-bits of an address in the

range $0000 – $00FF

An 8-bit or 16-bit relative offset from the current

pc is supplied in the instruction

Indexed with 8-bit (A or B) or 16-bit (D)

accumulator offset from x, y, sp, or pc

9-bit signed constant offset from x, y, sp, or pc

(lower 8-bits of offset in one extension byte)

16-bit constant offset from x, y, sp, or pc

(16-bit offset in two extension bytes)

Pointer to operand is found at...

16-bit constant offset from x, y, sp, or pc

(16-bit offset in two extension bytes)

Pointer to operand is found at...

x, y, sp, or pc plus the value in D

Technical Data MC68HC912DG128 — Rev 3.0

32 Central Processing Unit MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Central Processing Unit

Table 2-2. M68HC12 A ddressing Mode Summary

Addressing Mode Source Format Abbreviation Description

INST

Inherent

(no externally

supplied operands)

INH Operands (if any) are in CPU registers

Addressing Modes

nc...

I

cale Semiconductor,

Frees

INST #opr8i

Immediate

Direct INST opr8a DIR

Extended INST opr16a EXT Operand is a 16-bit address

Relative

Indexed

(5-bit offset)

Indexed

(auto pre-decrement)

Indexed

(auto pre-increment)

Indexed

(auto post-decrement)

Indexed

(auto post-increment)

Indexed

(accumulator offset)

Indexed

(9-bit offset)

INST oprx5,xysp IDX

INST oprx3,–xys IDX Auto pre-decrement x, y, or sp by 1 ~ 8

INST oprx3,+xys IDX Auto pre-increment x, y, or sp by 1 ~ 8

INST oprx3,xys– IDX Auto post-decrement x, y, or sp by 1 ~ 8

INST oprx3,xys+ IDX Auto post-increment x, y, or sp by 1 ~ 8

INST oprx9,xysp IDX1

or

INST #opr16i

INST rel8

or

INST rel16

INST abd,xysp IDX

IMM

REL

Operand is included in instruction stream

8- or 16-bit size implied by context

Operand is the lower 8-bits of an address in

the range $0000 – $00FF

An 8-bit or 16-bit relative offset from the

current pc is supplied in the instruction

5-bit signed constant offset from x, y, sp, or

pc

Indexed with 8-bit (A or B) or 16-bit (D)

accumulator offset from x, y, sp, or pc

9-bit signed constant offset from x, y, sp, or

pc

(lower 8-bits of offset in one extension byte)

Indexed

(16-bit offset)

Indexed-Indirect

(16-bit offset)

Indexed-Indirect

(D accumulator offset)

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Central Processing Unit 33

INST oprx16,xysp IDX2

INST [oprx16,xysp] [IDX2]

INST [D,xysp] [D,IDX]

For More Information On This Product,

Go to: www.freescale.com

16-bit constant offset from x, y, sp, or pc

(16-bit offset in two extension bytes)

Pointer to operand is found at...

16-bit constant offset from x, y, sp, or pc

(16-bit offset in two extension bytes)

Pointer to operand is found at...

x, y, sp, or pc plus the value in D

Freescale Semiconductor, Inc.

Central Processing Unit

2.6 Indexed Addressing Modes

The CPU12 indexed modes reduce execution time and eliminate code

size penalties fo r using the Y inde x register. CP U12 indexed ad dressing

uses a postbyte plus zero, one, or two extension bytes after the

instruction opcode. The postbyte and extension s do th e fo llowing ta sks:

• Specify which index register is used.

• Determine whethe r a value in an accumula tor is used as an offset.

• Enable automatic pre- or post-increment or decrement

• Specify use of 5-bit, 9-bit, or 16-bit signed offsets.

nc...

I

cale Semiconductor,

Frees

Table 2-3. Summary of Indexed Operations

Postbyte

Code (xb)

rr0nnnnn

111rr0zs

111rr011 [n,r]

rr1pnnnn

111rr1aa

Source

Code

Syntax

,r

n,r

–n,r

n,r

–n,r

n,–r n,+r

n,r– n,r+

A,r

B,r

D,r

Comments

5-bit constant offset n = –16 to +15

rr can specify X, Y, SP, or PC

Constant offset (9- or 16-bit signed)

z-0 = 9-bit with sign in LSB of postbyte(s)

1 = 16-bit

if z = s = 1, 16-bit offset indexed-indirect (see below)

rr can specify X, Y, SP, or PC

16-bit offset indexed-indirect

rr can specify X, Y, SP, or PC

Auto pre-decrement/incremen t or Auto post-

decrement/increment;

p = pre-(0) or post-(1), n = –8 to –1, +1 to +8

rr can specify X, Y, or SP (PC not a valid choice)

Accumulator offset (unsigned 8-bit or 16-bit)

aa-00 = A

01 = B

10 = D (16-bit)

11 = see accumulator D offset indexed-indirect

rr can specify X, Y, SP, or PC

111rr111 [D,r]

Technical Data MC68HC912DG128 — Rev 3.0

34 Central Processing Unit MOTOROLA

For More Information On This Product,

Accumulator D offset indexed-indirect

rr can specify X, Y, SP, or PC

Go to: www.freescale.com

Freescale Semiconductor, Inc.

2.7 Opcodes and Operands

The CPU12 uses 8-bit opcodes. Each opcode identifies a particular

instruction and associated addressing mode to the CPU. Several

opcodes are required to provide each instruction with a range of

addressing capabilities.

Only 256 opcodes would be available if the range of values were

restricted to the number that can be represented by 8-bit binary

numbers. To expand the num ber of opcodes, a second page i s added to

the opcode map. Opcodes on the second page are preceded by an

additional byte with the value $18.

Central Processing Unit

Opcodes and Operands

nc...

I

cale Semiconductor,

Frees

To provide additional addressing flexibility, opcodes can also be

followed by a postby te or ex tensio n by tes. Postb ytes impl eme nt cert ain

forms of indexed addr essing, transfers, e xchanges, and l oop primitiv es.

Extension bytes contain additional program information such as

addresses, offsets, and immedi at e data .

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Central Processing Unit 35

For More Information On This Product,

Go to: www.freescale.com

Central Processing Unit

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Technical Data MC68HC912DG128 — Rev 3.0

36 Central Processing Unit MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Technical Data — MC68HC912DG128

Section 3. Pinout and Signal Descriptions

3.1 Contents

3.2 Pin Assignments in 112-pin QFP . . . . . . . . . . . . . . . . . . . . . . .37

3.3 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

nc...

I

3.4 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

3.5 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

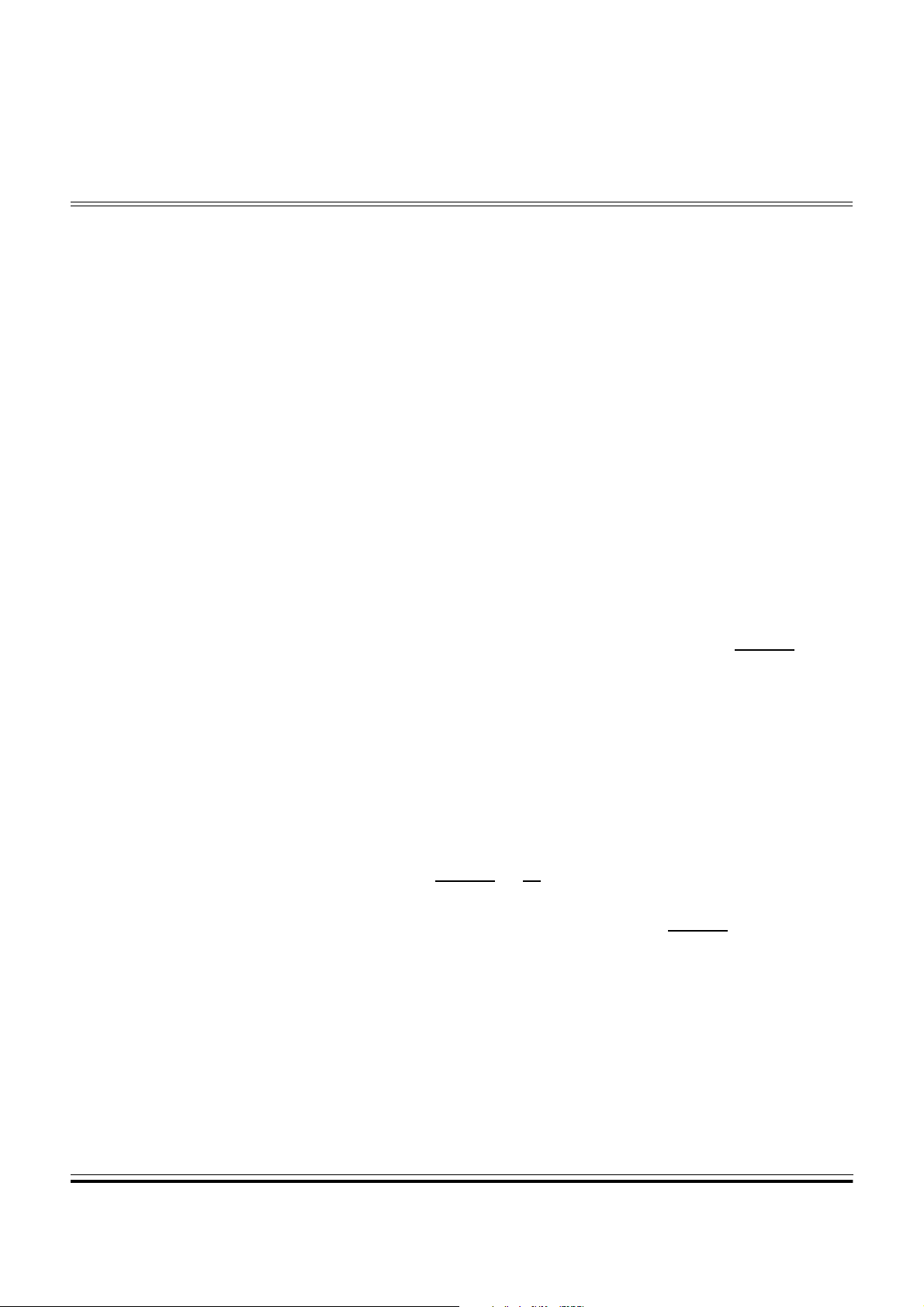

3.2 Pin Assignments in 112-pin QFP

The MC68HC912DG128 is available in a 112-pin thin quad flat pack

(TQFP). Most pins perform two or more functions, as described in the

Signal Descriptions. Figure 3-2 shows pin assignments. In expanded

narrow modes the lower byte data is multiplexed with higher byte data

through pins 57-64.

cale Semiconductor,

Frees

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Pinout and Signal Descriptions 37

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pinout and Signal Descriptions

nc...

I

cale Semiconductor,

Frees

PP3/PW3

PK0/PIX0

PK1/PIX1

111

112

V

PK3

V

1

2

3

4

5

6

7

8

9

10

11

12

DD

13

14

SS

15

16

17

18

19

20

21

22

23

24

25

26

27

28

293031323334353637383940414243444546474849505152535455

ADDR5/DATA5/PB5

ADDR6/DATA6/PB6

ADDR7/DATA7/PB7

PW2/PP2

PW1/PP1

PW0/PP0

IOC0/PT0

IOC1/PT1

IOC2/PT2

IOC3/PT3

KWJ7/PJ7

KWJ6/PJ6

KWJ5/PJ5

KWJ4/PJ4

IOC4/PT4

IOC5/PT5

IOC6/PT6

SMODN/TAGHI/

IOC7/PT7

KWJ3/PJ3

KWJ2/PJ2

KWJ1/PJ1

KWJ0/PJ0

BKGD

ADDR0/DATA0/PB0

ADDR1/DATA1/PB1

ADDR2/DATA2/PB2

ADDR3/DATA3/PB3

ADDR4/DATA4/PB4

DDXVSSX

PK2/PIX2

PK7/ECS

V

RxCAN0

TxCAN0

RxCAN1

TxCAN1

PIB4

110

109

108

107

106

105

104

103

102

101

MC68HC912DG128

SSX

V

CAL/PE7

KWH7/PH7

KWH6/PH6

KWH5/PH5

KWH4/PH4

ECLK/PE4

DBE/

MODB/IPIPE1/PE6

MODA/IPIPE0/PE5

*

PIB5

100

VSTBY

FP

PIB6/SDA

PIB7/SCL

V

PS7/SS

PS6/SCK

PS5/SDO/MOSI

PS4/SDI/MISO

PS3/TxD1

PS2/RxD1

999897969594939291908988878685

112TQFP

DDX

XFC

V

DDPLL

V

XTAL

SSPLL

EXTAL

V

RESET

KWH3/PH3

KWH2/PH2

PS1/TxD0

KWH1/PH1

SSAVRL1VRH1VDDA

PS0/RxD0

V

KWH0/PH0

/TAGLO/PE3

LSTRB

/PE2

R/W

/PE1

IRQ

84

PAD17/AN17

83

PAD07/AN07

82

PAD16/AN16

81

PAD06/AN06

80

PAD15/AN15

79

PAD05/AN05

78

PAD14/AN14

77

PAD04/AN04

76

PAD13/AN13

75

PAD03/AN03

74

PAD12/AN12

73

PAD02/AN02

72

PAD11/AN11

71

PAD01/AN01

70

PAD10/AN10

69

PAD00/AN00

68

V

RL0

67

V

RH0

66

V

SS

65

V

DD

64

PA7/ADDR15/DATA15/DATA7

63

PA6/ADDR14/DATA14/DATA6

62

PA5/ADDR13/DATA13/DATA5

61

PA4/ADDR12/DATA12/DATA4

60

PA3/ADDR11/DATA11/DATA3

59

PA2/ADDR10/DATA10/DATA2

58

PA1/ADDR9/DATA9/DATA1

57

PA0/ADDR8/DATA8/DATA0

56

/PE0

XIRQ

Figure 3-1. MC68HC912DG128 Pin Assignments in 112-pin QFP

Technical Data MC68HC912DG128 — Rev 3.0

38 Pinout and Signal Descriptions MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pin Assignments in 112-pin QFP

Pinout and Signal Descriptions

nc...

I

cale Semiconductor,

Frees

PIN 1

IDENT

C

4X

112 85

1

VIEW Y

L

28 57

29 56

C2

0.050

C1

VIEW AB

S1

A1

T

L-M0.20 N

4X 28 TIPS

N

A

S

2θ

3

θ

θ

R

R2

R1

R

(K)

E

(Y)

(Z)

L-M0.20 NT

84

V

B

M

B1

V1

VIEW AB

112X

T

0.10

SEATING

PLANE

T

0.25

GAGE PLANE

1θ

J1

J1

C

L

108X

J

0.13 NT

SECTION J1-J1

ROTATED 90 COUNTERCLOCKWISE

°

NOTES:

1. DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

2. DIMENSIONS IN MILLIMETERS.

3. DATUMS L, M AND N TO BE DETERMINED AT

SEATING PLANE, DATUM T.

4. DIMENSIONS S AND V TO BE DETERMINED AT

SEATING PLANE, DATUM T.

5. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION. ALLOWABLE

PROTRUSION IS 0.25 PER SIDE. DIMENSIONS

A AND B INCLUDE MOLD MISMATCH.

6. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL NOT CAUSE THE D

DIMENSION TO EXCEED 0.46.

DIMAMIN MAX

A1 10.000 BSC

B 20.000 BSC

B1 10.000 BSC

C --- 1.600

C1 0.050 0.150

C2 1.350 1.450

D 0.270 0.370

E 0.450 0.750

F 0.270 0.330

G 0.650 BSC

J 0.090 0.170

K 0.500 REF

P 0.325 BSC

R1 0.100 0.200

R2 0.100 0.200

S 22.000 BSC

S1 11.000 BSC

V 22.000 BSC

V1 11.000 BSC

Y 0.250 REF

Z 1.000 REF

AA 0.090 0.160

θ

θ

1

θ

2

θ

3

G

VIEW Y

F

D

M

MILLIMETERS

20.000 BSC

0 °

3 °

11 °

11 °

4X

P

X

X=L, M OR N

AA

L-M

8 °

7 °

13 °

13 °

BASE

METAL

Figure 3-2. 112-pin QFP Mechanical Dimensions (case no. 987)

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Pinout and Signal Descriptions 39

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pinout and Signal Descriptions

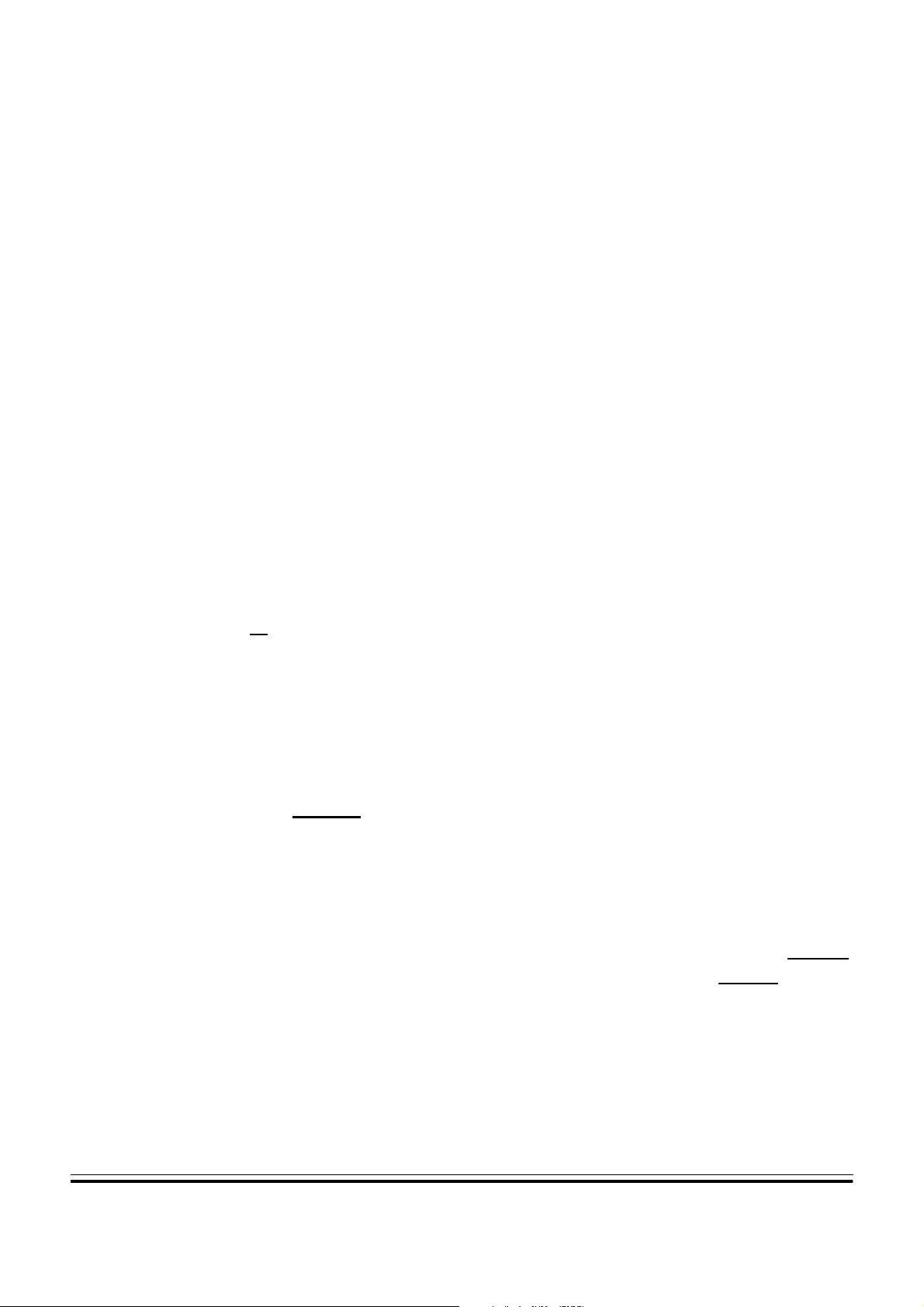

3.3 Power Supply Pins

Power and ground pins are described below and summarized in Table

3-1.

3.3.1 Internal Power (VDD) and Ground (VSS)

Power is supplied to the MCU through VDD and VSS. Because fast signal

transitions place high, short-duration current demands on the power

supply, use bypass capacitors with high-frequency characteristics and

place them as close to the MCU as possible. Bypass requirements

nc...

I

depend on how heavily the MCU pins are loaded.

3.3.2 External Power (V

3.3.3 V

DDA

, V

cale Semiconductor,

External power and ground for I/O drivers. Because fast signal

transitions place high, short-duration current demands on the power

supply, use bypass capacitors with high-frequency characteristics and

place them as close to the MCU as possible. Bypass requirements

depend on how heavily the MCU pins are loaded.

SSA

Provides operating volt age and gr ou nd for the ana l og-to-digital

converter. This allows the supply voltage to the ATD to be bypassed

independently. Connecting V

used will not result in an increase of power consumption.

and Ground (V

DDX)

Frees

3.3.4 Analog to Digital Reference Voltages (VRH, VRL)

V

RH0

, V

: reference voltage high and low for ATD converter 0.

RL0

SSX

)

to VDD if the ATD modules are not

DDA

V

, V

RH1

If the ATD modules are not use d, leavin g VRH connected to VDD will not

result in an increase of power consumption.

Technical Data MC68HC912DG128 — Rev 3.0

40 Pinout and Signal Descriptions MOTOROLA

For More Information On This Product,

: reference voltage high and low for ATD converter 1.

RL1

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pinout and Signal Descriptions

Power Supply Pins

nc...

I

cale Semiconductor,

Frees

3.3.5 V

DDPLL

3.3.6 XFC

, V

SSPLL

Provides operating voltage and ground for the P hase-Locked Loop. This

allows the supply voltage to the PLL to be bypassed independently.

NOTE: The VSSP LL pin should always be grou nded even if the PLL is not used.

The VDDPLL pin should not be left floating. It is recommended to

connect the VDDPLL pin to ground if the PLL is not used.

PLL loop filter. Please see Appendix: CGM Practical Aspects for

information on how to calculate PLL loop filter elements. Any current

leakage on this pin must be avoided.

VDDPLL

C

0

MCU

XFC

R

0

Figure 3-3. PLL Loop FIlter Connections

If VDDPLL is connected to VS S (t hi s is norm a l case ) , then the XFC pin

should either be left floating or connected to VSS (never to VDD). If

VDDPLL is tied to VD D but the PLL is switch ed off (PLLON bit cleare d),

then the XFC pin should be connected pre ferably t o VDDPLL ( i.e. read y

for VCO minimum frequency).

C

p

3.3.7 V

FP

Flash EEPROM program/erase voltage and supply voltage during

normal operation.

MC68HC912DG128 — Rev 3.0 Technical Data

MOTOROLA Pinout and Signal Descriptions 41

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pinout and Signal Descriptions

nc...

I

3.3.8 V

STBY

Mnemonic

V

DD

V

SS

V

DDX

V

SSX

V

DDA

V

SSA

V

RH1

V

RL1

V

RH0

V

RL0

V

DDPLL

V

SSPLL

V

FP

V

STBY

Pin Number

112-pin QFP

cale Semiconductor,

3.4 Signal Descriptions

Stand-by voltage supp ly to static RAM . Used to mainta in the contents of

RAM with minimal power when the rest of the chip is powered down.

Table 3-1. Power and Ground Connection Summary

Description

12, 65

14, 66

42, 107

40, 106

85

88

86

87

67

68

43

45

97

41

Internal power and ground.

External power and ground, supply to pin drivers.

Operating voltage and ground for the analog-to-digital converter, allows the

supply voltage to the A/D to be bypassed independently.

Reference voltages for the analog-to-digital converter 1

Reference voltages for the analog-to-digital converter 0.

Provides operating voltage and ground for the Phase-Locked Loop. This allows

the supply voltage to the PLL to be bypassed independently.

Program/erase voltage for the Flash EEPROM and required supply for normal

operation.

Stand-by voltage supply to maintain the contents of RAM with minimal power

when the rest of the chip is powered down.

Frees

3.4.1 Crystal Driver and External Clock Input (XTAL, EXTAL)

These pins provide the interface for either a crystal or a CMOS

compatible clock to control the internal clock generator circuitry. Out of

reset the frequency app lied to EXTAL is tw ice t he desir ed E–clock rate .

All the device clocks are derived from the EXTAL input frequency.

NOTE: CRYSTAL CIRCUIT IS CHANGED FROM STANDARD.

Technical Data MC68HC912DG128 — Rev 3.0

42 Pinout and Signal Descriptions MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Pinout and Signal Descriptions

Signal Descriptions

NOTE: The inte rnal return p ath for the osci llator is th e VSSPLL pin. Th erefore it

is recommended t o conne ct the co mmo n node of the reson ator and th e

capacitor d irectly to the VSSPLL pin.

2 x E crystal or ceramic resonator

EXTAL

nc...

I

cale Semiconductor,

Frees

MCU

XTAL

C1

C2

Figure 3-4. Common Crystal Connections

NOTE: When se lecting a cr ystal, it is r ecommended t o use one w ith the lo west

possible frequency in order to minimise EMC emissions.

2 x E

CMOS-COMPATIBLE

MCU

EXTAL

XTAL

NC

EXTERNAL OSCILLATOR

Figure 3-5. External Oscillator Connections