Datasheet MC68HC711P2CFS4, MC68HC711P2CFN3, MC68HC711P2CFN4, MC68HC11P0CFN3, MC68HC11P1CFN3 Datasheet (Motorola)

...

M68HC11

Microcontrollers

MC68HC11P2

MC68HC711P2

Technical Data

MC68HC11P2/D

Rev. 1, 4/2002

WWW.MOTOROLA.COM/SEMICONDUCTORS

MC68HC11P2

MC68HC711P2

Technical Data — Rev 1.0

Motorola reserves the righ t to make changes without further notice to any products

herein. Motorola makes no warranty, representation or guarantee regarding the

suitability of i ts products for any partic ular purpose, nor does Moto rola assume any

liability arising out of the application or use of any prod uct or circuit, and s pecifically

disclaims any an d all liability, including withou t limitation consequential or inc idental

damages. "Typical" parameters which may be provided in Motorola data sheets and/or

specifications can an d do vary in different applications and actua l performance may

vary over time. A ll operating parameters, i ncluding "Typicals" must be validated for

each customer application by customer’s technical experts. Motorola does not convey

any license under i ts patent rights nor the rig hts of others. Motorola prod ucts are not

designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other applicat ion in wh ich the failure of the Mo torola pr oduct could cr eate a

situation where personal injury or death may oc cur. Should Buyer purchase o r use

Motorola products for any such unintended or una uthorized application, Buye r shall

indemnify and hold Motorola and its officers, employees, subsid iaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of personal

injury or death associated with such unintended or unauthorized use, even if such claim

alleges that Motorola was negligent reg arding the design o r manufacture of the p art.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Motorola, Inc., 2002

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA 3

Technical Data MC68HC11P2 — Rev 1.0

4 MOTOROLA

Technical Data — MC68HC11P2

List of Paragraphs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Section 1. General Description . . . . . . . . . . . . . . . . . . . .17

Section 2. Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . .21

Section 3. Operating Modes and On-Chip Memory . . . .41

Section 4. Parallel In put/Output. . . . . . . . . . . . . . . . . . . .73

Section 5. Serial Communications Interface (SCI). . . . .87

List of Paragraphs

Section 6. Motorola Interconnect Bus (MI BUS). . . . . .109

Section 7. Serial Peripheral Interface (SPI). . . . . . . . . .125

Section 8. Timing System. . . . . . . . . . . . . . . . . . . . . . . .137

Section 9. Analog-to-Digital Converter . . . . . . . . . . . . .173

Section 10. Resets and Interrupts. . . . . . . . . . . . . . . . .185

Section 11. CPU Core and Instruction Set . . . . . . . . . .213

Section 12. Electrical Specificatio ns. . . . . . . . . . . . . . .231

Section 13. Mechanical Data . . . . . . . . . . . . . . . . . . . . .247

Section 14. Ordering Information . . . . . . . . . . . . . . . . .251

Section 15. Development Support. . . . . . . . . . . . . . . . .253

Glossary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA List of Paragraphs 5

List of Paragraphs

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265

Technical Data MC68HC11P2 — Rev 1.0

6 List of Paragraphs MOTOROLA

Technical Data — MC68HC11P2

1.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Table of Contents

List of Paragraphs

Table of Contents

List of Figures

List of Tables

Section 1. General Description

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Section 2. Pin Descriptions

2.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.3 VDD and VSS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.4 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.5 Crystal driver and external clock input (XTAL, EXTAL) . . . . . .24

2.6 E clock output (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.7 Phase-locked loop (XFC, VDDSYN). . . . . . . . . . . . . . . . . . . . .26

2.8 Interrupt request (IRQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2.9 Nonmaskable interrupt (XIRQ/VPPE). . . . . . . . . . . . . . . . . . . .32

2.10 MODA and MODB (MODA/LIR and MODB/VSTBY) . . . . . . . .33

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Table of Contents 7

Table of Contents

2.11 VRH and VRL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.12 PG7/R/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.13 Port signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Section 3. Operating Modes and On-Chip Memory

3.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.3 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.4 On-chip memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.5 System initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.6 EPROM, EEPROM and CONFIG register . . . . . . . . . . . . . . . .64

Section 4. Parallel Input/Output

4.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.3 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

4.4 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

4.5 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

4.6 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

4.7 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

4.8 Port F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

4.9 Port G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

4.10 Port H . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

4.11 Internal pull-up/pull-down resistors. . . . . . . . . . . . . . . . . . . . . .83

4.12 System configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Technical Data MC68HC11P2 — Rev 1.0

8 Table of Conten ts MOTOROLA

Table of Contents

Section 5. Serial Communications Interface (SCI)

5.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

5.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

5.3 Data format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

5.4 Transmit operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

5.5 Receive operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

5.6 Wakeup feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

5.7 SCI error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.8 SCI registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

5.9 Status flags and interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . .101

5.10 Additional SCI subsystems. . . . . . . . . . . . . . . . . . . . . . . . . . .104

Section 6. Motorola Interconnect Bus (MI BUS)

6.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

6.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

6.3 Push-pull sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

6.4 The push field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

6.5 The pull field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

6.6 Biphase coding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

6.7 Message validation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

6.8 Interfacing to MI BUS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

6.9 MI BUS clock rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

6.10 SCI/MI BUS2 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

6.11 SCI/MI BUS3 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Table of Contents 9

Table of Contents

Section 7. Serial Peripheral Interface (SPI)

7.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

7.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

7.3 Functional description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

7.4 SPI transfer formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 26

7.5 SPI signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

7.6 SPI system errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

7.7 SPI registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

Section 8. Timing System

8.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

8.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

8.3 Timer structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

8.4 Input capture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

8.5 Output compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 45

8.6 Real-time interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

8.7 Computer operating properly watchdog function . . . . . . . . . .157

8.8 Pulse accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

8.9 Pulse-width modulation (PWM) timer . . . . . . . . . . . . . . . . . . .1 62

Section 9. Analog-to-Digital Converter

9.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

9.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

9.3 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

9.4 A/D converter power-up and clock select. . . . . . . . . . . . . . . .178

9.5 Channel assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 80

9.6 Control, status and results registers. . . . . . . . . . . . . . . . . . . .181

Technical Data MC68HC11P2 — Rev 1.0

10 Table of Contents MOTOROLA

Table of Contents

9.7 Operation in STOP and WAIT modes. . . . . . . . . . . . . . . . . . .184

Section 10. Resets and Interrupts

10.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

10.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

10.3 Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

10.4 Effects of reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192

10.5 Reset and interrupt priority . . . . . . . . . . . . . . . . . . . . . . . . . . .195

10.6 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

10.7 Low power operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

Section 11. CPU Core and Instruction Set

11.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

11.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

11.3 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

11.4 Data types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

11.5 Opcodes and operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

11.6 Addressing modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

11.7 Instruction set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 23

Section 12. Electrical Specifications

12.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .231

12.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .231

12.3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .232

12.4 Thermal characteristics and power considerations. . . . . . . . .233

12.5 Test methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .234

12.6 DC electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . .235

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Table of Contents 11

Table of Contents

12.7 Control timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

Section 13. Mechanical Data

13.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .247

13.2 Pin assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .248

13.3 Package dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .249

Section 14. Ordering Information

14.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

14.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

Section 15. Development Support

15.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

15.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

15.3 EVS — Evaluation system . . . . . . . . . . . . . . . . . . . . . . . . . . .2 53

Glossary

Revision History

15.4 Major Changes Between Revision 1.0 and Revision 0.0 . . . .265

Technical Data MC68HC11P2 — Rev 1.0

12 Table of Contents MOTOROLA

Technical Data — MC68HC11P2

Figure Title Page

1-1 MC68HC11P2/MC68HC711P2 block diagram. . . . . . . . . . . . . 19

2-1 84-pin PLCC/CERQUAD pinout. . . . . . . . . . . . . . . . . . . . . . . .22

2-2 External reset circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2-3 Oscillator connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2-4 PLL circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2-5 RAM stand-by connections. . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3-1 MC68HC11P2 memory map. . . . . . . . . . . . . . . . . . . . . . . . . . .44

3-2 RAM and register overlap. . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

5-1 SCI baud rate generator circuit diagram. . . . . . . . . . . . . . . . . .88

5-2 SCI1 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

5-3 Interrupt source resolution within SCI. . . . . . . . . . . . . . . . . . .1 03

6-1 MI BUS timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

6-2 Biphase coding and error detection . . . . . . . . . . . . . . . . . . . .113

6-3 MI BUS block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

6-4 A typical interface between the MC68HC11P2 and the MI BUS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

7-1 SPI block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

7-2 SPI transfer format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

8-1 Timer clock divider chains . . . . . . . . . . . . . . . . . . . . . . . . . . .140

8-2 Capture/compare block diagram. . . . . . . . . . . . . . . . . . . . . . .141

8-3 Pulse accumulator block diagram. . . . . . . . . . . . . . . . . . . . . .159

8-4 PWM timer block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . .164

8-5 PWM duty cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

9-1 A/D converter block diagram . . . . . . . . . . . . . . . . . . . . . . . . .174

9-2 Electrical model of an A/D input pin (in sample mode). . . . . .175

9-3 A/D conversion sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . .177

10-1 Processing flow out of reset (1 of 2). . . . . . . . . . . . . . . . . . . .206

10-2 Processing flow out of reset (2 of 2). . . . . . . . . . . . . . . . . . . .207

10-3 Interrupt priority resolution (1 of 3) . . . . . . . . . . . . . . . . . . . . .208

List of Figures

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA List of Figures 13

List of Figures

10-4 Interrupt priority resolution (2 of 3) . . . . . . . . . . . . . . . . . . . . .209

10-5 Interrupt priority resolution (3 of 3) . . . . . . . . . . . . . . . . . . . . .210

10-6 Interrupt source resolution within the SCI subsystem. . . . . . .211

11-1 Programming model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

11-2 Stacking operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 16

12-1 Test methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 34

12-2 Timer inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

12-3 Reset timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238

12-4 Interrupt timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238

12-5 STOP recovery timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .239

12-6 WAIT recovery timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .239

12-7 Port read timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . .240

12-8 Port write timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . .240

12-9 SPI master timing (CPHA = 0) . . . . . . . . . . . . . . . . . . . . . . . .243

12-10 SPI master timing (CPHA = 1) . . . . . . . . . . . . . . . . . . . . . . . .243

12-11 SPI slave timing (CPHA = 0) . . . . . . . . . . . . . . . . . . . . . . . . .244

12-12 SPI slave timing (CPHA = 1) . . . . . . . . . . . . . . . . . . . . . . . . .244

12-13 Expansion bus timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246

13-1 84-pin PLCC/CERQUAD pinout. . . . . . . . . . . . . . . . . . . . . . .248

13-2 84-pin PLCC mechanical dimensions. . . . . . . . . . . . . . . . . . .249

13-3 84-pin CERQUAD mechanical dimensions . . . . . . . . . . . . . .250

Technical Data MC68HC11P2 — Rev 1.0

14 List of Figures MOTOROLA

Technical Data — MC68HC11P2

Table Title Page

2-1 Port signal functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

3-1 Example bootloader baud rates . . . . . . . . . . . . . . . . . . . . . . . .43

3-2 Register and control bit assignments . . . . . . . . . . . . . . . . . . . .47

3-3 Registers with limited write access. . . . . . . . . . . . . . . . . . . . . .51

3-4 Hardware mode select summary . . . . . . . . . . . . . . . . . . . . . . .53

3-5 RAM and register remapping . . . . . . . . . . . . . . . . . . . . . . . . . .56

3-6 EEPROM remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

3-7 EEPROM block protect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

3-8 Erase mode selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

4-1 Port configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

5-1 Example SCI baud rate control values . . . . . . . . . . . . . . . . . . .95

7-1 SPI clock rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 33

8-1 Timer resolution and capacity. . . . . . . . . . . . . . . . . . . . . . . . .139

8-2 RTI periodic rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

8-3 Pulse accumulator timing . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

8-4 Clock A and clock B prescalers . . . . . . . . . . . . . . . . . . . . . . .167

9-1 A/D converter channel assignments. . . . . . . . . . . . . . . . . . . .180

10-1 COP timer rate select. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

10-2 Reset cause, reset vector and operating mode . . . . . . . . . . .192

10-3 Highest priority interrupt selection . . . . . . . . . . . . . . . . . . . . .198

10-4 Interrupt and reset vector assignments . . . . . . . . . . . . . . . . .199

10-5 Stacking order on entry to interrupts. . . . . . . . . . . . . . . . . . . .201

11-1 Reset vector comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

11-2 Instruction set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

14-1 Ordering information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

15-1 M68HC11 development tools . . . . . . . . . . . . . . . . . . . . . . . . .253

List of Tables

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA List of Tables 15

List of Tables

Technical Data MC68HC11P2 — Rev 1.0

16 List of Tables MOTOROLA

Technical Data — MC68HC11P2

1.1 Contents

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

1.3 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

1.2 Introduction

The MC68HC11P2 8-bit microcomputer is a member of the M68HC11

family of HCMOS microco mput ers. In additi on to 32kbytes of ROM, the

MC68HC11P2 cont ains 1kbyte of RAM and 640 bytes of EEPROM. With

its advanced timer and communication features (including MI BUS

the MC68HC11P2 is especially suitable for mobile communications and

automotive applications.

Section 1. General Description

(1)

)

The MC68HC711P2 is an EPROM version of the MC68HC11P2, with

the User ROM replaced by a similar amount of EPROM. All references

to the MC68HC11P2 apply equally to the MC68HC711P2, unless

otherwise noted. References specific to the MC68HC711P2 are

italicised in the text.

1. The Motorola interconnect bus (MI BUS) is a serial communications protocol which supports

distributed real-tim e control effi ciently and with a high degr ee of noise immunity. I t allows data

to be transferred between the MCU and the slave de vice using only one wire, making this ty pe

of communication suitable for medium speed networks requiring very low cost multiplex wiring.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA General Description 17

General Description

1.3 Features

• Low power, high performanc e M68HC11 CPU core, with 4MHz

bus capability

• Power saving PLL clock circuit, with automatic disable during

WAIT mode

• 32kbytes of User ROM (MC68HC11P2); 32kbytes User EPROM

(MC68HC711P2)

• 1kbyte of RAM

• 640 bytes of byte-erasable User EEPROM, with on-chip charge

pump

• Up to 50 general purpose I/O lines, plus up to 12 input-only lines

• Non-multiplexed addr ess and data buses, permitting dir ect access

to the full 64k address map

• 16-bit timer with 3/4 input captures and 4/5 output compares;

pulse accumulator and COP watchdog timer

• Three 8- or 9-bit SCI subsystems, two with MI BUS† capability

• SPI subsystem, with software selectable MSB/LSB first option

• 8-channel, 8-bit analog-to-digital (A/D) converter

• Four 8-bit PWM timer channels (may be concatenated to form

one, or two, 16-bit channels)

• Available in 84-pin PLCC or 84-pin CERQUAD packages

Technical Data MC68HC11P2 — Rev 1.0

18 General Description MOTOROLA

General Description

Features

VPPE/XIRQ

IRQ

RESET

LIR/MODA

VSTBY/MODB

XTAL

EXTAL

XFC

VDDSYN

VDD

VSS

ROM or EPROM

Pulse accumula to r

Timer

Periodic inte rr u pt

COP watchdog

OC1/PAI

OC1/OC2

OC1/OC3

OC1/OC4

IC4/OC1/OC5

IC1

IC2

IC3

PA7

PA6

PA5

PA4

PA3

Port APort D

PA2

PA1

PA0

32768 x 8

(including 64 bytes for vectors)

SPI

SCI1+

640 bytes EEPROM

8-channel

A/D

converter

1024 bytes RAM

Interrupts

SS

SCK

MOSI

MISO

TXD1

RXD1

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

R/W

&

mode

select

E

Oscillator

PLL

5

5

M68HC11

CPU

SCI3+ (with MI BUS)

SCI2+ (with MI BUS)

PWM

TXD3

RXD3

TXD2

RXD2

PW4

PW3

PW2

PW1

PD5

PD4

PD3

PD2

PD1

PD0

VRH

VRL

PE7

PE6

PE5

PE4

PE3

Port E

PE2

PE1

PE0

PG7

PG6

PG5

PG4

PG3

Port G

PG2

PG1

PG0

PH7

PH6

PH5

PH4

PH3

Port H

PH2

PH1

PH0

Non-multiplexed address and data buses

A15

A14

A13

A12

A11

A10A9A8

A7A6A5A4A3A2A1A0D7D6D5D4D3D2D1

D0

Port B Port F Port C

PF6

PF5

PF4

PF3

PF2

PF1

PF0

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

PF7

PC0

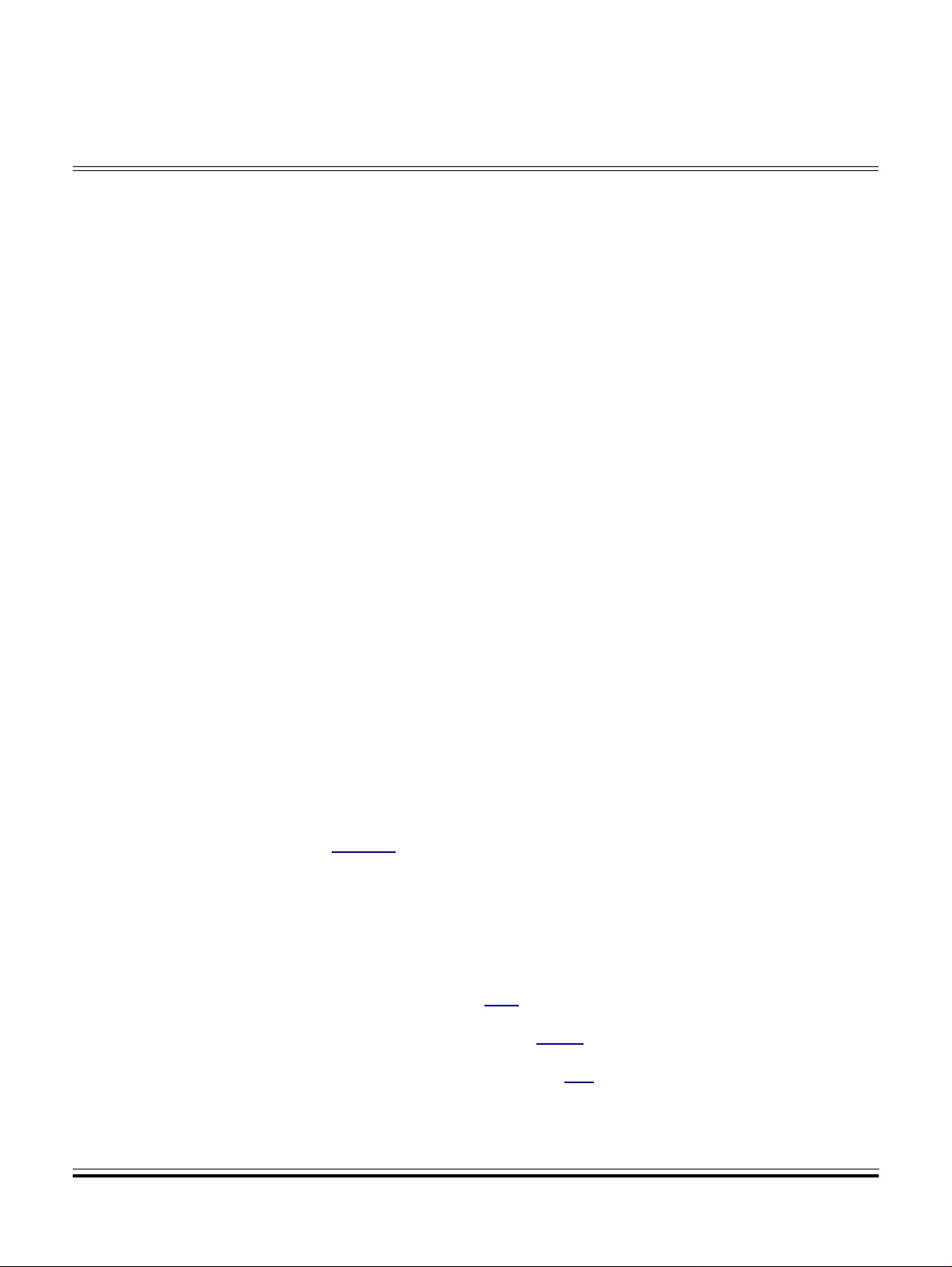

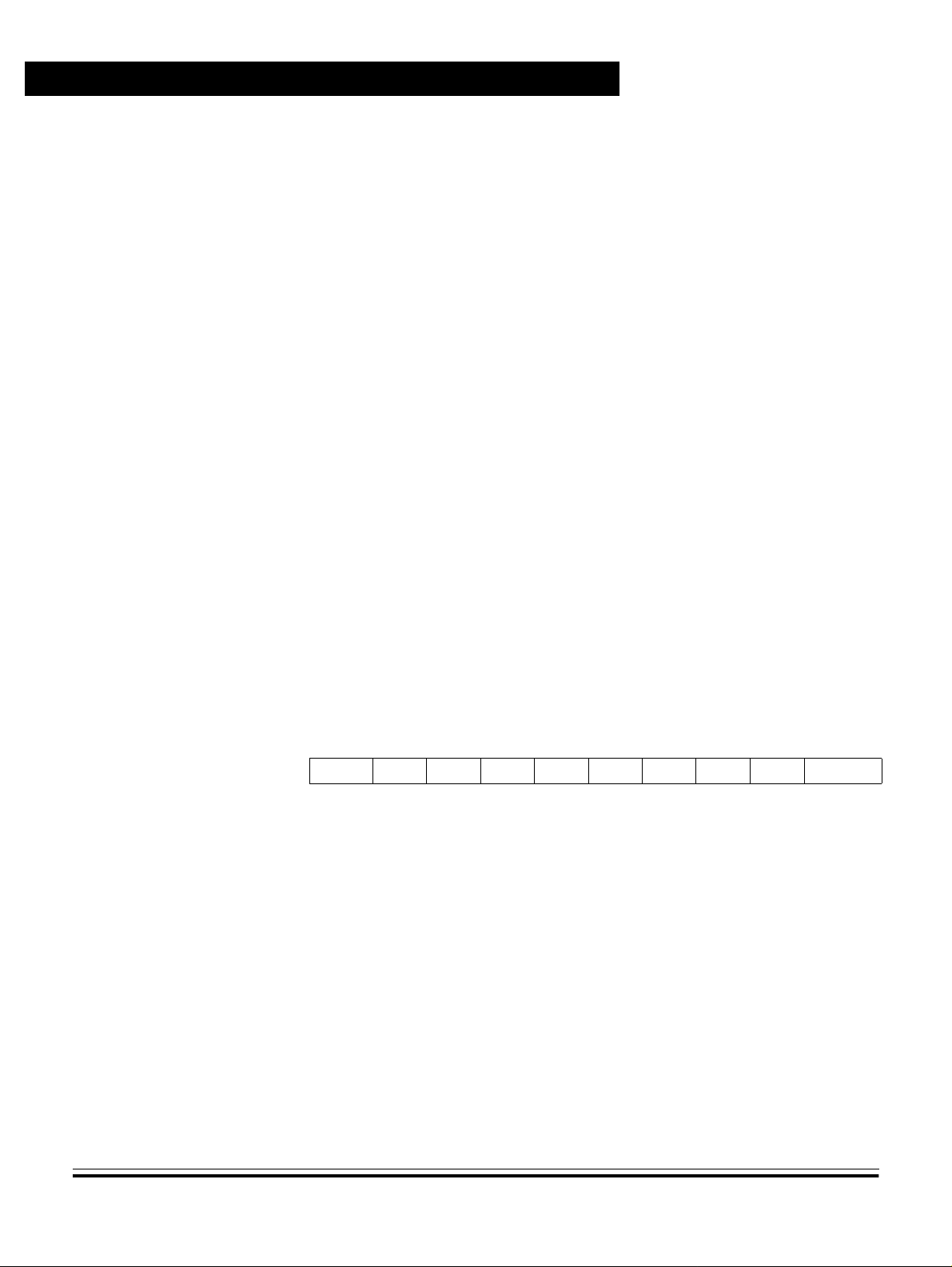

Figure 1-1. MC68HC11P2/MC68HC711P2 block diagram

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA General Description 19

General Description

Technical Data MC68HC11P2 — Rev 1.0

20 General Description MOTOROLA

Technical Data — MC68HC11P2

2.1 Contents

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.3 VDD and VSS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.4 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.5 Crystal driver and external clock input (XTAL, EXTAL) . . .24

2.6 E clock output (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.7 Phase-locked loop (XFC, VDDSYN) . . . . . . . . . . . . . . . . . . .26

2.8 Interrupt request (IRQ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2.9 Nonmaskable interrupt (XIRQ/VPPE) . . . . . . . . . . . . . . . . . .32

Section 2. Pin Descriptions

2.2 Introduction

2.10 MODA and MODB (MODA/LIR and MODB/VSTBY) . . . . . . .33

2.11 VRH and VRL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.12 PG7/R/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

2.13 Port signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

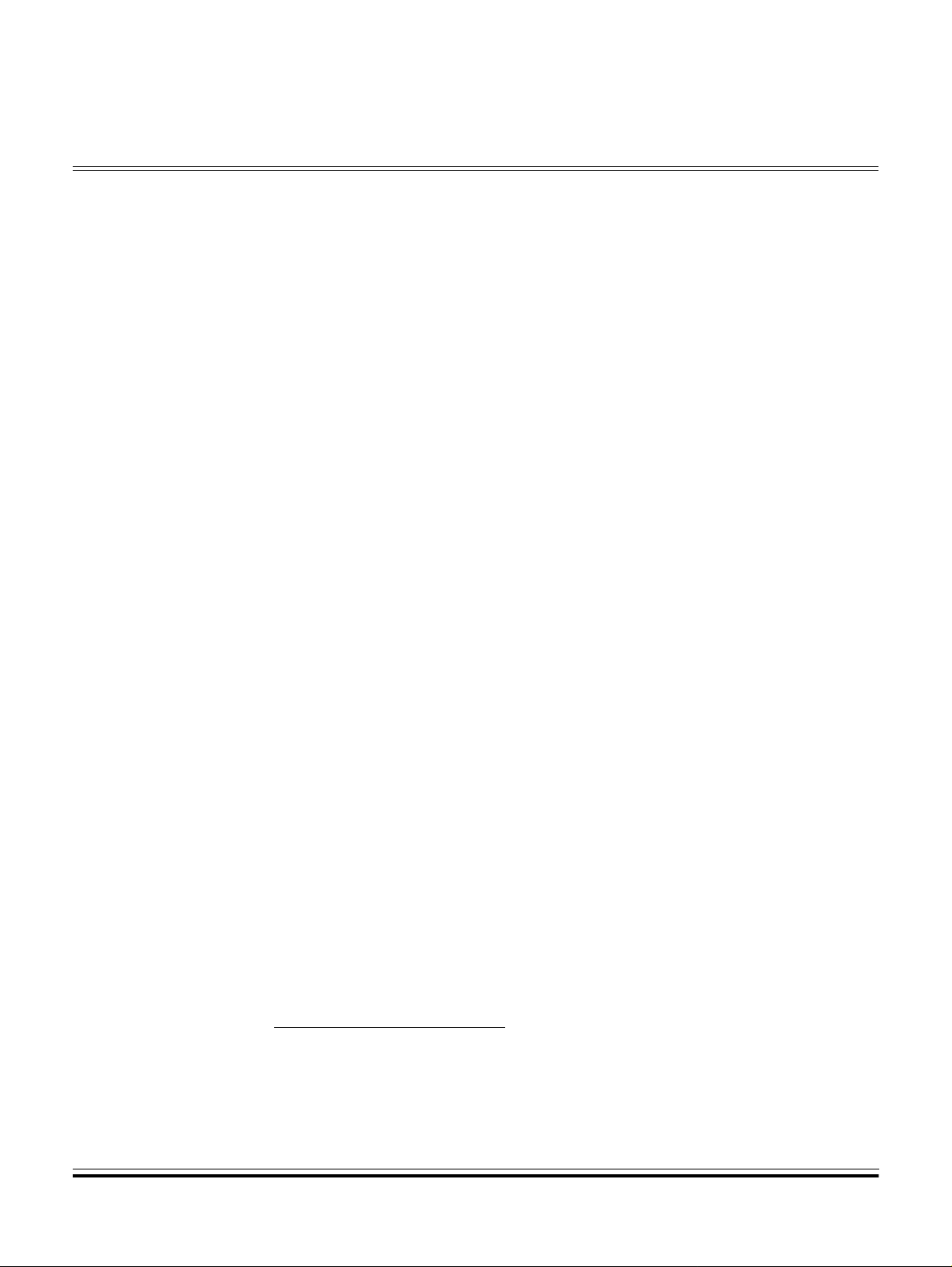

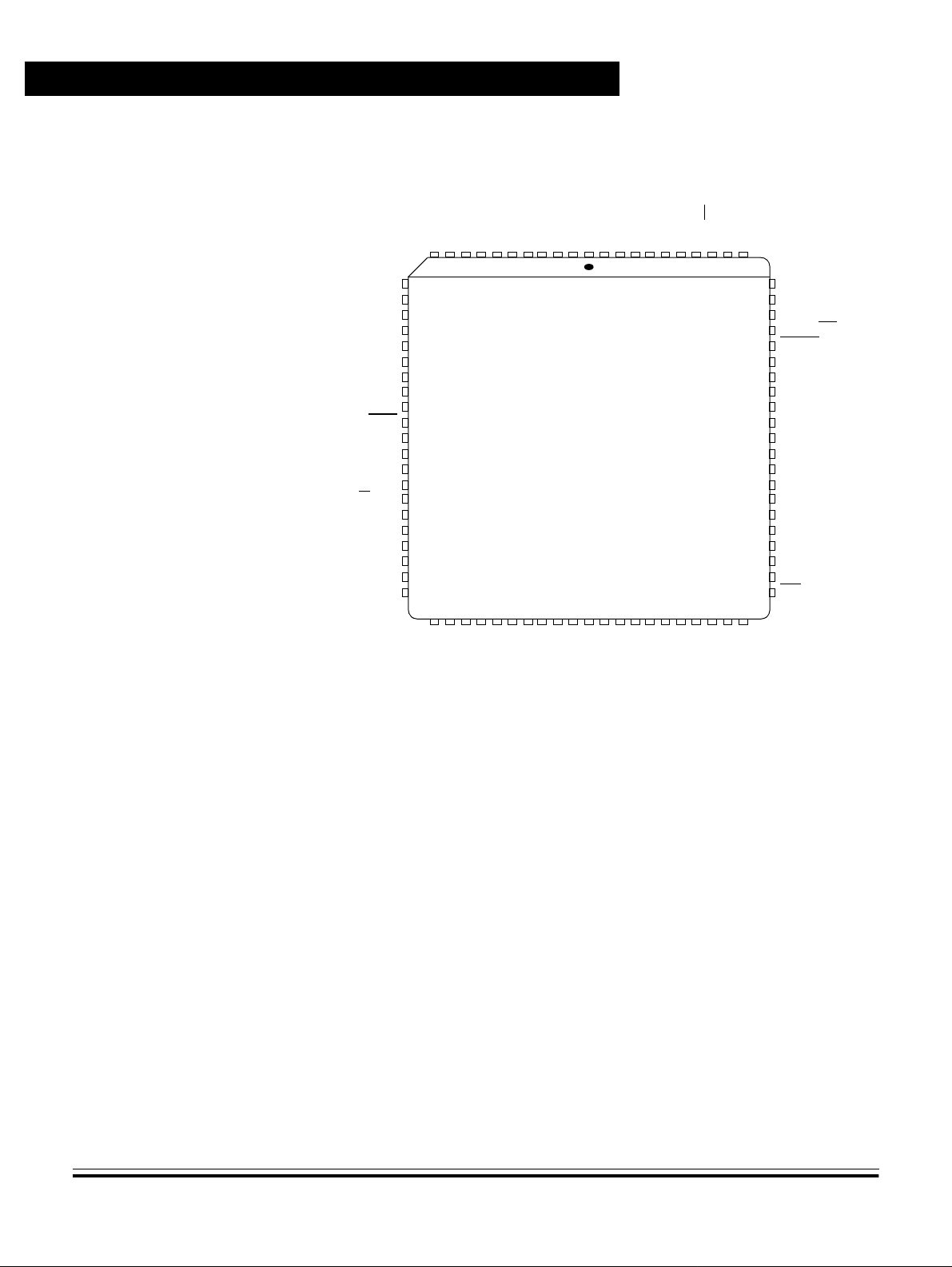

The MC68HC11P2 is available in an 84-pin plastic-leaded chip carrier

(PLCC); the MC68HC711P2 is also available in an 84-pin windowed

cerquad package, to all ow full use of the EPROM. Most pins on this MCU

serve two or more functions, as described in the following paragraphs.

Refer to Figure 2-1 which shows the pin assignments for both 84-pin

packages.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 21

Pin Descriptions

PW1/PH0

PW2/PH1

PW3/PH2

PW4/PH3

RXD2/PH4

TXD2/PH5

RXD3/PH6

TXD3/PH7

MODB/VSTBY

R/W

XIRQ

VDD

VDDL

VSSX

VSS

/PG7

PG6

PG5

PG4

PG3

PG2

PG1

PB0/A8

PB1/A9

PB2/A10

PB3/A11

PB4/A12

PB5/A13

PB6/A14

PB7/A15

VSS

VDD

PA0/IC3

PA1/IC2

PA2/IC1

PA3/OC1/OC5/IC4

PA4/OC1/OC4

PA5/OC1/OC3

PA6/OC1/OC2

65432

987

11

10

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

333435363738394041424344454647484950515253

8483828180

7978777675

PA7/OC1/PAI

PD5/SS

PD4/SCK

PD3/MOSI

74

PD2/MISO

73

PD1/TXD1

72

PD0/RXD1

71

MODA/LIR

RESET

70

XFC

69

VDDSYN

68

EXTAL

67

XTAL

66

E

65

VDDR

64

VSSX

63

PC7/D7

62

PC6/D6

61

PC5/D5

60

PC4/D4

59

PC3/D3

58

PC2/D2

57

PC1/D1

56

PC0/D0

55

IRQ

54

2.3 VDD and VSS

PG0

VDD AD

AD7/PE7

AD6/PE6

AD5/PE5

AD4/PE4

AD3/PE3

VRL

VRH

A7/PF7

A6/PF6

A5/PF5

A4/PF4

A3/PF3

A2/PF2

A1/PF1

AD2/PE2

AD1/PE1

VSS AD

AD0/PE0

A0/PF0

Figure 2-1. 84-pin PLCC/CERQUAD pinout

Power is supplied to the microcontroller via these pins. VDD is the

positive supply and VSS is grou nd. The MCU op erates from a single 5V

(nominal) power supply.

It is in the nature of CMOS designs that very fast signal transitions occur

on the MCU pins. These short rise and fall times place very high shortduration current demands on the power supply. To prevent noise

problems, special care must be taken to provide good power supply

bypassing at the MCU. Bypass capacitors should have good highfrequency characteristics and be as close to the MCU as possible.

Technical Data MC68HC11P2 — Rev 1.0

22 Pin Descriptions MOTOROLA

2.4 RESET

Pin Descriptions

RESET

Bypassing requirem e nts v ar y, depending on how heavily the MCU p ins

are loaded.

The MC68HC11P2 MCU has five VDD pins and five VSS pins. One pair

of these pins is reserved for supplying power to the analog-to-digital

converter (VDD AD, VSS AD); two pairs are used for the internal logic

(VDD, VSS); the remaining two pairs supply power for the port logic on

either half of the chip (VDDL, VSSX and VDDR, VSSX). This

arrangement minimizes the injection of noise into the digital circuitry on

the chip.

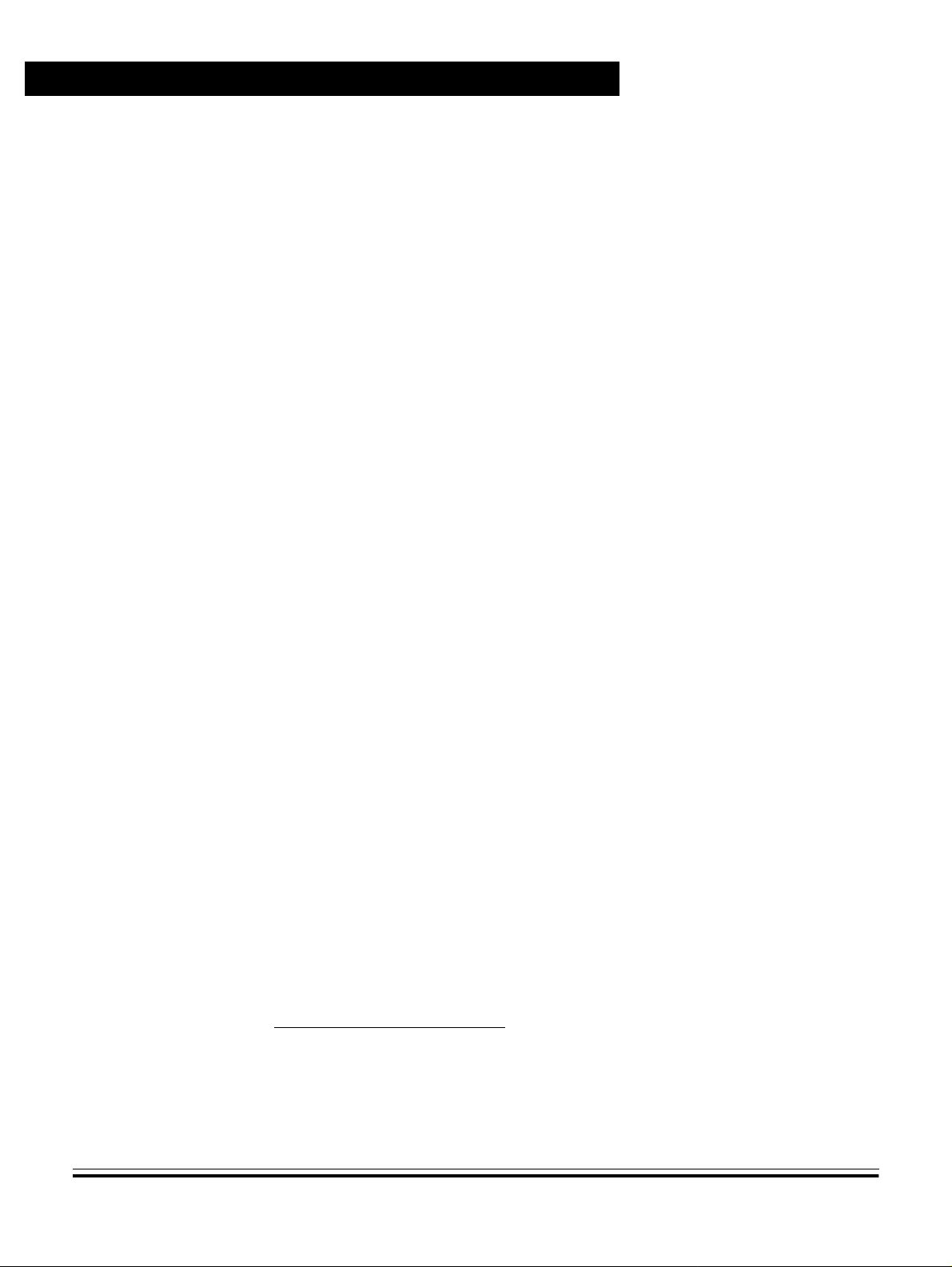

An active low bidirectional control signal, RESET, acts as an input to

initialize the MCU to a known start- up state. It also acts as an open-drain

output to indicate that an internal failure has been detected in either the

clock monitor or the COP watchdog circuit. The CPU distinguishes

between internal and external reset conditions by sensing whether the

reset pin rises to a logic one in less than six E clock cycles after a reset

has occurred. It is therefore not advisable to connect an external

resistor-capacitor (RC) power-up delay circuit to the reset pin of

M68HC11 devices because the circuit charge time constant can cause

the device to misinterpret the type of reset that occurred. Refer to

Resets and Interrupts for further information.

Figure 2-2 illustrates a typical reset circuit that includes an external

switch together with a low voltage inhibit circuit, to prevent power

transitions, or RAM or EEPROM corruption.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 23

Pin Descriptions

V

V

DD

DD

Manual

reset

4.7 k¾

2

IN

1

GND

IN

GND

RESET

3

2

RESET

3

1

MC34064

V

DD

4.7 k¾

1µF

MC34164

4.7 k¾

To M68HC11

RESET

Figure 2-2. External reset circuitry

2.5 Crystal driver and external clock input (XTAL, EXTAL)

These two pins provide the interface for either a cr ystal or a CMOS

compatible clock to control the internal clock generator circuitry. The

frequency applied to these pins must be four times higher than the

desired E clock rate (unless the PLL circuit is used to provide the E

clock).

The XTAL pin is normally left unconnected when an external CMOS

compatible clock inp ut is connected to the EXTAL pin. However , a 10 k¾

to 100 k¾ load resistor connected from XTAL to ground can be used to

reduce RFI noise emission. The XTAL output is normally intended to

drive only a crys tal. The XTAL output can be buffered with a highimpedance buffe r, o r i t can be u sed to dri ve the EX TAL inp ut of a nothe r

M68HC11 family device.

Technical Data MC68HC11P2 — Rev 1.0

24 Pin Descriptions MOTOROLA

Pin Descriptions

Crystal driver and external clock input (XTAL, EXTAL)

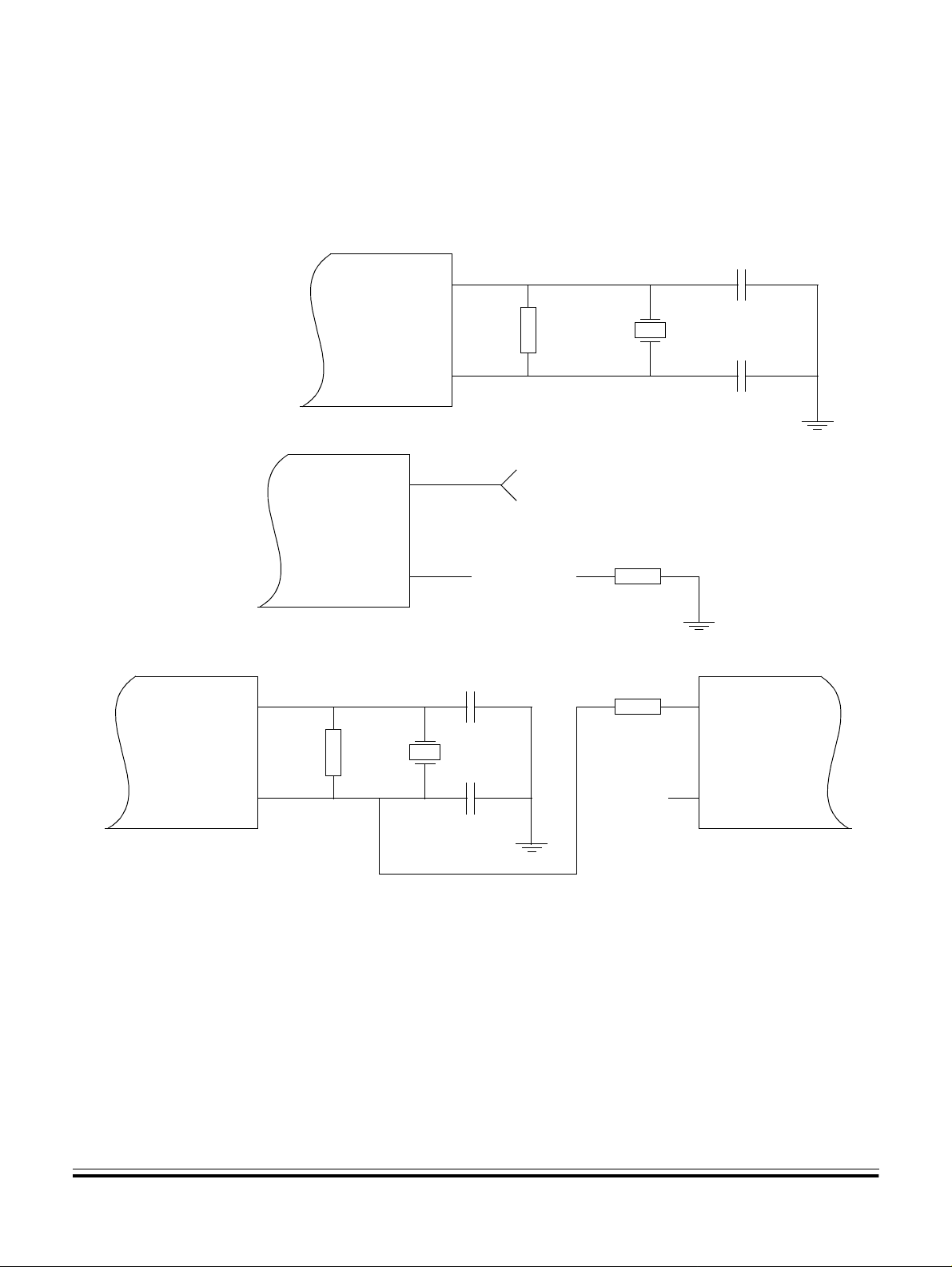

In all cases, use caution when designing circuitry associated with the

oscillator pins. Load cap acitances shown in the oscillator cir cuits include

all stray layout capacitances. See Figure 2-3.

(a) Common crystal

connections

(b) External oscilla tor

connections

EXTAL

M68HC11

M68HC11

EXTAL

XTAL

EXTAL

XTAL

10 M¾

External oscillator

NC or

10–100k¾ load

25 pF

25 pF

4•E

crystal

25 pF

220¾

EXTAL

M68HC11

XTAL

(c) One crystal driving two MCUs

10 M¾

4•E

crystal

25 pF

M68HC11

NC or

10–100k¾

load

Note: capacitor values include all stray capacitance.

XTAL

Figure 2-3. Oscillator connections

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 25

Pin Descriptions

2.6 E clock output (E)

E is the output connect ion for the internally generated E clo ck. The signal

from E is used as a timing reference. The frequency of the E clock output

is one quarter that of the input frequency at the XTAL and EXTAL pins

(except when the PLL is used as the clock source). When E clock outp ut

is low, an internal process is taking place; when it is high, data is being

accessed. All clocks, including the E clock, are halted when the MCU is

in STOP mode. The E clock output can be turned off in single chip

modes to reduce the effects of RFI.

2.7 Phase-locked loop (XFC, VDDSYN)

The XFC and VDDSYN pins are the inputs for the on-chip PLL (phaselocked loop) circuitry. On rese t all the device clocks are de rived from the

EXTAL input. The EXTAL clock is used as a reference for the PLL circuit,

which generates a cl ock that is a multiple of the EXTAL frequency. Once

the PLL has stabilized, alternate clocks may be selected.

VDDSYN is the powe r supply pin for the PL L. Connecting it high en ables

the internal low frequency oscillator circuitry designed for the PLL. The

PLL has been designed particularly for use with 614.4 and 640kHz

crystals, though other values may be used. The maximum

recommended crystal freq uency for PLL opera tion is 2MHz. Above this

frequency VDDSYN sh ould be g roun ded to disa ble the PLL a nd en able

the high frequency oscillator circuit; in this state EXTAL is designed for

16MHz operation and XFC may be left unconnected.

The PLL consists of a variable bandwidth loop filter, a voltage controlled

oscillator (VCO), a feedback frequency divider and a digital phase

detector. VDDSYN is the supply voltage for th e PLL and must be suitab ly

bypassed. The extern al capacito r on XFC sh ould be located a s close to

the chip as possible to minimi ze nois e. A typical val ue for thi s capacito r

is 0.047µF, for a crystal frequency of 614.4kHz.

1. In general, a larger capacitor will improve the PLL’s frequency stability, at the expense of increasing the time required for it to settle (t

cation, or one in which the slew rate is not critical, a capacitor value of 0.1µF is usually

adequate. For a crystal frequency of 614.4kHz and a slew time of 1–2ms (from 614kHz in

WAIT mode to 16MHz in RUN mode), a capacitor of 0.047µF has been found satisfactory.

Technical Data MC68HC11P2 — Rev 1.0

26 Pin Descriptions MOTOROLA

) at the desired frequency. For a 32kHz appli-

PLLS

(1)

Pin Descriptions

Phase-locked loop (XFC, VDDSYN)

The PLL filter has two band widths that are au tomatically selected by th e

PLL, if the AUTO bit in PLL CR is set. Whenever the PLL is first enable d,

the wide bandwidth mode is used. This enables the PLL frequency to

ramp up quickly. When the output frequency is near the desired value,

the filter is switched to the narrow bandwidth mode, to make the final

frequency more stable. Manual control is possible, by clearing AUTO in

PLLCR, and setting the appropriate value for BWC.

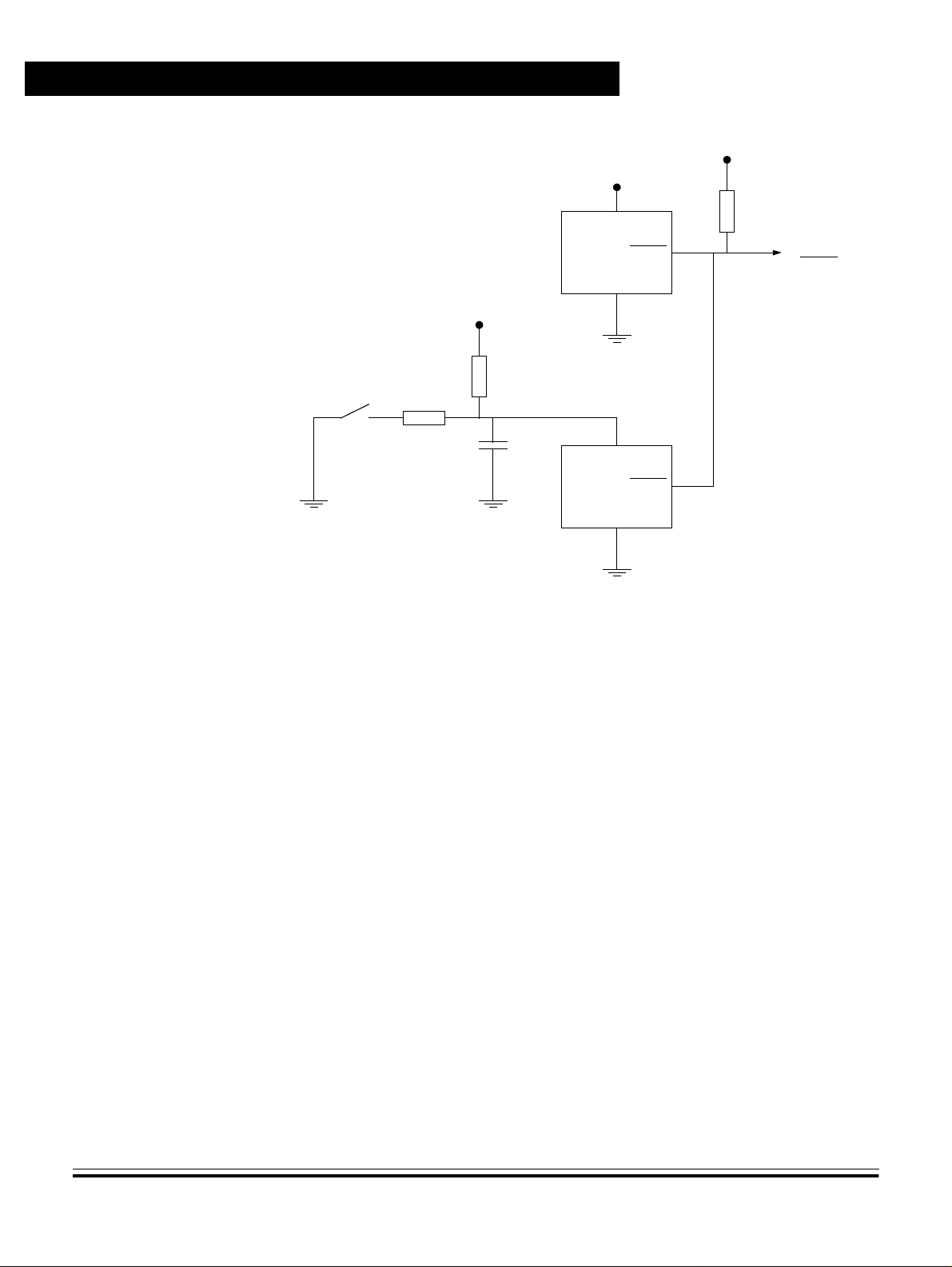

A block diagram of the PLL circuitry is given in Figure 2-4.

V

DDSYN

EXTAL

t

REF

EXTAL

Low frequency

crystal oscillator

Phase

detect

PCOMP

t

FB

XFC

Loop filter VCO

Frequency divider

SYNR

VCOOUT

Figure 2-4. PLL circuit

4XCLK

Bus clock

select

To clock

generation

circuitry

BCS

ST4XCK

Module clock

select

For SCI

and timer

EXTAL

MCS

2.7.1 Synchronization of PLL with subsystems

The timer and SCI subsystems operate off the EXTAL clock, but are

accessed by the CPU relative to the internal PH2 signal. Although the

EXTAL clock is used as the referenc e for the PLL, the PH2 clock and the

module clocks for the timer and the SCI are not synchronized. In order

to ensure synchronized data , special circuitry has been incorporated into

both subsystems.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 27

Pin Descriptions

2.7.2 Changing the PLL frequency

To change the PLL frequency it is necessary to perform the following

sequence of events, in order to prevent possible bursts of high frequency

operation during the reconfiguration of the PLL:

1. Switch to the low frequency bus rate (BCS = 0)

2. Disable the PLL (PLLON = 0)

3. Change the value in SYNR

4. Enable the PLL (PLLON = 1)

5. Wait a time t

6. Switch to the high frequency bus rate (BCS = 1)

2.7.3 PLL registers

Two registers are used to control the operation of the MC68HC11P2

phase-locked loop circuitry. These are the PLL control register and the

synthesizer program register, each of which is described below.

2.7.3.1 PLLCR — PLL control register

Address bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

PLL control (PLLCR) $002E PLLON BCS AUTO BWC VCOT MCS LCK WEN 1010 1000

This read/write register contains two bits that are used to enable and

disable the synthesizer and to switch from slow (EXTAL) to one of the

fast speeds. Two further bi ts are used to control the filt er bandwidth. The

SCI and timer clock source and the slow clock for WAIT mode are also

controlled by this register.

for the PLL frequency to stabilize

PLLS

State

on reset

PLLON — PLL on

1 = Switch PLL on.

0 = Switch PLL off.

Technical Data MC68HC11P2 — Rev 1.0

28 Pin Descriptions MOTOROLA

Pin Descriptions

Phase-locked loop (XFC, VDDSYN)

This bit activates the synthesizer circuit without connecting it to the

control circuit. This allows the circuit to stabilize before it drives the

CPU clocks. PLLON is set by reset, to allow the control loop to

stabilize during power up.

PLLON cannot be cleared whilst using VCOOUT to drive the internal

processor clock, i.e. when BCS is set.

BCS — Bus clock select

1 = VCOOUT output drives the clock circuit (4XCLK).

0 = EXTAL drives t he clock circuit (4XCLK).

This bit determine s which signal drives the clock cir cuit generating the

bus clocks. Once BCS has been altered it can take up to [1.5 EX TAL

+ 1.5 VCOOUT] cycles for the change in the clock to occur. Reset

clears this bit.

NOTE: PLLON and BCS have built-in safeguards so that VCOOUT cannot be

selected as the clock source (BCS = 1) if the PLL is off (PLLON = 0).

Similarly, the PLL ca nnot be tu rned off ( PLLON = 0) if it is on and in us e

(BCS = 1). Turning th e PLL on and selecting VCOOUT as the clock

source therefore requires two independent writes to PLLCR.

AUTO — Automatic bandwidth control

1 = Automatic bandwidth control selected.

0 = Manual bandwidth control selected.

AUTO selects between automatic bandwidth control circuits in the

phase detect block and manual bandwidth control. Reset sets this bit.

BWC — Bandwidth control

1 = High bandwidth control selected.

0 = Low bandwidth control selected.

Bandwidth control is unde r manu al cont rol onl y when AU TO is clear.

(When AUTO is set, BWC acts as a read-only status bit to indicate

which mode has been selected by the internal circuit.) A delay of t

is required between changes to BWC. The low bandwidth driver is

always enabled, so this bit determines whether the high bandwidth

driver is on or off. On PLL start-up in automatic mode (AUTO = 1), th e

high bandwidth driver is enabled (BWC = 1) by internal circuitry until

PLLS

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 29

Pin Descriptions

the PLL is near the specif ied frequ ency. The high bandwidth driver is

then disabled and BWC is cleared by internal circuitry. Reset clears

this bit.

Auto BWC

00 Off

01 On

1XAuto

High

bandwidth

VCOT — VCO test (Test mode only)

1 = Loop filter operates as specified by AUTO and BWC.

0 = Low bandwidth mode of the PLL filter is disabled .

This bit is used to isolate the loop filter from the VCO for testing

purposes. VCOT is always set when AUTO = 1 when running in

automatic mode. This bit is writable only in test mode. Reset sets this

bit.

MCS — Module clock select

1 = 4XCLK is the source for the SCI and timer divider chain.

0 = EXTAL is the source for the SCI and timer divider chain.

Reset clears this bit.

LCK — Synthesizer lock detect

1 = The PLL has stabilized.

0 = The PLL is not stable.

This bit is used as an indicator for software that it is all right to set

BCS.

WEN — WAIT enable

1 = Low-power WAIT mode selected (PLL set to ‘idle’ in WAIT

mode).

0 = Do not alter the 4XCLK during WAIT mode.

This bit determines whether the 4XCLK is disconnected from

VCOOUT during WAIT and connected to EXTAL. Reset clears this

bit.

When set, the CPU will respond to a WAIT instruction by first stacking

the relevant registers, then by clearing BCS and setting the PLL to

‘idle’, with modulus = 1.

Technical Data MC68HC11P2 — Rev 1.0

30 Pin Descriptions MOTOROLA

Any interrupt, any reset, or the assertion of RAF in any of the SCIs will

allow the PLL to resume operating at the frequency specified in the

SYNR. The user must set BCS after the PLL has had time to adjust

(t

). If, for a specific SCI, the RE bit is clear, then RAF cannot

PLLS

become set, hence the PLL will not resume normal operation.

2.7.3.2 SYNR — Synthesizer program register

Pin Descriptions

Phase-locked loop (XFC, VDDSYN)

Addressbit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0

Synthesizer program (SYNR) $002F SYNX1SYNX0SYNY5SYNY4SYNY3SYNY2SYNY1SYNY00000 1011

State

on reset

The PLL frequency synthesizer multiplies the frequency of the crystal

oscillator. The mult ipl ication factor is softw are pro gramm able vi a a loop

divider, which c onsists of a six-bit modulo N counter, with a further two

bit scaling factor.

The multiplicatio n factor is given by 2(Y + 1)2X, where 0 ð X ð 3 and 0 ð

Y ð 63.

NOTE: Exceeding recommended operating frequencies can result in

indeterminate MCU operation.

SYNX[1:0]

These bits program the binary taps (divide by 1, 2, 4 and 8). Reset

clears these bits.

SYNY[5:0]

These bits program the six-bit modulo N (1 to 64) counter. Reset sets

these bits to %001011.

NOTE: The resolut ion of the multiplic ation facto rs decreases b y a fa ctor of two,

as X increases:

X Y Possible multipliers

00 – 63 2, 4, 6, 8, …, 128

10 – 63 4, 8, 12, 16, …, 256

20 – 63 8, 16, 24, 32, …, 512

30 – 63 16, 32, 48, 64, …, 1024

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 31

Pin Descriptions

2.8 Interrupt request (IRQ)

The IRQ input provides a means of applying asynchronous interrupt

requests to the MCU. Either falling edge sensitive triggering or level

sensitive triggering is program selectable (OPTION register). IRQ is

always configured to level sensitive triggering at reset.

NOTE: Connect an external pull-up resistor, typically 4.7k¾, to V

is used in a level sensitive wired-OR configuration. See also

Nonmaskable interrupt (XIRQ/VPPE).

2.9 Nonmaskable interrupt (XIRQ/VPPE)

The XIRQ input provides a means of requesting a non-maskable

interrupt after reset initialization. During reset, the X bit in the condition

code register (CCR) is set and any interrupt is masked until MCU

software enables it. B ecause the X IRQ input is level-sensitive, it can be

connected to a multiple-source wired- OR network with an external pullup resistor to VDD. XIRQ is often used as a power loss detect interrupt.

Whenever XIRQ or IRQ is used with multip le interrupt sources (IRQ

must be configured for level sensitive operation if there is more than one

source of IRQ interrupt), each source must drive the interrupt input with

an open-drain type of driver t o avoid con tention betw een outputs. There

should be a single pull-up resistor near the MCU interrupt input pin

(typical ly 4. 7 k¾). There must also be an interlock mechanism at each

interrupt source so that the source holds the interrupt line low until the

MCU recognizes and ackn owledges the interrupt req uest. If one or more

interrupt source is still pending after the MCU services a re quest, the

interrupt line will still be held low and the MCU will be interrupted again

as soon as the interrupt mask bit in the MCU is cleared (normally upon

return from an interrupt). Refer to Resets and Interrupts.

when IRQ

DD

The VPPE pin is used to input the external EPROM programming

voltage, which must be present during EPROM programming.

Technical Data MC68HC11P2 — Rev 1.0

32 Pin Descriptions MOTOROLA

MODA and MODB (MODA/LIR and MODB/VSTBY)

2.10 MODA and MODB (MODA/LIR and MODB/VSTBY)

During reset, MODA and MODB sele ct one of the fo ur operatin g modes.

Refer to Operating Modes and On-Chip Memory.

After the operating mode has been selected, the LIR pin provides an

open-drain output to indicate that executi on of an instruction has begun.

The LIR pin is normally configured for wired-OR operation (only pulls

low). In order to detect consecutive instructions in a high-speed

application, this signal can be made to drive high for a short time to

prevent false triggering. A series of E clock cycles occurs during

execution of each instruction. The LIR signal goes low during the first E

clock cycle of each instruction (opcod e fetch). This output is provided for

assistance in program debugging and its operation is controlled by the

LIRDV bit in the OPT2 register.

Pin Descriptions

The VSTBY pin is used to input RAM stand-by power. The MCU is

powered from the VDD pin unless the difference between the level of

VSTBY and VDD is greater than one MOS threshold (about 0.7 volts).

When these voltages differ by more than 0.7 volts, the internal 1024-byte

RAM and part of the reset logic are powered from VSTBY rather than

VDD. This allows RAM contents to be retained without VDD power

applied to the MCU. Reset must be driven low before VDD is removed

and must remain low until VDD has been restored to a valid level.

V

DD

4.8 V NiCd

(+)

V

DD

MAX 690

V

BATT

V

OUT

4.7k¾

To MODB/VSTBY

pin of M68HC1 1

Figure 2-5. RAM stand-by connections

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 33

Pin Descriptions

2.11 VRH and VRL

2.12 PG7/R/W

These pins provide the reference voltages for the analog-to-digital

converter.

This pin provides two separate functions, depending on the operating

mode. In single chip and bootstr ap mo de s, PG7/R /W acts as

input/output port G bit 7. Refer to Parallel Input/Output for further

information.

In expanded and test m odes, PG7/R/W performs the read/writ e function.

PG7/R/W signals the direction of transfers on the external data bus. A

high on this pin indicates that a read cycle is in progress.

2.13 Port signals

NOTE: When using the information about port functions, do not confuse pin

In the 84-pin PLCC package , 62 pins are arranged into seven 8-bit ports:

A, B, C, E, F, G, and H, and on e six- bit port ( D). The lines of ports A, B,

C, D, F, G, and H are fully bidirectional; E is input only. Each of the

bidirectional ports serves a purpose other than I/O, depending on the

operating mode or p eri ph er al fun cti on se le cte d. N ote t hat ports B, C, F,

and one bit of port G are available for I/O functions only in single chip

and bootstrap modes. Refer to Table 2-1 for details of the port signals’

functions in different operating modes.

function with the electrical state of the pin at reset. All general-purpose

I/O pins configure d as inputs at reset are in a high-impedance state. P ort

data registers reflect the functional state of the port at reset. The pin

function is mode dependent.

Technical Data MC68HC11P2 — Rev 1.0

34 Pin Descriptions MOTOROLA

Table 2-1. Port signal functions

Pin Descriptions

Port signals

Single chip

Port/bit

PA0 PA0/IC3

PA1 PA1/IC2

PA2 PA2/IC1

PA3 PA3/OC5/IC4 and/or OC1

PA4 PA4/OC4 and/or OC1

PA5 PA5/OC3 and/or OC1

PA6 PA6/OC2 and/or OC1

PA7 PA7/PAI and/or OC1

PB[7:0] PB[7:0] A[15:8]

PC[7:0] PC[7:0] D[7:0]

PD0 PD0/RXD1

PD1 PD1/TXD1

PD2 PD2/MISO

PD3 PD3/MOSI

PD4 PD4/SCK

PD5 PD5/SS

PE[7:0] Input only or analog inputs

PF[7:0] PF[7:0] A[7:0]

PG[6:0] PG[6:0]

PG7 PG7/R/W

PH0 PH0/PW1

PH1 PH1/PW2

PH2 PH2/PW3

PH3 PH3/PW4

PH4 PH4/RXD2

PH5 PH5/TXD2

PH6 PH6/RXD3

PH7 PH7/TXD3

and

bootstrap mode

Expanded multiplexed

and

special test mode

2.13.1 Port A

Port A is an 8-bit general- purpose I/O port w ith a data regist er (PORTA)

and a data direction register (DDRA). Port A pins share functions with

the 16-bit timer system (see Timing System for further information).

PORTA can be read at any time: inputs return the pin level; outputs

return the pin driver input level. If written, PORTA stores the data in

internal latches. The pins are driven only if they are configured as

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 35

Pin Descriptions

2.13.2 Port B

outputs. Writes to PORTA do not change the pin state wh en the pins are

configured for timer output compares.

Out of reset, port A pins [7:0] are general-purpose high-impedance

inputs. When the function s associa ted wi th the se pin s are disab led, the

bits in DDRA govern the I/O state of the associated pin. For further

information, refer to Parallel Input/Output.

Port B is an 8-bit general- purpose I/O port w ith a data regist er (PORTB)

and a data direction re gister (DDRB). In single chip mode, por t B pins are

general-purpose I/O pins (PB[7:0]). In expanded mode, port B pins act

as the high-order address lines (A[15:8]) of the address bus.

PORTB can be read at any time: inputs return the pin level; outputs

return the pin dr iver inpu t level. If POR TB is writ ten, the data i s stored in

internal latches. The pins are driven only if they are configured as

outputs in single chip or b ootstrap mode. For further information, refer to

Parallel Input/Output.

2.13.3 Port C

Port B pins include on-chip pull-up devices which can be enabled or

disabled.

Port C is an 8 -bit general -purpose I/O port with a data regi ster (PORTC)

and a data direction register (DDRC). In single chip mode, port C pins

are general-purpose I/O pins (PC[7:0]). In the expanded mode, port C

pins are configured as data bus pins (D[7:0]).

PORTC can be read at any time: inputs return the pin level; outputs

return the pin driver i nput level . If PORTC is writt en, the d ata is store d in

internal latches. The pins are driven only if they are configured as

outputs in single chip or bootstrap mode. Port C pins are generalpurpose inputs out of reset in single chip and bootstrap modes. In

expanded and test modes, these pins are data bus lines out of reset.

Technical Data MC68HC11P2 — Rev 1.0

36 Pin Descriptions MOTOROLA

2.13.4 Port D

Pin Descriptions

Port signals

The CWOM control bit in the OPT2 register disables port C’s P-channel

output drivers. Be cau se the N-ch annel dr iver is no t affecte d by C WOM,

setting CWOM causes port C to become an open -drain- type output port

suitable for wired-OR oper ation. In wired -OR mode (PORTC bits at logic

level zero), the pins are actively dr i ven lo w by the N-chan ne l dr i ver .

When a port C bit is at logic level one, the associated pin is in a high

impedance state as neither the N-channel nor the P-channel devices are

active. It is customary to have an external pull-up resistor on lines that

are driven by open-drain devices. Port C can only be configured for

wired-OR operation when the MCU is in single chip mode. For further

information, refer to Parallel Input/Output.

Port D, a 6-bit g eneral-purpose I/O port, has a data register (PORTD)

and a data direction register (DDRD). The six p ort D lines (D[5:0]) can

be used for general-purpose I/O, for one of the serial communications

interfaces (SCI1, bits [0:1]) and for the serial peripheral interface (SPI,

bits [2:5]) subsystem.

2.13.5 Port E

PORTD can be read at any time: inputs return the pin level; outputs

return the pin driver i nput level . If PORTD is writt en, the d ata is store d in

internal latches and are driven only if port D is configured for generalpurpose output.

For further information, refer to Parallel Input/Output, Serial

Communications Interface (SCI) and Serial Peripheral Interface

(SPI).

Port E, PE/AD[7:0], is an input-only port that can also be used as the

analog inputs for the analog-to-digital converter.

For further information, refer to Parallel Input/Output and Analog-to-

Digital Converter.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 37

Pin Descriptions

2.13.6 Port F

Port F is an 8-bit general-purpose I/O port with a data register (P ORTF)

and a data direction register (DDRF). In single chip mode, port F pins are

general-purpose I/O pins (PF[7:0]). In expanded mode, port F pins act

as the low-order address lines (A[7:0]) of the address bus.

PORTF can be read at any time: inputs return the pin level; outputs

return the pin driver input level. If PORTF is written, the data is stored in

internal latches. The pins are driven only if they are configured as

outputs in single chip or bootstrap mode.

Port F pins include on-chip pull-up devices that can be enabled or

disabled.

For further information, refer to Parallel Input/Output.

2.13.7 Port G

2.13.8 Port H

In normal modes, Port G is a n 8-bit general-purpose I/O port with a data

register (PORTG) and a data direction register (DDRG). Port G bit 7 is

the R/W line in expanded mode; the remaining bits are always general

purpose I/O.

PORTG can be read at any time: inputs return the pin level; outputs

return the pin driver input level. If PORTG is written, the data is stored in

internal latches.The pins are driven only if they are configured as outputs

in single chip or bootstrap mode. For further information, refer to Parallel

Input/Output.

Port G pins include on-chip pull-up devices that can be enabled or

disabled.

Port H is an 8 -bit general -purpose I/O port with a data regi ster (PORTH)

and a data direction register (DDRH). Port H pins support either

input/output, SCI2 (bits [7:6]), SCI3 (bits [5:4]), or pulse-width

modulation channels (bits [3:0]). Both of these SCI subsystems also

have MI BUS capability.

Technical Data MC68HC11P2 — Rev 1.0

38 Pin Descriptions MOTOROLA

Pin Descriptions

Port signals

PORTH can be read at any time: inputs return the pin level; outputs

return the pin driver i nput level . If PORTH is writt en, the d ata is store d in

internal latches. The pins are driven only if they are configured as

outputs in single chip or bootstrap mode.

Port H pins includ e on-chip pull-up or pull-down de vices that can be

enabled or disabled via the Port pull-up assignment register (PPAR).

Port H [7:4] have pull-up resistors; p ort H [3 :0] h ave pull-do wn resistors.

For further information, refer to Parallel Input/Output, Serial

Communications Interface (SCI), Motorola Interconnect Bus

(MI BUS) and Timing System.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Pin Descriptions 39

Pin Descriptions

Technical Data MC68HC11P2 — Rev 1.0

40 Pin Descriptions MOTOROLA

Technical Data — MC68HC11P2

Section 3. Operating Modes and On-Chip Memory

3.1 Contents

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.3 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.4 On-chip memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

3.5 System initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.6 EPROM, EEPROM and CONFIG register . . . . . . . . . . . . . . .64

3.2 Introduction

This section contains information about the modes that define

MC68HC11P2 op erating conditions , and about the on-chi p memory that

allows the MCU to be configur ed for var i ou s appl ic ati o ns.

3.3 Operating modes

The values of the mode select inputs MODB and MODA during reset

determine the ope rating mode. Single chi p and expanded modes are the

normal modes. In single chip mode only on-board memory is available.

Expanded mode, however, allows access to external memory. Each of

these two normal modes is paired with a special mode. Bootstrap, a

variation of the single chip mode, is a special mode that executes a

bootloader program in an internal bootstrap ROM. Test is a special

mode that allows privileged access to internal resources.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Operating Modes and On-Chip Memory 41

Operating Modes and On-Chip Memory

3.3.1 Single chip operating mode

In single chip ope rating mode, the MC68HC11P2 microc ontroller has no

external address or data bus. Ports B, C, F, and the R/W pin are

available for general-purpose parallel I/O.

3.3.2 Expanded operating mode

In expanded operating mode, the MCU can access a 64kbyte physical

address space. The address space includes the same on-chip me m or y

addresses used for single chip mode, in add ition to external memo ry and

peripheral devices.

The expansion bus is made up of ports B, C, and F, and the R/W signal.

In expanded mode, hig h order address bits are o utput on the port B pins,

low order address bits on t he port F pins, and the data bus on port C. Th e

R/W/PG7 pin signals the direction of data transfer on the port C bus.

3.3.3 Special test mode

Special test, a variatio n of the expa nd ed mode, i s primar ily us ed duri ng

Motorola’s internal production testing; however, it is accessible for

programming the CO NFIG register, programming calibration data into

EEPROM, and supporting emulation and debugging during

development.

Technical Data MC68HC11P2 — Rev 1.0

42 Operating Modes and On-Chip Memory MOTOROLA

3.3.4 Special bootstrap mode

When the MCU is reset in special bootstrap mode, a small on-chip ROM

is enabled at address $BE 40–$BFFF. The ROM conta ins a reset vector

and a bootloader program. The MCU fetches the reset vector, then

executes the bootloader.

For normal use of the bootloader program, send a synchronization byte

$FF to the SCI receiver at either E clock ÷25 6, or E clo ck ÷1664 (7812

or 1200 baud respectively, for an E clock of 2MHz). Then download up

to 1024 bytes of progr am data (which is p ut into RAM star ting at $0080).

These characters are echoed through the transmitter. The bootloader

program ends the download after a timeout of four character times or

1024 bytes. When loading is complete, the program jumps to location

$0080 and begins exec uting the code. Use of an external pull-up resistor

is required when using the SCI transmitter pin (TXD) because port D pins

are configured for wired-OR op eration by the bootloader. In bootstrap

mode, the interrupt vectors point to RAM. This allows the use of

interrupts through a jump table.

Operating Modes and On-Chip Memory

Operating modes

Further baud rate op tions are available on the MC68HC11P2 by using a

different value for the synchro nization byte, as shown in Table 3-1. Refer

also to Motorola appl ic at ion note AN1060, M68HC11 Bootstrap Mode

(the bootloader mode is similar to that used on the MC68HC11K4).

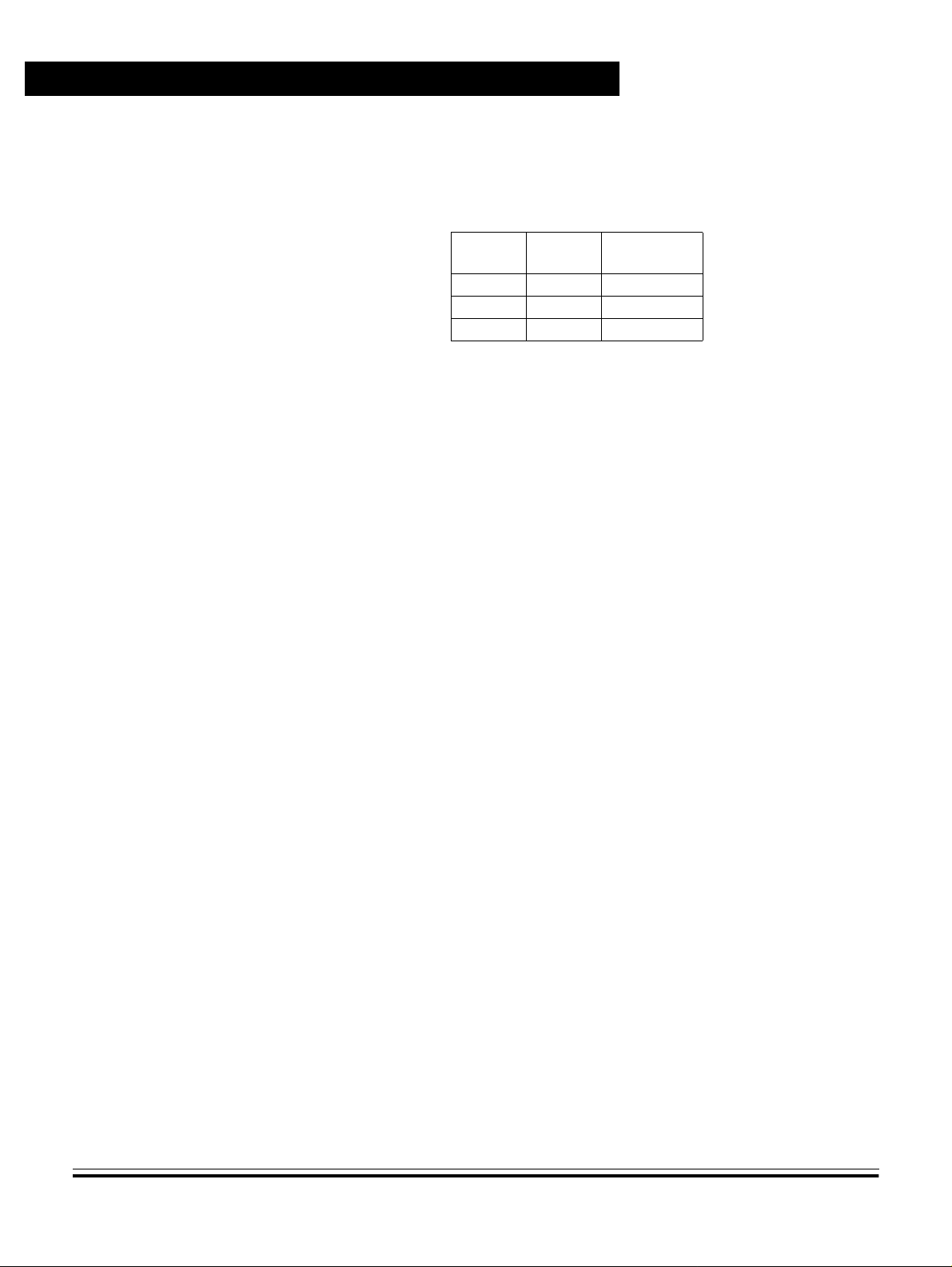

Table 3-1. Example bootloader baud rates

Sync.

byte

$FF 4 char. 7812 8192 11718 12288 15624

$FF 4 1200 1260 1800 1890 2400

$F0 4.9 9600 10080 14400 15120 19200

$FD 17.3 5208 5461 7812 8192 10416

$FD 13 3906 4096 5859 6144 7812

Timeout

delay

2.00MHz 2.10MHz 3.00MHz 3.15MHz 4.00MHz

Baud rates for an E clock of:

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Operating Modes and On-Chip Memory 43

Operating Modes and On-Chip Memory

3.4 On-chip memory

The MC68HC11P2 M CU includes 1024 bytes of on-chip RAM, 32kbytes

of ROM/EPROM and 640 bytes of EEPROM. The bootloader ROM

occupies a 512 byte block of the memory map. The CONFIG register is

implemented as a separate EEPROM byte.

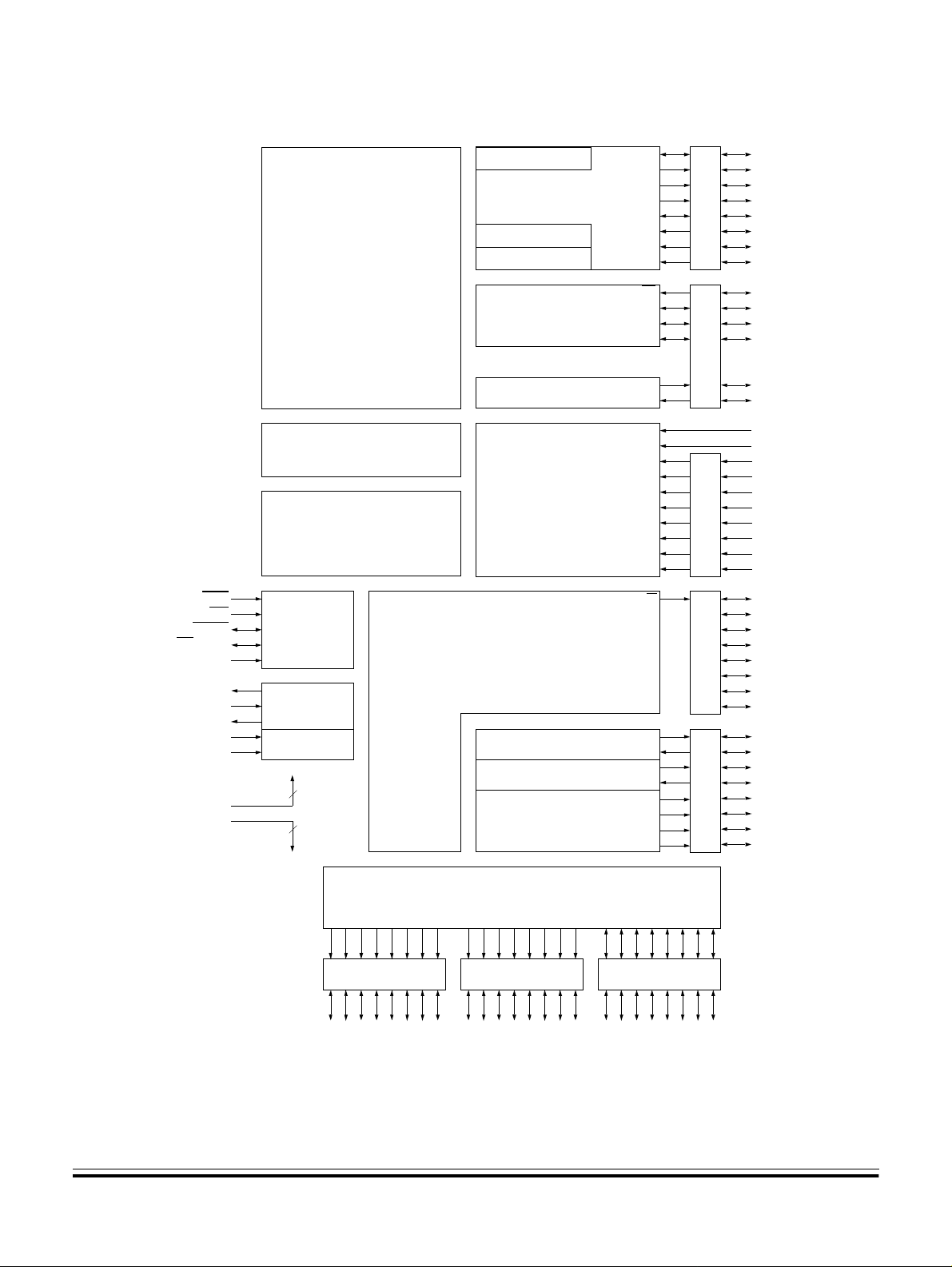

Start

address

$0000

$0080

$0480

$0D80

$1000

$8000

$BE40

$C000

$FFC0

–$FFFF

Single

chip

Expanded Special

Bootstrap

Special

Test

Register

block

RAM

1024 bytes

EEPROM

640 bytes

BootROM

Vectors

NVM

32kbytes

Vectors

$x000

$x07F

$x080

$x47F

$xD80

$xFFF

$BE40

$BFFF

$8000

$FFBF

$FFFF

Each of these blocks

can be mapped to any

4k page boundary,

using the INIT register.

This block may be remapped

to any 4k page, using INIT2.

Special Bootstrap mode only.

Special modes only.

32kbytes ROM

(MC68H C 11P2) or

32kbytes EPROM

(MC68HC711P2).

Can be mapped to either

$0000–$7FFF or

$8000–$FFFF,

using the CONFIG register.

Normal mode vectors.

Figure 3-1. MC68HC11P2 memory map

3.4.1 Mapping allocations

Memory locations for on-chi p resources are the same for both expanded

and single chip modes. The 12 8-byte regi ster blo ck origi nates at $0000

after reset and can be placed at any other 4k boundary ($x000) after

reset by writing an app ropriate value to the IN IT register. Refer to Figure

3-1, which shows the memory map.

The on-board 1024-b yte RAM is initially located at $0080 aft er reset. The

RAM is divided into two sections of 128 byt es and 896 bytes. If RAM and

Technical Data MC68HC11P2 — Rev 1.0

44 Operating Modes and On-Chip Memory MOTOROLA

Operating Modes and On-Chip Memory

On-chip memory

registers are both mapped to the same 4k boundary, RAM starts at

$x080 and 128 bytes are remapped at $x400–$x47F. Otherwise, RAM

starts at $x00 0.

Remapping is accomplished by writing appropriate values into the two

nibbles of the INIT register.

The 640-byte EEPROM is initially located at $0D80 after reset when

EEPROM is enabled in the memory map by the CONFIG register.

EEPROM can be placed at any ot her 4k bounda ry ($xD80) by writi ng to

the INIT2 register.

If ROM is available, the ROMAD and ROMON bits in the CONFIG

register control the position and presence of ROM in the memory map.

In special test mode, the ROMON bit is cleared so the ROM is removed

from the memory map. In single chip mode, the ROMAD bit is set to one

after reset, which enables the ROM at $8000–$FFFF. In expanded

mode, the ROM may be enabled from $0000–7FFF (ROMAD = 0) to

allow an external memory to contain the interrupt vectors and

initialization code.

In special bootstrap mode, a bootloader ROM is enabled at locations

$BE40–$BFFF. The vectors for special bootstrap mode are contained in

the bootloader progr am. The boot ROM occupies a 512 by te block of the

memory map, though not all locations are used.

3.4.1.1 RAM

The MC68HC11P2 ha s 10 24 b y te s of f ul ly stat ic R A M t hat are used for

storing instructions, variables and temporary data during program

execution. RAM can be placed at any 4k boundary in the 64kbyte

address space by writing an appropriate value to the INIT register.

By default, RAM is initially located at $0080 in the memory map. Direct

addressing mode can acce ss the first 128 location s of RAM using a onebyte address op erand. Direct mode accesses save program memory

space and execution time. R egisters c an be mo ved to oth er bounda ries

to allow 256 bytes of RAM to be located in direct addressing space.

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Operating Modes and On-Chip Memory 45

Operating Modes and On-Chip Memory

The on-chip RAM is a fully static memory. RAM contents can be

preserved during periods of processor inactivity by either of two

methods, both of which reduce power consumption:

1. During the software-based STOP mode, MCU clocks are stop ped,

but the MCU continues to draw power from VDD. Power supply

current is directly related to operating frequency in CMOS

integrated circuits and there is very little leakage when the clocks

are stopped. Thes e two factors reduce power consumptio n while

the MCU is in STOP mode.

2. To reduce power consumption to a minimum, VDD can be turned

off, and the MODB/VSTBY p in can be used to supply RAM power

from either a battery back-up or a second power supply. Although

this method requires external hardware, it is very effective. Refer

to Pin Descriptions for information about how to connect the

stand-by RAM power supply and to Resets and Interrupts for a

description of low power operation.

3.4.1.2 ROM and EPROM

3.4.1.3 Bootloader ROM

The MC68HC11P2 MCU has 32kbytes of ROM/EPROM. The

ROM/EPROM array is enabled when the ROMON bit in the CONFIG

register is set to one (erased). The ROMAD bit in CONFIG places the

ROM/EPROM at either $8000–$FFFF out of reset (ROMAD = 1) or at

$0000–$7FFF (ROMAD = 0) in expanded mode.

The bootloader ROM is enabled at address $BE40–$BFFF during

special bootstrap mode. The reset vector is fetched from this ROM an d

the MCU executes the bootloader firmware. In normal modes, the

bootloader ROM is disabled.

Technical Data MC68HC11P2 — Rev 1.0

46 Operating Modes and On-Chip Memory MOTOROLA

3.4.2 Registers

Table 3-2. Register and control bit assignments (Sheet 1 of 4)

Operating Modes and On-Chip Memory

On-chip memory

In Table 3-2, a summary of registers and control bits, the registers are

shown in ascending order within the 128-byte register block. The

addresses shown are for default block mapping ($0000–$007F),

however, the INIT register remaps the block to any 4k page

($x000–$x07F).

Register name

Port A data (PORTA) $0000 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 undefined

Data direction A (DDRA) $0001 DDA7 DDA6 DDA5 DDA4 DDA3 DDA2 DDA1 DDA0 0000 0000

Data direction B (DDRB) $0002 DDB7 DDB6 DDB5 DDB4 DDB3 DDB2 DDB1 DDB0 0000 0000

Data direction F (DDRF) $0003 DDF7 DDF6 DDF5 DDF4 DDF3 DDF2 DDF1 DDF0 0000 0000

Port B data (PORTB) $0004 PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 undefined

Port F data (PORTF) $0005 PF7 PF6 PF5 PF4 PF3 PF2 PF1 PF0 undefined

Port C data (PORTC) $0006 PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0 undefined

Data direction C (DDRC) $0007 DDC7 DDC6 DDC5 DDC4 DDC3 DDC2 DDC1 DDC0 0000 0000

Port D data (PORTD) $0008 0 0 PD5 PD4 PD3 PD2 PD1 PD0 undefined

Data direction D (DDRD) $0009 0 0 DDD5 DDD4 DDD3 DDD2 DDD1 DDD0 0000 0000

Port E data (PORTE) $000A PE7 PE6 PE5 PE4 PE3 PE2 PE1 PE0 undefined

Timer compare force (CFORC) $000B FOC1 FOC2 FOC3 FOC4 FOC5 0 0 0 0000 0000

Output compare 1 mask (OC1M) $000C OC1M7 OC1M6 OC1M5 OC1M4 OC1M3 0 0 0 0000 0000

Output compare 1 data (OC1D) $000D OC1D7 OC1D6 OC1D5 OC1D4 OC1D3 0 0 0 0000 0000

Timer count (TCNT) high $000E (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 0000 0000

Timer count (TCNT) low $000F (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) 0000 0000

Timer input capture 1 (TIC1) high $0010 (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) undefined

Timer input capture 1 (TIC1) low $0011 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

Timer input capture 2 (TIC2) high $0012 (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) undefined

Timer input capture 2 (TIC2) low $0013 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

Timer input capture 3 (TIC3) high $0014 (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) undefined

Timer input capture 3 (TIC3) low $0015 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

Timer output compare 1 (TOC1) high $001 6 (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 1111 1111

Timer output compare 1 (TOC1) low $0017 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) 1111 1111

Timer output compare 2 (TOC2) high $001 8 (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 1111 1111

Timer output compare 2 (TOC2) low $0019 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) 1111 1111

Timer output compare 3 (TOC3) high $001A (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 1111 1111

Timer output compare 3 (TOC3) low $001B (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) 1111 1111

Address

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

State

on reset

MC68HC11P2 — Rev 1.0 Technical Data

MOTOROLA Operating Modes and On-Chip Memory 47

Operating Modes and On-Chip Memory

Table 3-2. Register and control bit assignments (Sheet 2 of 4)

Register name

Timer output compare 4 (TOC4) high $001C (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 1111 1111

Timer output compare 4 (TOC4) low $ 001D (bit 7) (6) (5) (4) (3) (2) (1) (b it 0) 1111 1111

Capture 4/compare 5 (TI4/O5) high $001E (bit 15) (14) (13) (12) (11) (10) (9) (bit 8) 1111 1111

Capture 4/compare 5 (TI4/O5) low $001F (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) 1111 1111

Timer control 1 (TCTL1) $0020 OM2 OL2 OM3 OL3 OM4 OL4 OM5 OL5 0000 0000

Timer control 2 (TCTL2) $0021 EDG4B EDG4A EDG1B EDG1A EDG2B EDG2A EDG3B EDG3A 0000 0000

Timer interrupt mask 1 (TMSK1) $0022 OC1I OC2I OC3I OC4I I4/O5I IC1I IC2I IC3I 0000 0000

Timer interrupt flag 1 (TFLG1) $0023 OC1F OC2F OC3F OC4F I4/O5F IC1F IC2F IC3F 0000 0000

Timer interrupt mask 2 (TMSK2) $0024 TOI RTII PAOVI PAII 0 0 PR1 PR0 0000 0000

Timer interrupt flag 2 (TFLG2) $0025 TOF RTIF PAOVF PAIF 0 0 0 0 0000 0000

Pulse accumulator control (PACTL) $0026 0 PAEN PAMODPEDGE 0 I4/O5 RTR1 RTR0 0000 0000

Pulse accumulator count (PACNT) $0027 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

SPI control (SPCR) $0028 SPIE SPE DWOM MSTR CPOL CPHA SPR1 SPR0 0000 01uu

SPI status (SPSR) $0029 SPIF WCOL 0 MODF 0 0 0 0 0000 0000

SPI data (SPDR) $002A (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

EPROM programming (EPROG)

Port pull-up assignment (PPAR) $002C 0 0 0 0 HPPUE GPPUE FPPUE BPPUE 0000 1111

reserved $002D

PLL control (PLLCR) $002E PLLON BCS AUTO BWC VCOT MCS LCK WEN 1010 1000

Synthesizer program (SYNR) $002F SYNX1 SYNX0 SYNY5 SYNY4 SYNY3 SYNY2 SYNY1 SYNY0 0000 1011

A/D control & status (ADCTL) $0030 CCF 0 SCAN MULT CD CC CB CA u0uu uuuu

A/D result 1 (ADR1) $0031 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

A/D result 2 (ADR2) $0032 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

A/D result 3 (ADR3) $0033 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

A/D result 4 (ADR4) $0034 (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

B lock protect (BPROT) $0035 BULKP 0 BPRT4 PTCON BPRT3 BPRT2 BPRT 1 BPRT0 1011 1111

reserved $0036

EEPROM mapping (INIT2) $0037 EE3 EE2 EE1 EE0 M3DL1 M3DL0 M2DL1 M2DL0 0000 0000

System config. options 2 (OPT2) $0038 LIRDV CWOM STRCH IRVNE LSBF SPR2 0 0 000x 0000

System config. options 1 (OPTION) $0039 ADPU CSEL IRQE DLY CME FCME CR1 CR0 0001 0000

COP timer arm/reset (COPRST) $003A (bit 7) (6) (5) (4) (3) (2) (1) (bit 0) undefined

EEPROM programming (PPROG) $003B ODD EVEN 0 BYTE ROW ERASE EELAT EEPGM 0000 0000

Highest priority interrupt (HPRIO) $003C RBOOT SMOD MDA PSEL4 PSEL3 PSEL2 PSEL1 PSEL0 xxx0 0110

RAM & I/O mapping (INIT) $003D RAM3 RAM2 RAM1 RAM0 REG3 REG2 REG1 REG0 0000 0000

Factory test (TEST1) $003E TILOP PLTST OCCR CBYP DISR FCM FCOP MIDLY 0000 x000

Configuration control (CONFIG ) $003F ROMAD 1 1 PAREN NOSECNOC OPRO MON EEON x1 1x 1xxx

Address

‡

$002B MBE 0 ELAT EXCOL EXROW 0 0 EPGM 0000 0000

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

State

on reset

Technical Data MC68HC11P2 — Rev 1.0