Datasheet MC68L11E1PB2, MC68L11E20FN2, MC68L11E20FU2, MC68L11E9B2, MC68L11E9FU2 Datasheet (Motorola)

...

M68HC11

Microcontrollers

M68HC11E Family

Technical Data

M68HC11E/D

Rev. 4, 7/2002

WWW.MOTOROLA.COM/SEMICONDUCTORS

MC68HC11E Family

Technical Data

To provide the most up-to-date information, the revision of our

documents on the World Wide Web will be the most current. Your printed

copy may b e an earlier revision. To ve rify you have the latest information

available, refer to:

http://www.motorola.com/semiconductors/

The following revision history table summarizes changes contained in

this document. For your convenience, the page number designators

have been linked to the appropriate location.

Motorola and the Stylized M Logo are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Motorola, Inc., 2002

0&+&()DPLO\²5HY

027252/$

7HFKQLFDO'DWD

5HYLVLRQ+LVWRU\

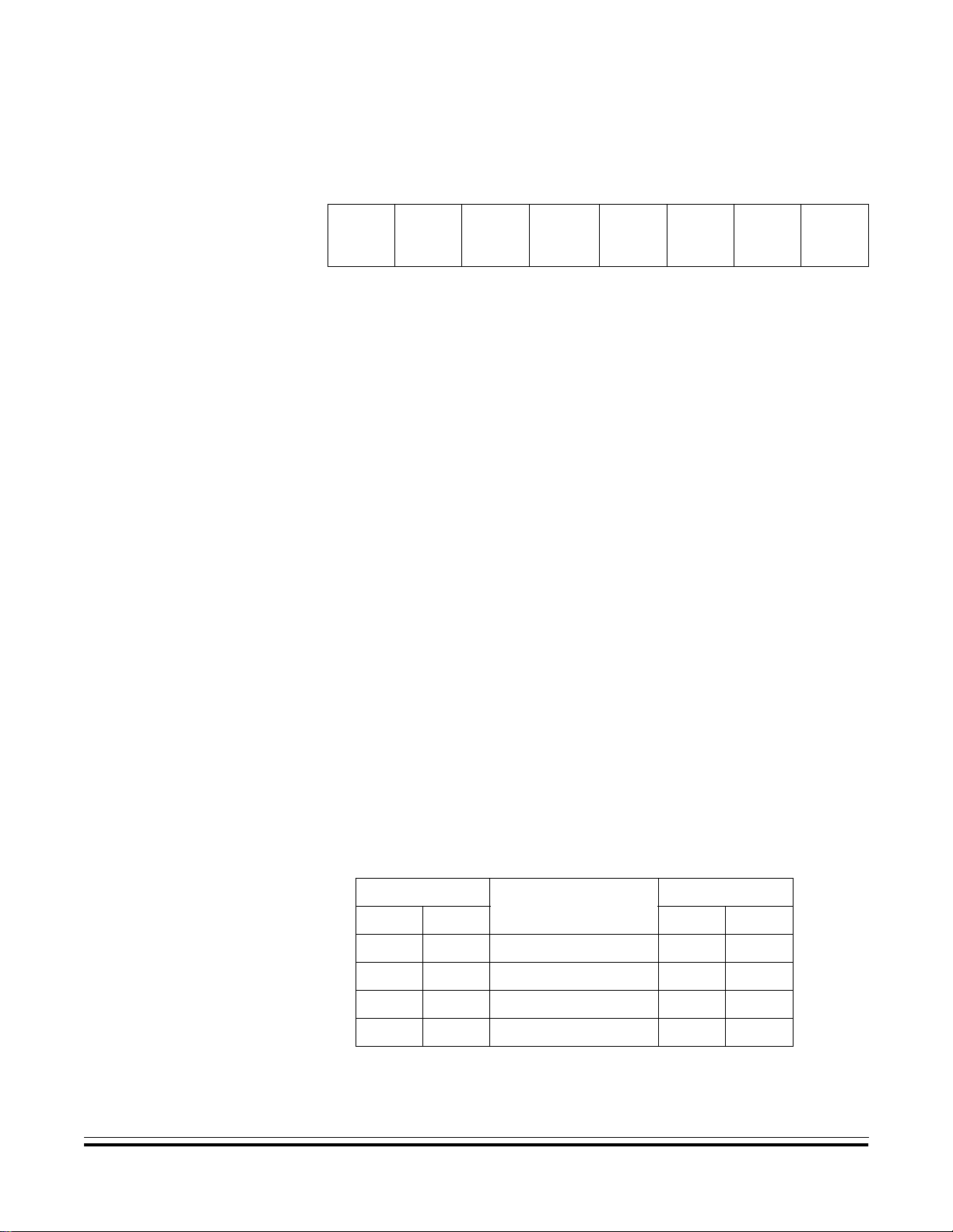

Revision History

Date

May, 2001 3.1

June, 2001 3.2

December,

2001

July, 2002 4

Revision

Level

3.3

Description

4.4.3.1 System Configuration Register — Addition to NOCOP bit

description

Added 11.22 EPROM Characteristics 251

11.22 EPROM Characteristics — For clarity, addition to note 2

following the table

7.8.2 Serial Communications Control Register 1 — SCCR1 bit 4

(M) description corrected

11.8 MC68L11E9/E20 DC Electrical Characteristics — Title

changed to include the MC68L11E20

11.9 MC68L11E9/E20 Supply Currents and Power Dissipation —

Title changed to include the MC68L11E2 0

11.11 MC68L11E9/E20 Control Timing — Title changed to include

the MC68L11E20

11.13 MC68L11E9/E20 Pe ripher al Port Timin g — Title changed to

include the MC68L1 1E20

11.15 MC68L11E9/E20 Analog-to-Digital Converter

Characteristics — Title changed to include the MC68L11E20

11.17 MC68L11E9/E20 Expansio n Bus Timing Characteristics —

Title changed to include the MC68L11E2 0

Page

Number(s)

88

251

153

226

227

230

236

241

244

11.19 MC68L11E9/E20 Serial Peirpheral Interface Characteristics

— Title changed to include the MC68L11E20

11.21 MC68L11E9/E20 EEPROM Char acteri stics — Title changed

to include the MC68L11E20

13.5 Extended Voltage Device Ordering Information (3.0 Vdc to

5.5 Vdc) — Updated table to include MC68L1120

7HFKQLFDO'DWD 0&+&()DPLO\²5HY

247

250

267

027252/$

Technical Data — M68HC11E Family

Section 1. General Description . . . . . . . . . . . . . . . . . . . .23

Section 2. Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . .27

Section 3. Central Processor Unit (CPU) . . . . . . . . . . . .45

Section 4. Operating Modes and On-Chip Memory . . . .65

Section 5. Resets and Interrupts . . . . . . . . . . . . . . . . . .107

Section 6. Parallel Input/Output (I/O) Ports . . . . . . . . .133

List of Sections

Section 7. Serial Communications Interface (SCI). . . .145

Section 8. Serial Peripheral Interface (SPI). . . . . . . . . .165

Section 9. Timing System. . . . . . . . . . . . . . . . . . . . . . . .177

Section 10. Analog-to-Digital (A/D) Converter . . . . . . .209

Section 11. Electrical Characteristics . . . . . . . . . . . . . .221

Section 12. Mechanical Data . . . . . . . . . . . . . . . . . . . . .253

Section 13. Ordering Information . . . . . . . . . . . . . . . . .261

Appendix A. Development Support. . . . . . . . . . . . . . . .269

Appendix B. EVBU Schematic . . . . . . . . . . . . . . . . . . . .275

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA List of Sections 5

List of Sec ti o ns

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . .277

EB184 — Enabling the Secu rity Feature

on the MC68HC711E9 Devices with PCbug11

on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . 323

EB188 — Enabling the Secu rity Feature

on M68H C811E2 Devi ces with PCbug11

on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . 327

EB296 — Programming MC68HC711E9 Devices

with PCbug11 and the M68HC11EVBU . . . . . . . . . 331

Technical Data MC68HC11E Family — Rev. 4

6 List of Sections MOTOROLA

Technical Data — M68HC11E Family

Section 1. General Description

1.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

1.4 Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Section 2. Pin Descriptions

2.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table of Contents

2.3 V

2.4 RESET

2.5 Crystal Driver and External Clock Input

2.6 E-Clock Output (E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

2.7 Interrupt Request (IRQ

2.8 Non-Maskable Interrupt (XIRQ

2.9 MODA and MODB (MODA/LIR and MODB/V

2.10 VRL and VRH. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.11 STRA/AS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.12 STRB/R/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.13 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

2.13.1 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

2.13.2 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

2.13.3 Port C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2.13.4 Port D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

2.13.5 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

and VSS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

(XTAL and EXTAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

/V

). . . . . . . . . . . . . . . . . . . .36

PPE

) . . . . . . . . .37

STBY

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Table of Contents 7

Table of Contents

Section 3. Central Processor Unit (CPU)

3.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3.1 Accumulators A, B, and D . . . . . . . . . . . . . . . . . . . . . . . . . .4 7

3.3.2 Index Register X (IX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.3 Index Register Y (IY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

3.3.6 Condition Code Register (CCR). . . . . . . . . . . . . . . . . . . . . .51

3.3.6.1 Carry/Borrow (C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.2 Overflow (V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.3 Zero (Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.4 Negative (N). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.5 Interrupt Mask (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.6 Half Carry (H). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.7 X Interrupt Mask (X). . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.8 STOP Disable (S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

3.4 Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

3.5 Opcodes and Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 3

3.6 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4

3.6.1 Immediate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

3.6.2 Direct . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.6.3 Extended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 5

3.6.4 Indexed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.6.5 Inherent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.6.6 Relative . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

3.7 Instruction Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Technical Data MC68HC11E Family — Rev. 4

8 Table of Contents M OTOROLA

Table of Contents

Section 4. Operating Modes and On-Chip Memory

4.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.3 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.3.1 Single-Chip Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.3.2 Expanded Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

4.3.3 Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

4.3.4 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.4 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 9

4.4.1 RAM and Input/Output Mapping. . . . . . . . . . . . . . . . . . . . . .80

4.4.2 Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

4.4.3 System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

4.4.3.1 System Configuration Register . . . . . . . . . . . . . . . . . . . .86

4.4.3.2 RAM and I/O Mapping Register . . . . . . . . . . . . . . . . . . . .89

4.4.3.3 System Configuration Options Register. . . . . . . . . . . . . .91

4.5 EPROM/OTPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

4.5.1 Programming an Individual EPROM Address . . . . . . . . . . .93

4.5.2 Programming the EPROM with Downloaded Data. . . . . . . .94

4.5.3 EPROM and EEPROM Programming

Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

4.6 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

4.6.1 EEPROM and CONFIG Programming and Erasure. . . . . . .98

4.6.1.1 Block Protect Register . . . . . . . . . . . . . . . . . . . . . . . . . . .9 9

4.6.1.2 EPROM and EEPROM Programming

Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

4.6.1.3 EEPROM Bulk Erase. . . . . . . . . . . . . . . . . . . . . . . . . . .103

4.6.1.4 EEPROM Row Erase. . . . . . . . . . . . . . . . . . . . . . . . . . .103

4.6.1.5 EEPROM Byte Erase. . . . . . . . . . . . . . . . . . . . . . . . . . .104

4.6.1.6 CONFIG Register Programming . . . . . . . . . . . . . . . . . .104

4.6.2 EEPROM Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Table of Contents 9

Table of Contents

Section 5. Resets and Interrupts

5.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

5.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

5.3 Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

5.3.1 Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . .109

5.3.2 External Reset (RESET) . . . . . . . . . . . . . . . . . . . . . . . . . .109

5.3.3 Computer Operating Properly (COP) Reset. . . . . . . . . . . .110

5.3.4 Clock Monitor Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

5.3.5 System Configuration Options Register . . . . . . . . . . . . . . .112

5.3.6 Configuration Control Register. . . . . . . . . . . . . . . . . . . . . .113

5.4 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

5.4.1 Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . .115

5.4.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

5.4.3 Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

5.4.4 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . .116

5.4.5 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

5.4.6 Computer Operating Properly (COP). . . . . . . . . . . . . . . . .116

5.4.7 Serial Communications Interface (SCI) . . . . . . . . . . . . . . .116

5.4.8 Serial Peripheral Interface (SPI). . . . . . . . . . . . . . . . . . . . .117

5.4.9 Analog-to-Digital (A/D) Converter. . . . . . . . . . . . . . . . . . . .117

5.4.10 System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

5.5 Reset and Interrupt Priority. . . . . . . . . . . . . . . . . . . . . . . . . . .117

5.5.1 Highest Priority Interrupt and Miscellaneous Register. . . .119

5.6 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

5.6.1 Interrupt Recognition and Register Stacking . . . . . . . . . . .122

5.6.2 Non-Maskable Interrupt Request (XIRQ). . . . . . . . . . . . . .123

5.6.3 Illegal Opcode Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

5.6.4 Software Interrupt (SWI). . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.6.5 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

5.6.6 Reset and Interrupt Processing . . . . . . . . . . . . . . . . . . . . .124

5.7 Low-Power Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

5.7.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.7.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

Technical Data MC68HC11E Family — Rev. 4

10 Table of Contents M OTOROLA

Table of Contents

Section 6. Parallel Input/Output (I/O) Ports

6.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

6.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

6.3 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

6.4 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

6.5 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

6.6 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

6.7 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

6.8 Handshake Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

6.9 Parallel I/O Control Register. . . . . . . . . . . . . . . . . . . . . . . . . .141

Section 7. S e ri al Com m uni c at ion s Int er fa ce (SCI)

7.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

7.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

7.3 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

7.4 Transmit Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

7.5 Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

7.6 Wakeup Feature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

7.6.1 Idle-Line Wakeup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

7.6.2 Address-Mark Wakeup. . . . . . . . . . . . . . . . . . . . . . . . . . . .150

7.7 SCI Error Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

7.8 SCI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

7.8.1 Serial Communications Data Register . . . . . . . . . . . . . . . .152

7.8.2 Serial Communications Control Register 1 . . . . . . . . . . . .153

7.8.3 Serial Communications Control Register 2 . . . . . . . . . . . .154

7.8.4 Serial Communication Status Register. . . . . . . . . . . . . . . .155

7.8.5 Baud Rate Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

7.9 Status Flags and Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . .160

7.10 Receiver Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Table of Contents 11

Table of Contents

Section 8. Serial Peripheral Interface (SPI)

8.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165

8.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

8.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

8.4 SPI Transfer Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

8.5 Clock Phase and Polarity Controls . . . . . . . . . . . . . . . . . . . . .169

8.6 SPI Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

8.6.1 Master In/Slave Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

8.6.2 Master Out/Slave In . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

8.6.3 Serial Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

8.6.4 Slave Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

8.7 SPI System Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

8.8 SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172

8.8.1 Serial Peripheral Control Register . . . . . . . . . . . . . . . . . .173

8.8.2 Serial Peripheral Status Register . . . . . . . . . . . . . . . . . . .175

8.8.3 Serial Peripheral Data I/O Register . . . . . . . . . . . . . . . . . . 176

Section 9. Timing System

9.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

9.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

9.3 Timer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

9.4 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

9.4.1 Timer Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . .183

9.4.2 Timer Input Capture Registers. . . . . . . . . . . . . . . . . . . . . .184

9.4.3 Timer Input Capture 4/Output Compare 5 Register. . . . . .186

9.5 Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

9.5.1 Timer Output Compare Registers . . . . . . . . . . . . . . . . . . .187

9.5.2 Timer Compare Force Register . . . . . . . . . . . . . . . . . . . . .190

9.5.3 Output Compare Mask Register. . . . . . . . . . . . . . . . . . . . .191

9.5.4 Output Compare Data Register . . . . . . . . . . . . . . . . . . . . .192

9.5.5 Timer Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . .193

9.5.6 Timer Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . .194

9.5.7 Timer Interrupt Mask 1 Register. . . . . . . . . . . . . . . . . . . . .195

9.5.8 Timer Interrupt Flag 1 Register . . . . . . . . . . . . . . . . . . . . .196

Technical Data MC68HC11E Family — Rev. 4

12 Table of Contents M OTOROLA

Table of Contents

9.5.9 Timer Interrupt Mask 2 Register. . . . . . . . . . . . . . . . . . . . .196

9.5.10 Timer Interrupt Flag Register 2 . . . . . . . . . . . . . . . . . . . . .198

9.6 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

9.6.1 Timer Interrupt Mask Register 2. . . . . . . . . . . . . . . . . . . . .200

9.6.2 Timer Interrupt Flag Register 2 . . . . . . . . . . . . . . . . . . . . .201

9.6.3 Pulse Accumulator Control Register . . . . . . . . . . . . . . . . .202

9.7 Computer Operating Properly (COP) Watchdog Function . . .203

9.8 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

9.8.1 Pulse Accumulator Control Register . . . . . . . . . . . . . . . . .205

9.8.2 Pulse Accumulator Count Register . . . . . . . . . . . . . . . . . .206

9.8.3 Pulse Accumulator Status and Interrupt Bits . . . . . . . . . . .207

Section 10. Analog-to-Digital (A/D) Converter

10.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

10.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

10.3 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .210

10.3.1 Multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .210

10.3.2 Analog Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212

10.3.3 Digital Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212

10.3.4 Result Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212

10.3.5 A/D Converter Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

10.3.6 Conversion Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

10.4 A/D Converter Power-Up and Clock Select . . . . . . . . . . . . . .214

10.5 Conversion Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215

10.6 Channel Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

10.7 Single-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . .216

10.8 Multiple-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . .217

10.9 Operation in Stop and Wait Modes. . . . . . . . . . . . . . . . . . . . .217

10.10 A/D Control/Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . 218

10.11 A/D Converter Result Registers . . . . . . . . . . . . . . . . . . . . . . .220

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Table of Contents 13

Table of Contents

Section 11. Electrical Characteristics

11.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

11.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

11.3 Maximum Ratings for Standard

and Extended Voltage Devices . . . . . . . . . . . . . . . . . . . . .222

11.4 Functional Operating Range. . . . . . . . . . . . . . . . . . . . . . . . . .223

11.5 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

11.6 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . .224

11.7 Supply Currents and Power Dissipation. . . . . . . . . . . . . . . . .225

11.8 MC68L11E9/E20 DC Electrical Characteristics . . . . . . . . . . .226

11.9 MC68L11E9/E20 Supply Currents and Power Dissipation. . .227

11.10 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

11.11 MC68L11E9/E20 Control Timing . . . . . . . . . . . . . . . . . . . . . .230

11.12 Peripheral Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .235

11.13 MC68L11E9/E20 Peripheral Port Timing . . . . . . . . . . . . . . . .236

11.14 Analog-to-Digital Converter Characteristics . . . . . . . . . . . . . .240

11.15 MC68L11E9/E20 Analog-to-Digital

Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . .241

11.16 Expansion Bus Timing Characteristics. . . . . . . . . . . . . . . . . .242

11.17 MC68L11E9/E20 Expansion Bus Timing Characteristics. . . .244

11.18 Serial Peripheral Interface Timing Characteristics . . . . . . . . .246

11.19 MC68L11E9/E20 Serial Peirpheral

Interface Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . .247

11.20 EEPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . .250

11.21 MC68L11E9/E20 E EPROM Characteristics. . . . . . . . . . . . . .250

11.22 EPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

Technical Data MC68HC11E Family — Rev. 4

14 Table of Contents M OTOROLA

Table of Contents

Section 12. Mechanical Data

12.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

12.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

12.3 52-Pin Plastic-Leaded Chip Carrier (Case 778) . . . . . . . . . . .254

12.4 52-Pin Windowed Ceramic-Leaded

Chip Carrier (Case 778B) . . . . . . . . . . . . . . . . . . . . . . . . .255

12.5 64-Pin Quad Flat P a ck (Case 840C) . . . . . . . . . . . . . . . . . . .256

12.6 52-Pin Thin Quad Flat Pack (Case 848D) . . . . . . . . . . . . . . .257

12.7 56-Pin Dual in-Line Package (Case #859) . . . . . . . . . . . . . . .258

12.8 48-Pin Plastic DIP (Case 767) . . . . . . . . . . . . . . . . . . . . . . . .259

Section 13. Ordering Information

13.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .261

13.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .261

13.3 Standard Device Ordering Information. . . . . . . . . . . . . . . . . .262

13.4 Custom ROM Device Ordering Information . . . . . . . . . . . . . .265

13.5 Extended Voltage Device Ordering Information

(3.0 Vdc to 5.5 Vdc). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .267

Appendix A. Development Support

A.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .269

A.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .269

A.3 Motorola M68HC11 E-Series Development Tools . . . . . . . . .270

A.4 EVS — Evaluation System. . . . . . . . . . . . . . . . . . . . . . . . . . .270

A.5 Motorola Modular Development System (MMDS11) . . . . . . .271

A.6 SPGMR11 — Serial Programmer for M68HC11 MCUs . . . . .273

Appendi x B . EVBU Schematic

M68HC11EVBU Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .275

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Table of Contents 15

Table of Contents

AN1060

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . 277

EB184

EB184 — Enabling the Security Feature on the MC68HC711E9

Devices with PCbug11 on the M68HC711E9PGMR 323

EB188

EB188 — Enabling the Security Feature on M68HC811E2

Devices with PCbug11 on the M68HC711E9PGMR . . . . . . . . . 327

EB296

EB296 — Programming MC68HC711E9 Devices

with PCbug11 and the M68HC11EVBU. . . . . . . . . . . . . . . . . . . 331

Technical Data MC68HC11E Family — Rev. 4

16 Table of Contents M OTOROLA

Technical Data — M68HC11E Family

Figure Title P age

1-1 M68HC11 E-Series Block Diagram . . . . . . . . . . . . . . . . . . . .26

2-1 Pin Assignments for 52-Pin PLCC and CLCC . . . . . . . . . . . .28

2-2 Pin Assignments for 64-Pin QFP . . . . . . . . . . . . . . . . . . . . . .29

2-3 Pin Assignments for 52-Pin TQFP . . . . . . . . . . . . . . . . . . . . .3 0

2-4 Pin Assignments for 56-Pin SDIP. . . . . . . . . . . . . . . . . . . . . .31

2-5 Pin Assignments for 48-Pin DIP (MC68HC811E2). . . . . . . . .32

2-6 External Reset Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

2-7 External Reset Circuit with Delay . . . . . . . . . . . . . . . . . . . . . .33

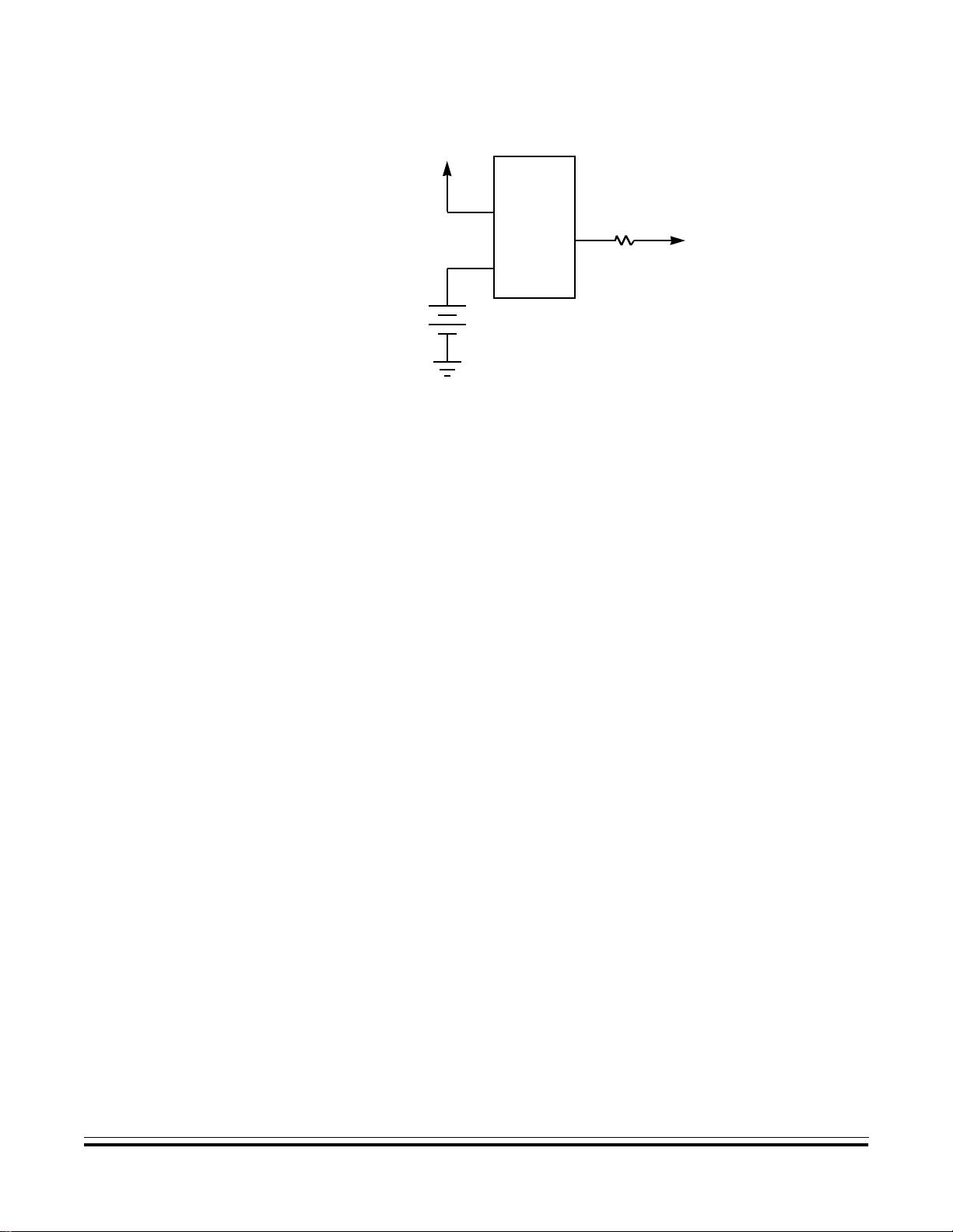

2-8 Common Parallel Resonant Crystal Connections . . . . . . . . .35

2-9 External Oscillator Connections . . . . . . . . . . . . . . . . . . . . . . .35

List of Figures

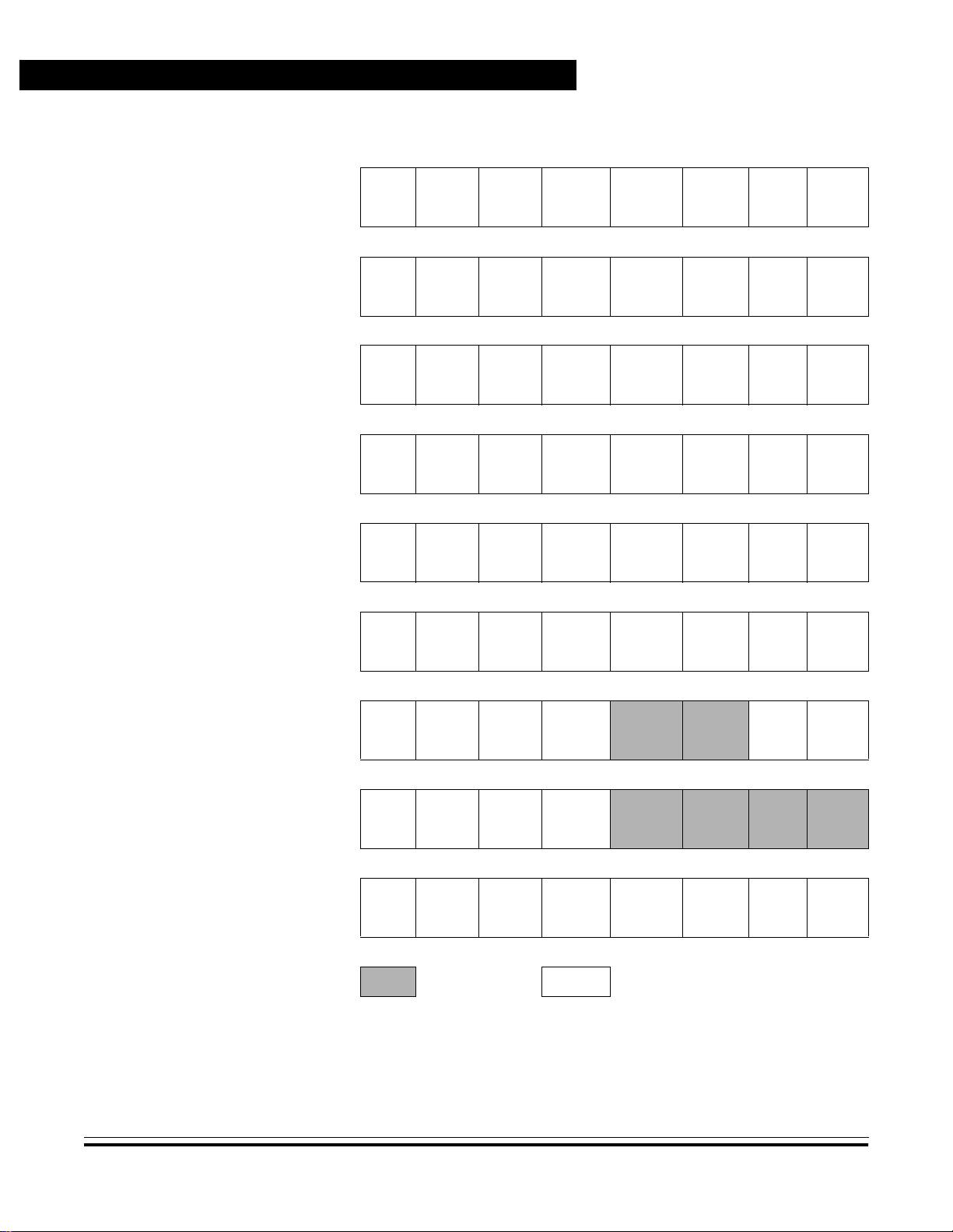

3-1 Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

3-2 Stacking Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 9

4-1 Address/Data Demultiplexi ng . . . . . . . . . . . . . . . . . . . . . . . . .68

4-2 Memory Map for MC68HC11E0. . . . . . . . . . . . . . . . . . . . . . .70

4-3 Memory Map for MC68HC11E1. . . . . . . . . . . . . . . . . . . . . . .70

4-4 Memory Map for MC68HC(7)11E9. . . . . . . . . . . . . . . . . . . . .71

4-5 Memory Map for MC68HC(7)11E20. . . . . . . . . . . . . . . . . . . .71

4-6 Memory Map for MC68HC811E2. . . . . . . . . . . . . . . . . . . . . .72

4-7 Register and Control Bit Assignments . . . . . . . . . . . . . . . . . .72

4-8 RAM Standby MODB/V

4-9 Highest Priority I-Bit Interrupt and Miscellaneous

Register (HPRIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

4-10 System Configuration Register (CONFIG) . . . . . . . . . . . . . . .87

4-11 MC68HC811E2 System Configuration

Register (CONFIG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

4-12 RAM and I/O Mapping Register (INIT) . . . . . . . . . . . . . . . . . .89

Connections . . . . . . . . . . . . . . .81

STBY

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA List of Figures 17

List of Figu r e s

Figure Title P age

4-13 System Configuration Options Register (OPTION) . . . . . . . .91

4-14 EPROM and EEPROM Programming

Control Register (PPROG) . . . . . . . . . . . . . . . . . . . . . . . .95

4-15 MC68HC711E20 EPROM Programming

Control Register (EPROG) . . . . . . . . . . . . . . . . . . . . . . . .96

4-16 Block Protect Register (BPROT) . . . . . . . . . . . . . . . . . . . . . .99

4-17 EPROM and EEPROM Programming

Control Register (PPROG) . . . . . . . . . . . . . . . . . . . . . . .101

5-1 Arm/Reset COP Timer Circuitry Register (COPRST). . . . . .111

5-2 System Configuration Options Register (OPTION) . . . . . . .112

5-3 Configuration Control Register (CONFIG) . . . . . . . . . . . . . .113

5-4 Highest Priority I-Bit Interrupt

and Miscellaneous Register (HPRIO) . . . . . . . . . . . . . . .119

5-5 Processing Flow Out of Reset . . . . . . . . . . . . . . . . . . . . . . .125

5-6 Interrupt Priority Resolution . . . . . . . . . . . . . . . . . . . . . . . . .127

5-7 Interrupt Source Resolution Within SCI . . . . . . . . . . . . . . . . 129

6-1 Port A Data Register (PORTA). . . . . . . . . . . . . . . . . . . . . . .134

6-2 Pulse Accumulator Control Register (PACTL) . . . . . . . . . . .135

6-3 Port B Data Register (PORTB). . . . . . . . . . . . . . . . . . . . . . .136

6-4 Port C Data Register (PORTC) . . . . . . . . . . . . . . . . . . . . . .136

6-5 Port C Latched Register (PORTCL) . . . . . . . . . . . . . . . . . . .137

6-6 Port C Data Direction Register (DDRC) . . . . . . . . . . . . . . . .137

6-7 Port D Data Register (PORTD) . . . . . . . . . . . . . . . . . . . . . .138

6-8 Port D Data Direction Register (DDRD) . . . . . . . . . . . . . . . .138

6-9 Port E Data Register (PORTE). . . . . . . . . . . . . . . . . . . . . . .139

6-10 Parallel I/O Control Register (PIOC). . . . . . . . . . . . . . . . . . .141

7-1 SCI Transmitter Block Diagram . . . . . . . . . . . . . . . . . . . . . .147

7-2 SCI Receiver Block Diagram . . . . . . . . . . . . . . . . . . . . . . . .149

7-3 Serial Communications Data Register (SCDR) . . . . . . . . . .152

7-4 Serial Communications Control Register 1 (SCCR1). . . . . .153

7-5 Serial Communications Control Register 2 (SCCR2). . . . . .154

7-6 Serial Communications Status Register (SCSR) . . . . . . . . .155

7-7 Baud Rate Register (BAUD). . . . . . . . . . . . . . . . . . . . . . . . .157

Technical Data MC68HC11E Family — Rev. 4

18 List of Figures MOTOROLA

List of Figures

Figure Title P age

7-8 SCI Baud Rate Generator Block Diagram . . . . . . . . . . . . . .160

7-9 MC68HC(7)11E20 SCI Baud Rate

Generator Block Diagram . . . . . . . . . . . . . . . . . . . . . . . .161

7-10 Interrupt Source Resolution Within SCI . . . . . . . . . . . . . . . .163

8-1 SPI Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

8-2 SPI Transfer Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

8-3 Serial Peripheral Control Register (SPCR). . . . . . . . . . . . . .173

8-4 Serial Peripheral Status Register (SPSR) . . . . . . . . . . . . . .175

8-5 Serial Peripheral Data I/O Register (SPDR). . . . . . . . . . . . .176

9-1 Timer Clock Divider Chains . . . . . . . . . . . . . . . . . . . . . . . . .179

9-2 Capture/Compare Block Diagram. . . . . . . . . . . . . . . . . . . . .181

9-3 Timer Control Register 2 (TCTL2) . . . . . . . . . . . . . . . . . . . .183

9-4 Timer Input Capture 1 Register Pair (TIC1) . . . . . . . . . . . . .184

9-5 Timer Input Capture 2 Register Pair (TIC2) . . . . . . . . . . . . .185

9-6 Timer Input Capture 3 Register Pair (TIC3) . . . . . . . . . . . . .185

9-7 Timer Input Capture 4/Output

Compare 5 Register Pair (TI4/O5). . . . . . . . . . . . . . . . . .186

9-8 Timer Output Compare 1 Register Pair (TOC1). . . . . . . . . .188

9-9 Timer Output Compare 2 Register Pair (TOC2). . . . . . . . . .188

9-10 Timer Output Compare 3 Register Pair (TOC3). . . . . . . . . .189

9-11 Timer Output Compare 4 Register Pair (TOC4). . . . . . . . . .189

9-12 Timer Compare Force Register (CFORC) . . . . . . . . . . . . . .190

9-13 Output Compare 1 Mask Register (OC1M) . . . . . . . . . . . . .191

9-14 Output Compare 1 Data Register (OC1D) . . . . . . . . . . . . . .192

9-15 Timer Counter Register (TCNT). . . . . . . . . . . . . . . . . . . . . .193

9-16 Timer Control Register 1 (TCTL1) . . . . . . . . . . . . . . . . . . . .194

9-17 Timer Interrupt Mask 1 Register (TMSK1) . . . . . . . . . . . . . .195

9-18 Timer Interrupt Flag 1 Register (TFLG1) . . . . . . . . . . . . . . .196

9-19 Timer Interrupt Mask 2 Register (TMSK2) . . . . . . . . . . . . . .196

9-20 Timer Interrupt Flag 2 Register (TFLG2) . . . . . . . . . . . . . . .198

9-21 Timer Interrupt Mask 2 Register (TMSK2) . . . . . . . . . . . . . .200

9-22 Timer Interrupt Flag 2 Register (TFLG2) . . . . . . . . . . . . . . .201

9-23 Pulse Accumulator Control Register (PACTL) . . . . . . . . . . .202

9-24 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA List of Figures 19

List of Figu r e s

Figure Title P age

9-25 Pulse Accumulator Control Register (PACTL) . . . . . . . . . . .205

9-26 Pulse Accumulator Count Register (PACNT). . . . . . . . . . . .206

9-27 Timer Interrupt Mask 2 Register (TMSK2) . . . . . . . . . . . . . .207

9-28 Timer Interrupt Flag 2 Register (TFLG2) . . . . . . . . . . . . . . .207

10-1 A/D Converter Block Diagram . . . . . . . . . . . . . . . . . . . . . . .211

10-2 Electrical Model of an A/D Input Pin (Sample Mode) . . . . . .211

10-3 A/D Conversion Sequence . . . . . . . . . . . . . . . . . . . . . . . . . .213

10-4 System Configuration Options Register (OPTION) . . . . . . .214

10-5 A/D Control/Status Register (ADCTL) . . . . . . . . . . . . . . . . .218

10-6 Analog-to-Digital Converter

Result Registers (ADR1–ADR4) . . . . . . . . . . . . . . . . . . .220

11-1 Test Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .228

11-2 Timer Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .230

11-3 POR External Reset Timing Diagram. . . . . . . . . . . . . . . . . .231

11-4 STOP Recovery Timing Diagram. . . . . . . . . . . . . . . . . . . . .232

11-5 WAIT Recovery from Interrupt Timing Diagram . . . . . . . . . .233

11-6 Interrupt Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . .234

11-7 Port Read Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . .237

11-8 Port Write Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . .237

11-9 Simple Input Strobe Timing Diagram . . . . . . . . . . . . . . . . . .237

11-10 Simple Output Strobe Timing Diagram. . . . . . . . . . . . . . . . .238

11-11 Port C Input Handshake Timing Diagram. . . . . . . . . . . . . . .238

11-12 Port C Output Handshake Timing Diagram . . . . . . . . . . . . .238

11-13 3-State Variation of Output Handshake Timing Diagram

(STRA Enables Output Buffer) . . . . . . . . . . . . . . . . . . . .239

11-14 Multiplexed Expansion Bus Timing Diagram . . . . . . . . . . . .245

11-15 SPI Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .248

B-1 EVBU Schematic Diagram. . . . . . . . . . . . . . . . . . . . . . . . . .276

Technical Data MC68HC11E Family — Rev. 4

20 List of Figures MOTOROLA

Technical Data — M68HC11E Family

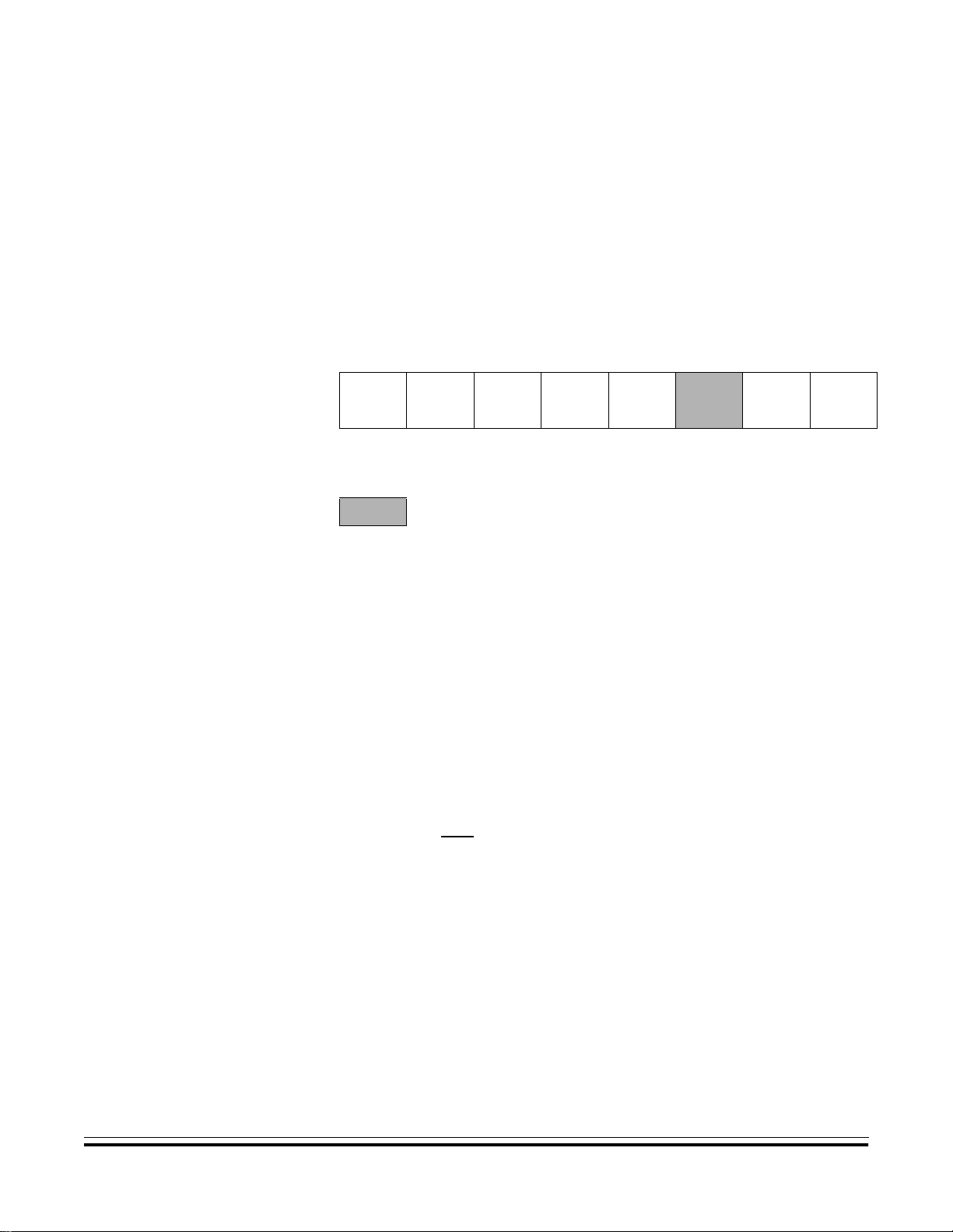

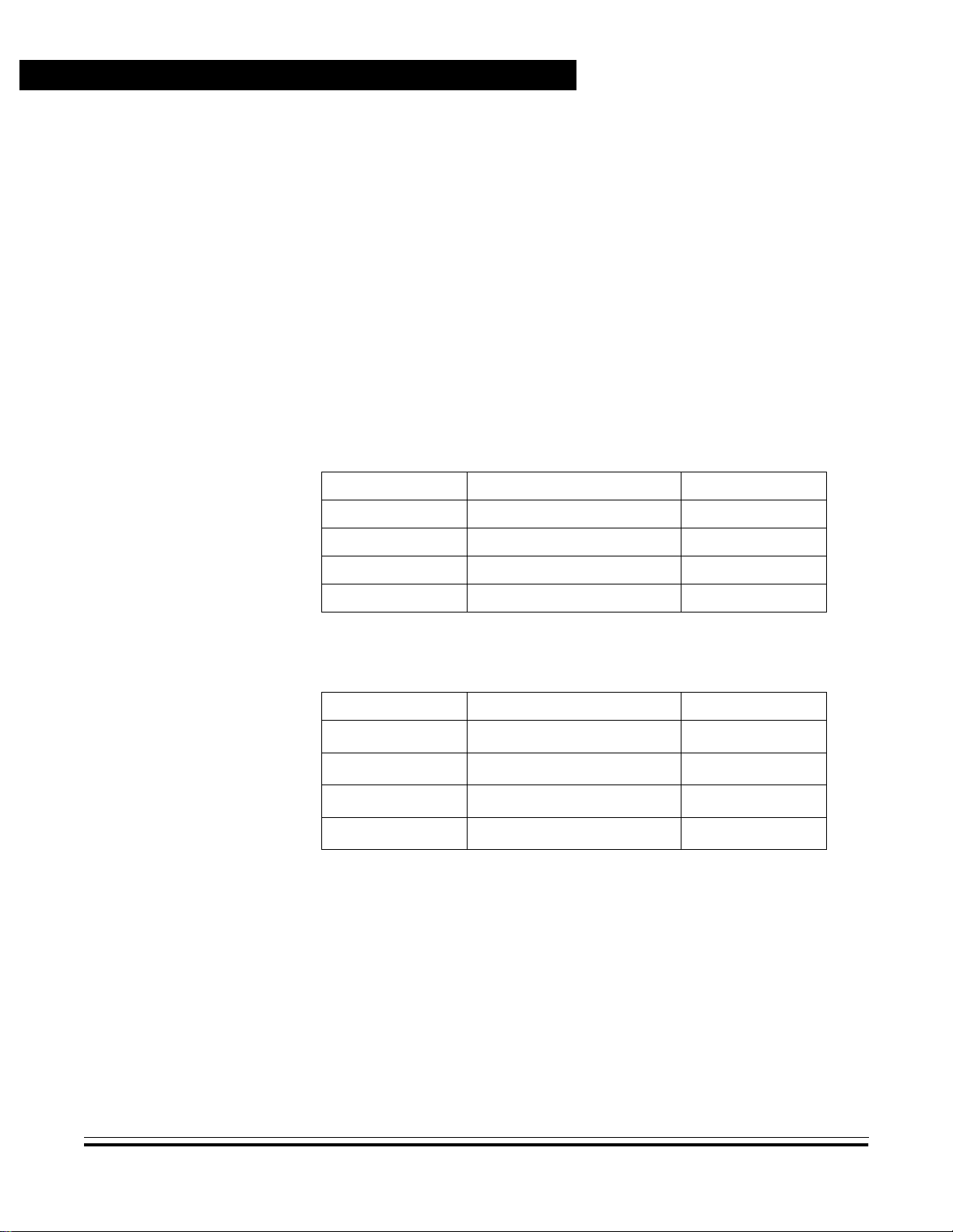

Table Title Page

2-1 Port Signal Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

3-1 Reset Vector Comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

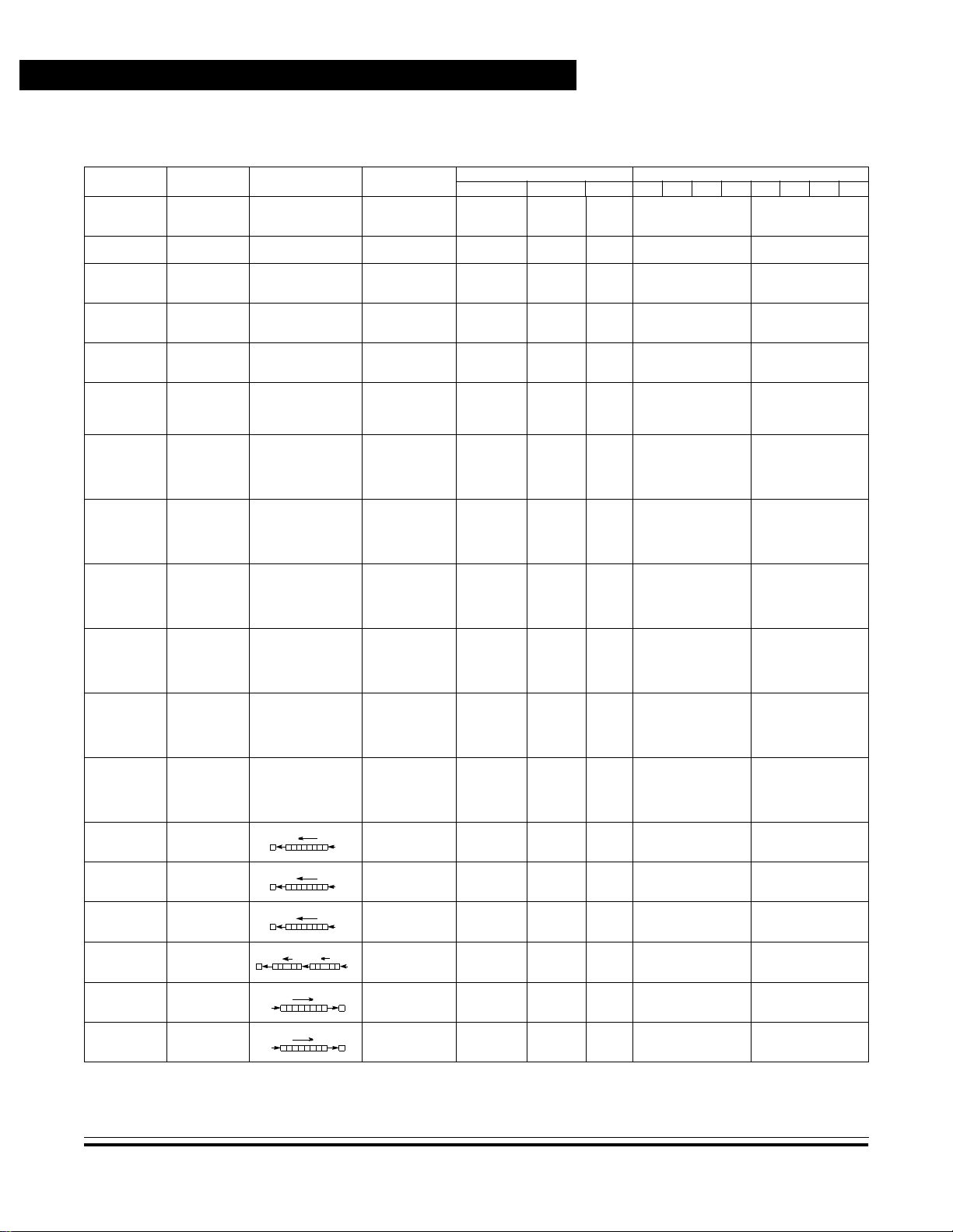

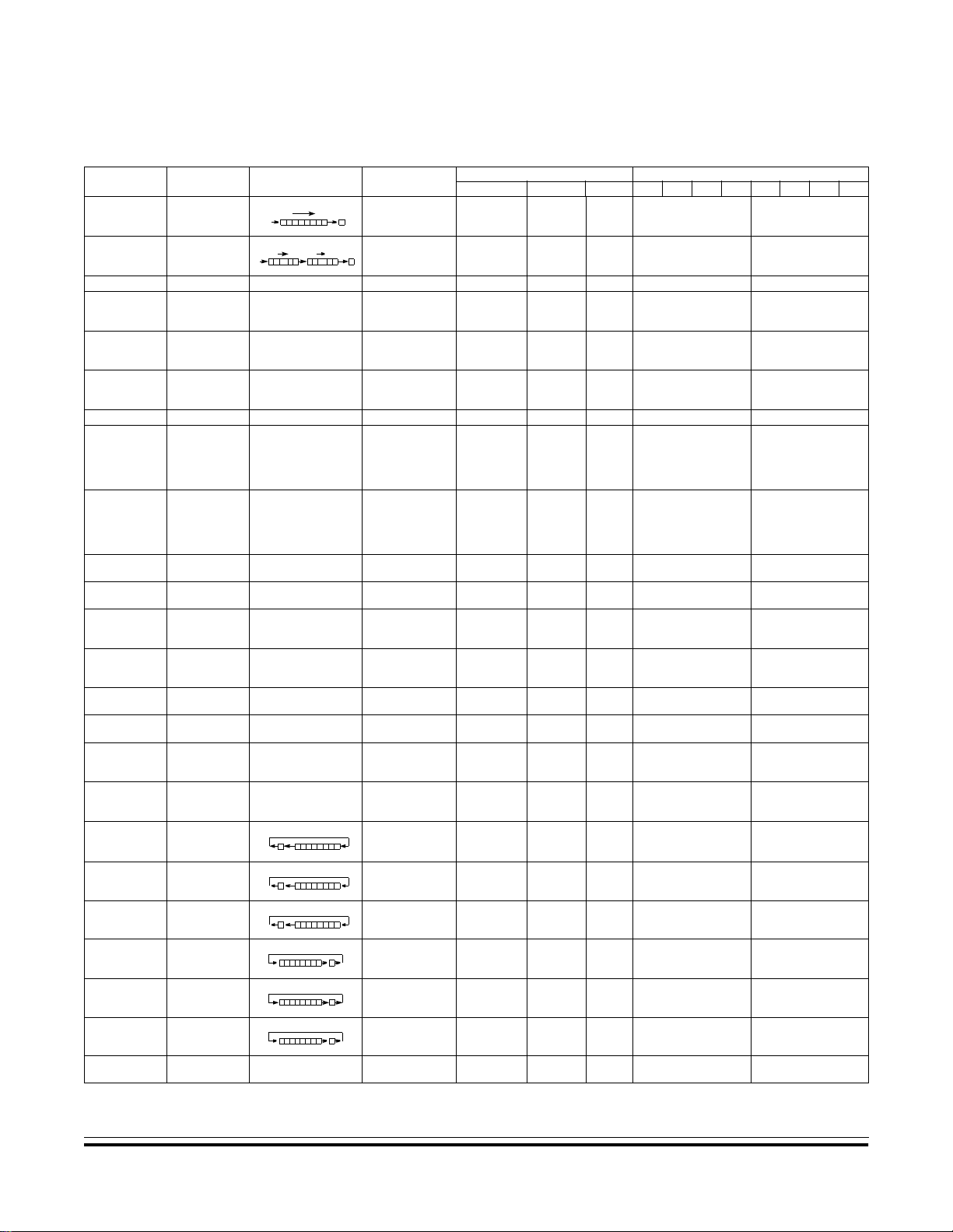

3-2 Instruction Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4-1 Hardware Mode Select Summary. . . . . . . . . . . . . . . . . . . . . . .82

4-2 Write Access Limited Registers . . . . . . . . . . . . . . . . . . . . . . . .85

4-3 EEPROM Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

4-4 RAM Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

4-5 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

4-6 EEPROM Block Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

4-7 EEPROM Block Protect in MC68HC811E2 MCUs. . . . . . . . .100

4-8 EEPROM Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

List of Tables

5-1 COP Timer Rate Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

5-2 Reset Cause, Reset Vector, and Operating Mode . . . . . . . . .114

5-3 Highest Priority Interrupt Selection. . . . . . . . . . . . . . . . . . . . .120

5-4 Interrupt and Reset Vector Assignments . . . . . . . . . . . . . . . .121

5-5 Stacking Order on Entry to Interrupts. . . . . . . . . . . . . . . . . . .122

6-1 Input/Output Ports. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

6-2 Parallel I/O Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

7-1 Baud Rate Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

8-1 SPI Clock Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

9-1 Timer Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

9-2 Timer Control Configuration . . . . . . . . . . . . . . . . . . . . . . . . . .183

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA List of Tables 21

List of Tables

Table Title Page

9-3 Timer Output Compare Actions . . . . . . . . . . . . . . . . . . . . . . .194

9-4 Timer Prescale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197

9-5 RTI Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

9-6 Pulse Accumulator Timing . . . . . . . . . . . . . . . . . . . . . . . . . . .204

9-7 Pulse Accumulator Edge Control . . . . . . . . . . . . . . . . . . . . . .205

10-1 Converter Channel Assignments . . . . . . . . . . . . . . . . . . . . . .216

10-2 A/D Converter Channel Selection. . . . . . . . . . . . . . . . . . . . . .219

Technical Data MC68HC11E Family — Rev. 4

22 List of Tables MOTOROLA

Technical Data — M68HC11E Family

1.1 Contents

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

1.4 Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

1.2 Introduction

This documen t contains a detail ed description of the M68HC11 E series

of 8-bit microcontroller units (MCUs). These MCUs all combine the

M68HC11 centra l proce ssor un it (C PU ) with h ig h-pe rfor manc e, on- chip

peripherals.

Section 1. General Descr ip tion

The E series is comprised of many devices with various

configurations of:

• Random-access memory (RAM)

• Read-only mem ory (R OM)

• Erasable programmable read-only memory (EPROM)

• Electrically erasable programmable read-only memory

(EEPROM)

• Several low-voltage devices are also available.

With the exception of a few minor differences, the operation of all

E-series MCUs is identical. A fully static design and high-density

complementary metal-oxide semiconductor (HCMOS) fabrication

process allow the E-seri es devices to operate at frequencies fr om 3 MHz

to dc with very low power consumption.

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA General Description 23

General Description

1.3 Features

Features of the E-series devices include:

• M68HC11 CPU

• Power-saving stop and wait modes

• Low-voltage devices available (3.0–5.5 Vdc)

• 0, 256, 512, or 768 bytes of on-chip RAM, data retained during

standby

• 0, 12, or 20 Kbytes of on-chip ROM or EPROM

• 0, 512, or 2048 bytes of on-chip EEPROM with block protect for

security

• 2048 bytes of EEP ROM with selectable base address in the

MC68HC811E2

• Asynchronous non-return-to-zero (NRZ) serial communications

interface (SCI)

• Additional baud rates available on MC68HC(7)11E20

• Synchronous serial peripheral interface (SPI)

• 8-channel, 8-bit analog-to-digital (A/D) converter

• 16-bit timer system:

– Three input capture (IC) channels

– Four output compare (OC) channels

– One additional channel, selectable as fourth IC or fifth OC

• 8-bit pulse accumulator

• Real-time interrupt circui t

• Computer operating properly (COP) watchdog system

• 38 general-purpose input/output (I/O) pins:

– 16 bidirectional I/O pins

– 11 input-only pins

– 11 output-only pins

Technical Data MC68HC11E Family — Rev. 4

24 General Descri ptio n MOTOR OLA

1.4 Structure

General Description

Structure

• Several packaging options:

– 52-pin plastic-leaded chip carrier (PLCC)

– 52-pin windowed ceramic leaded chip carrier (CLCC)

– 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

– 64-pin quad flat pack (QFP)

– 48-pin plastic dual in- line packa ge (DI P), MC68HC81 1E2 only

– 56-pin plastic shrink dual in-line package, .070-inch lead

spacing (SDIP)

See Figure 1-1 for a functional diagram of the E-series MCUs.

Differences among devices are noted in the table accompanying

Figure 1-1.

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA General Description 25

General Description

MODA/

MODB/

LIR

V

STBY

XTAL EXTAL E IRQ XIRQ/V

PPE*

RESET

MODE CONTROL

TIMER

SYSTEM

COPPULSE ACCUMUL A TO R

OC2

OC3

OC4

PAI

OC5/IC4/OC1

PORT A

IC1

IC2

PERIODIC INTERRUPT

IC3

OSC

CLOCK LOGIC

BUS EXPANSION

ADDRESS

STROBE AND HANDSHAKE

M68HC11 CPU

ADDRESS/DATA

PARALLEL I/O

CONTROL

PORT CPORT B

INTERRUPT

LOGIC

ROM OR EPROM

(SEE TABLE)

EEPROM

(SEE TABLE)

RAM

(SEE TABLE)

SERIAL

AS

STRA

PERIPHERAL

INTERFACE

SPI

SCK

SS

CONTROL

PORT D PORT E

MOSI

MISO

R/W

STRB

SERIAL

COMMUNICATION

INTERFACE

SCI

TxD

RxD

A/D CONVERTER

V

DD

V

SS

V

RH

V

RL

PA2/IC1

PA1/IC2

PA7/PAI

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

* V

applies only to devices with EPROM/OT PR OM .

PPE

PA0/IC3

PB6/ADDR14

PB7/ADDR15

PA3/OC5/IC4/OC1

STRA/AS

PB1/ADDR9

PB5/ADDR13

PB4/ADDR12

PB0/ADDR8

PB3/ADDR11

PB2/ADDR10

PC7/ADDR7/DATA7

PC6/ADDR6/DATA6

PC5/ADDR5/DATA5

PC4/ADDR4/DATA4

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

STRB/R/W

PC1/ADDR1/DATA1

PC0/ADDR0/DATA0

DEVICE

MC68HC11E0

MC68HC11E1

MC68HC11E9

MC68HC711E9

MC68HC11E20

MC68HC711E20

PD5/SS

PD4/SCK

PD3/MOSI

RAM

512

512

512

512

768

768

256 — — 2048MC68HC811E2

PD2/MISO

PD1/TxD

PD0/RxD

ROM

—

—

12 K

—

20 K

—

PE7/AN7

PE6/AN6

EPROM

—

—

—

12 K

—

20 K

PE5/AN5

PE4/AN4

PE3/AN3

EEPROM

PE2/AN2

—

512

512

512

512

512

PE1/AN1

PE0/AN0

Figure 1-1. M68HC11 E-Series Block Diagram

Technical Data MC68HC11E Family — Rev. 4

26 General Descri ptio n MOTOR OLA

Technical Data — M68HC11E Family

2.1 Contents

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

2.3 VDD and VSS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Section 2. Pin Descriptions

2.4 RESET

2.5 Crystal Driver and External Clock Input

2.6 E-Clock Output (E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

2.7 Interrupt Request (IRQ

2.8 Non-Maskable Interrupt (XIRQ/V

2.9 MODA and MODB (MODA/LIR and MODB/V

2.10 VRL and VRH. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.11 STRA/AS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.12 STRB/R/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

2.13 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

2.13.1 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

2.13.2 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

2.13.3 Port C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

2.13.4 Port D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

2.13.5 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

(XTAL and EXTAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

). . . . . . . . . . . . . . . . . . . .36

PPE

) . . . . . . . . .37

STBY

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 27

Pin Des cr ip t io ns

2.2 Introduction

M68HC11 E-series MCUs are available packaged in:

• 52-pin plastic-leaded chip carrier (PLCC)

• 52-pin windowed ceramic leaded chip carrier (CLCC)

• 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

• 64-pin quad flat pack (QFP)

• 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

• 56-pin plastic shrink dual in-line package, .070-inch lead spacing

(SDIP)

Most pins on these MCUs serve two or more functions, as described in

the following paragraphs. Refer to Figure 2-1, Figure 2-2, Figure 2-3,

Figure 2-4, and Figure 2-5 which show the M68HC11 E-series pin

assignments for the PLCC/CLCC, QFP, TQFP, SDIP, and DIP

packages.

EXTAL

STRB/R/WESTRA/AS

7

6

5

XTAL

8

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ /V

PD0/RxD

* V

applies only to devices with EPROM/OTPROM.

PPE

PPE

IRQ

9

10

11

12

13

14

15

16

17

18

19

20

21

222324252627282930

PD1/TxD

PD2/MISO

PD3/MOSI

STBY

MODA/LIR

MODB/V

VSSVRHVRLPE7/AN7

4

312

525150

M68HC11 E SERIES

DD

V

PD5/SS

PD4/SCK

PA7/PAI/OC1

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PE3/AN3

PE6/AN648

PE2/AN2

47

49

PE5/AN546

PE1/AN1

45

PE4/AN4

44

PE0/AN0

43

PB0/ADDR8

42

PB1/ADDR9

41

PB2/ADDR10

40

PB3/ADDR11

39

PB4/ADDR12

38

PB5/ADDR13

37

PB6/ADDR14

36

PB7/ADDR15

35

PA0/IC3

34

31

33

PA2/IC132PA1/IC2

PA3/OC5/IC4/OC1

Figure 2-1. Pin Assignments for 52-Pin PLCC and CLCC

Technical Data MC68HC11E Family — Rev. 4

28 Pin Descriptions MOTOROLA

Pin Descriptions

Introduction

PA1/IC2

PA2/IC1

PA3/OC5/IC4/OC1NCNC

64

63626160595857

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

* V

PPE

1

2

NC

3

NC

NC

4

5

6

7

8

9

10

11

12

13

14

15

16

17181920212223

PE2/AN2

PE6/AN6

PE3/AN3

applies only to devices with EP ROM/OTPROM.

PA4/OC4/OC1

PA5/OC3/OC1

M68HC11 E SERIES

RL

RH

V

VSSV

V

PE7/AN7

PA6/OC2/OC1

PA7/PAI/OC1

PD5/SS

VDDPD4/SCK

55

56

26

25

24

SS

NC

STBY

MODB/V

PD3/MOSI

5352515049

54

2829303132

27

E

STRA/AS

MODA/LIR

PD2/MISO

STRB/R/W

SS

PD1/TxD

V

NC

48

PD0/RxD

47

IRQ

46

XIRQ/V

45

NC

44

RESET

43

PC7/ADDR7/DATA7

42

PC6/ADDR6/DATA6

41

PC5/ADDR5/DATA5

40

PC4/ADDR4/DATA4

39

PC3/ADDR3/DATA3

38

PC2/ADDR2/DATA2

37

PC1/ADDR1/DATA1

36

NC

35

PC0/ADDR0/DATA0

34

33

XTAL

NC

EXTAL

PPE

*

Figure 2-2. Pin Assignments for 64-Pin QFP

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 29

Pin Des cr ip t io ns

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

PA1/IC2

PA2/IC1

PA3/OC5/IC4/OC1

PA4/OC4/OC1

PA5/OC3/OC1

PA6/OC2/OC1

PA7/PAI/OC1

52

51504948474645

1

2

3

4

5

6

7

8

9

10

11

12

13

M68HC11 E SERIES

1415161718192021222423

PD5/SS

VDDPD4/SCK

44

PD3/MOSI

PD2/MISO

PD1/TxD

42

43

41

40

PD0/RxD

39

IRQ

38

XIRQ/V

37

RESET

36

PC7/ADDR7/DATA7

35

PC6/ADDR6/DATA6

34

PC5/ADDR5/DATA5

33

PC4/ADDR4/DATA4

32

PC3/ADDR3/DATA3

31

PC2/ADDR2/DATA2

30

PC1/ADDR1/DATA1

29

PC0/ADDR0/DATA0

28

27

25

XTAL

26

PPE

*

RL

SS

RH

V

V

V

PE2/AN2

PE6/AN6

PE3/AN3

PE7/AN7

* V

applies only to devic es with EPROM/OTPROM.

PPE

STBY

MODB/V

E

STRA/AS

MODA/LIR

EXTAL

STRB/R/W

Figure 2-3. Pin Assignments for 52-Pin TQFP

Technical Data MC68HC11E Family — Rev. 4

30 Pin Descriptions MOTOROLA

Pin Descriptions

Introduction

V

MODB/V

STBY

MODA/LIR

STRA/AS

STRB/R/W

EXTAL

XTAL

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ/V

PPE

IRQ

PD0/RxD

EV

SS

PD1/TxD

PD2/MISO

PD3/MOSI

PD4/SCK

PD5/SS

V

DD

V

SS

SS

1

2

3

4

E

5

6

7

8

9

10

11

12

13

14

15

M68HC11 E SERIES

16

17

18

19

20

21

22

23

24

25

26

27

28

EV

56

SS

V

RH

55

V

54

RL

PE7/AN7

53

PE3/AN3

52

PE6/AN6

51

PE2/AN2

50

PE5/AN5

49

PE1/AN1

48

PE4/AN4

47

PE0/AN0

46

PB0/ADDR8

45

PB1/ADDR9

44

PB2/ADDR10

43

PB3/ADDR11

42

PB4/ADDR12

41

PB5/ADDR13

40

PB6/ADDR14

39

PB7/ADDR15

38

PA0/IC3

37

PA1/IC2

36

PA2/IC1

35

PA3/OC5/IC4/OC1

34

PA4/OC4/OC1

33

PA5/OC3/OC1

32

PA6/OC2/OC1

31

PA7/PAI/OC1

30

EV

29

DD

* V

applies on ly to devices with EPROM/OTP ROM.

PPE

Figure 2-4. Pin Assignments for 56-Pin SDIP

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 31

Pin Des cr ip t io ns

PA7/PAI/OC1

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PA3/OC5/IC4/OC1

PA2/IC1

PA1/IC2

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE1/AN1

PE2/AN2

PE3/AN3

V

V

RH

V

SS

MODB/V

STBY

V

1

2

3

4

5

6

7

8

9

10

11

MC68HC811E2

12

13

14

15

16

17

18

19

20

21

RL

22

23

24

48

DD

PD5/SS

47

PD4/SCK46

PD3/MOSI

45

PD2/MISO44

PD1/TxD

43

PD0/RxD42

IRQ

41

40

XIRQ

RESET

39

38

PC7/ADDR7/DATA7

37

PC6/ADDR6/DATA6

36

PC5/ADDR5/DATA5

35

PC4/ADDR4/DATA4

34

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

33

PC1/ADDR1/DATA1

32

PC0/ADDR0/DATA0

31

30

XTAL

29

EXTAL

28

STRB/R/W

E27

STRA/AS26

MODA/LIR

25

Figure 2-5. Pin Assignments for 48-Pin DIP (MC68HC811E2)

2.3 VDD and VSS

Power is supplied to the MCU through VDD and VSS. VDD is the power

supply, VSS is ground. The MC U operate s from a s ingle 5- volt (nomi nal)

power supply. Low-voltage devices in the E series operate at

3.0–5.5 volts.

Very fast signal tra nsitions occur on the MCU pins. The short r ise and fall

times place high, short duration current demands on the power supply.

To prevent nois e problems, pro vide good power sup ply bypassing at t he

MCU. Also, use bypass capacitors that have good

Technical Data MC68HC11E Family — Rev. 4

32 Pin Descriptions MOTOROLA

Pin Descriptions

VDD and VSS

high-frequen cy characteristics and situate them as close to the MCU as

possible. Bypa ss requirements var y, depending on h ow heavily the M CU

pins are loaded.

V

DD

2

IN

RESET

MC34(0/1)64

GND

3

V

DD

4.7 kΩ

1

TO RESET

OF M68HC11

Figure 2-6. External Reset Circuit

V

DD

IN

RESET

V

DD

MC34064

GND

V

DD

4.7 kΩ

TO RESET

OF M68HC11

MANUAL

RESET SWITCH

4.7 kΩ

OPTIONAL POWER-ON DELAY AND MANUAL RESET SWITCH

4.7 kΩ

1.0 µF

IN

RESET

MC34164

GND

Figure 2-7. External Reset Circuit with Delay

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 33

Pin Des cr ip t io ns

2.4 RESET

CAUTION: Do not connect an external resistor capacitor (RC) power-up delay

A bidirectional control signal, RESET, acts as an input to initialize the

MCU to a known startup state. It also acts as an open-drain output to

indicate that an internal failure has been detected in either the clock

monitor or computer operating properly (COP) watchdog circuit. The

CPU distinguishes between internal and external reset conditions by

sensing whether the reset pin rises to a logic 1 in less than two E-clock

cycles after a reset has occurred. See Figure 2-6 and Figure 2-7.

circuit to the reset pin of M68HC11 devices because the circuit charge

time constant can cau se t he devi ce to misinter pre t th e type of reset that

occurred.

Because the CPU is not able to fetch and execute instructions properly

when V

be controlled. A low-voltage inhibit (LVI) circuit is required primarily for

protection of EEPROM contents. However, since the configuration

register (CONFIG) value is read from the EEPROM, protection is

required even if the EEPROM array is not being used.

falls below the minimum operating voltage level, reset must

DD

Presently, there are several economi cal way s to solve this pro blem. For

example, two good external components for LVI reset are:

1. The Seiko S0854HN (or other S805 series devices):

— Extremely low power (2 µA)

— TO-92 package

— Limited temperature range, –20°C to +70°C

— Av ailabl e in various trip-poi nt voltage rang es

2. The Motorola MC34064:

— TO-92 or SO-8 package

— Draws about 300 µA

— Temperature range –40°C to 85°C

— Well controlled trip point

— Inexpensive

Refer to Section 5. Resets and Interrupts for further information.

Technical Data MC68HC11E Family — Rev. 4

34 Pin Descriptions MOTOROLA

Crystal Driver and External Clock Input (XTAL and EXTAL)

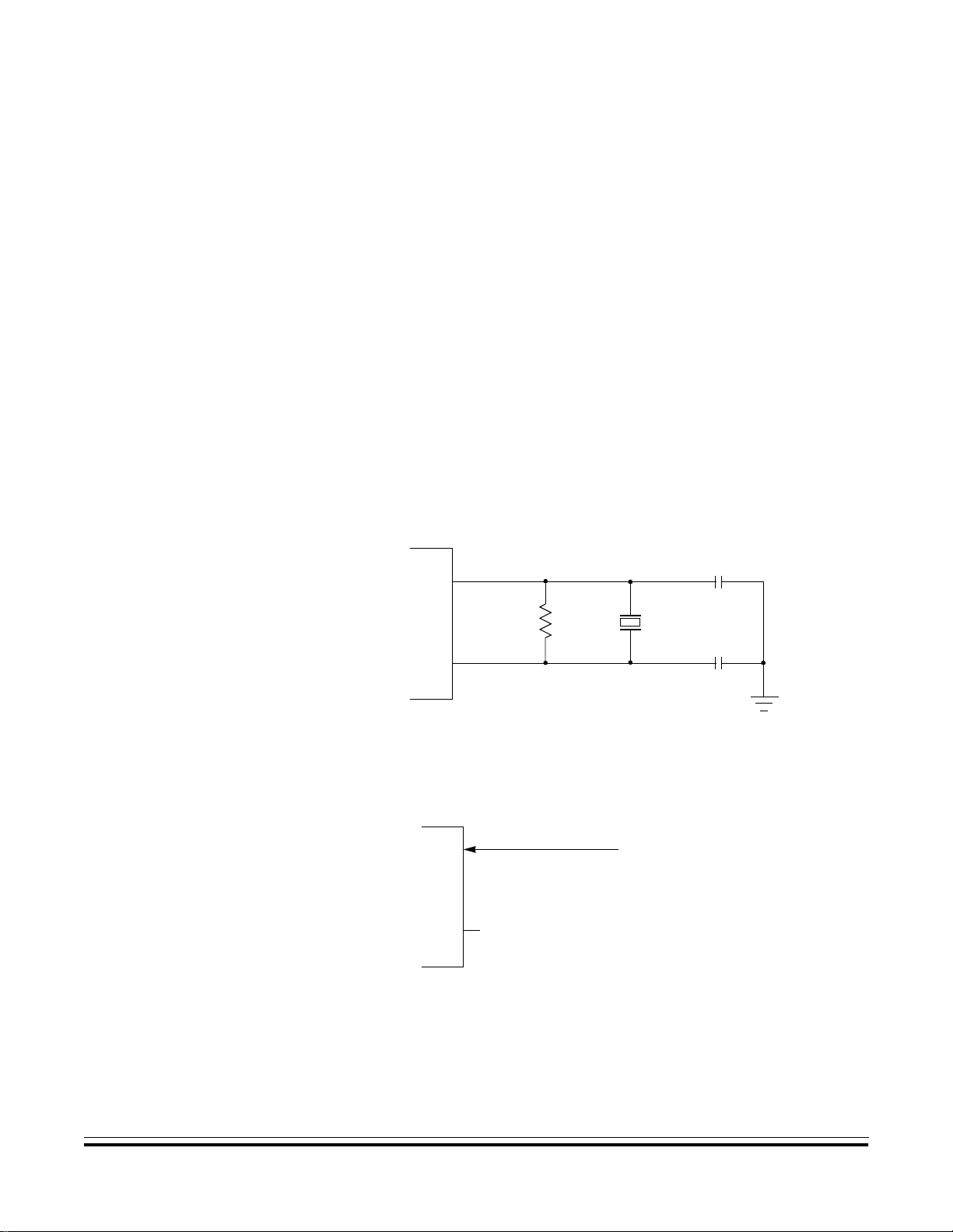

2.5 Crystal Driver and External Clock Input (XTAL and EXTAL)

These two pins provide the interface for either a crystal or a CMOScompatible clock to control the internal clock generator circuitry. The

frequency applied to these pins is four times higher than the desired

E-clock rate.

The XTAL pin must be left unterminated when an external CMOScompatible clock input i s connected to the EXTAL pin. T he XTAL output

is normally intended to drive only a crystal.

CAUTION: In all cases, use caution around the oscillator pins. Load capacitances

shown in the oscillator circuit are specified by the crystal manufacturer

and should include all stray layout capacitances.

Refer to Figure 2-8 and Figure 2-9.

Pin Descriptions

C

L

C

L

MCU

EXTAL

XTAL

10 MΩ

4 x E

CRYSTAL

Figure 2-8. Common Parallel Resonant

Crystal Connections

4 x E

CMOS-COMPATIBLE

MCU

EXTAL

XTAL

EXTERNAL OSCILLATOR

NC

Figure 2-9. External Oscillator Connections

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 35

Pin Des cr ip t io ns

2.6 E-Clock Output (E)

E is the o utput connection for the internally gen erated E clock. T he signal

from E is used as a ti ming reference. The fr equency of the E-clock out put

is one fourth that of the input frequency at the XTAL and EXTAL pins.

When E-clock outpu t is low , an intern al pr ocess is taking place. When it

is high, data is being accessed.

All clocks, including the E clock, are halted when the MCU is in stop

mode. To reduce R FI emissions, the E-clock output of most E-series

devices can be disabled while operating in single-chip modes.

The E-clock signal is always enabled on the MC68HC811E2.

2.7 Interrupt Request (IRQ)

The IRQ input provides a means of applying asynchronous interrupt

requests to the MCU. Either negative edge-sensitive triggering or

level-sensitive triggering is program selectable (OPTION register). IRQ

is always configured to level-sensitive triggering at reset. When using

IRQ in a level-sensitive wired-OR configuration, connect an external

pullup resistor, typically 4.7 kΩ, to VDD.

2.8 Non-Maskable Interrupt (XIRQ/V

The XIRQ input provides a means of requesting a non-maskable

interrupt after reset initialization. During reset, the X bit in the condition

code register (CCR) is set and any interrupt is masked until MCU

software enable s it. Becau s e the XIR Q input is level- sensitiv e, it can b e

connected to a multiple -source wired-OR network with an external pullup

resistor to VDD. XIRQ is often used as a power loss detect interrupt.

Whenever XIRQ or IRQ is used with multiple interrupt sources each

source must drive the interr upt input with an open -drain type of dri ver to

avoid contention between outputs.

PPE

)

NOTE: IRQ must be configured for level -sensitive operation if the re is more than

one source of IRQ interrupt.

Technical Data MC68HC11E Family — Rev. 4

36 Pin Descriptions MOTOROLA

Pin Descriptions

MODA and MODB (MODA/LIR and MODB/VSTBY)

There should be a single pullup resistor near the MCU interrupt input pin

(typically 4.7 kΩ). There must also be an interlock mechanism at each

interrupt source so that the source holds the interrupt line low until the

MCU recognizes and acknowledg es the interrupt request. If one or more

interrupt sources are still p ending aft er the MCU se rvices a r equest , the

interrupt line will still be held low and the MCU will be interrupted again

as soon as the interrupt mask bit in the MCU is cleared (normally upon

return from an interrupt). Refer to Section 5. Resets and Interrupts.

V

is the input for the 12-volt nominal programming voltage required

PPE

for EPROM/OTPROM programming. On devices without

EPROM/OTPROM, this pin is only an XIRQ

input.

2.9 MODA and MODB (MODA/LIR and MODB/V

During reset, MODA and MODB select one of the four oper ating modes:

• Single-chip mode

• Expanded mode

• Test m ode

• Bootstrap mode

Refer to Section 4. Operating Modes and On-Chip Memory.

After the ope rating mode h as been sel ected, the load instruction regi ster

(LIR) pin provides an open-drain output to indicate that execution of an

instruction has begun. A series of E-clock cycles occurs during

execution of each instruction. The LIR signal goes low during the first

E-clock cycle of each instr uction (opcode fe tch). This outp ut is provide d

for assistance in program debugging.

The V

power. When the voltage on this pin is more than one MOS threshold

(about 0.7 volts) above th e VDD voltage, the internal R AM and part o f the

reset logic are powered from this signal rather than the VDD input. This

allows RAM contents to be retained without VDD power applied to the

MCU. Reset must be driven lo w before VDD is removed and must remain

low until VDD has been restored to a valid level.

pin is used to input random-access memory (R AM) standb y

STBY

STBY

)

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 37

Pin Des cr ip t io ns

2.10 V

and VRH

RL

2.11 STRA/AS

These two inputs pro vide the reference volta ges for the analog-to- digital

(A/D) converter ci rcuitry:

• VRL is the low reference, typically 0 Vdc.

• VRH is the high reference.

For proper A/D converter operation:

• VRH should be at least 3 Vdc greater than VRL.

• VRL and VRH should be between VSS and VDD.

The strobe A (ST RA) and addre ss strobe (AS) pin p erforms eit her of two

separate functions, depending on the operating mode:

• In single-chip mode, STRA performs an input handshake (strobe

input) function.

2.12 STRB/R/W

• In the expanded multiplexed mode, AS provides an address

strobe function.

AS can be used to demultiplex the address and data signals at port C.

Refer to Section 4. Operating Modes and On-Chip Memory.

The strobe B (STRB) and read/write (R/W) pin act as either an output

strobe or as a data bus direction indicator, depending on the operating

mode.

In single-chip operating mode, STRB acts as a programmab le strobe for

handshake with other parallel devices. Refer to Section 6. Parallel

Input/Output (I/O) Ports for further information.

In expanded multiplexed operating mode, R/W is used to indicate the

direction of transfers on the external data bus. A low on the R/W pin

indicates data is bei ng written to the externa l data bus. A high on this pin

Technical Data MC68HC11E Family — Rev. 4

38 Pin Descriptions MOTOROLA

2.13 Port Signals

Pin Descriptions

Port Signals

indicates that a read cycle is in progress. R/W stays low during

consecutive data bus write cycles, such as a double-byte store. It is

possible for data to be driven out o f port C, if inte rnal r ead visibility (IRV)

is enabled and an internal address is read, even though R/W is in a

high-impedance state. Refer to Section 4. Operating Modes and

On-Chip Memory for more information about IRVNE (internal read

visibility not E).

Port pins have different functions in different operating modes. Pin

functions for port A, port D, and port E are independent of operating

modes. Port B and port C, however, are affected by operating mode.

Port B provides eight general-purpose output signals in single-chip

operating modes. When the microcontroller is in expanded multiplexed

operating mode, port B pins are the eight high-order address lines.

2.13.1 Port A

Port C provides eight general-purpose input/output signals when the

MCU is in t he single-chip operating mod e. When the microcontroll er is in

the expanded multiplexed ope rating mode, por t C pins are a multi plexed

address/data bus.

Refer to Table 2-1 for a functional description of the 40 port signals

within different operating modes. Terminate unused inputs and

input/output (I/O) pins configured as inputs high or low.

In all operating modes, port A can be configured for three timer input

capture (IC) functions a nd four timer outp ut compar e (OC) f unctions. An

additional pin can be configured as either the fourth IC or the fifth OC.

Any port A pin tha t is not curr ently bei ng use d for a timer function can be

used as either a general-purpose input or output line. Only port A pins

PA7 and PA3 have an associated data direction control bit that allows

the pin to be selectively configured as input or output. Bits DDRA7 and

DDRA3 located in PACTL register control data direction for PA7 and

PA3, respective ly. All other port A pins are fixed as either input o r output.

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 39

Pin Des cr ip t io ns

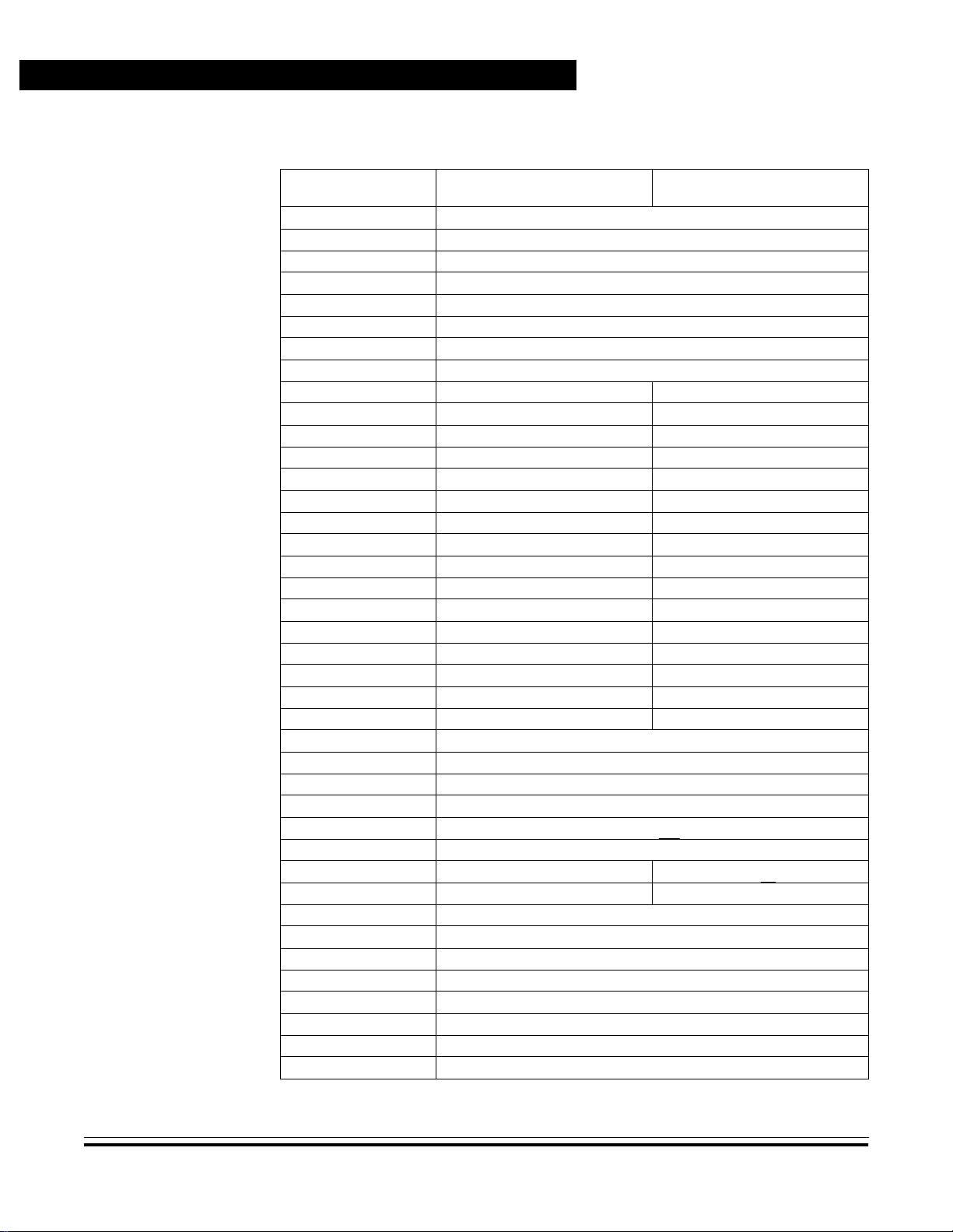

Table 2-1. Port Sig na l Functions

Port/Bit

PA0 PA0/IC3

PA1 PA1/IC2

PA2 PA2/IC1

PA3 PA3/OC5/IC4/OC1

PA4 PA4/OC4/OC1

PA5 PA5/OC3/OC1

PA6 PA6/OC2/OC1

PA7 PA7/PAI/OC1

PB0 PB0 ADDR8

PB1 PB1 ADDR9

PB2 PB2 ADDR10

PB3 PB3 ADDR11

PB4 PB4 ADDR12

PB5 PB5 ADDR13

PB6 PB6 ADDR14

PB7 PB7 ADDR15

PC0 PC0 ADDR0/DATA0

PC1 PC1 ADDR1/DATA1

PC2 PC2 ADDR2/DATA2

PC3 PC3 ADDR3/DATA3

PC4 PC4 ADDR4/DATA4

PC5 PC5 ADDR5/DATA5

PC6 PC6 ADDR6/DATA6

PC7 PC7 ADDR7/DATA7

PD0 PD0/RxD

PD1 PD1/TxD

PD2 PD2/MISO

PD3 PD3/MOSI

PD4 PD4/SCK

PD5 PD5/SS

— STRA AS

— STRB R/W

PE0 PE0/AN0

PE1 PE1/AN1

PE2 PE3/AN2

PE3 PE3/AN3

PE4 PE4/AN4

PE5 PE5/AN5

PE6 PE6/AN6

PE7 PE7/AN7

Singl e-Chip and

Boots t rap Modes

Expanded and

Test Modes

Technical Data MC68HC11E Family — Rev. 4

40 Pin Descriptions MOTOROLA

Pin Descriptions

Port Signals

PA7 can function as genera l-purpose I /O or as tim er output compare fo r

OC1. PA7 is also the input to the pulse accumulator, even while

functioning as a general-purpose I/O or an OC1 output.

PA6–PA4 serve as either general-p urpose outputs, timer input captu res,

or timer output comp are 2–4. In a ddition, PA6–PA4 can be controlled by

OC1.

PA3 can be a general-purpose I/O pin or a timer IC/OC pin. Timer

functions associated with this pin incl ude OC1 and IC4/OC5. I C4/OC5 is

software selectable as either a fourth input capture or a fifth output

compare. PA3 can al so be configu red to allow OC1 edges to trigger IC 4

captures.

PA2–PA0 serve as general-purpose inputs or as IC1–IC3.

PORTA can be read at any time. Reads of pins configured as inputs

return the logic level present on the pin. Pins configured as outputs

return the logic level present at the pin driver input. If written, PORTA

stores the data in an inter nal latch, bits 7 and 3. I t drives the pin s only if

they are confi gur ed a s out puts. Wri tes to POR TA d o no t chan ge the p i n

state when pins are configured for timer input captures or output

compares. Refer to Section 6. Parallel Input/Output (I/O) Ports.

2.13.2 Port B

During single -chip operat ing modes, al l port B pins are gen eral-purp ose

output pins. During MCU reads of this port, the level sensed at the input

side of the port B ou tput drivers is read. Por t B can also be used in simple

strobed output mode. In thi s mode, an output pulse appear s at the STRB

signal each time data is written to port B.

In expanded multiplexed operating modes, all of the port B pins act as

high order ad dress outp ut sign als. Du ring each MCU cycle, b its 15–8 of

the address bus are output on the PB7–PB0 pins. The PORTB register

is treated as an external address in expanded modes.

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 41

Pin Des cr ip t io ns

2.13.3 Port C

While in single-chip operating modes, all port C pins are

general-pur pose I/O pins. Port C inputs can be latched into an alternate

PORTCL register by providing an input transition to the STRA signal.

Port C can also be used in full handshake modes of parall el I/O where

the STRA input and STRB output act as handshake control lines.

When in exp ande d m ul tiplexe d m odes, a ll por t C pi n s a re config ured as

multiplexed address/data signals. During the address portion of each

MCU cycle, bits 7–0 of the address are output on the PC7–PC0 pins.

During the data portion of each MCU cycle (E high), PC7–PC0 are

bidirectional data signals, DATA7–DATA0. The direction of data at the

port C pins is indicated by the R/W

signal.

The CWOM con trol bit in the PIOC register disables th e port C P-channel

output driver. CWOM simultaneously affects all eight bits of port C.

Because the N-channel driver is not aff ected by CWOM , setting CWOM

causes port C to become an open-drain type output port suitable for

wired-OR operation.

In wired-OR mode:

• When a port C bit is at logic level 0, it is driven low by the

N-channel driver .

• When a port C bit is at logic level 1, the associated pin has

high-impedance, as neither the N-channel nor the P-channel

devices are active.

It is customary to have an exter nal pullup resistor on lines tha t are driven

by open-drain devices. Port C can only be configured for wired-OR

operation when the MCU is in single-chip mode. Refer to Section 6.

Parallel Input/Ou tput (I/O) Ports for addi tional information about port C

functions.

Technical Data MC68HC11E Family — Rev. 4

42 Pin Descriptions MOTOROLA

2.13.4 Port D

Pin Descriptions

Port Signals

Pins PD5–PD0 can be used for general-pur pose I/O signals. Th ese pins

alternately serve as the seri al com munica tion i nterf ace (SC I) and ser ial

peripheral interfac e (SPI) signals when those subsystems are enabled .

• PD0 is the recei ve data input (RxD) signal for the SCI.

• PD1 is the transmit data output (TxD) signal for the SCI.

• PD5–PD2 are dedicated to the SPI:

– PD2 is the master in/slave out (MISO) signal.

– PD3 is the master out/slave in (MOSI) signal.

– PD4 is the serial clock (SCK) signal.

2.13.5 Port E

CAUTION: If high accuracy is required for A/D conversions, avoid reading port E

– PD5 is the slave select (SS

) input.

Use port E for general-purpose or analog-to-digital (A/D) inputs.

during sampling, as small disturbances can red uce th e accur acy of t hat

result.

MC68HC11E Family — Rev. 4 Technical Data

MOTOROLA Pin Descriptions 43

Pin Des cr ip t io ns

Technical Data MC68HC11E Family — Rev. 4

44 Pin Descriptions MOTOROLA

Technical Data — M68HC11E Family

Section 3. Central Processor Unit (CPU)

3.1 Contents

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3.1 Accumulators A, B, and D . . . . . . . . . . . . . . . . . . . . . . . . . .4 7

3.3.2 Index Register X (IX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.3 Index Register Y (IY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.3.5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

3.3.6 Condition Code Register (CCR). . . . . . . . . . . . . . . . . . . . . .51

3.3.6.1 Carry/Borrow (C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.2 Overflow (V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.3 Zero (Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.3.6.4 Negative (N). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.5 Interrupt Mask (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.6 Half Carry (H). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.7 X Interrupt Mask (X). . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

3.3.6.8 STOP Disable (S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53