MOTOROLA MC33157DW Datasheet

MC33157

Half Bridge Controller and

Driver for Industrial

Linear Tubes

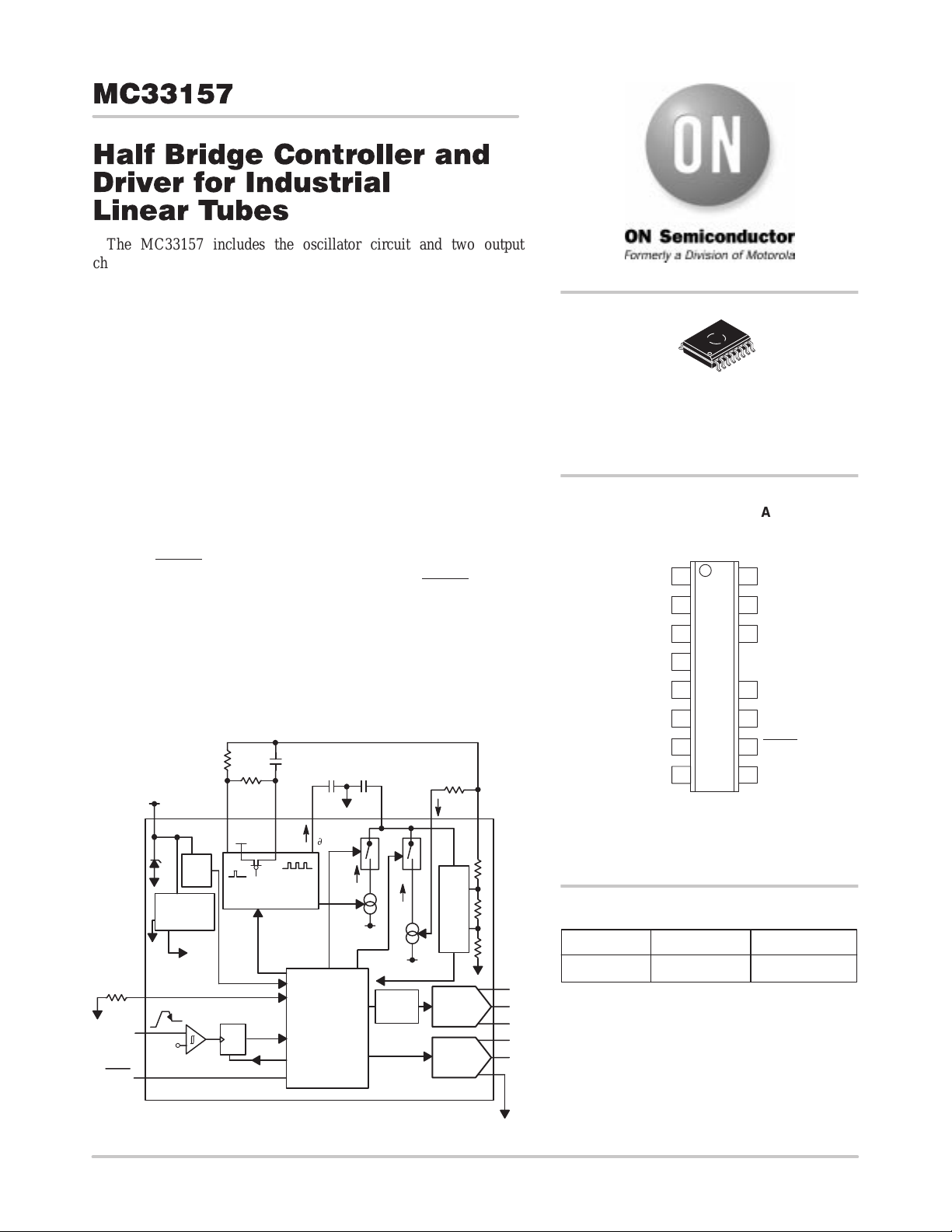

The MC33157 includes the oscillator circuit and two output

channels to control a half–bridge power stage.

One of the channels is ground–referenced. The second one is

floating to provide a bootstrap operation for the high side switch.

Dedicated Driver for Industrial Linear T ubes

• Main oscillator is current controlled, making it easy to set up by a

single external resistor . On top of that, such a feature is useful to

implement a dimming function by frequency shift.

• Filament pre–heating time control built–in.

• The strike sequence is controllable by external passive components,

the resonnant frequency being independently adjustable. This

frequency can be made different from the pre–heating and the steady

state values. A frequency sweep between two defined values makes

this IC suitable for any series resonnant topologies.

• Dedicated internal comparator provides an easy lamp strike detection

implementation.

• Digital RESET pin provides a fast reset of the system (less than 10µs).

Both output MOSFET are set to “OFF” state when RESET is zero.

• Adjustable dead time makes the product suitable for any snubber

capacitor and size of MOSFET used as power switches.

• Designed to be used with standard setting capacitors ≤ 470nF.

• A voltage reference, derived from the internal bandgap, is provided

for external usage. This voltage is 100% trimmed at probe level

yielding a 2% tolerance over the temperature range.

C

PH

SWEEP

C

PH

Iph

ē

Iph

Ifstrike

ENABLE

Dead Time

CONTROL LOGIC

Strike Detection

Clear

INHIBIT

+Vref

C

OP

SHIFTER

Iop

LEVEL

+Vref

R

OP

ICO

COMPARATOR

HIGH SIDE

BUFFER

LOW SIDE

BUFFER

+Vref

2

R

R

R

16

VHS

15

VHO

14

VOUT

13

NC

12

VLO

11

GND

DT adjust

Strike

Detection

RESET

R

ENDSWP

U

VLO

+Vref

(+7 V)

R

+Vref

PREHEAT

& STRIKE CONTROL

Latch

Q

C

V

DD

145367

15 V

BAND GAP

REFERENCE

8

9

Vth

10

http://onsemi.com

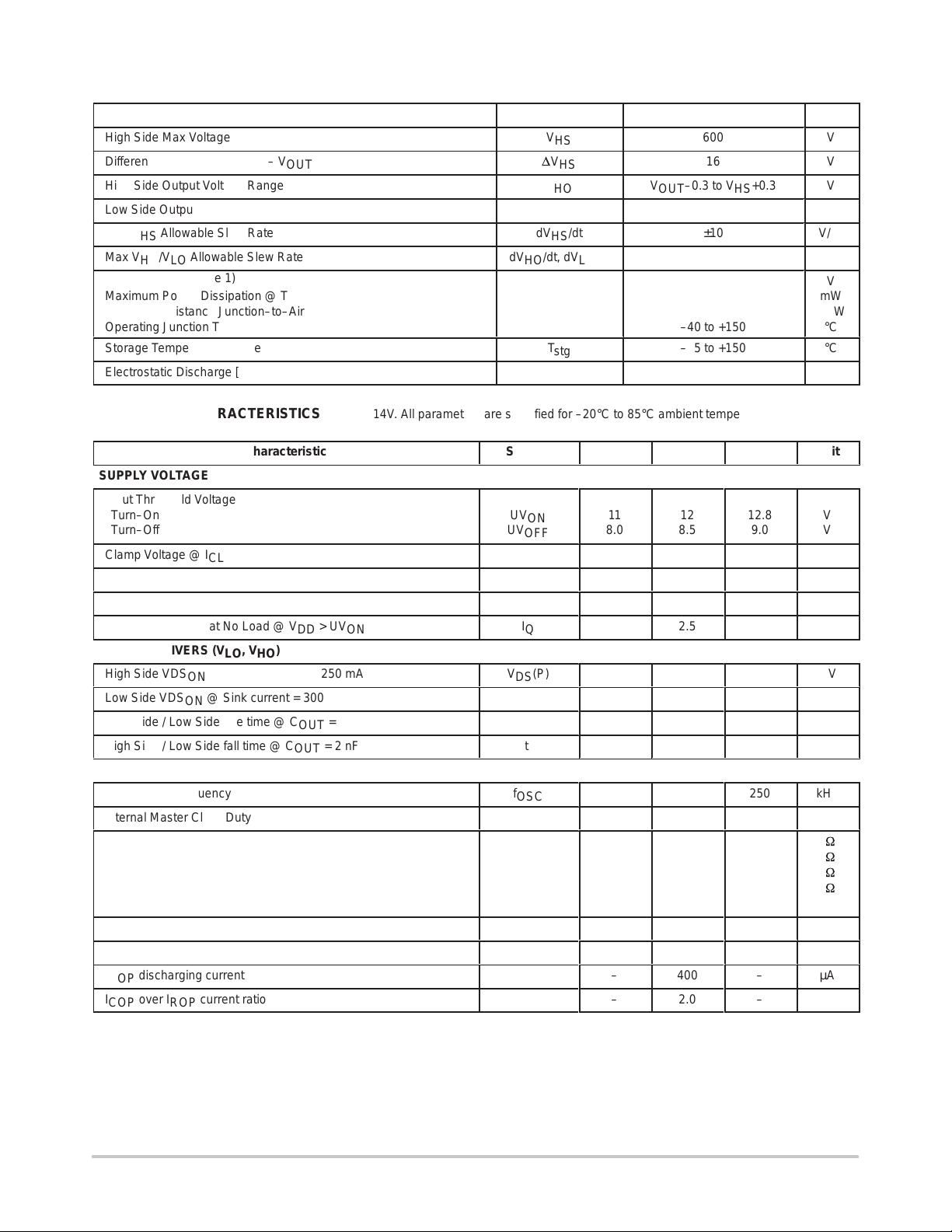

16

1

SO–16L

DW SUFFIX

CASE 751G

PIN CONNECTIONS AND

MARKING DIAGRAM

116

V

DD

2

+V

ref

C

3

PH

R

4

PH

C

SWEEP

512

MC33157DW

6

C

OP

ICO

7

DTA SD

AWL = Manufacturing Code

YYWW = Date Code

(Top View)

15

14

AWLYYWW

11

10

98

V

HS

V

HO

V

OUT

V

LO

GND

RESET

ORDERING INFORMATION

Device Package Shipping

MC33157DW Plastic SO–16L 47 Units / Rail

Semiconductor Components Industries, LLC, 1999

November, 1999 – Rev. 1

1 Publication Order Number:

MC33157/D

MC33157

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

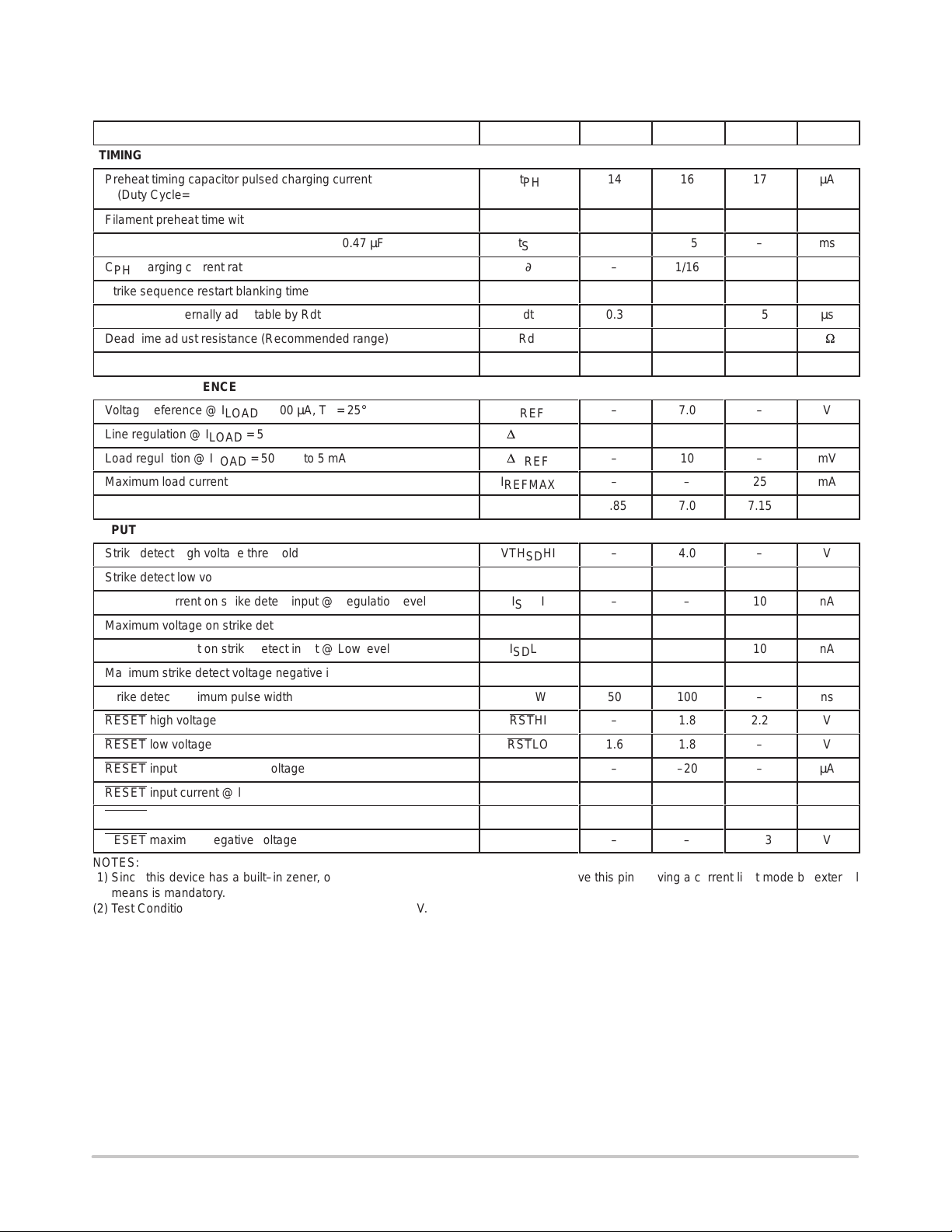

MAXIMUM RATINGS

Rating Symbol Value Unit

High Side Max Voltage

Differential Max Voltage VHS – V

High Side Output Voltage Range

Low Side Output Voltage Range

Max VHS Allowable Slew Rate

Max VHO/VLO Allowable Slew Rate

Supply Voltage

Maximum Power Dissipation @ TA = 50°C

ББББББББББББББББ

Thermal Resistance Junction–to–Air

Operating Junction Temperature

ББББББББББББББББ

(Note 1)

Storage Temperature Range

Electrostatic Discharge [HBMI]

OUT

V

HS

D

V

HS

V

HO

V

LO

dVHS/dt

dVHO/dt, dVLO/dt

V

DD

P

БББББ

БББББ

D

R

θJA

T

J

T

stg

ESD

600

16

V

–0.3 to VHS+0.3

OUT

–0.3 to +16

±10

±10

16

ББББББ

ББББББ

600

140

–40 to +150

–65 to +150

2.0

V/ns

V/ns

mW

Á

°C/W

Á

V

V

V

V

V

°C

°C

kV

ELECTRICAL CHARACTERISTICS (V

= 14V . All parameters are specified for –20 °C to 85°C ambient temperature

DD

unless otherwise noted.)

Characteristic

SUPPLY VOLTAGE

Input Threshold Voltage

Turn–On

ББББББББББББББББ

Turn–Off

Clamp Voltage @ I

Supply Current

(Note 2)

Standby Current at No Load @ VDD < UV

Quiescent Current at No Load @ VDD > UV

CLAMP

= 10 mA

OFF

ON

OUTPUT DRIVERS (VLO, VHO)

High Side VDSON @ Source current = 250 mA

Low Side VDSON @ Sink current = 300 mA

High Side / Low Side rise time @ C

High Side / Low Side fall time @ C

OUT

OUT

= 2 nF

= 2 nF

OSCILLATOR

Output Max Frequency

Internal Master Clock Duty Cycle

System operation programming recommended values

ББББББББББББББББ

ББББББББББББББББ

ББББББББББББББББ

V

High threshold

COP

V

Low threshold

COP

I

discharging current

COP

I

COP

over I

current ratio

ROP

Symbol Min Typ Max Unit

UV

ON

ÁÁÁ

UV

OFF

V

CLAMP

I

S

I

STDBY

I

Q

VDS(P)

VDS(N)

t

r

t

f

f

OSC

DC

R

OP

ÁÁÁ

R

PH

R

ENDSWEEP

ÁÁÁ

R

DTA

ÁÁÁ

C

OP

11

ÁÁ

8.0

15

–

–

–

68

ÁÁ

68

68

ÁÁ

10

ÁÁ

100

–

–

–

–

12

ÁÁ

8.5

16

12

1.5

2.5

880

880

40

35

50

ÁÁ

ÁÁ

ÁÁ

4.2

2.8

400

2.0

12.8

ÁÁ

9.0

16.5

1500

1500

250

–

560

ÁÁ

560

2200

ÁÁ

250

ÁÁ

560

–

–

–

–

Á

mA

mA

mA

mV

mV

ns

ns

kHz

%

k

Á

k

k

Á

k

Á

pF

µA

V

V

V

W

W

W

W

V

V

http://onsemi.com

2

MC33157

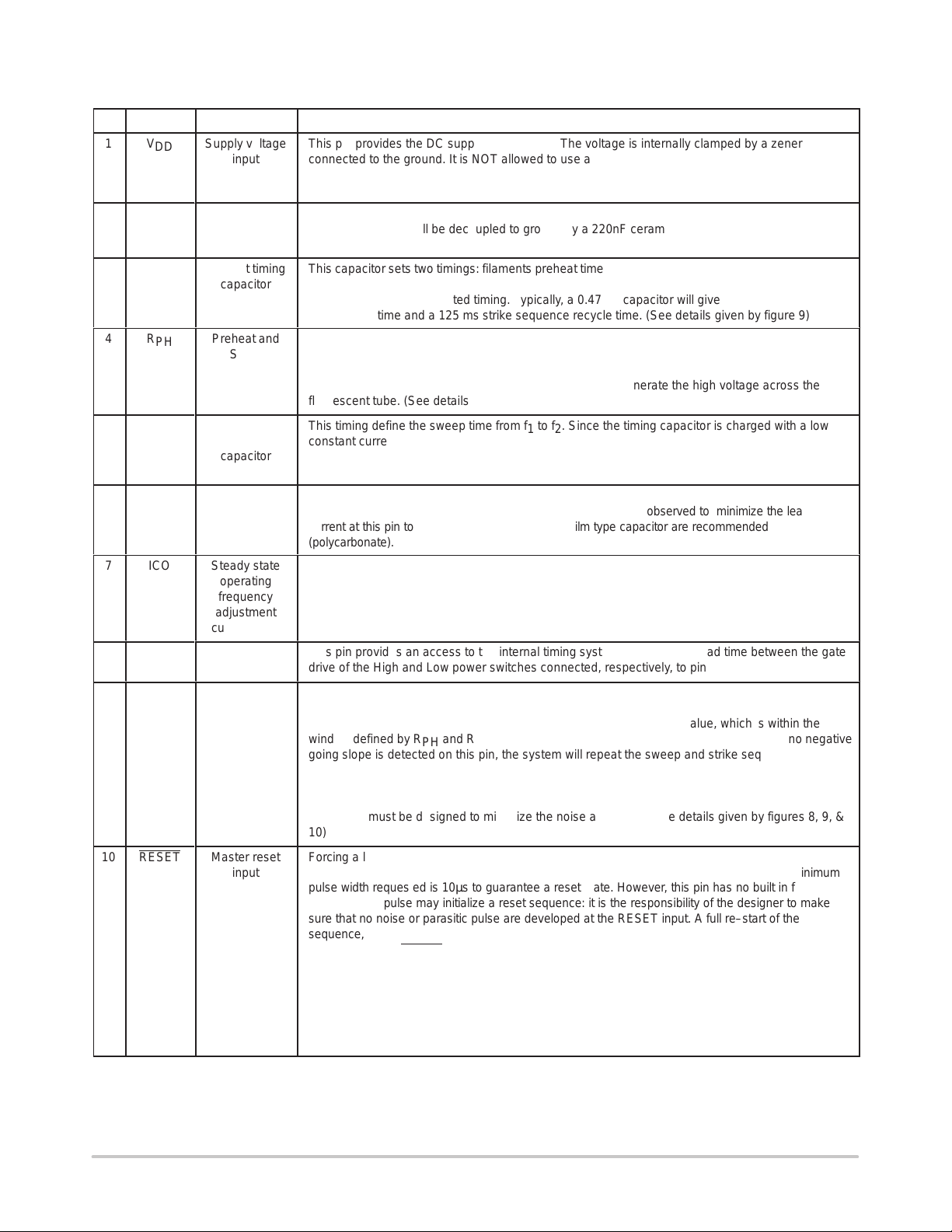

ELECTRICAL CHARACTERISTICS (continued) (V

unless otherwise noted.)

Characteristic UnitMaxTypMinSymbol

TIMING

Preheat timing capacitor pulsed charging current

(Duty Cycle=1/16)

Filament preheat time with CPH = 0.47 µF

Strike sequence recycling time with CPH = 0.47 µF

CPH charging current ratio

Strike sequence restart blanking time with CPH = 470nF

Dead time: externally adjustable by Rdt

Dead time adjust resistance (Recommended range)

Dead time tolerance

VOLTAGE REFERENCE

Voltage reference @ I

Line regulation @ I

Load regulation @ I

Maximum load current

Total V

REF

INPUT

Strike detect high voltage threshold

Strike detect low voltage threshold

Maximum current on strike detect input @ Regulation level ISDHI – – 10 nA

Maximum voltage on strike detect @ Regulation level VSDHI – – 7.0 V

Maximum current on strike detect input @ Low level ISDLO – – 10 nA

Maximum strike detect voltage negative input VSDNEG – – –0.3 V

Strike detect minimum pulse width

RESET high voltage

RESET low voltage

RESET input current @ high voltage

RESET input current @ low voltage

RESET maximum voltage

RESET maximum negative voltage

NOTES:

(1) Since this device has a built–in zener, one cannot use a low impedance supply to drive this pin. Having a current limit mode by external

means is mandatory.

(2) Test Conditions: C

LOAD

variation over Line, Temperature, Load

OUT

= 500 µA, TJ = 25°C

LOAD

= 500 µA, TJ = 25°C

= 500 µA to 5 mA

LOAD

= 2.2 nF, f = 100 kHz, VDD = 15V.

= 14V . All parameters are specified for –20 °C to 85°C ambient temperature

DD

It

PH

t

PH

t

SK

∂

t

bk

dt

Rdt

dt

Tol

V

REF

D

V

REF

D

V

REF

I

REFMAX

V

REF

VTHSDHI

VTHSDLO

SDPW

RSTHI

RSTLO

14

–

–

–

–

0.3

10

–

–

–

–

6.85

–

–

50

–

1.6

–

–

–

–

16

2.0

125

1/16

10

–

–

±10

7.0

10

10

–

7.0

4.0

3.75

100

1.8

1.8

–20

–20

–

–

17

–

–

–

–

2.5

220

–

–

–

25

7.15

–

–

–

2.2

–

–

–

7.0

–0.3

µA

s

ms

ms

µs

k

%

V

mV

mV

mA

V

V

V

ns

V

V

µA

µA

V

V

W

http://onsemi.com

3

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

MC33157

PIN FUNCTION DESCRIPTION

Pin Symbol Function Description

1

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

Á

10

Á

Á

Á

Á

Á

Á

Á

Á

V

DD

ÁÁ

ÁÁ

2

+V

ÁÁ

3

C

PH

ÁÁ

ÁÁ

4

R

PH

ÁÁ

ÁÁ

ÁÁ

5

C

SWEEP

ÁÁ

ÁÁ

6

C

OP

ÁÁ

ÁÁ

7

ICO

ÁÁ

ÁÁ

8

DTA

ÁÁ

9

SD

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

RESET

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ÁÁ

ref

Supply voltage

input

ÁÁÁ

ÁÁÁ

Voltage

reference

ÁÁÁ

output

Preheat timing

ÁÁÁ

capacitor

ÁÁÁ

Preheat and

ÁÁÁ

Strike

frequencies

ÁÁÁ

adjustment

resistors

ÁÁÁ

Frequency

sweep timing

ÁÁÁ

capacitor

ÁÁÁ

Oscillator

capacitor

ÁÁÁ

ÁÁÁ

Steady state

operating

ÁÁÁ

frequency

adjustment

ÁÁÁ

current input

Dead Time

ÁÁÁ

Adjust

Strike detection

input

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

Master reset

input

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

ÁÁÁ

This pin provides the DC supply to the circuit. The voltage is internally clamped by a zener

connected to the ground. It is NOT allowed to use a DC low impedance power supply to feed this

ББББББББББББББББББББББ

pin, but limiting the current by an external resistor is mandatory. It is recommended to damp this pin

ББББББББББББББББББББББ

to ground by an electrolytic capacitor connected close to pin 1.

This pin provides a +7V voltage reference derived from the internal bandgap. The +Vref can supply

up to 25 mA and shall be decoupled to ground by a 220nF ceramic capacitor

ББББББББББББББББББББББ

This capacitor sets two timings: filaments preheat time (tPH) and strike sequence recycle time (tSK).

ББББББББББББББББББББББ

It is charged with a constant current and cares must be observed to minimize the leakage current

at this pin to get the expected timing. Typically, a 0.47 µF capacitor will give a 2 seconds

ББББББББББББББББББББББ

pre–heating time and a 125 ms strike sequence recycle time. (See details given by figure 9)

The RPH resistor together with R

ББББББББББББББББББББББ

filaments (fPH = f1). R

timing, the frequency will sweep from the high pre–heating f1 to the low strike f2 values. Normally,

ББББББББББББББББББББББ

f1 is far from the LC resonance but f2 is close enough to generate the high voltage across the

fluorescent tube. (See details given by figure 9)

ББББББББББББББББББББББ

ENDSWEEP

ENDSWEEP

defines the strike frequency (f

This timing define the sweep time from f1 to f2. Since the timing capacitor is charged with a low

constant current, cares must be observed to minimize the leakage current at this pin to get the

ББББББББББББББББББББББ

expected timing. Since this capacitor is charged through resistor RPH, the voltage rises according

to an exponential and the frequency shifts with the same law.

ББББББББББББББББББББББ

This pin defines the steady state operation frequency (f3 = fOP) of the controller. Since this timing

capacitor is charged with a low constant current, cares must be observed to minimize the leakage

ББББББББББББББББББББББ

current at this pin to get the expected frequency. Film type capacitor are recommended

(polycarbonate).

ББББББББББББББББББББББ

Since the circuit uses a Current Controlled Oscillator (ICO), the current forced into this pin will

control the operating frequency. The allowable current range is from 1 µA to 500 µA. The +Vref

ББББББББББББББББББББББ

output can be used to provide the voltage across ROP. An auxiliary voltage source can be used to

implement a dimming function.

ББББББББББББББББББББББ

This pin provides an access to the internal timing system to adjust the dead time between the gate

ББББББББББББББББББББББ

drive of the High and Low power switches connected, respectively, to pin VHO and VLO.

This pin drives a comparator, with an internal fixed reference, and acknowledges the tube strike.

When a negative going slope (across the internal reference) is detected, the system considers the

ББББББББББББББББББББББ

lamp has struck and the oscillator jumps from the present frequency value, which is within the

ББББББББББББББББББББББ

window defined by RPH and R

going slope is detected on this pin, the system will repeat the sweep and strike sequence four

ББББББББББББББББББББББ

times, then stops. The circuit will re–start from either a RESET, or by pulling +VDD to ground. The

ББББББББББББББББББББББ

input signal can be either a logic level or an analog voltage ramping up from zero to +Vref followed

by a negative going slope to zero. In any case, the positive pulse width must be 1 µs minimum. The

ББББББББББББББББББББББ

pcb layout must be designed to minimize the noise at this pin. (See details given by figures 8, 9, &

ББББББББББББББББББББББ

10)

ENDSWEEP

Forcing a logic zero to this pin (HCMOS low level) will reset the circuit, initializing a frequency sweep

and lamp strike sequence. The master reset does not include the pre–heating timing. The minimum

ББББББББББББББББББББББ

pulse width requested is 10µs to guarantee a reset state. However, this pin has no built in filtering

ББББББББББББББББББББББ

and a shorter pulse may initialize a reset sequence: it is the responsibility of the designer to make

sure that no noise or parasitic pulse are developed at the RESET input. A full re–start of the

ББББББББББББББББББББББ

sequence, including the pre–heating time, can be initialized by pulling the +VDD pin to ground. In this

case, +VDD and RESET

ББББББББББББББББББББББ

low (active) both outputs MOS are biased in the off condition. An internal 20µA pull up current forces

ББББББББББББББББББББББ

the pin to logic one, allowing the designer to left this pin open if the RESET function is not used. In

order to avoid any uncontrolled state of the output drivers, it is recommended to set up a 10ms low

ББББББББББББББББББББББ

level at pin 10. The reset is activated in less than 10 microsecond, but releasing this pin while the Vcc

ББББББББББББББББББББББ

supply is high (above 300V) can generate a random operation, depending upon the dv/dt coming

from the power supply.

ББББББББББББББББББББББ

must be simultaneously released to a high state. When RESET is asserted

http://onsemi.com

4

and COP defines the frequency used to preheat the

ENDSWEEP

= f2). During the sweep

to the steady state value defined by ROP. If no negative

Loading...

Loading...