Motorola MC141524T1 Datasheet

MCM64AF32

1

MOTOROLA FAST SRAM

Product Preview

256K Asynchronous Secondary

Cache Module for Pentium

The MCM64AF32 is designed to provide 256K of asynchronous L2 cache for

the Pentium microprocessor in conjunction with Intel’s Triton chip set. The module is configured as 32K x 64 bits in a 160 pin card edge connector . The module

uses eight Motorola 3.3 V 32K x 8 FSRAMs for the cache memory, one Motorola

5 V 32K x 8 FSRAM for the tag RAM, and an upper order address latch.

Eight write enables are provided for byte write control.

PD0–PD4 identify density and functionality.

This cache module is plug and pin compatible with the other members of

Motorola’s Triton chip set module family, the MCM72JG32SG66 (a 256K byte

pipelined BurstRAM module) and the MCM72JG64SG66 (a 512K byte pipelined

BurstRAM module).

• Low–Cost Asynchronous Solution for Triton Chip Set

• All Cache Data Inputs and Outputs are LVTTL (3.3 V I/O) Compatible

• All Tag I/Os are TTL Compatible

• Byte Write Capability

• Fast SRAM Access Times:15 ns for Data RAMs and Tag RAM

• Decoupling Capacitors for each Fast Static RAM and Logic Device

• High Quality Multi–Layer FR4 PWB With Separate Power and Ground

Planes

• 160 Pin Card Edge Module

• Burndy Connector, Part Number: CELP2X80SC3Z48

BurstRAM is a trademark of Motorola.

Pentium is a trademark of Intel Corp.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

Order this document

by MCM64AF32/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

* SEE CHAPTER 9 FOR PRELIMINARY

CASE OUTLINE.

MCM64AF32

160–LEAD

CARD EDGE

CASE TBD*

TOP VIEW

80

43

42

1

* SEE BACK PAGE FOR PRELIMINARY

CASE OUTLINE.

5/95

Motorola, Inc. 1995

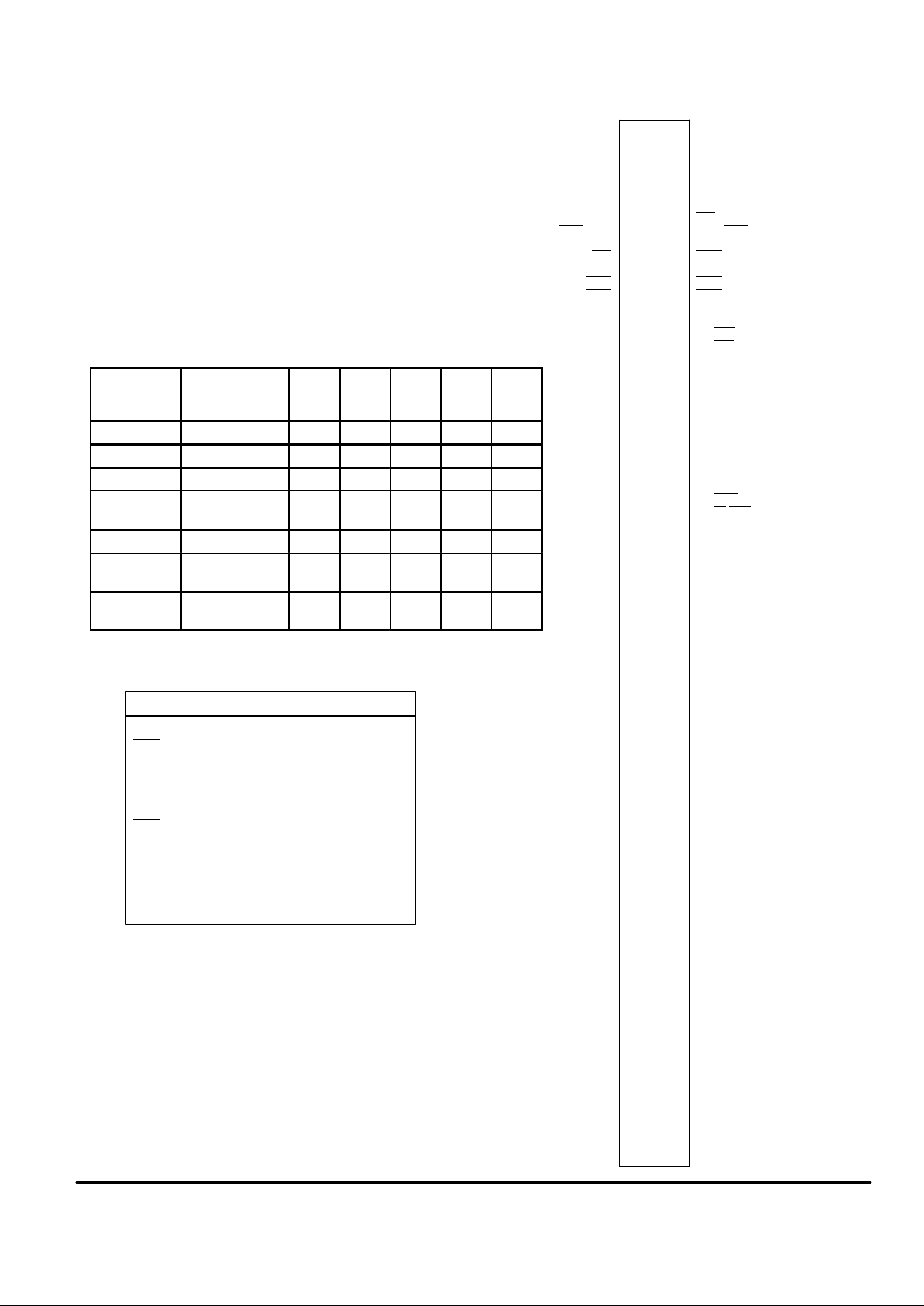

PIN ASSIGNMENT

160–LEAD CARD EDGE MODULE

TOP VIEW

V

SS

TIO1

TIO7

TIO5

TIO3

(RSVD) NC

VCC5

(RSVD) NC

(CADV

) CAA4

V

SS

COE

CWE5

CWE7

CWE1

VCC5

CWE3

CAB3

CALE

V

SS

(RSVD) NC

(A4) NC

A6

A8

A10

VCC5

A17

V

SS

A9

A14

A15

(RSVD) NC

PD0

PD2

PD4

V

SS

(CLK0) NC

V

SS

DQ63

VCC5

DQ61

DQ59

DQ57

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

V

SS

TIO0

TIO2

TIO6

TIO4

NC (RSVD)

VCC3

TWE

CAA3 (CADS)

V

SS

CWE4

CWE6

CWE0

CWE2

VCC3

CAB4 (CCS

)

NC (GWE

)

NC (BWE

)

V

SS

NC (A3)

A7

A5

A11

A16

VCC3

NC (A18)

V

SS

A12

A13

NC (ADSP

)

NC (CS

/ECS1)

NC (ECS2

)

PD1

PD3

V

SS

NC (CLK1)

V

SS

DQ62

VCC3

DQ60

DQ58

DQ56

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

V

SS

DQ55

DQ53

DQ51

DQ49

V

SS

DQ47

DQ45

DQ43

VCC5

DQ41

DQ39

DQ37

V

SS

DQ35

DQ33

DQ31

VCC5

DQ29

DQ27

DQ25

V

SS

DQ23

DQ21

DQ19

VCC5

DQ17

DQ15

DQ13

V

SS

DQ11

DQ9

DQ7

VCC5

DQ5

DQ3

DQ1

V

SS

V

SS

DQ54

DQ52

DQ50

DQ48

V

SS

DQ46

DQ44

DQ42

VCC3

DQ40

DQ38

DQ36

V

SS

DQ34

DQ32

DQ30

VCC3

DQ28

DQ26

DQ24

V

SS

DQ22

DQ20

DQ18

VCC3

DQ16

DQ14

DQ12

V

SS

DQ10

DQ8

DQ6

VCC3

DQ4

DQ2

DQ0

V

SS

PIN NAMES

TIO0 – TIO7 Tag RAM I/O. . . . . . . . . . . . . . . . . . . . .

TWE

Tag Write Enable. . . . . . . . . . . . . . . . . . . . . . . .

CALE Address Latch Enable. . . . . . . . . . . . . . . . . . .

A5 – A17 Address Inputs. . . . . . . . . . . . . . . . . . . . . .

CWE0

– CWE7 Cache Write Enable. . . . . . . . . . .

CAA3 –CAA4 Cache Address A. . . . . . . . . . . . . . . .

CAB3 – CAB4 Cache Address B. . . . . . . . . . . . . . .

COE

Cache Output Enable. . . . . . . . . . . . . . . . . . . .

DQ0 – DQ63 Data Input/Output. . . . . . . . . . . . . . . .

PD0 – PD4 Presence Detect. . . . . . . . . . . . . . . . . .

VCC3 + 3.3 V Power Supply. . . . . . . . . . . . . . . . . . .

VCC5 + 5.0 V Power Supply. . . . . . . . . . . . . . . . . . .

V

SS

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

NC No Connection. . . . . . . . . . . . . . . . . . . . . . . . . . .

For proper operation of the device, VSS must be

connected to ground.

NOTE: Signals in parentheses indicate pin designations for

burstable members of the Triton chip set module family.

MCM64AF32

2

MOTOROLA FAST SRAM

PRESENCE DETECT TABLE

Cache Size

and

Functionality

Module PD4 PD3 PD2 PD1 PD0

256KB Async MCM64AF32 V

SS

NC V

SS

V

SS

NC

512KB Async — V

SS

V

SS

NC V

SS

NC

256K Burst — V

SS

NC V

SS

NC V

SS

256K Pipe

Burst

MCM72JG32 V

SS

NC V

SS

NC NC

512K Burst — V

SS

V

SS

NC NC V

SS

512K Pipe

Burst

MCM72JG64 V

SS

V

SS

NC NC NC

512K 2–Bank

Burst

— V

SS

V

SS

NC V

SS

V

SS

MCM64AF32

3

MOTOROLA FAST SRAM

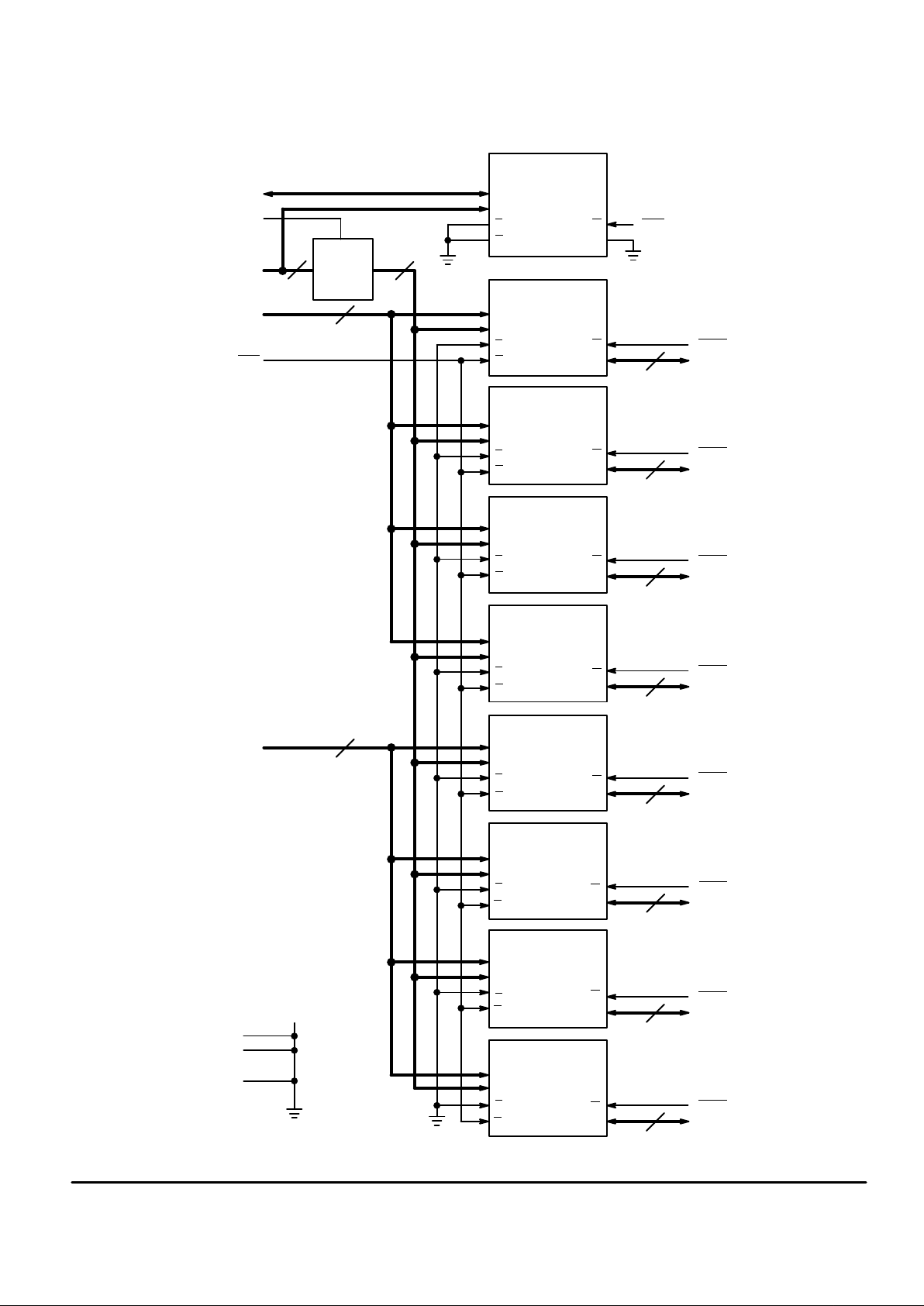

MCM64AF32 MODULE BLOCK DIAGRAM

32K X 8

DQ0 – DQ7

CAA3 – CAA4

2

E

G

COE

CWE0

DQ0 – DQ7

A0 – A12

13

W

A13 – A14

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

32K X 8

3.3 V

A0 – A1

E

DQ0 – DQ7

A2 – A14

A2 – A14

A2 – A14

A2 – A14

A2 – A14

A2 – A14

A2 – A14

A2 – A14

8

CWE1

DQ8 – DQ15

8

CWE2

DQ16 – DQ23

8

CWE3

DQ24 – DQ31

8

CWE4

DQ32 – DQ39

8

CWE5

DQ40 – DQ47

8

CWE6

DQ48 – DQ55

8

CWE7

DQ56 – DQ63

8

TIO0 – TIO7

LE

’373

TWE

A5 – A17

CALE

13

CAB3 – CAB4

2

PD0 – NC

PD1

PD2

PD3 – NC

PD4

A18 – NC

G

W

G

W

G

W

G

W

G

W

G

W

G

W

G

W

5 V

MCM64AF32

4

MOTOROLA FAST SRAM

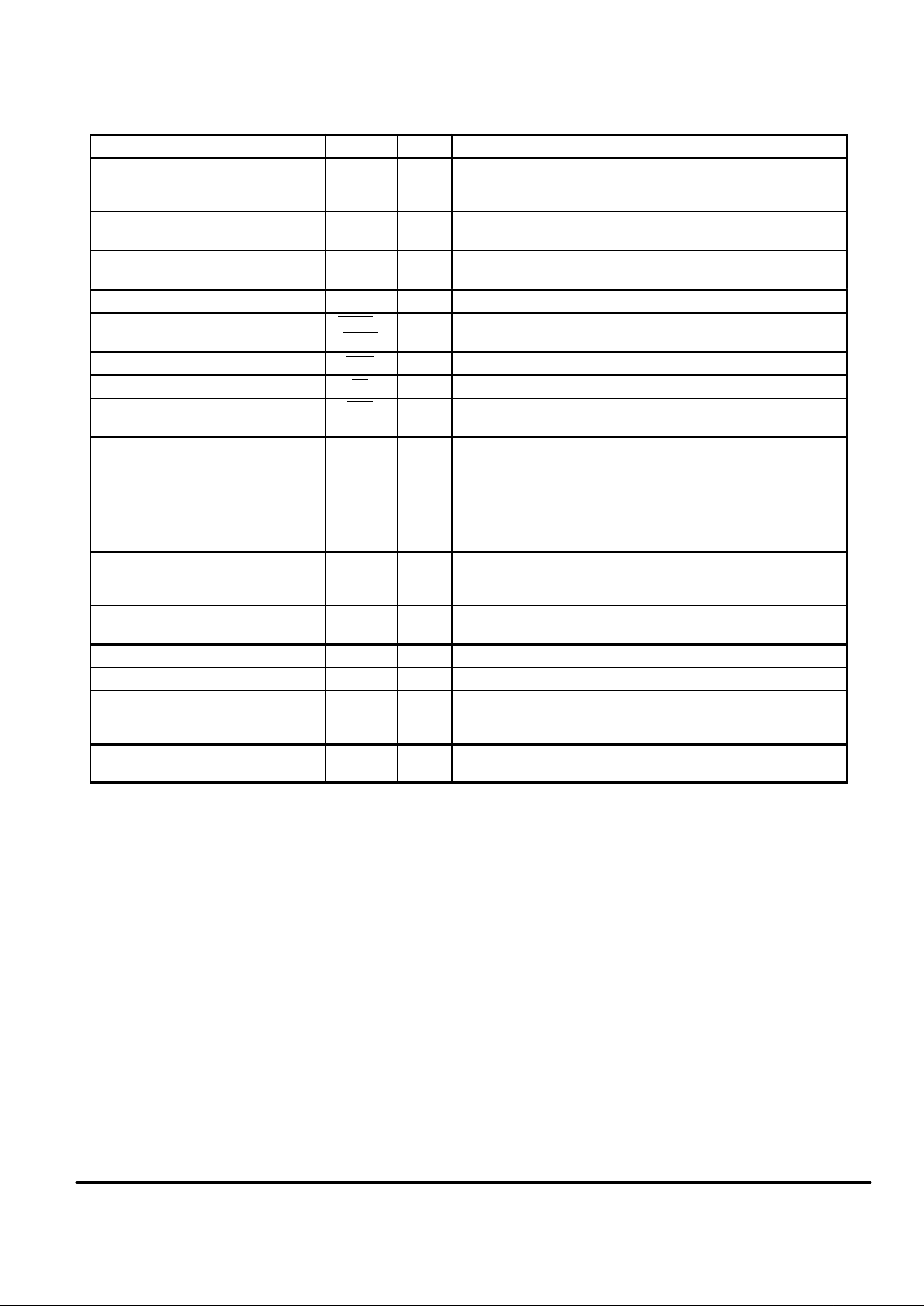

PIN DESCRIPTIONS

160–Lead Card Edge Pin Locations Symbol

Type Description

21, 22, 23, 24, 28, 29,

102, 103, 104, 106, 108, 109, 110

A5 – A17 Input Address Inputs: These inputs are latched into data RAMs and must

meet setup and hold times. The tag RAM addresses are not latched.

(See Block Diagram).

9, 89 CAA3,

CAA4

Input Cache Address A: Low order address inputs for bursting. Not latched.

16, 97 CAB3,

CAB4

Input Cache Address B: Low order address inputs for bursting. Not latched.

98 CALE Input Address Latch Enable: Active low signal latches A5 – A17.

11, 12, 13, 14, 92, 93, 94, 96 CWE0 –

CWE7

Input Cache Data Write Enable: Active low write signal for data RAMs.

8 TWE Input Tag Write Enable: Active low write signal for tag RAMs.

— CS Input Chip Select: Active low chip enable for tag and data RAMs. Not used.

91 COE Input Cache Output Enable: Asynchronous active low output enable for data

RAMs.

38, 40, 41, 42, 44, 45, 46, 47, 49, 50, 51,

53, 54, 55, 57, 58, 59, 61, 62, 63, 65, 66,

67, 69, 70, 71, 73, 74, 75, 77, 78, 79,

118, 120, 121, 122, 124, 125, 126, 127,

129, 130, 131, 133, 134, 135, 137, 138,

139, 141, 142, 143, 145, 146, 147, 149,

150, 151, 153, 154, 155, 157, 158, 159

DQ0 –

DQ63

I/O Data I/O

2, 3, 4, 5, 82, 83, 84, 85 TIO0 –

TIO7

I/O Tag RAM I/O:

Drives data out during tag compare cycles.

Stores data to tag RAM during tag WRITE cycles.

33, 34, 112, 113, 114 PD0 –

PD4

Presence Detect: See Presence Detect Table.

7, 15, 25, 39, 52, 60, 68, 76 VCC3 Supply Power Supply: 3.3 V ± 5%.

87, 95, 105, 119, 132, 140, 148, 156 VCC5 Supply Power Supply: 5.0 V ± 5%.

1, 10, 19, 27, 35, 37, 43, 48, 56, 64,

72, 80, 81, 90, 99, 107, 115, 117,

123, 128, 136, 144, 152, 160

V

SS

Supply Ground

6, 17, 18, 20, 26, 30, 31, 32, 36,

86, 88, 100, 101, 111, 116

NC — No Connection: There is no connection to the module.

Loading...

Loading...