查询MC100H641FN供应商

SEMICONDUCTOR TECHNICAL DATA

#$

!" #"

The MC10H/100H641 is a single supply , low skew translating 1:9 clock

driver. Devices in the Motorola H600 translator series utilize the 28–lead

PLCC for optimal power pinning, signal flow through and electrical

performance.

The device features a 24mA TTL output stage, with AC performance

specified into a 50pF load capacitance. A latch is provided on–chip. When

LEN is LOW (or left open, in which case it is pulled LOW by the internal

pulldown) the latch is transparent. A HIGH on the enable pin (EN

all outputs LOW. Both the LEN and EN

The VBB output is provided in case the user wants to drive the device

with a single–ended input. For single–ended use the VBB should be

connected to the D

The 10H version of the H641 is compatible with positive MECL 10H

logic levels. The 100H version is compatible with positive 100K levels.

input and bypassed with a 0.01µF capacitor.

pins are positive ECL inputs.

• PECL–TTL Version of Popular ECLinPS E111

• Low Skew

• Guaranteed Skew Spec

• Latched Input

• Dif ferential ECL Internal Design

• V

Output for Single–Ended Use

BB

• Single +5V Supply

• Logic Enable

• Extra Power and Ground Supplies

• Separate ECL and TTL Supply Pins

) forces

SINGLE SUPPLY

PECL–TTL 1:9 CLOCK

DISTRIBUTION CHIP

FN SUFFIX

PLASTIC PACKAGE

CASE 776–02

Pinout: 28–Lead PLCC (Top View)

GT Q6 VT Q7 VT Q8 GTGT Q6 VT Q7 VT Q8 GT

25 24 23 22 21 20 19

26

GT

27

Q5

28

VT

Q4

1

2

VT

3

Q3

4

GT

567891011

GT Q2 VT Q1 VT Q0 GT

MECL 10H is a trademark of Motorola, Inc.

11/93

Motorola, Inc. 1996

2–1

18

17

16

15

14

13

12

VBB

D

D

VE

LEN

GE

EN

PIN NAMES

Pins

GT, VT

GE, VE

D, D

V

BB

Q0–Q8

EN

LEN

REV 3

Function

TTL GND, TTL V

ECL GND, ECL V

Signal Input (Positive ECL)

VBB Reference Output

(Positive ECL)

Signal Outputs (TTL)

Enable Input (Positive ECL)

Latch Enable Input

(Positive ECL)

CC

CC

MC10H641 MC100H641

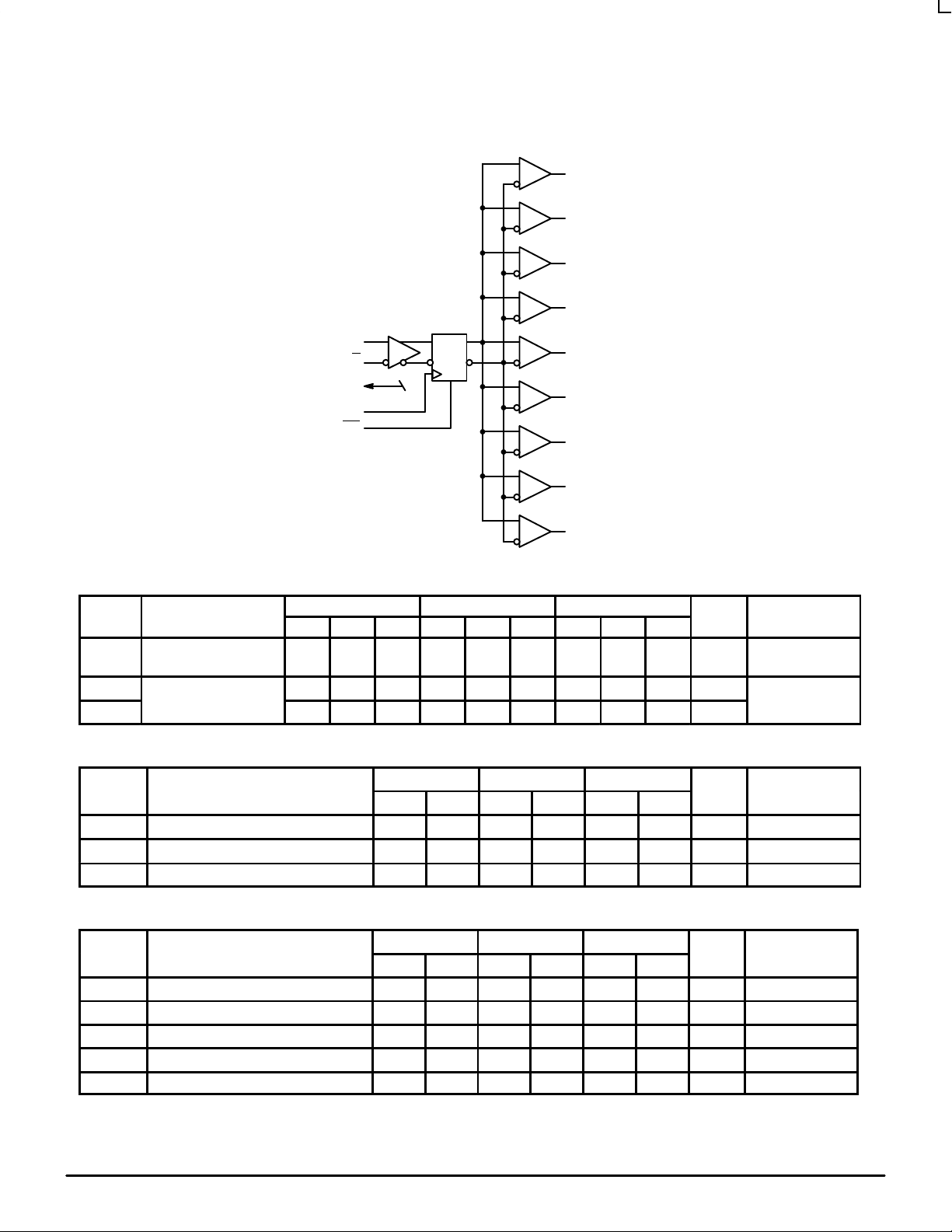

LOGIC DIAGRAM

TTL Outputs

Q0

Q1

Q2

PECL Input

D

D

VBB

LEN

EN

DQ

Q3

Q4

Q5

Q6

Q7

Q8

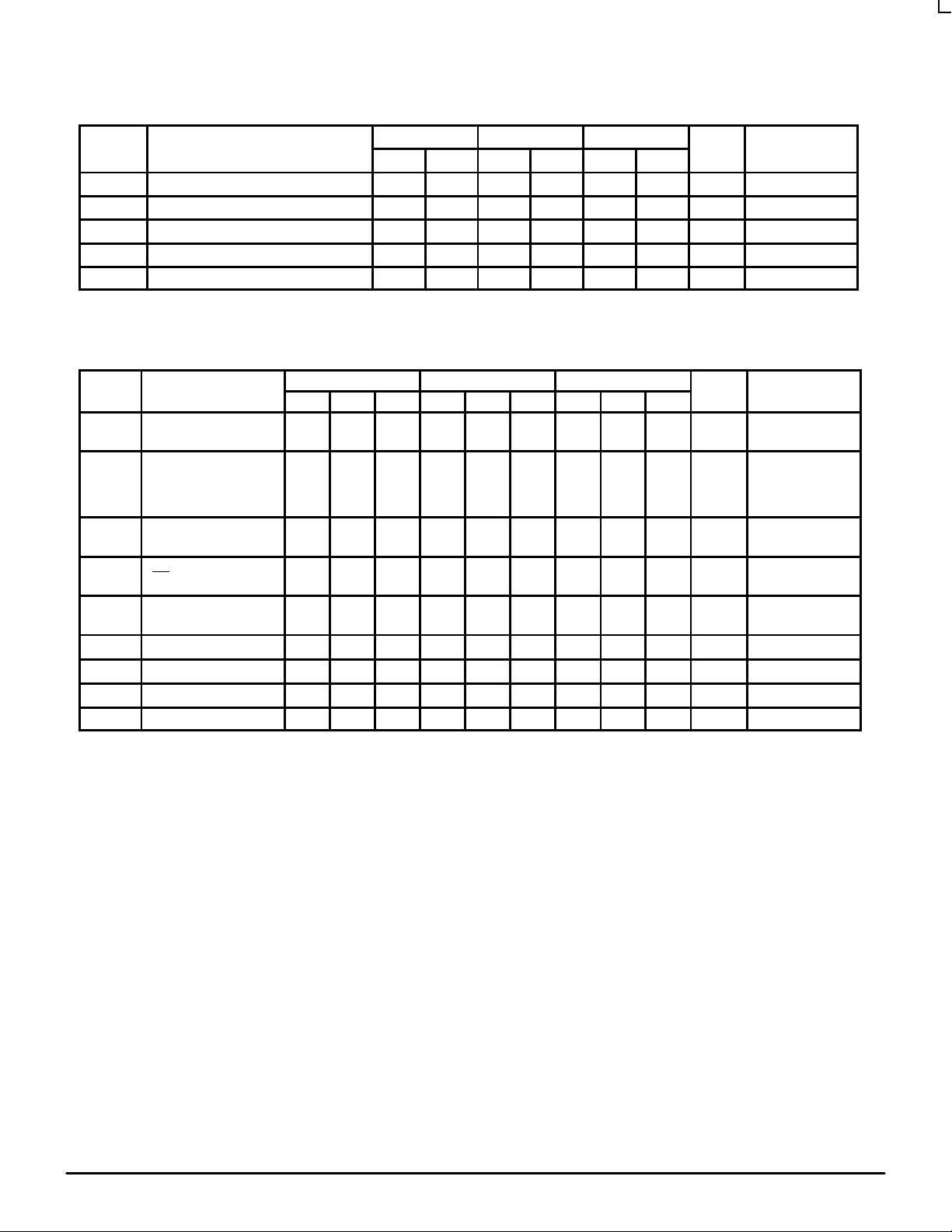

DC CHARACTERISTICS (VT = VE = 5.0V ±5%)

TA = 0°C TA = + 25°C TA = + 85°C

Symbol Characteristic Min Typ Max Min Typ Max Min Typ Max Unit Condition

I

EE

I

CCH

I

CCL

Power Supply Current

PECL

TTL 24 30 24 30 24 30 mA

24 30 24 30 24 30 mA

27 35 27 35 27 35 mA

TTL DC CHARACTERISTICS (VT = VE = 5.0V ±5%)

0°C 25°C 85°C

Symbol Characteristic Min Max Min Max Min Max Unit Condition

V

V

I

OH

OL

OS

Output HIGH Voltage 2.5 2.5 2.5 V IOH = –15mA

Output LOW Voltage 0.5 0.5 0.5 V IOL = 24mA

Output Short Circuit Current –100 –225 –100 –225 –100 –225 mA V

OUT

= 0V

10H PECL DC CHARACTERISTICS

0°C 25°C 85°C

Symbol Characteristic Min Max Min Max Min Max Unit Condition

I

IH

I

IL

V

IH

V

IL

V

BB

1. PECL VIH, VIL, and VBB are referenced to VE and will vary 1:1 with the power supply. The levels shown are for VE = 5.0V.

MOTOROLA MECL Data

Input HIGH Current 225 175 175 µA

Input LOW Current 0.5 0.5 0.5 µA

Input HIGH Voltage 3.83 4.16 3.87 4.19 3.94 4.28 V VE = 5.0V

Input LOW Voltage 3.05 3.52 3.05 3.52 3.05 3.55 V VE = 5.0V

Output Reference Voltage 3.62 3.73 3.65 3.75 3.69 3.81 V VE = 5.0V

2–2

DL122 — Rev 6

1

1

1

MC10H641 MC100H641

100H PECL DC CHARACTERISTICS

0°C 25°C 85°C

Symbol Characteristic Min Max Min Max Min Max Unit Condition

I

IH

I

IL

V

IH

V

IL

V

BB

1. PECL VIH, VIL, and VBB are referenced to VE and will vary 1:1 with the power supply. The levels shown are for VE = 5.0V.

AC CHARACTERISTICS (VT = VE = 5.0V ±5%)

Symbol Characteristic Min Typ Max Min Typ Max Min Typ Max Unit Condition

t

PLH

t

PHL

t

skew

t

PLH

t

PHL

t

PLH

t

PHL

t

r

t

f

f

MAX

t

REC

t

S

t

H

1. Propagation delay measurement guaranteed for junction temperatures. Measurements performed at 50MHz input frequency .

2. Skew window guaranteed for a single temperature across a VCC = VT = VE of 4.75V to 5.25V (See Application Note in this datasheet).

3. Skew window guaranteed for a single temperature and single VCC = VT = V

4. Output–to–output skew is specified for identical transitions through the device.

5. Frequency at which output levels will meet a 0.8V to 2.0V minimum swing.

Input HIGH Curren 225 175 175 µA

Input LOW Current 0.5 0.5 0.5 µA

Input HIGH Voltage 3.835 4.120 3.835 4.120 3.835 4.120 V VE = 5.0V

Input LOW Voltage 3.190 3.525 3.190 3.525 3.190 3.525 V VE = 5.0V

Output Reference Voltage 3.62 3.74 3.62 3.74 3.62 3.74 V VE = 5.0V

TJ = 0°C TJ = + 25°C TJ = + 85°C

Propagation Delay

D to Q

Device Skew

Part–to–Part

Single V

CC

Output–to–Output

Propagation Delay

LEN to Q

Propagation Delay

to Q

EN

Output Rise/Fall

0.8V to 2.0V

Max Input Frequency 65 65 65 MHz CL = 50 pF

Recovery Time EN 1.25 1.25 1.25 ns

Setup Time 0.75 0.50 0.75 0.50 0.75 0.50 ns

Hold Time 0.75 0.50 0.75 0.50 0.75 0.50 ns

5.00

5.50

6.00

4.86

5.36

5.86

5.08

5.58

5.36

5.86

6.36

5.27

5.77

6.27

5.43

1000

750

350

4.9 6.9 4.9 6.9 5.0 7.0 ns CL = 50 pF

5.0 7.0 4.9 6.9 5.0 7.0 ns CL = 50 pF

1.7

1.6

1000

750

350

1.7

1.6

E

5.93

6.08

6.43

1000

750

350

1.7

1.6

ns CL = 50 pF

ps

CL = 50pF

CL = 50 pF

CL = 50 pF

ns CL = 50 pF

1

1

1

1

2

3

4

5

DETERMINING SKEW FOR A SPECIFIC APPLICATION

The H641 has been designed to meet the needs of very low

skew clock distribution applications. In order to optimize the

device for this application special considerations are

necessary in the determining of the part–to–part skew

specification limits. Older standard logic devices are specified

with relatively slack limits so that the device can be

guaranteed over a wide range of potential environmental

conditions. This range of conditions represented all of the

potential applications in which the device could be used. The

result was a specification limit that in the vast majority of cases

was extremely conservative and thus did not allow for an

optimum system design. For non–critical skew designs this

practice is acceptable, however as the clock speeds of

DL122 — Rev 6

systems increase overly conservative specification limits can

kill a design.

The following will discuss how users can use the

information provided in this data sheet to tailor a part–to–part

skew specification limit to their application. The skew

determination process may appear somewhat tedious and

time consuming, however if the utmost in performance is

required this procedure is necessary. For applications which

do not require this level of skew performance a generic

part–to–part skew limit of 2.5ns can be used. This limit is good

for the entire ambient temperature range, the guaranteed V

(VT, VE) range and the guaranteed operating frequency range.

2–3 MOTOROLAMECL Data

CC

MC10H641 MC100H641

T emperature Dependence

A unique characteristic of the H641 data sheet is that the

AC parameters are specified for a junction temperature rather

than the usual ambient temperature. Because very few

designs will actually utilize the entire commercial temperature

range of a device a tighter propagation delay window can be

established given the smaller temperature range. Because

the junction temperature and not the ambient temperature is

what affects the performance of the device the parameter

limits are specified for junction temperature. In addition the

relationship between the ambient and junction temperature

will vary depending on the frequency, load and board

environment of the application. Since these factors are all

under the control of the user it is impossible to provide

specification limits for every possible application. Therefore a

baseline specification was established for specific junction

temperatures and the information that follows will allow these

to be tailored to specific applications.

Since the junction temperature of a device is difficult to

measure directly, the first requirement is to be able to

“translate” from ambient to junction temperatures. The

standard method of doing this is to use the power dissipation

of the device and the thermal resistance of the package. For

a TTL output device the power dissipation will be a function of

the load capacitance and the frequency of the output. The total

power dissipation of a device can be described by the

following equation:

Figure 2 illustrates the thermal resistance (in °C/W) for the

28–lead PLCC under various air flow conditions. By reading

the thermal resistance from the graph and multiplying by the

power dissipation calculated above the junction temperature

increase above ambient of the device can be calculated.

70

60

C/W)

°

50

40

THERMAL RESISTANCE (

30

0 200 400 600 800 1000

AIRFLOW (LFPM)

Figure 2. ∅JA versus Air Flow

PD (watts) = ICC (no load) * VCC +

VS * VCC * f * CL * # Outputs

where:

VS= Output Voltage Swing = 3V

f = Output Frequency

CL = Load Capacitance

ICC = IEE + I

CCH

Figure 1 plots the ICC versus Frequency of the H641 with

no load capacitance on the output. Using this graph and the

information specific to the application a user can determine

the power dissipation of the H641.

5

4

3

2

NORMALIZED ICC

1

Finally taking this value for junction temperature and

applying it to Figure 3 allows the user to determine the

propagation delay for the device in question. A more common

use would be to establish an ambient temperature range for

the H641’s in the system and utilize the above methodology

to determine the potential increased skew of the distribution

network. Note that for this information if the TPD versus

Temperature curve were linear the calculations would not be

required. If the curve were linear over all temperatures a

simple temperature coefficient could be provided.

6.4

PROPAGATION DELAY (ns)

6.2

6.0

5.8

5.6

5.4

T

PHL

T

PLH

0

0 1020304050607080

FREQUENCY (MHz)

Figure 1. ICC versus f (No Load)

MOTOROLA MECL Data

2–4

5.2

–30

–10 10 30 50 70 90 110 130

JUNCTION TEMPERATURE (

°

C)

Figure 3. TPD versus Junction T emperature

DL122 — Rev 6

MC10H641 MC100H641

VCC Dependence

TTL and CMOS devices show a significant propagation

delay dependence with VCC. Therefore the VCC variation in a

system will have a direct impact on the total skew of the clock

distribution network. When calculating the skew between two

devices on a single board it is very likely an assumption of

identical VCC’s can be made. In this case the number provided

in the data sheet for part–to–part skew would be overly

conservative. By using Figure 4 the skew given in the data

sheet can be reduced to represent a smaller or zero variation

in VCC. The delay variation due to the specified VCC variation

is ≈270ps. Therefore, the 1ns window on the data sheet can

be reduced by 270ps if the devices in question will always

experience the same VCC. The distribution of the propagation

delay ranges given in the data sheet is actually a composite

of three distributions whose means are separated by the fixed

difference in propagation delay at the typical, minimum and

maximum VCC.

140

100

60

20

(ps)

PD

T

–20

∆

CC

T

PLH

–60

–100

–140

T

PHL

4.75

4.85 4.95 5.05 5.15 5.25

Figure 4. ∆TPD versus V

VCC (V)

Capacitive Load Dependence

As with VCC the propagation delay of a TTL output is

intimately tied to variation in the load capacitance. The skew

specifications given in the data sheet, of course, assume

equal loading on all of the outputs. However situations could

arise where this is an impossibility and it may be necessary to

estimate the skew added by asymmetric loading. In addition

the propagation delay numbers are provided only for 50pF

loads, thus necessitating a method of determining the

propagation delay for alternative loads.

Figure 5 shows the relationship between the two

propagation delays with respect to the capacitive load on the

output. Utilizing this graph and the 50pF limits the specification

of the H641 can be mapped into a spec for either a different

value load or asymmetric loads.

1.15

1.10

MORMALIZED PROPAGATION DELAY (ns)

1.05

1.00

0.95

0.90

0.85

0.80

0.75

MEASURED

T

PHL

THEORETICAL

0

10 20 30 40 50 60 70 80 90 100

CAPACITIVE LOAD (pF)

T

PLH

Figure 5. TPD versus Load

Rise/Fall Skew Determination

The rise–to–fall skew is defined as simply the difference

between the T

and the T

PLH

propagation delays. This

PHL

skew for the H641 is dependent on the VCC applied to the

device. Notice from Figure 4 the opposite relationship of T

versus VCC between T

PLH

and T

. Because of this the

PHL

PD

rise–to–fall skew will vary depending on VCC. Since in all

likelihood it will be impossible to establish the exact value for

VCC, the expected variation range for VCC should be used. If

this variation will be the ±5% shown in the data sheet the

rise–to–fall skew could be established by simply subtracting

the fastest T

from the slowest T

PLH

; this exercise yields

PHL

1.41ns. If a tighter VCC range can be realized Figure 4 can be

used to establish the rise–to–fall skew.

Specification Limit Determination Example

The situation pictured in Figure 6 will be analyzed as an

example. The central clock is distributed to two different cards;

on one card a single H641 is used to distribute the clock while

on the second card two H641’s are required to supply the

needed clocks. The data sheet as well as the graphical

information of this section will be used to calculate the skew

between H641a and H641b as well as the skew between all

three of the devices. Only the T

will be analyzed, the T

PLH

PHL

numbers can be found using the same technique. The

following assumptions will be used:

– All outputs will be loaded with 50pF

– All outputs will toggle at 30MHz

– The VCC variation between the two boards is ±3%

– The temperature variation between the three

devices is ±15°C around an ambient of 45°C.

– 500LFPM air flow

The first task is to calculate the junction temperature for the

devices under these conditions. Using the power equation

yields:

PD =ICC (no load) * VCC +

VCC * VS * f * CL * # outputs

= 1.8 * 48mA * 5V + 5V * 3V * 30MHz *

50pF * 9

= 432mW + 203mW = 635mW

DL122 — Rev 6

2–5 MOTOROLAMECL Data

MC10H641 MC100H641

Using the thermal resistance graph of Figure 2 yields a

thermal resistance of 41°C/W which yields a junction

temperature of 71°C with a range of 56°C to 86°C. Using the

TPD versus Temperature curve of Figure 3 yields a

propagation delay of 5.42ns and a variation of 0.19ns.

Since the design will not experience the full ±5% V

CC

variation of the data sheet the 1ns window provided will be

unnecessarily conservative. Using the curve of Figure 4

shows a delay variation due to a ±3% VCC variation of

±0.075ns. Therefore the 1ns window can be reduced to

1ns – (0.27ns – 0.15ns) = 0.88ns. Since H641a and H641b

are on the same board we will assume that they will always be

at the same VCC; therefore the propagation delay window will

only be 1ns – 0.27ns = 0.73ns.

Putting all of this information together leads to a skew

between all devices of

0.19ns + 0.88ns

(temperature + supply , and inherent device),

while the skew between devices A and B will be only

0.19ns + 0.73ns

(temperature + inherent device only).

In both cases, the propagation delays will be centered

around 5.42ns, resulting in the following t

T

= 4.92ns – 5.99ns; 1.07ns window

PLH

PLH

windows:

(all devices)

T

= 5.00ns – 5.92ns; 0.92ns window

PLH

(devices a & b)

the conservative worst case limits provided at the beginning

of this note. For very high performance designs, this extra

information and effort can mean the difference between going

ahead with prototypes or spending valuable engineering time

searching for alternative approaches.

Card 1

H641a

ECL

H641b

ECL

BACKPLANE

H641c

ECL

Q0

TTL

Q8

Q0

TTL

Q8

Card 2

Q0

TTL

Q8

Of course the output–to–output skew will be as shown in

the data sheet since all outputs are equally loaded.

This process may seem cumbersome, however the delay

windows, and thus skew, obtained are significantly better than

Figure 6. Example Application

MOTOROLA MECL Data

2–6

DL122 — Rev 6

OUTLINE DIMENSIONS

FN SUFFIX

PLASTIC PLCC PACKAGE

CASE 776–02

ISSUE D

MC10H641 MC100H641

–L–

–N–

28 1

Z

C

G

G1

S

0.010 (0.250) N

L–M

T

S

T

L–M

S

S

S

L–M

T

M

Y BRK

0.007 (0.180) N

B

0.007 (0.180) N

U

M

D

Z

–M–

W

D

V

0.010 (0.250) N

G1X

S

S

L–M

T

S

VIEW D–D

A

0.007 (0.180) N

0.007 (0.180) N

R

E

M

M

S

L–M

T

L–M

T

S

S

S

H

0.007 (0.180) N

M

S

L–M

T

S

K1

0.004 (0.100)

SEATING

J

–T–

PLANE

VIEW S

S

S

K

VIEW S

0.007 (0.180) N

F

M

S

L–M

T

S

NOTES:

1. DATUMS –L–, –M–, AND –N– DETERMINED

WHERE TOP OF LEAD SHOULDER EXITS

PLASTIC BODY AT MOLD PARTING LINE.

2. DIMENSION G1, TRUE POSITION TO BE

MEASURED AT DA TUM –T–, SEATING PLANE.

3. DIMENSIONS R AND U DO NOT INCLUDE

MOLD FLASH. ALLOWABLE MOLD FLASH IS

0.010 (0.250) PER SIDE.

4. DIMENSIONING AND TOLERANCING PER

ANSI Y14.5M, 1982.

5. CONTROLLING DIMENSION: INCH.

6. THE PACKAGE TOP MAY BE SMALLER THAN

THE PACKAGE BOTTOM BY UP TO 0.012

(0.300). DIMENSIONS R AND U ARE

DETERMINED AT THE OUTERMOST

EXTREMES OF THE PLASTIC BODY

EXCLUSIVE OF MOLD FLASH, TIE BAR

BURRS, GATE BURRS AND INTERLEAD

FLASH, BUT INCLUDING ANY MISMATCH

BETWEEN THE TOP AND BOTTOM OF THE

PLASTIC BODY.

7. DIMENSION H DOES NOT INCLUDE DAMBAR

PROTRUSION OR INTRUSION. THE DAMBAR

PROTRUSION(S) SHALL NOT CAUSE THE H

DIMENSION TO BE GREATER THAN 0.037

(0.940). THE DAMBAR INTRUSION(S) SHALL

NOT CAUSE THE H DIMENSION TO BE

SMALLER THAN 0.025 (0.635).

DIM MIN MAX MIN MAX

A 0.485 0.495 12.32 12.57

B 0.485 0.495 12.32 12.57

C 0.165 0.180 4.20 4.57

E 0.090 0.110 2.29 2.79

F 0.013 0.019 0.33 0.48

G 0.050 BSC 1.27 BSC

H 0.026 0.032 0.66 0.81

J 0.020 ––– 0.51 –––

K 0.025 ––– 0.64 –––

R 0.450 0.456 11.43 1 1.58

U 0.450 0.456 11.43 1 1.58

V 0.042 0.048 1.07 1.21

W 0.042 0.048 1.07 1.21

X 0.042 0.056 1.07 1.42

Y ––– 0.020 ––– 0.50

Z 2 10 2 10

____

G1 0.410 0.430 10.42 10.92

K1 0.040 ––– 1.02 –––

MILLIMETERSINCHES

DL122 — Rev 6

2–7 MOTOROLAMECL Data

MC10H641 MC100H641

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty , representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. “T ypical” parameters which may be provided in Motorola

data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”

must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of

others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other

applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury

or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees

arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that

Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal

Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center,

P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

MFAX: RMF AX0@email.sps.mot.com – T OUCHTONE 602–244–6609 ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Ta i Ping Industrial Park,

INTERNET: http://Design–NET .com 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298

MOTOROLA MECL Data

2–8

*MC10H641/D*

◊

MC10H641/D

DL122 — Rev 6

Loading...

Loading...