D

1

Q

8

D0V

CCO

Q0V

CCO

Q7V

CCO

V

CCO

D

8

D

7

D

6

D

5

D

4

D

3

V

EE

LEN

MR

D

2

26

27

28

2

3

4

25 24 23 22 21 20 19

18

17

16

15

14

13

12

115 6 7 8 9 10

Q

6

Q

5

V

CC

Q

4

Q

3

V

CCO

Q

2

Q

1

ODDPAR

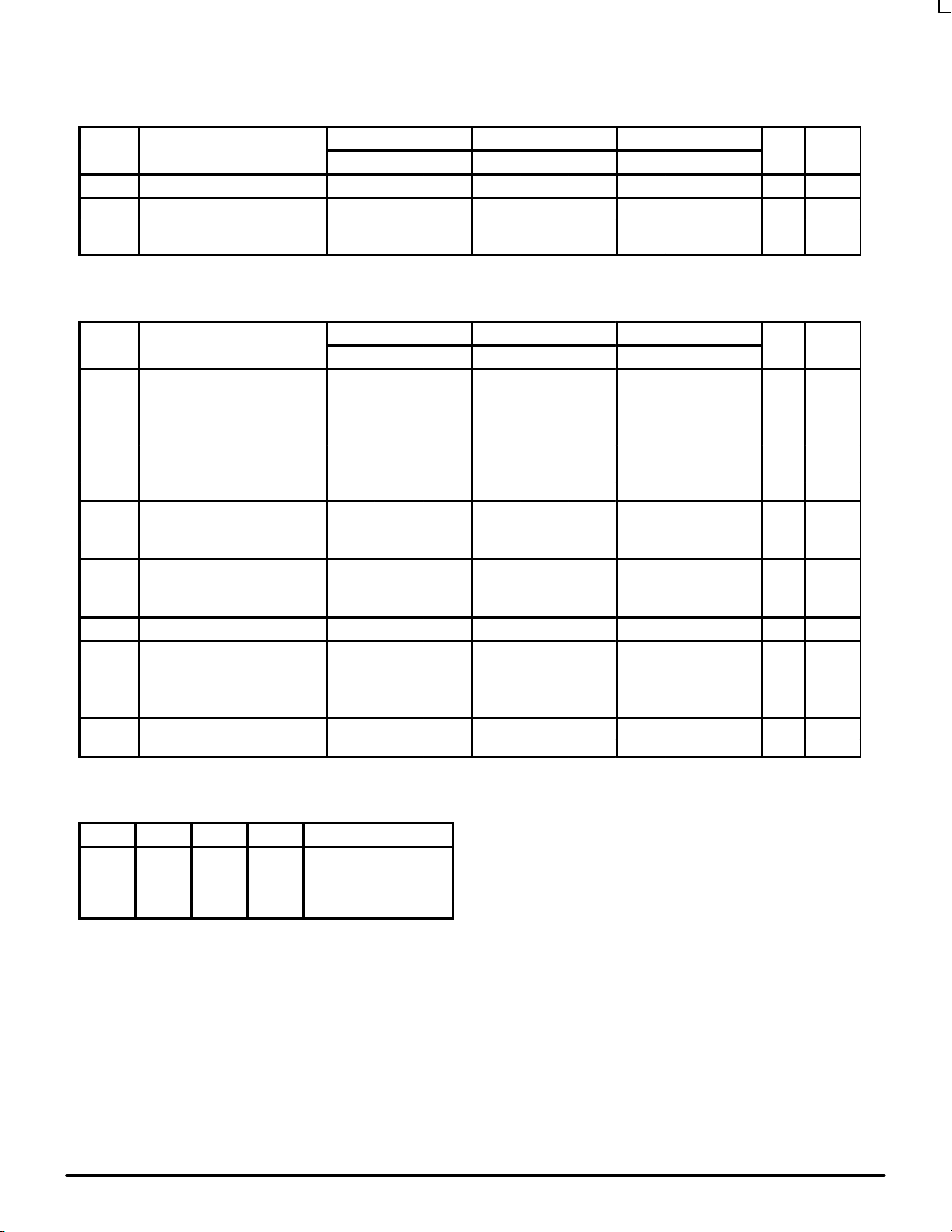

LOGIC DIAGRAM

D

0

D

8

LEN

MR

Q

0

Q

8

ODDPAR

BITS

1–7

D

EN

Q

R

D

EN

Q

R

D

EN

Q

R

1

Pinout: 28-Lead PLCC (Top View)

* All VCC and V

CCO

pins are tied together on the die.

SEMICONDUCTOR TECHNICAL DATA

2–1

REV 2

Motorola, Inc. 1996

12/93

The MC10E/100E175 is a 9-bit latch. It also features a tenth latched

output, ODDPAR, which is formed as the odd parity of the nine data

inputs (ODDPAR is HIGH if an odd number of the inputs are HIGH).

The E175 can also be used to generate byte parity by using D8 as the

parity-type select (L = even parity , H = odd parity), and using ODDP AR as

the byte parity output.

The LEN pin latches the data when asserted with a logical high and

makes the latch transparent when placed at a logic low level.

• 9-Bit Latch

• Parity Detection/Generation

• 800ps Max. D to Output

• Reset

• Extended 100E V

EE

Range of – 4.2V to – 5.46V

• Internal 75kΩ Input Pulldown Resistors

PIN NAMES

Pin Function

D0– D

8

Data Inputs

LEN Latch Enable

MR Master Reset

Q0– Q

8

Data Outputs

ODDPAR Parity Output

9-BIT LATCH

WITH PARITY

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

MC10E175 MC100E175

MOTOROLA ECLinPS and ECLinPS Lite

DL140 — Rev 4

2–2

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = V

CCO

= GND)

0°C 25°C 85°C

Symbol Characteristic min typ max min typ max min typ max Unit Cond

I

IH

Input HIGH Current 150 150 150 µA

I

EE

Power Supply Current mA

10E 110 132 110 132 110 132

100E 110 132 110 132 127 152

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = V

CCO

= GND)

0°C 25°C 85°C

Symbol Characteristic min typ max min typ max min typ max Unit Cond

t

PLH

Propagation Delay to Output ps

t

PHL

D to Q 450 600 800 450 600 800 450 600 800

D to ODDPAR 850 1150 1450 850 1150 1450 850 1150 1450

LEN to Q 525 700 900 525 700 900 525 700 900

LEN to ODDPAR 525 700 900 525 700 900 525 700 900

MR to Q(t

PHL

) 525 700 900 525 700 900 525 700 900

MR to ODDPAR(t

PHL

) 525 700 900 525 700 900 525 700 900

t

s

Setup Time ps

D (Q) 275 100 275 275

D (ODDPAR) 900 700 900 900

t

h

Hold Time ps

D (Q) 175 –100 175 175

D (ODDPAR) – 300 – 70 – 300 – 300

t

RR

Reset Recovery Time 850 600 850 600 850 600 ps

t

SKEW

Within-Device Skew ps 1

LEN, MR 75 75 75

D to Q 75 75 75

D to ODDPAR 200 200 200

t

r

Rise/Fall Times ps

t

f

20 - 80% 300 500 800 300 500 800 300 500 800

1. Within-device skew is defined as identical transitions on similar paths through a device.

FUNCTION TABLE

D EN MR Q ODDPAR

H L L H H if odd no. of Dn HIGH

L L L L H if odd no. of Dn HIGH

X H L Q

0

Q

0

X X H L L

Loading...

Loading...