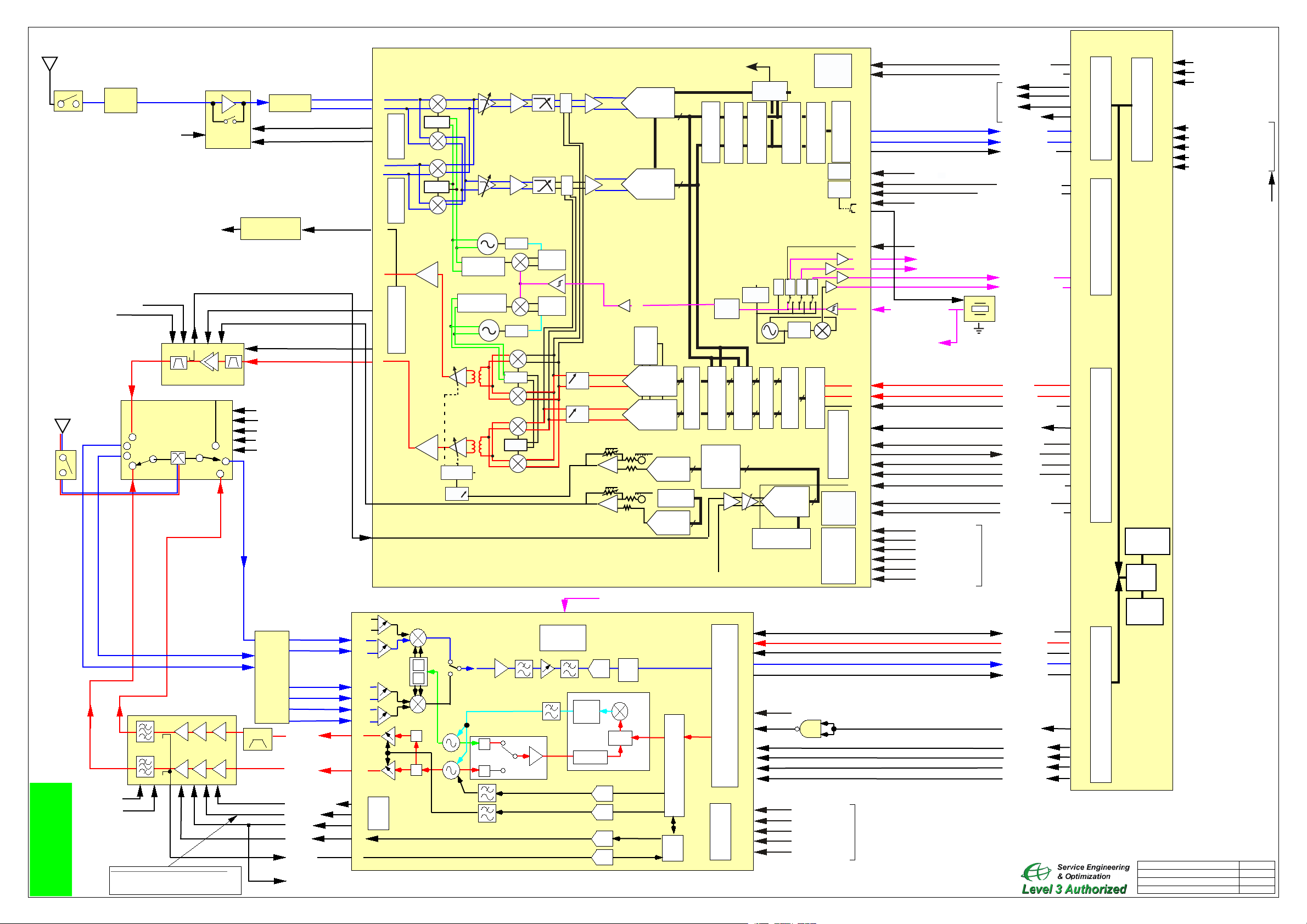

Page 1

Antenna

C2

Antenna

M1

M001

P1

M002

C1

C2

C1

VRF_TX_2_775V

K3_K3m

FL001

2100_PREFILT_OUT

21

VRF_RX_2_775V

(to Atlas)

TEMP_SENSE

VRF_TX_2_775V

BATT+

PA_2100_RF_OUT

14 16132

8

PASSKEY 5W

7

U001

FEM

9

8

14 17

DCS_PCS_OUT

6

5

18

PA_BATT+

PA Power Control selection via VRAMP, TX_HB and TX_LB

1. IPC: Input Power Control mode - for EDGE mode

(PA gain is fixed and PAinput power varies)

2.BCM: Bias Control mode - for GMSK mode

(PA gain varies according to power step and fixed input PApower)

21

EGSM_OUT

DCS_RX

PCS_RX

16

14

10

6

11

U400

10

GSM PA

(U800)

17

15

U300

2

NC

2

5

4

3

6

26

25

9

3

2

FL300

8

7

U495

3

TEMP Sensor

(high & low power selection)

(analog bias adujst voltage)

15

18

VRF_RX_2_775V

FE1(ARGON)

FE2(ARGON)

FE3(ARGON)

FEM_LATCH(ARGON)

11

EGSM_RX

SAW

FILTER

10

4

11

3

1

FL500

12

13

14

15

4

FL801

2

RX_WB_2100_NEG

4

RX_WB_2100_POS

6

LNA_GAIN

LNA_ENABLE

TEMP_SENSE_EN

4

PA_VDET

PASSKEY_VLD

PA_VBA

PA_2100_EN

TX_WB_2100

TX_LB_IN

TX_HB_IN

LB_HB_SWITCH

IPC_BCM

TX_EN

VRAMP

VDETECT

(to Atlas)

TX_EN

NC

NC

D12

E12

G12

H12

K12

L12

L8

L10

C3

B2

A1

B3

A4

NC

NC

NC

NC

L12

J13

J14

F10

A4

C9

F11

E1

D10

D12

CTL

L5

L6

LNA Control

H1

J1

LNA Control

TX Seq. Manager

Tx_AOC_DAC_1

Tx_AOC_ADC_Det_In

U1000 / Argon LV

Mixer

Quad

Quad

LB

HB

Mixer

Gain

Tx

L

PF

A

GC

A

PMA

FracN Div

FracN Div

Ct

rl

GC

RX

Mstr

Cntl

Clock

Cntl

(2.4 to 2.8 vdc)

Base Band

TX

S

equence

Manager

POWER

H12

G12

(to FEM)

G14

H14

Translator

G13

Parallel to Serial

K14

J15

D11

J10

F12

H15

G15

RESET_B

J9

VRF_TCXO_2_775V

(Enable)

BT_CLK_REQ_B

REF_CLK

APPS_CLK

(from Atlas)

(to U5600-BT IC)

(to FL2301 - Flip)

TCXO_Ref_Out

4

J11

TCXO_OUT_CLK

3

GSM_TCXO

E14

B14

D14

F15

D15

C15

C14

D13

SPI & Control Interface

A12

A11

A13

VRF_TX_2_775V

VRFCP_2_775V

VHVIO_2_2_775V

VRF_LVIO_1_875V

VRF_TCXO_2_775V

VRF_RX_2_775V

C10

C3

G7

D8

J9

F5

to LNA Control

Rx_I+

x

u

m

Rx_I-

Rx_Q+

x

u

m

Rx_Q-

R x ’I’ Ch

10 bit S igma-D

A-D C onv

R x ’Q’ Ch

10 bit S igma-D

A-D C onv

´I´/`Q` Channel

Decimation Filter

AGC

C ontroller

Digital

Detection

Selectivity

D.C. offset

U100

To AUX

Comp. Loop

I/Q Gain & Phase

Sequence

Manager

SPI

Prep for CSP

Level & Sampling

WCDMA Tranceiver

“SYMPHONY”

R

x V

Tx

CO

L

VCO

LPF

Div 2

Div 2Div 2

PF

Rx CP

T

x CP

Tx_I+

Tx_I-

LPF

Tx_Q+

Tx_Q-

LPF

_CTx _Ga in

26 MHz TCXO

12 bit S igma-D

12 bit S igma-D

Gain

-

+

Gain Offset

-

+

Tx

DAC

Bias

Gen

Xmit ’I’ C h

DAC

DAC

Xmit ’Q’ Ch

DAC

Offset

Tx PA_Bias

Tx PA_Bias

GSM_TCXO

10 bit

DAC

PA Bias

Register

10 bit

DAC

’I’ Feedback

’Q’ Feedback

184.32 MHz

10

10

Interpolation

Valid

Ref In

Counter

I/Q Gain &

AOC

Digital

Loop

Ctlr / Fltr

Equalizer Phase

+

-

ToData Clk Recov

Freq

Doubler

DC Offset Correction

+

-

BB Input Atten.

/N/N

Frac_N

Divider

Xmit Data

FIR Filter

Word Mux

R x ’I’ C h

10 bit Sigma-D

A-D Conv

ADC

AOC

Gen

Bias

/N /N

Translator

Serial to Parallel

Tx_AOC_ADC_Ref_In

C12

NC

RX_SLOT_WB

RX_WARMUP_WB

FE1

FE2

FE3

FEM_LATCH

RX_I_WB

RX_Q_WB

RX_FRAME_WB

APPS_CLK_EN_B

ARGON_REF_CLK_EN_B

(from BT-IC)

WB_CKIH_CLK

ARGON_REF_CLK

Y190

26MHz

2

TX_I_WB

TX_Q_WB

TX_FRAME_WB

STBY_WB

SPIWB_CLK

SPIWB_DR

SPIWB_DW

SPIWB_CS

AOC_PWR_UP_DN

TX_SLOT_WB

TX_WARMUP_WB

(from Atlas)

U28

T27

AA28

AA27

AB28

V28

U24

U23

T26

AC28

R26

R28

R24

T24

T23

T28

V24

V27

W28

Y28

Y23

AA24

W24

V26

TIMER

RX BB

WBCDMA

RESET and CLOCK

TX BB

WBCDMA

SPI

GPIO

Timer

DSP / Control BUS

K5

TIMER

/4

/2

/2

/3

GSM/ EDGE Tranceiver

ADC

TX/RX

CP

/5 OR /6

/2

/3

DAC

DAC

DAC

ADC

U500

“TransAAM”

VLIF

RX

FracN

RX_IQ

MOD

PWR

CTL

D1

E3

RX / TX

F3

BB

G2

E2

TX

TX_IQ

Timer

B9

G1

RESET_B

(from Atlas)

(Strobe)

G3

G12

Control

H12

SPI

K12

Power

C5

H2, C1

J5, B4

J8

C10

VRF_BG_1_2V

VRF_LVIO_1_875V

VRF_RX_2_775V

VRFCP_2_775V

VRF_TX_2_775V

(from Atlas)

SSI_TX_FRAME

SSI_TX_DATA

SSI_TX_CLK

SSI_RX_DATA

SSI_RX_CLK

STBY_MBU590

SPIMB_DR

SPIMB_CLK

SPIMB_DW

SPIMB_CS

J24

J23

J27

L28

J28

N27

N26

N28

P27

N24

GSM BB

Timer

SPI

J9..

N23..

AA13..

POWER

AA15

AB6..

M26..

L3..

C22..

STARCORE

IPCM

M*CORE

REVISIONS

Service Engineering & Optimization

Level 3 Block Diagram

K3_K3m

Service Training and Documentation

VARGON_CORE

VARGON_PLL

VARGON_HVIO

VARGON_PWRCUT

VARGON_LVIO

VCCQ_IO_SDRAM_FLASH

VFLASH_CORE

VSDRAM_CORE

2007.05.04

Rev.1 .0

Page 1 of 2

SW2_OUT

(from Atlas)

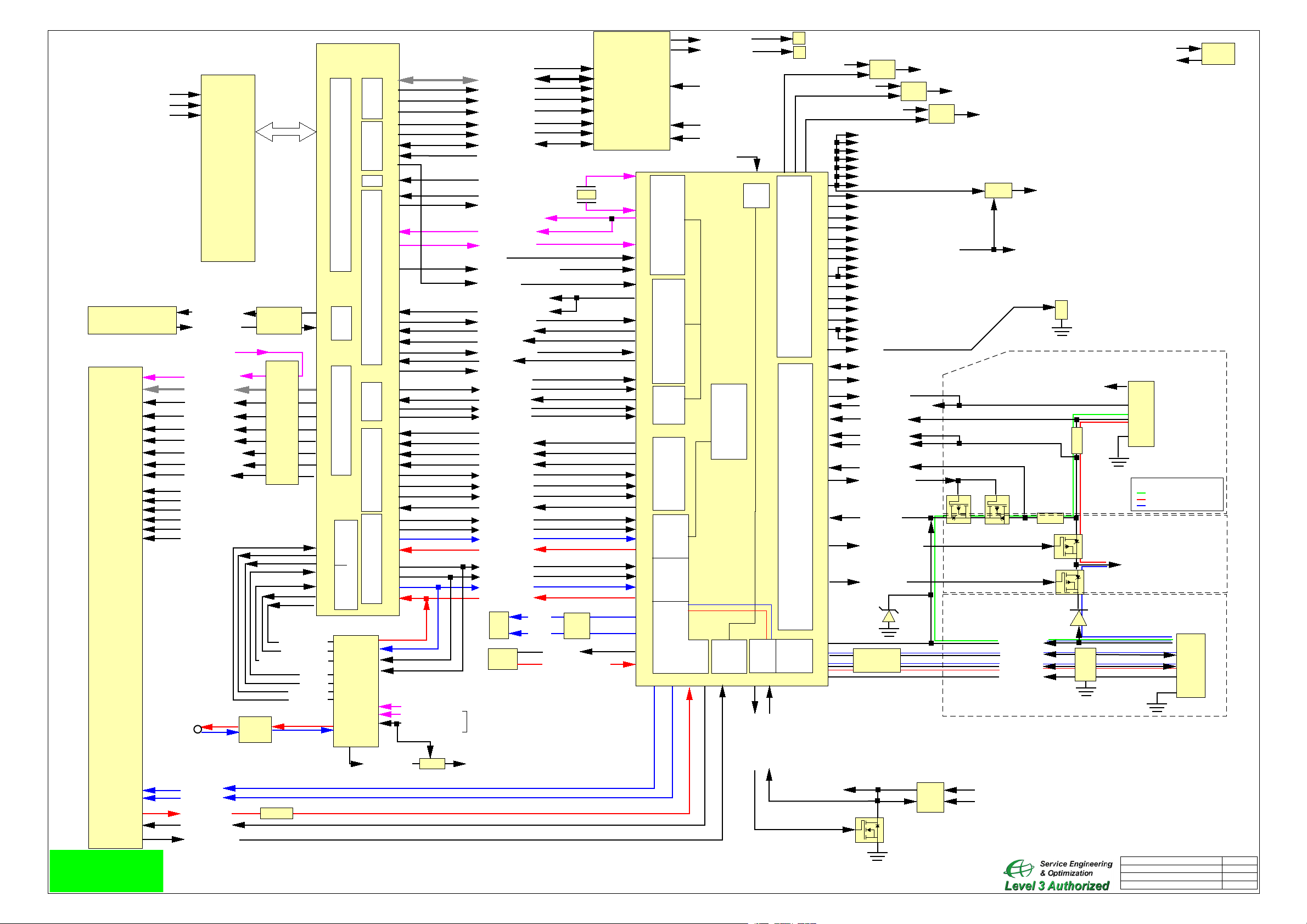

Page 2

VFLASH_CORE

VSDRAM_CORE

VCCQ_IO_SDRAM_FLASH

Keyboard Matrix

0-9, *, #, 5-Way Navigation,

Side Buttons

J2370

48

41,...

30

28

24

26

22

32

34

13,15

3,5

9

19

52

18

Board to Board Conector (Flip)

-50 pin-

(from U100)

GPU_EXT_CLK

IPU_READ_B

IPU_A2

IPU_CS_B

B+

VCAM

VHVIO_2_775V

VLVIO_1_8V_IPU

VGPU_CORE_1_5V

USB_PWR

P5801

BT RF

Connector

U1300

64MB NOR Flash, 64MB NAND Flash, 64MB SDRAM

Triple-Stack Memory

KPR_ROW(7:0)

KPR_COL(7:0)

APPS_CLK

IPU_LD(15:0)

IPU_WRITE_B

IPU_INT_B

IPU_RESET_B

IPU_IND_ADDR

2

FL5600

POP

ESD Protection

VS5100 VS5103

FL2370

FL2371

FL2372

FL2373

BT_REG_CTL

BT_WAKE_B

BT_HOST_WAKE_B

BT_RX

BT_TX

BT_CTS_B

BT_RTS_B

RFIO_N

1

Argon LV

U1000

External Memory Interface

AF11...

AC10....

AD3,...

U1

T5

A25

B24

A24

U2

V6

AF27

URAT1GPIO

AB24

AE27

AD24

AF25

AD23

AH24

U5600

B3

B5

B6

B8

B9

C8

C9

H1

TP5100

TP5101

T18

H18

K17

V13

C12

E3

V11

U11

G18

G3

G2

C11

K2

B6

E2

C16

K13

G8

M14

D15

A14

C14

B17

C18

B19

A12

B15

D3

D2

C2

F7

EL Panel

B+

Q3300

Driver

B+

VFLASH_CORE

VSDRAM_CORE

VCCQ_IO_SDRAM_FLASH

VARGON_LVIO

VARGON_PWRCUT

VDIG_1_8V

VLVIO_1_8V

VBOOST

VARGON_CORE

VIOLO_REG_1_8V

VATLAS

VSIM

VCAM

VMELODY_CORE

VARGON_PLL

VGPU_CORE_1_5V

VRF_TCXO_2_775V

VRFCP_2_775V

VRF_BG_1_2V

VRF_LVIO_1_875V

VHVIO_2_775V

VARGON_HVIO

VVIB

COIN_CELLL

BATTDET_B

ATLAS_GPO1

BATT_TEMP_SENSE

BATT+_RAW

BPSENSE

BATTISENSE

CHRGISNSP

CHRG_CTRL_2

CHRGRAW

BATTFET_CTRL_2

BPFET_DRV

VS5000

(16V)

1

FL5000

4

VRF_RX_2_775V

Q3350

Driver

B+

(5V)

(Atlas internal use only)

(to Daughter Board - SIM VCC)

(2.8V,to Flip - Camera VCC)

Q3400

Driver

(1.8V)

(1.8V)

(1.8V)

(1.5, to U1000 - PLL VCC)

(to U100 - VCC)

(to Flip - VCC)

(from/to BT5400)

(to Argon)

(1.8V)

(1.8V)

(to Argon - Core VCC)

(1.225 - 1.6V CPU speed)

(Atlas internal use only)

(to U100 - VCC)

(to Flip - Graphic Proc. VCC)

(to U100 - Reference Clock VCC)

(to U100 - Charge Pump VCC)

(to U100+ U1000 RF VCC)

(2.775V)

(Bias)

G

S

USB_PWR

2

3

(VCC to RF Section)

VRF_TX_2_775V

VMMC_2_9V

Q2550

Switch

Q3712

Q3713

G

D

D

(VCC to RF Section)

(VCC to Daoughter Board)

(enable)

(OWB to Argon)

S

USB_PWR

USB_DM

USB_DP

USB_ID

VLVIO_1_8V_IPU

J4401

1

VIB

2

BATT_DAT

R5424

BATT+

R3712

D

G

D

G

S

(to Flip)

Q3711

S

Q3710

VS5001

(to Argon)

Battery Con.

B+

VHVIO_2_775V

FLIP_DETECT

J5400

3

2

4

1

Color definition for charge part

Main Charge Path

B+ support without ext. Charger

B+ support with ext. Charger

Dual Path

Charger

EMU

J5000

1

2

3

4

5

U5110

Hall Switch

MINIUSB

J5600

(from Atlas)

VMMC_2_9V

AG6

AD8

AH7

MMC

Memory

Y27

B23

A23

F21

SIM

AC22

AC21

AB27

Batt

AC2

AC24

A21

AG23

(from U500 TransAAM)

R26

B21

F24

Keypad

IPU

D7

AG26

AG25

GPIO, Reset & Clock

AF23

B22

H23

AH18

AD18

AG18

PRI SPI

CNTL.

AC17

M24

E28

D27

G23

F23

D28

USB/RS232

E27

AF22

AD19

AC19

AH21

AG21

AD20

AF20

Bluetooth

AH22

Serial Audio Port

AC20

D9

E8

D8

F8

BlueTooth

J5

A5

H9....

REF_CLK

PERIPH_32K_CLK

VLVIO_1_8V

(from U495/RF)

(from Symphony)

SD1_DATA(3:0)

SD1_CLK

SD1_CMD

SD1_DET_B

USIM_RST

USIM_CLK

USIM_IO

BATTDET_B

BATT_DAT

FLIP_DETECT

(to J5600)

ELEN1

PERIPH_32K_CLK

PROC_32K_CLK

BB_SYS_CLK

TX_EN

ARGON_REF_CLK_EN

VSIM_EN

PERIPH_RESET_B

PROC_RESET_B

POWER_DVS0

POWER_RDY

LOBAT_B

WATCHDOG_B

PM_INT

VFUSE_EN

TEMP_SENSE

BB_SPI_MOSI

BB_SPI_MISO

BB_SPI_CLK

PM_SPI_CS

VARGON_FUSE

USB_VMIN

USB_VPIN

USB_XRXD

USB_VPOUT

USB_VMOUT

USB_TXEN_B

USB_XCVR_EN

MMSAP_FS

MMSAP_CLK

MMSAP_TX

MMSAP_RX

ASAP_CLK

ASAP_FS

ASAP_TX

ASAP_RX

2

J4200

1

4

MK1

1

(from Atlas)

(from Batt, OWB)

(from Hall Sensor)

(to U3600)

(from U3600)

LSPM

LSPP

MIC1_BIAS

ATLAS_MIC1_INPUT

3

U4400

4

27

18,20,22,24

28

14

10

7

13

9

(Standby)

2

1

Y3810

32KHz

1

2

8

17

25

21

Daughter Board Conector

(USIM, EL circuit,

Transflash

V16

V14

R14

L6

Timer, ClockGPIO / Reset

N15

H14

R14

G16

J15

U17

N14

F17

P5

U15

N8

P7

N5

N6

PRI SPI

B2

B3

B5

C5

C6

USB/RS232

C4

C3

M2

16 Bit

M8

Stereo

M3

SAP

M5

M7

13 Bit

M9

L5

SAP

M6

V4

V5

R2

V2

Audio Multiplexer,

V9 V10 U2 P3

EL_PANEL_VA

EL_PANEL_VB

ELEN1

B+

VSIM

VHVIO_2_775V

ON_OFF_END_B

(from Keyboard)

Atlas

U3000

CNTL.

LED

Amplifier

Driver

D13

(from Argon)

(from Atlas)

Logic Control

(from Atlas)

E16

ON

Logic

G9 V18

VFUSE_SELECT

K8J6L7

Power supplies

Charge Control

USBEMU

OTG

VFUSE_SENSE

4

6

12

10

16

K3_K3m

EAR_SP+

EAR_SP-

MIC2_INPUT

MIC2_BIAS

CHARGE_LED

FL4150

BT_CLK_REQ

U5615

BT_CLK_REQ_B

(to U100)

(to Argon)

VARGON_FUSE

Q3600

(FB)

U3600

C1

A3

C3

A1

VBOOST

VFUSE_EN

(VCC)

(enable)

REVISIONS

Service Engineering & Optimization

Level 3 Block Diagram

K3_K3m

Service Training and Documentation

2007.05.04

Rev.1 .0

Page 2 of 2

Loading...

Loading...