Page 1

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

A780 Quad-Band EDGE / GPRS GSM Phone

Hardware INTERFACE DOCUMENT

Motorola, Inc.

Personal Communication Sector

Beijing Design Center

A780 Hardware Team

August 2nd, 2003

08/02/2003 Motorola Confidential Proprietary 1 / 126

Page 2

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

1. Revision History.......................................................................................................... 12

2. Purpose / Introduction................................................................................................ 13

3. PCAP2 Hardware Overview......................................................................................14

3.1 Power Management.............................................................................................. 15

3.1.1 Switching & Linear Regulators Default Configuration............................. 15

3.1.2 Regulator Usage Description ........................................................................ 16

1) V1 Linear Regulator....................................................................................... 16

2) V2 Linear Regulator....................................................................................... 16

3) V3 Linear Regulator....................................................................................... 16

4) V4 Linear Regulator....................................................................................... 16

5) V5 Linear Regulator....................................................................................... 16

6) V6 Linear Regulator....................................................................................... 17

7) V7 Linear Regulator....................................................................................... 17

8) V8 Linear Regulator....................................................................................... 17

9) V9 Linear Regulator....................................................................................... 17

10) V10 Linear Regulator................................................................................... 17

11) VAUX1 Linear Regulator............................................................................ 17

12) VAUX3 Linear Regulator............................................................................ 18

13) VAUX4 Linear Regulator............................................................................ 18

14) SW1 Switching Regulator............................................................................ 18

15) SW2 Switching Regulator............................................................................ 18

16) SW3 Switching Regulator............................................................................ 18

3.1.3 Power Distribution Tree................................................................................ 19

3.1.4 A780 Power Management Control............................................................... 21

3.2 A780 Audio System and PCAP2 Audio Section................................................. 26

3.2.1 A780 Audio System Architecture Block Diagram ...................................... 26

3.2.2 Audio Input Section....................................................................................... 28

3.2.3 Audio Output Section.................................................................................... 29

3.2.4 A780 Audio Routing and SPI Control ......................................................... 30

3.3 A/D Conversion And Channel Allocations......................................................... 31

3.3.1 Detailed Description Of Each A/D Channel................................................ 34

08/02/2003 Motorola Confidential Proprietary 2 / 126

Page 3

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

1) Li-Cell Battery A/D (AD1)............................................................................. 34

2) BATT_SENSE A/D (AD2) ............................................................................. 35

3) B+_SENSE A/D (AD3)...................................................................................35

4) MPB_SENSE A/D (AD4) ............................................................................... 35

5) BATT_THERM A/D (AD5)...........................................................................35

6) CHRG_ID (AD6) ............................................................................................ 37

7) Touch Panel AD (AD11 ~ AD14)................................................................... 37

3.3.2 A780 Charge Operation Description............................................................ 37

4. Neptune-LTE Logic Interfaces.................................................................................. 37

4.1 Neptune IC Description........................................................................................38

4.2 Neptune IC Features.............................................................................................38

4.3 Neptune Functional Summary............................................................................. 38

4.3.1 DSP.................................................................................................................. 38

1) DSP Memory................................................................................................... 39

2) SP BIST (DBIT).............................................................................................. 39

3) DSP Program Paging...................................................................................... 39

4) DSP Peripherals..............................................................................................40

5) Baseband Port Module (BBP) ....................................................................... 40

6) Layer1 Encryption Module (LEM)...............................................................40

7) DSP Timer Module (DTIMER).....................................................................40

8) Serial Audio CODEC Port (SAP).................................................................. 40

9) Direct Memory Access Controller (DMA) ................................................... 40

10) Viterbi Accelerator (VIAC)......................................................................... 40

11) DSP Special Interrupt Handler (DSIH)...................................................... 41

12) SP On Chip Emulator Debug Module (OnCE) ......................................... 41

13) DSP Debug Module (PDDM).......................................................................41

14) Voice CODEC (VOCOD)............................................................................. 41

15) DSP Clock Generator (DCLKG)................................................................. 42

16) IC Identification Module (IIM)................................................................... 42

17) Clock Monitor (CMON)............................................................................... 42

18) Power On Reset (POR)................................................................................. 42

08/02/2003 Motorola Confidential Proprietary 3 / 126

Page 4

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

19) System JTAG Controller (SJC)................................................................... 42

4.3.2 ARM7 MCU ................................................................................................... 43

4.3.2.1 MCU Memory ......................................................................................... 43

4.3.2.2 MCU Peripherals....................................................................................43

1) ARM7 Platform Core Arbiter (CARB).................................................... 43

2) ARM External Interface Module (AEIM)................................................ 43

3) ARM Peripheral Interface Gasket (APIG)..............................................44

4) ARM IPBus Interface (AIPI)..................................................................... 44

5) Alternate Master Arbiter (AMARB)........................................................ 44

6) Multiple Queue Serial Peripheral Interface (MQSPI)............................44

7) ARM7TDMI-S Interrupt Controller (AITC) .......................................... 44

8) SIM Interface Modifications (SIM) .......................................................... 44

9) Universal Asynchronous Receiver Transmitter (UART)........................ 45

10) Deep Sleep Module (DSM).......................................................................45

11) Watchdog Timer (WDOG)...................................................................... 45

12) General Packet Radio Service Encryption Module (GEM).................. 45

13) Keypad Port (KPP)................................................................................... 45

14) Enhanced General Purpose Timer (EGPT)........................................... 45

15) Test Control Module (TCM) ................................................................... 46

16) MCU Watchpoint (AWPT)......................................................................46

17) USB Digital Phase Locked Loop (REFPLL)..........................................46

18) Real Time Reference (RTR) .................................................................... 46

19) Real Time Clock (RTC) ........................................................................... 47

20) Display Memory Access Controller (DMAC)........................................47

21) Clock Control Module (CCM)................................................................. 47

22) External Interrupt Module (INT)........................................................... 47

23) Analog to Digital Interface (A2DIGL)....................................................47

4.3.3 Shared Peripherals......................................................................................... 48

4.3.3.1 Patch RAM (MXRAM) .......................................................................... 48

4.3.3.2 Universal Serial Bus Module (USB)...................................................... 48

4.3.3.3 General Purpose I/O (GPIO)................................................................. 48

08/02/2003 Motorola Confidential Proprietary 4 / 126

Page 5

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

4.3.3.4 MCU / DSP Interface (MDI)..................................................................48

4.3.3.5 Layer 1 Timer (L1T)............................................................................... 48

4.4 Neptune GPIO Summary..................................................................................... 49

4.5 Neptune-LTE Memory Interface......................................................................... 52

4.5.1 Flash................................................................................................................ 52

4.5.2 SRAM..............................................................................................................54

4.5.3 Neptune-LTE Chip Select Assignments....................................................... 54

4.6 Neptune MQSPI Module......................................................................................56

4.7 SIM Interface ........................................................................................................ 59

5. Neptune-LTE RF Interface........................................................................................62

5.1 RF6003 (Fractional-N RF Synthesizer) Chipset Description............................ 62

5.1.1 RF6003 Functional Description.................................................................... 62

5.1.2 RF6003 Serial Data Interface and Device Control ..................................... 63

5.2 RF2722 (GPRS / EDGE Receiver) Chipset Description.................................... 66

5.2.1 RF2722 Functional Description.................................................................... 66

5.2.2 RF2722 Serial Data Interface and Device Control ..................................... 67

5.3 RF3144 (Quad-Band Power Amplifier Module) Chipset Description............. 68

5.4 A780 RF System Signaling................................................................................... 69

5.4.1 RF System Block Diagram............................................................................ 69

5.4.2 Description of RF Signal and Interface ....................................................... 71

1) Antenna Switching Control........................................................................ 71

2) Digital RX Signal Interface........................................................................ 72

3) Digital TX Signal Interface........................................................................ 72

4) RF SPI Port Interface.................................................................................72

5) RF Control Related Signals........................................................................ 73

6) Neptune-LTE RF Related Signals............................................................. 74

6. AGPS Module Interface.............................................................................................75

6.1 AGPS Functional Block Diagram ....................................................................... 75

6.2 AGPS Interface Descriptions............................................................................... 75

6.2.1 AGPS_NRESET.............................................................................................76

6.2.2 UART Interface.............................................................................................. 76

08/02/2003 Motorola Confidential Proprietary 5 / 126

Page 6

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

6.2.3 Miscellaneous Signals .................................................................................... 77

6.2.4 AGPS Operation Mode Descriptions........................................................... 77

6.2.4.1 Boot Mode Operation............................................................................. 77

6.2.4.2 Tracking Mode Operation ..................................................................... 78

6.2.4.3 Sleep Mode Operation............................................................................ 78

6.3 AGPS Clock System.............................................................................................. 78

6.3.1 Reference Clock (24.5535MHz TCXO)........................................................ 78

6.3.2 RTC Clock (32.768KHz) ............................................................................... 78

6.4 AGPS Power On / Off Sequence.......................................................................... 78

7. Application Processor (Bulverde).............................................................................. 80

7.1 Bulverde Functional Overview............................................................................ 80

7.2 Bulverde Memory Interface.................................................................................82

7.2.1 Bulverde SDRAM Interface..........................................................................82

7.2.2 Bulverde Flash Interface............................................................................... 84

7.3 Bulverde GPIO Assignment................................................................................. 85

7.3.1 Bulverde GPIO Operation as Application-specific GPIO ......................... 85

7.3.2 Bulverde GPIO Operation as Alternate Function...................................... 87

7.3.3 Bulverde GPIO Operation as A780 Function ............................................. 91

7.4 A780 Keypad And Its Backlight Interface.......................................................... 95

7.4.1 Keypad Interface............................................................................................ 95

7.4.2 Keypad Backlight Interface.......................................................................... 99

7.5 A780 LCD Module Interface.............................................................................. 101

7.6 Bulverde Peripherals Interface.......................................................................... 108

7.6.1 Blue Tooth Module ...................................................................................... 109

7.6.2 Digital Camera............................................................................................. 110

TM

7.6.2.1 OmniVision

7.6.2.2 OmniVision

1.3MegaPixel Module Features................................ 111

TM

1.3MegaPixel Functional Description...................... 112

7.6.2.3 A780 Digital Camera Hardware Architecture................................... 113

7.6.2.4 A780 Digital Camera Operation Mode Description..........................115

7.6.3 Tri-Flash Card ............................................................................................. 116

8. A780 System Architecture Description...................................................................120

08/02/2003 Motorola Confidential Proprietary 6 / 126

Page 7

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

8.1 A780 System architecture block diagram.........................................................120

8.2 A780 Interconnection Link between Neptune-LTE & Bulverde (ICL).........121

8.3 A780 Clock System Control............................................................................... 123

8.3.1 Neptune-LTE Related Clock Signal........................................................... 123

8.3.2 RFMD Related Clock Signal....................................................................... 124

8.3.3 Bulverde Related Clock Signal................................................................... 124

8.3.4 Bluetooth Related Clock Signal.................................................................. 124

8.3.5 AGPS Related Clock Signal........................................................................ 125

8.3.6 PCAP2 Related Clock Signal...................................................................... 125

9. EMU Bus and A780 Accessories..............................................................................126

10. Reference Documentation List............................................................................... 126

08/02/2003 Motorola Confidential Proprietary 7 / 126

Page 8

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

List of Tables:

T

ABLE 1 - DEFAULT PCAP2 REGULATOR VOLTAGE AT PGM [1:0] SETTINGS ................. 15

ABLE 2 – PCAP2 SWITCHING MODE REGULATOR STANDBY CONTROL TRUE TABLE ..... 23

T

ABLE 3 – PCAP2 LINEAR MODE REGULATOR STANDBY CONTROL TRUE TABLE ........... 25

T

TABLE 4 –BULVERDE GPIO ASSIGNMENT FOR AUDIO SSP AND SPI ................................ 27

ABLE 5 – A780 A/D CONVERTER ALLOCATION TABLE .................................................. 34

T

ABLE 6 – BATTERY THERMISTOR READINGS OVER TEMPERATURE................................. 36

T

ABLE 7 – NEPTUNE DSP MEMORY REQUIREMENTS ........................................................ 39

T

ABLE 8 – NEPTUNE GPIO USAGE ASSIGNMENT (PA0 ~ PC7) ........................................ 50

T

TABLE 9 – NEPTUNE GPIO USAGE ASSIGNMENT (PC8 ~ PE15)....................................... 51

ABLE 10 – NEPTUNE-LTE CHIP SELECT ASSIGNMENT .................................................... 54

T

ABLE 11 – RF2722 REGISTER MAP ................................................................................. 57

T

ABLE 12 – RF6003 REGISTER MAP ................................................................................. 58

T

ABLE 13 – SIM CARD PRESENCE DETECT MATRIX ......................................................... 60

T

ABLE 14 – RF6003 SERIAL DATA INTERFACE REGISTER MAP ........................................ 65

T

ABLE 15 – RF2722 SERIAL DATA INTERFACE REGISTER MAP ........................................ 68

T

ABLE 16 – A780 ANTENNA SWITCH CONTROL TRUTH TABLE ........................................ 72

T

TABLE 17 – A780 RFMD CONTROL NEPTUNE-LTE GPIO ASSIGNMENT ........................ 74

ABLE 18 – A780 AGPS AND NEPTUNE-LTE CONNECTION ............................................ 76

T

ABLE 19 – MG4100 AGPS CHIPSET MODE SELECTION.................................................. 77

T

ABLE 20 – BULVERDE GPIO ALTERNATIVE FUNCTION (GPIO [0] ~ GPIO [20]) ........... 87

T

ABLE 21 – BULVERDE GPIO ALTERNATIVE FUNCTION (GPIO [21] ~ GPIO [60]) ......... 88

T

ABLE 22 – BULVERDE GPIO ALTERNATIVE FUNCTION (GPIO [61] ~ GPIO [100]) ....... 89

T

ABLE 23 – BULVERDE GPIO ALTERNATIVE FUNCTION (GPIO [101] ~ GPIO [120]) ..... 90

T

TABLE 24 – A780 BULVERDE GPIO ASSIGNMENT (GPIO [0] ~ GPIO [34]).................... 91

ABLE 25 – A780 BULVERDE GPIO ASSIGNMENT (GPIO [35] ~ GPIO [69]) .................. 92

T

ABLE 26 – A780 BULVERDE GPIO ASSIGNMENT (GPIO [70] ~ GPIO [104])................ 93

T

TABLE 27 – A780 BULVERDE GPIO ASSIGNMENT (GPIO [105] ~ GPIO [120]).............. 94

ABLE 28 – A780 MATRIX SCAN KEY ASSIGNMENT ........................................................ 96

T

TABLE 29 – A780 JOYSTICK SWITCH CONNECTION SCHEME ............................................ 97

08/02/2003 Motorola Confidential Proprietary 8 / 126

Page 9

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

T

ABLE 30 – A780 KEYPAD MATRIX SCAN TABLE ............................................................ 98

ABLE 31 – A780 BULVERDE GPIO ASSIGNMENT OF KEYPAD CONTROLLER .................. 98

T

ABLE 32 – PCAP2 BACKLIGHT DUTY CYCLE CONTROL BIT DEFINITION ..................... 100

T

TABLE 33 – A780 LCD POWER UP TIMING FIGURES....................................................... 103

ABLE 34 – A780 LCD POWER DOWN TIMING FIGURES ................................................ 104

T

ABLE 35 – A780 BULVERDE GPIO ASSIGNMENT OF LCD CONTROLLER ..................... 106

T

ABLE 36 – A780 LCD CONNECTOR PIN-OUT DEFINITION .............................................. 107

T

ABLE 37 – A780 DIGITAL CAMERA SIGNAL FUNCTION DESCRIPTION........................... 114

T

TABLE 38 – A780 DIGITAL CAMERA BULVERDE GPIO ASSIGNMENT ............................ 115

ABLE 39 – TRI-FLASH CARD PIN DEFINITION................................................................ 117

T

ABLE 40 – TRI-FLASH CARD MMC BUS AND SPI BUS COMPARISON ........................... 117

T

ABLE 41 – BULVERDE TRI-FLASH CARD GPIO ASSIGNMENT ....................................... 119

T

ABLE 42 – A780 ICL SIGNALS FUNCTION DESCRIPTION............................................... 122

T

ABLE 43 – BULVERDE 13MHZ CLOCK OUTPUT AT GPIO [9] SETTING BIT................... 124

T

08/02/2003 Motorola Confidential Proprietary 9 / 126

Page 10

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

List Of Figures

FIGURE 1 – A780 POWER DISTRIBUTION TREE DIAGRAM ............................................................................ 20

IGURE 2 – A780 POWER MANAGEMENT CONTROL DIAGRAM..................................................................... 21

F

F

IGURE 3 – A780 BULVERDE SLEEP AND OPERATION MODE POWER SUPPLY CONTROL.............................. 22

IGURE 4 – PCAP2 SWITCHING MODE REGULATOR STANDBY CONTROL .................................................... 23

F

F

IGURE 5 – PCAP2 LINEAR MODE REGULATOR STANDBY CONTROL .......................................................... 24

IGURE 6 – A780 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM........................................................... 26

F

F

IGURE 7 – PCAP2 AUDIO INPUT SECTION BLOCK DIAGRAM...................................................................... 28

IGURE 8 – PCAP2 AUDIO OUTPUT SECTION BLOCK DIAGRAM .................................................................. 29

F

F

IGURE 9 – A780 AUDIO ROUTING AND SPI CONTROL BLOCK DIAGRAM.................................................... 30

IGURE 10 – PCAP2 A/D CONVERSION TIMING DIAGRAM WITH AD_SEL = 0 ........................................... 31

F

F

IGURE 11 – PCAP2 A/D CONVERSION TIMING DIAGRAM WITH AD_SEL = 1 ........................................... 32

IGURE 12 – BATTERY THERMISTOR CONNECTION BLOCK DIAGRAM.......................................................... 36

F

F

IGURE 13 – A780 BASEBAND 64W18 + 8MB SRAM STACKED-CSP BLOCK DIAGRAM ........................... 52

IGURE 14 – A780 BASEBAND NEPTUNE-LTE AND MEMORY CONNECTION BLOCK DIAGRAM ................... 55

F

IGURE 15 – NEPTUNE MQSPI CONNECTION WITH PCAP2 AND RF6003 BLOCK DIAGRAM ....................... 57

F

IGURE 16 – A780 SIM CONNECTION BLOCK DIAGRAM.............................................................................. 59

F

IGURE 17 – A780 SIM PRESENT DETECTION CIRCUIT LOGIC BLOCK DIAGRAM ........................................ 60

F

IGURE 18 – R6003 FUNCTIONAL BLOCK DIAGRAM .................................................................................... 63

F

IGURE 19 – R6003 SERIAL DATA INTERFACE TIMING DIAGRAM ................................................................ 64

F

IGURE 20 – R6003 SERIAL DATA WRITE SEQUENCE (SINGLE ADDRESS) ................................................... 64

F

IGURE 21 – R6003 SERIAL DATA WRITE SEQUENCE (MULTIPLE ADDRESS)............................................... 64

F

IGURE 22 – R2722 FUNCTIONAL BLOCK DIAGRAM AND PIN OUT.............................................................. 67

F

IGURE 23 – R2722 SERIAL INTERFACE TIMING DIAGRAM .......................................................................... 68

F

F

IGURE 24 – A780 RFMD RF SYSTEM BLOCK DIAGRAM............................................................................ 70

IGURE 25 – A780 QUAD-BAND RF INTERFACE BETWEEN NEPTUNE, RF6003 & RF2722........................... 71

F

IGURE 26 – A780 AGPS FUNCTIONAL BLOCK DIAGRAM........................................................................... 75

F

IGURE 27 – A780 AGPS POWER ON AND OFF SEQUENCE .......................................................................... 79

F

IGURE 28 – BULVERDE PROCESSOR BLOCK DIAGRAM................................................................................ 81

F

IGURE 29 – BULVERDE MEMORY CONNECTION BLOCK DIAGRAM ............................................................. 83

F

IGURE 30 – BULVERDE GPIO PIN FUNCTION BLOCK DIAGRAM ................................................................. 86

F

IGURE 31 – A780 KEYPAD LOCATION DIAGRAM........................................................................................ 95

F

IGURE 32 – A780 KEYPAD INTERFACE BLOCK DIAGRAM........................................................................... 96

F

IGURE 33 – A780 JOYSTICK CONNECTION WITH BULVERDE KEYPAD CONTROL PIN ................................. 97

F

IGURE 34 – A780 JOYSTICK PIN CONNECTION DIAGRAM ........................................................................... 97

F

IGURE 35 – A780 KEYPAD BACKLIGHT CONTROL BLOCK DIAGRAM ......................................................... 99

F

IGURE 36 – A780 LCD MODULE ELECTRICAL BLOCK DIAGRAM ............................................................. 102

F

08/02/2003 Motorola Confidential Proprietary 10 / 126

Page 11

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

FIGURE 37 – A780 LCD MODULE HORIZONTAL READING / WRITING TIMING DIAGRAM .......................... 102

IGURE 38 – A780 LCD MODULE VERTICAL READING / WRITING TIMING DIAGRAM ............................... 103

F

F

IGURE 39 – A780 LCD POWER UP TIMING DIAGRAM .............................................................................. 103

IGURE 40 – A780 LCD POWER DOWN TIMING DIAGRAM ........................................................................ 104

F

F

IGURE 41 – A780 CONNECTION BLOCK DIAGRAM BETWEEN BULVERDE AND LCD MODULE ................. 105

IGURE 42 – A780 BULVERDE PERIPHERALS CONNECTIONS BLOCK DIAGRAM ......................................... 108

F

IGURE 43 – BCM2035 FUNCTIONAL BLOCK DIAGRAM ............................................................................ 110

F

IGURE 44 – OV9640 FUNCTIONAL BLOCK DIAGRAM ............................................................................... 112

F

IGURE 45 – A780 DIGITAL CAMERA SYSTEM ARCHITECTURE BLOCK DIAGRAM ..................................... 113

F

IGURE 46 – A780 DIGITAL CAMERA DETAILED CONNECTION WITH BULVERDE ...................................... 114

F

F

IGURE 47 – TRI-FLASH CARD OUTLINE DIAGRAM .................................................................................... 116

IGURE 48 – TRI-FLASH WITH MMC AND SPI INTERFACE BLOCK DIAGRAM............................................ 117

F

IGURE 49 – A780 TRI-FLASH CARD CONTROL BLOCK DIAGRAM ............................................................. 118

F

IGURE 50 – A780 QUAD-BAND SYSTEM ARCHITECTURE BLOCK DIAGRAM ............................................... 120

F

F

IGURE 51 – A780 QUAD-BAND INTERCONNECTION LINK BETWEEN NEPTUNE & BULVERDE ................... 121

IGURE 52 – A780 CLOCK SYSTEM CONTROL BLOCK DIAGRAM ............................................................... 123

F

IGURE 53 – PCAP2 CLOCK SELECTION OF VOICE PLL AND STEREO PLL BLOCK DIAGRAM .................. 125

F

08/02/2003 Motorola Confidential Proprietary 11 / 126

Page 12

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

1. Revision History

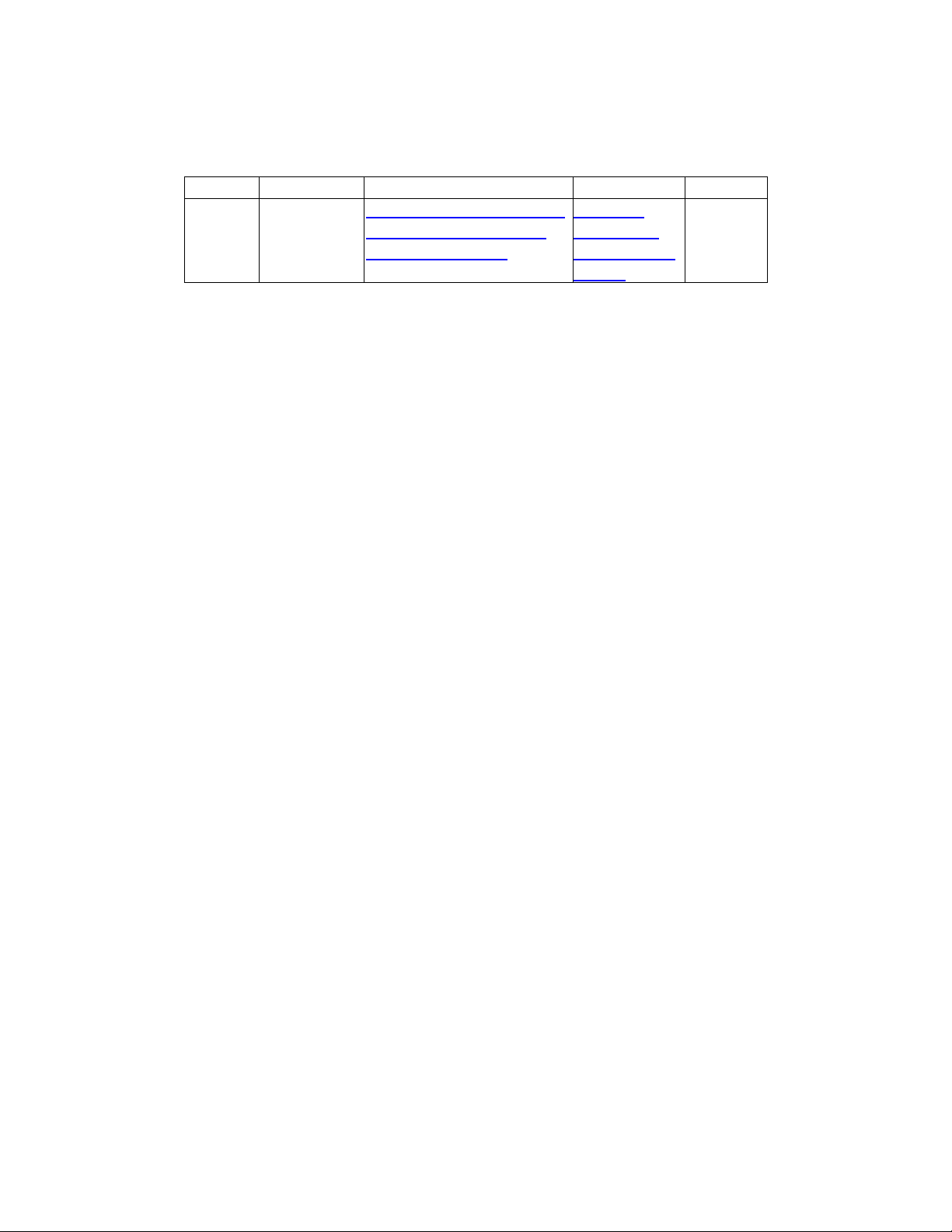

Revision Date Section Author Reason

5. Neptune-LTE RF Interface

0.1 11/12/2003

6. AGPS Module Interface Cevin Wang

7.6.2 Digital Camera Cai Xiaochuan

Other Colin Li

Erin Geng

Initial Draft

08/02/2003 Motorola Confidential Proprietary 12 / 126

Page 13

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

2. Purpose / Introduction

The purpose of this document is to list and define the power supplies and interfaces

between base band and adjunct processor, base band and RF chipset etc for

GSM/DCS/CEL/PCS A780 cellular phone. This phone will bring to market with the

Neptune-LTE IC (base band call processor), Bulverde IC (adjunct application processor),

PCAP2 (Platform Audio Interface and Power Control) IC, as well as the air interface

RF6003 IC and RF3144 power amplifier IC. At the time of designing, the base band call

processor Neptune-LTE core will run at 1.8V while other IC will run at 2.775V. The

memory chipsets connected with Neptune-LTE need to run at 1.875V as well.

In this document, the major chipset features and functionality will be introduced as well

as the dedicated usage in A780 phone design. The interconnections between NeptuneLTE and Bulverde will be introduced in detail. The control signals from Neptune-LTE to

RF6003 and RF2722 will also introduced as well.

08/02/2003 Motorola Confidential Proprietary 13 / 126

Page 14

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

3. PCAP2 Hardware Overview

This section describes the general features of the PCAP2 (Platform

Control/Audio/Power) IC that will be developed for Dakota platform products. The

PCAP2 architecture is derived from previous devices such as GCAP-III and CCAP, with

feature enhancements as needed to support requirements of next-generation mobile

terminals.

The system-level requirements that have created the need for a new PCAP2 device

include the following:

Improved Power Cut/Power Power supply and control for external

Stereo Audio capability for Multimedia support

Dedicated Transceiver power supply

The PCAP2 will also include additional features to improve system efficiency

and reduce external component count such as:

Dual SPI control interface to allow access from two independent base band

processors

Multiple Switch mode power supply controllers for buck and/or boost

conversion

Additional independent, configurable voltage regulators

Enhanced touch screen interface

Improved backlight controller capability

Certain functions that were available on previous devices such as GCAP-II, GCAP-III

will NOT be carried over to the PCAP2 parts due to changes in system requirements or

lack of use on previous products.

These include:

Internal over voltage protection / clamp as implemented in CCAP

Negative voltage generation charge pump

Negative voltage linear regulators

DSC serial communication interface

08/02/2003 Motorola Confidential Proprietary 14 / 126

Page 15

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

3.1 Power Management

3.1.1 Switching & Linear Regulators Default Configuration

PGM0 & PGM1 along determine the power up default switching & linear

regulators’ voltage of PCAP2. Those two pins are also used to determine the

regulators turn on timing. The default voltage of each regulator at PGM [1:0]

settings is shown in Table 1

. A780 use PGM [1:0] = 0:1 as its default setting.

PGM [1:0] 00 01 10 11

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

SW1

SW2

SW3

SW4

VAUX1

VAUX2

VAUX3

VAUX4

VHOLD

VUSB

VUSB_MSTR

VSIM

VSIM2

V_VIB

1.600 2.775 1.875

2.775

1.875

2.775

1.275

2.775

1.875

1.875 2.775 1.875

2.775 2.775 2.775

2.775

1.875

1.875

2.475

5.000

2.250

1.600

5.500

2.775

2.775

1.275

1.575

5.000

1.200

1.875

5.500

2.775

1.875

1.875

2.475

5.000

2.250

1.600

5.500

2.775

2.775

1.550

2.775

2.775

2.775

2.775

1.875

1.575

5.000

1.600

1.875

5.500

OFF OFF OFF OFF

2.775

2.775

1.875

2.775

2.775

2.775

2.775

1.875

OFF OFF OFF OFF

OFF 3.0 OFF OFF

1.550

1.550

1.550

1.550

OFF OFF OFF OFF

OFF OFF OFF OFF

1.875

1.875

1.875

OFF

1.875 OFF

1.875 OFF

OFF OFF OFF OFF

Table 1 - Default PCAP2 Regulator Voltage at PGM [1:0] Settings

08/02/2003 Motorola Confidential Proprietary 15 / 126

Page 16

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

3.1.2 Regulator Usage Description

Regulators of PCAP2 were assigned as dedicated power supplies for Neptune-LTE or

Bulverde side. The functions were listed as below.

1) V1 Linear Regulator

V1 is a programmable linear regulator. It is programmable via the SPI bus to 1.275V ~

2.775V. For A780, V1 is programmed to 2.775V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V

as default. V1 supplies Neptune-LTE interface control data pins, test pins and RF6003,

RF2722 SPI port. V1 is also used to provide I/O voltages to Bulverde sub-system. Some

external level shifters power supplies were also provided by V1. V1 was assigned as label

VAB_IO in A780 schematic.

2) V2 Linear Regulator

V2 is a programmable linear regulator. It is programmable via the SPI bus to 2.500V or

2.775V. For A780, V2 is programmed to 2.775V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V

as default. V2 supplies Neptune internal CODEC circuitry power supply and PCAP2

internal audio related circuitry such as audio amplifiers, microphone bias etc. V2 was

assigned as label V_AUDIO in A780 schematic.

3) V3 Linear Regulator

V3 is a programmable linear regulator. It is programmable via the SPI bus to 1.075V ~

2.275V. For A780, V3 is programmed to 1.275V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 1.275V

as default. V3 supplies the power for Bulverde VCC_SRAM power. V3 was assigned as

label VAP_SRAM in A780 schematic. This regulator can be switched off when Bulverde

entering into sleep mode, the control signal for this is PWR_EN of Bulverde.

4) V4 Linear Regulator

V4 is a programmable linear regulator. It is programmable via the SPI bus to 1.275V ~

2.775V. For A780, V4 is programmed to 2.775V as default. V4 supplies the power for

PCAP2 internal circuitry such as SPI module and RF related circuitry etc. V4 was

assigned as VRF_VCO in A780 schematic. During standby mode of Neptune-LTE

system, V4 should be switch off when Standby pin of PCAP2 asserted.

5) V5 Linear Regulator

V5 is a programmable linear regulator. It is programmable via the SPI bus to 1.275V ~

2.775V. For A780, V5 is programmed to 2.775V as default. V5 supplies the power for

PCAP2 internal circuitry such as SPI module and RF related circuitry etc. V5 was

08/02/2003 Motorola Confidential Proprietary 16 / 126

Page 17

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

assigned as VRF_LNA in A780 schematic. During standby mode of Neptune-LTE

system, V5 should be switch off when Standby pin of PCAP2 asserted.

6) V6 Linear Regulator

V6 is a programmable linear regulator. It is programmable via the SPI bus to 2.475V or

2.775V. For A780, V6 is not used.

7) V7 Linear Regulator

V7 is a programmable linear regulator. It is programmable via the SPI bus to 1.875V or

2.775V. For A780, V7 is programmed to 2.775V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V

as default. V7 supplies to Neptune-LTE, RF6003 & RF2722 RF related circuitries. V7

was assigned as label VRF_TXRX in A780 schematic.

8) V8 Linear Regulator

V8 is a programmable linear regulator. It is programmable via the SPI bus to 1.075V ~

2.275V. For A780, V8 is programmed to 1.275V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 1.275V

as default. V8 supplies the power for Bulverde VCC_PLL power. V8 was assigned as

label VAP_PLL in A780 schematic. This regulator can be switched off when Bulverde

entering into sleep mode, the control signal for this is PWR_EN of Bulverde.

9) V9 Linear Regulator

V9 is a programmable linear regulator. It is programmable via the SPI bus to 1.575V ~

2.775V. For A780, V9 is programmed to 1.575V and is supplied directly by B+. This

regulator is on whenever the radio is turned on, and the initial power-up level is 1.575V

as default. V9 supplies to Neptune LVDD1 as Neptune internal reference voltage. V9

was assigned as label VBB_REF in A780 schematic. This power supply is also connected

with PCAP2 VCC_OUT pin to provide power for PCAP2 internal 32KHz oscillator and

output buffer.

10) V10 Linear Regulator

V10 is an un-programmable linear regulator for its output voltage, but it can be switched

on or off via the SPI port. V10 output at 5.0V and is supplied by SW3. This regulator is

on whenever the radio is turned on, and the initial power-up level is 5.0V as default. V10

is not used in A780 design.

11) VAUX1 Linear Regulator

VAUX1 is a programmable linear regulator. It is programmable via the SPI bus to

1.275V ~ 2.775V. For A780, VAUX1 is programmed to 1.875V and is supplied directly

08/02/2003 Motorola Confidential Proprietary 17 / 126

Page 18

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

by B+. This regulator is on whenever the radio is turned on, and the initial power-up level

is 1.875V as default. VAUX1 supplies Bluetooth core and RF power. VAUX1 was

assigned as label VBT_RF in A780 schematic.

12) VAUX3 Linear Regulator

VAUX1 is a programmable linear regulator. It is programmable via the SPI bus to

1.275V ~ 2.775V. For A780, VAUX1 is programmed to 2.800V and is supplied directly

by B+. This regulator is off when the radio is turned on, and the initial power-up level is

0V as default. VAUX3 supplies power to Tri-Flash card. VAUX3 was assigned as label

VAP_MMC in A780 schematic.

13) VAUX4 Linear Regulator

VAUX4 is a programmable linear regulator. It is programmable via the SPI bus to

1.800V ~ 5.000V. For A780, VAUX4 is programmed to 3.000V and is supplied directly

by B+. This regulator is on whenever the radio is turned on, and the initial power-up level

is 3.00V as default. VAUX4 supplies power to AGPS RF module. VAUX4 was assigned

as label VAP_GAM_RF in A780 schematic.

14) SW1 Switching Regulator

SW1 is a programmable switching regulator. It is programmable via the SPI bus to

0.900V ~ 2.250V. For A780, SW1 is programmed to 1.2V and is supplied directly by B+.

This regulator is on whenever the radio is turned on, and the initial power-up level is

1.20V as default. SW1 supplies power to Bulverde VCC_CORE domain. SW1 was

assigned as label VAP_CORE in A780 schematic.

15) SW2 Switching Regulator

SW2 is a programmable switching regulator. It is programmable via the SPI bus to

0.900V ~ 2.250V. For A780, SW2 is programmed to 1.875V and is supplied directly by

B+. This regulator is on whenever the radio is turned on, and the initial power-up level is

1.875V as default. SW2 supplies power to Bulverde memory system and Neptune-LTE

memory interface. SW1 was assigned as label VAB_MEM in A780 schematic.

16) SW3 Switching Regulator

SW3 is a programmable switching regulator. It is programmable via the SPI bus to 4.00V

~ 5.50V. For A780, SW3 is programmed to 5.5V as default and is supplied directly by

B+. This regulator is on whenever the radio is turned on, and the initial power-up level is

5.50V as default. SW3 supplies power to PCAP2 VBUS_IN as USB OTG host function.

SW3 was assigned as label V_BOOST in A780 schematic.

08/02/2003 Motorola Confidential Proprietary 18 / 126

Page 19

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

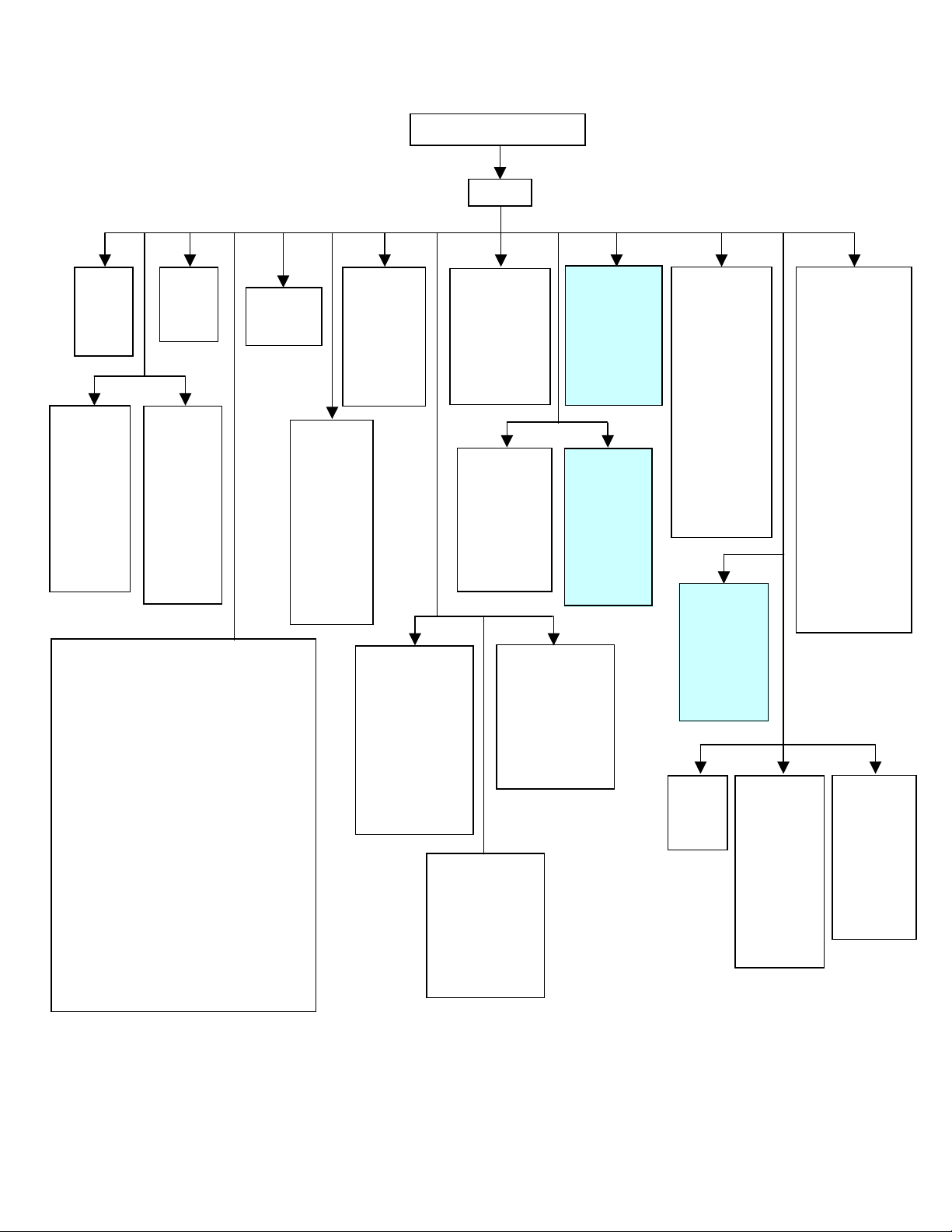

3.1.3 Power Distribution Tree

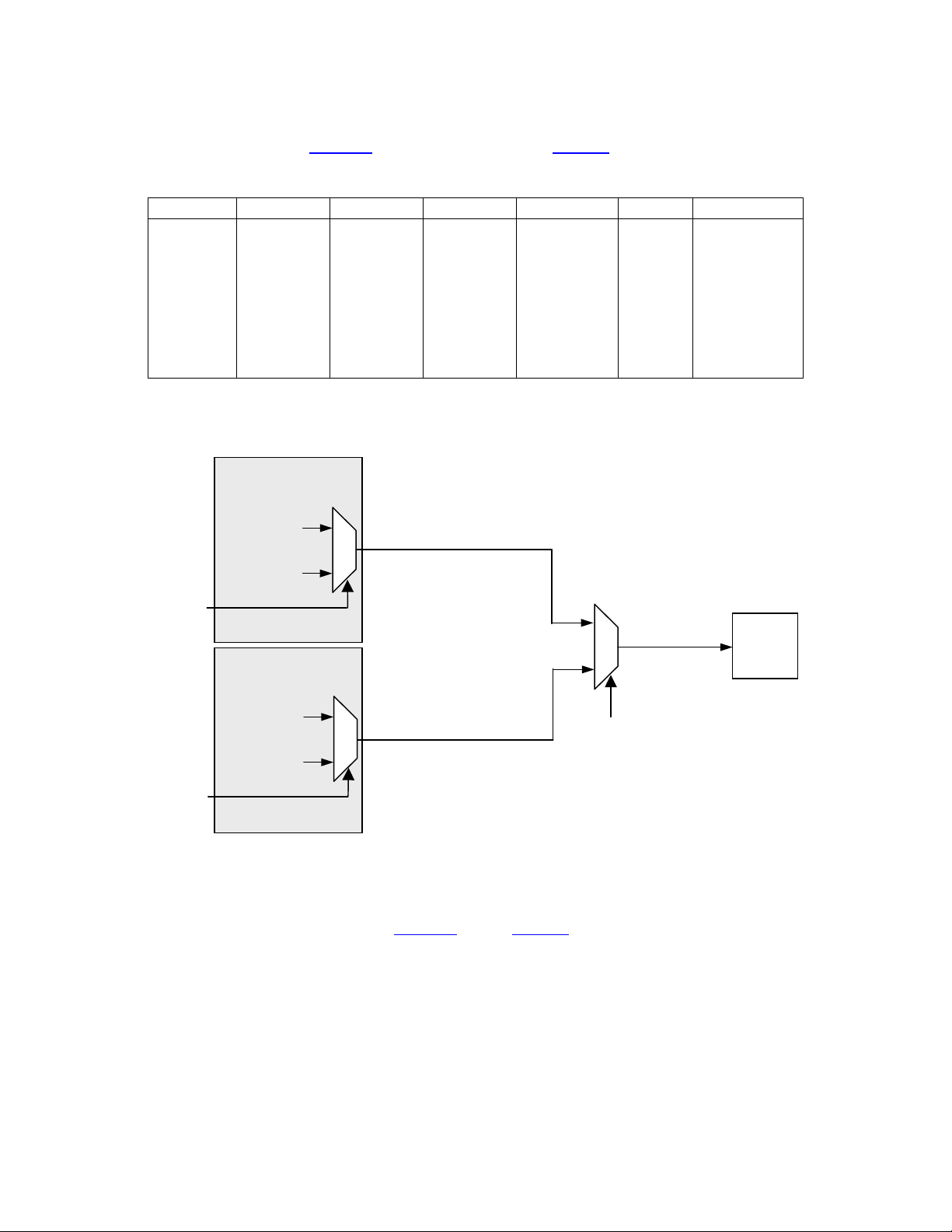

For A780 cellular phone, not all the regulators listed in Table 1

A780 power distribution tree in which all the used regulators load were addressed.

PCAP2 provides all the regulated power supplies to Neptune-LTE subsystem, Bulverde

adjunct processor sub-system, Bluetooth system and AGPS system etc.

are used. Figure 1 shows

08/02/2003 Motorola Confidential Proprietary 19 / 126

Page 20

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

_

_

RF3144

VBATT

PCAP2

V5 (Linear)

VRF_LNA

(2.775V)

RF6003

VDD_RX

RF2722

FLT_VCC

LNA_VCC

Neptune

BVDD

CVDD1

CVDD2

CVDD3

DVDD

EVDD

JVDD

VDDA

Bulverde

VCC_IO

VCC_BB

Hall Effect

Supply

LCD

Module

V

PCAP2

V4 (Linear)

VRF_VCO

(2.775V)

RF6003

VCCV

RF2722

MIX_VCC

LO_VCC

VCO

PCAP2

V1 (Linear)

VAB_IO

(2.775V)

PCAP2

PRISSIVCC

SECSSIVCC

PRISPIVCC

SECSPIVCC

USBDIGVCC

Blue-Tooth

V-I-O

Digital Camera

LCD Module

VDD2

LED

VCC

VCC

VDD1

Single Cell Li-Ion

B+

PCAP2

PCAP2

ALRT_VCC

V9 (Linear)

VBB_REF

(1.575V)

Neptune

LVDD1

PCAP2

SW3 (Boost)

V_BOOST

(5.50V)

PCAP2

IN

VUSB

PCAP2

SW1 (BUCK)

VAP_CORE

(0.9 ~ 1.3V)

Bulverde

VCC_CORE

PCAP2

AGPS

VDD_IO

Other

U602

U604

U605

U606

U401

V7 (Linear)

VRF_TXRX

(2.775V)

Neptune

VDD_TXRX

RF6003

VCC (_PLL)

VDD

RF2722

DIG_VCC

PCAP2

VAUX1 (Linear)

VBT_RF

(1.875V)

Blue-Tooth

BTRF_REG

AGPS

VAP_GAM_RF

PCAP2

VUSB (Linear)

VAP_USB

(3.3V)

Bulverde

VCC_USB

PCAP2

VAUX3 (Linear)

VAP_MMC

(2.80V)

MMC / SD Card

MMC_VCC

PCAP2

VAUX4 (Linear)

VAP_GAM_RF

(3.00V)

AGPS

VGAM_RF

PCAP2

V8

(Linear)

VAP_PLL

(1.275V)

Bulverde

VCC_PLL

PCAP2

SW2 (BUCK)

VAB_MEM

(1.875V)

Neptune

QVDD

Stack-Memory

VCC1

VCC2

VCCQ

S-VCC

VPP

Bulverde

VCC_MEM

PCAP2

V3 (Linear)

VAP_SRAM

(1.275V)

Bulverde

VCC_SRAM

PCAP2

LEDG

LEDR

PCAP2

(Linear)

SIM_VCC

(1.875V/3.0V)

Neptune

SIM Card

RRight Amplifier

VSIM

FVDD

VCC

PCAP2

V2 (Linear)

V_AUDIO

(2.775V)

Neptune

VDD_CODEC

PCAP2

A1 Amplifier

A4 Amplifier

Left PGA

Right PGA

ALeft Amplifier

Phone DAC

Stereo DAC

A3 Amplifier

A5 Amplifier

MIC_BIAS1

MIC_BIAS2

PCAP2

V_VIB

(Linear)

VVIBB

(1.30V)

Vibrator

POS

Figure 1 – A780 Power Distribution Tree Diagram

08/02/2003 Motorola Confidential Proprietary 20 / 126

Page 21

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

T

I/Q

VCO1

VCO2

3.1.4 A780 Power Management Control

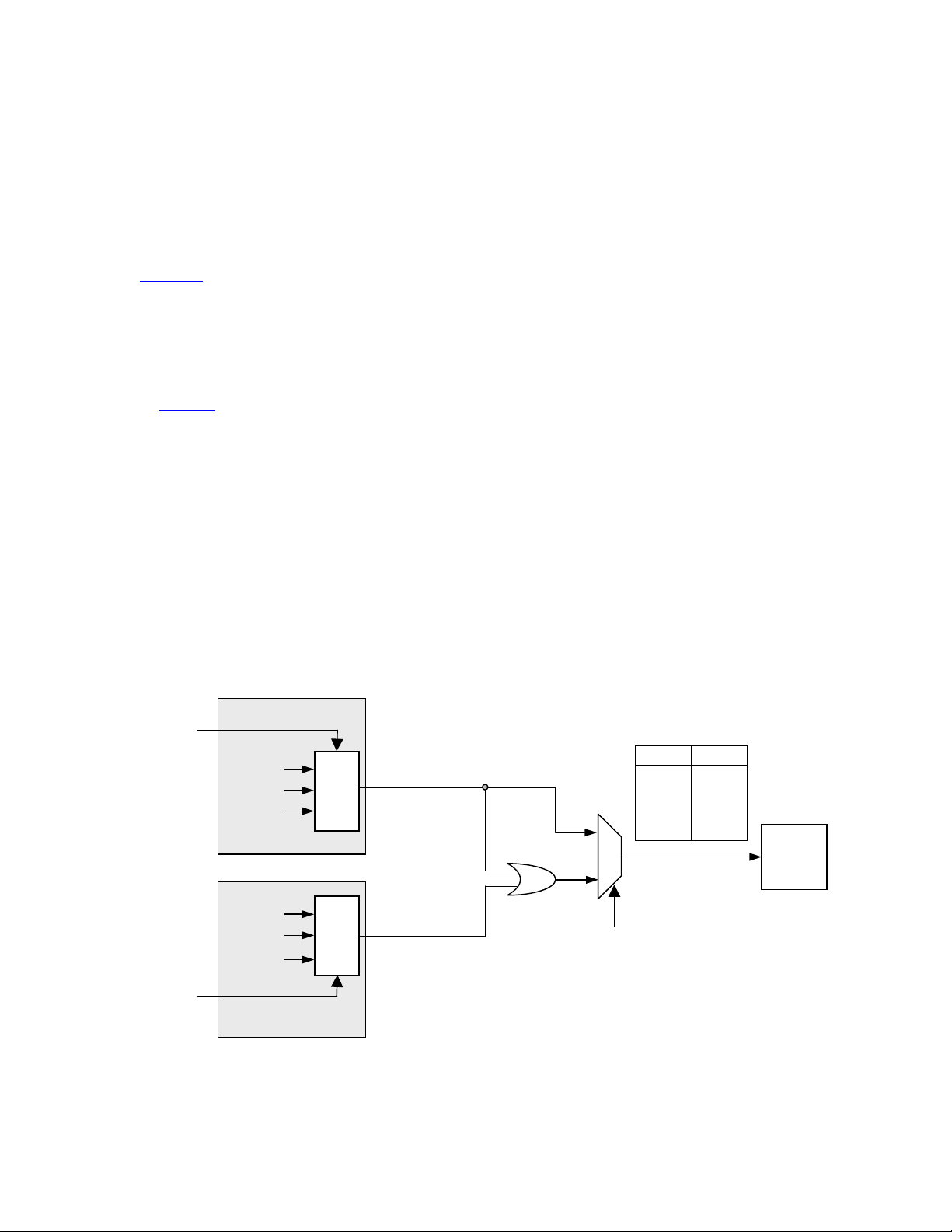

Figure 2

shows the detailed control signal connection for power management in A780.

Bulverde

VCC_CORE

VCC_MEM

VCC_PLL

USB Host Port3

GPIO [89]

PWR_EN

VCC_IO etc

VCC_SRAM

GPIO [1]

ICL

TC_MM_EN

nPWR_EN

USB

INT3

INT0

BVDD

Neptune

VDD_CODEC

STANDBY

SPI_CS3

BB_SPI

LVDD1

QVDD

BB_TX

BB_RX

L1_Timer

RF_SPI

RF_SPI

VBB_IO

VA

VAP_PLL

VAP_SRAM

VAB_MEM

P_CO

RE

VAB_IO

PCAP2_SEC_IN

SEC_SPI

PRI_SPI

PCAP2_PRI_IN

STANDBY

V_AUDIO

VBB_REF

VBB_CORE

BT

DC

INT

V1

V3

V8

SW1

SW2

SEC_SPI

Controllable

VAUX1

VAUX4

STANDBY2

V1

INTPRI

STANDBY

PRI_SPI

PCAP2

V2

SW2

CHAGC

V9

V10_IN

MAIN_FE

VCC_OUT

SW3

Boost

B+

Hall-Effect

USB

AGPS

EMU Support

EXT_B+

Mini-USB Connector

RAW_EXT_B+

LCD Module

Figure 2 – A780 Power Management Control Diagram

In Figure 2

, A780 power management block diagram, the power saving mode of

operation for both Neptune-LTE baseband and Bulverde adjunct processor need to be

described as below.

RF6003

RF2722

SAW

RF Switch

BATT+

V

V

Range

RAMP

RF3144

GSM/DCS

CEL/PCS

08/02/2003 Motorola Confidential Proprietary 21 / 126

Page 22

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

There are two standby control signals with PCAP2 in which is different from PCAP2

design. In A780 power management design, one standby control pin of PCAP2 is

connected with Neptune-LTE standby pin and another standby control pin is connected

with Bulverde PWR_EN pin (need to be inverted as PCAP2 required).

During the period of Neptune-LTE in standby mode, Neptune-LTE asserts it’s

STANDBY pin and PCAP2 shutdown the power supplies to Neptune-LTE subsystem

needed to be for power saving purpose. The power supplies need to be switched off for

Neptune-LTE standby mode is V7, V4 & V5.

In A780 adjunct processor power saving mode, Bulverde needs to enter into Sleep mode

for achieving minimum power consumption. That needs the power supplies provided to

Bulverde Core, PLL and internal SRAM power domain to be switched off after Bulverde

entered into sleep mode. The pin PWR_EN of Bulverde will be changed from logic

HIGH to logic LOW after Bulverde entering into Sleep mode. The inverted PWR_EN

(nPWR_EN) was connected with PCAP2 STANDBY2 pin in A780, so when

STANDBY2 of PCAP2 was changed from logic LOW to logic HIGH, the power supplies

to Bulverde Core, PLL and internal SRAM can be shutdown. Two types of power

supplies involved into Bulverde sleep mode operation, one is a linear regulator and

another one is switching mode regulator.

Figure 3

illustrates the waveform of control sequence for VCC_SRAM, VCC_PLL, and

VCC_CORE with PWR_EN.

PWR_EN

STANDBY2 (nPWR_EN)

SW1, V3, V8 (CORE, SRAM, PLL)

Running Mode Period

Sleep Mode Period

Running Mode Period

Figure 3 – A780 Bulverde Sleep and Operation Mode Power Supply Control

The state of PWR_EN signal of Bulverde will change from high to low automatically

after software entering into sleep mode and can automatically change back to high from

low while triggered by wakeup events settled by software. There is a small delay for

SW1, V3 and V8 to setup after STANDBY2 pin changed from high to low. But that is

within the timing requirement of Bulverde.

08/02/2003 Motorola Confidential Proprietary 22 / 126

Page 23

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

)

])

)

[

])

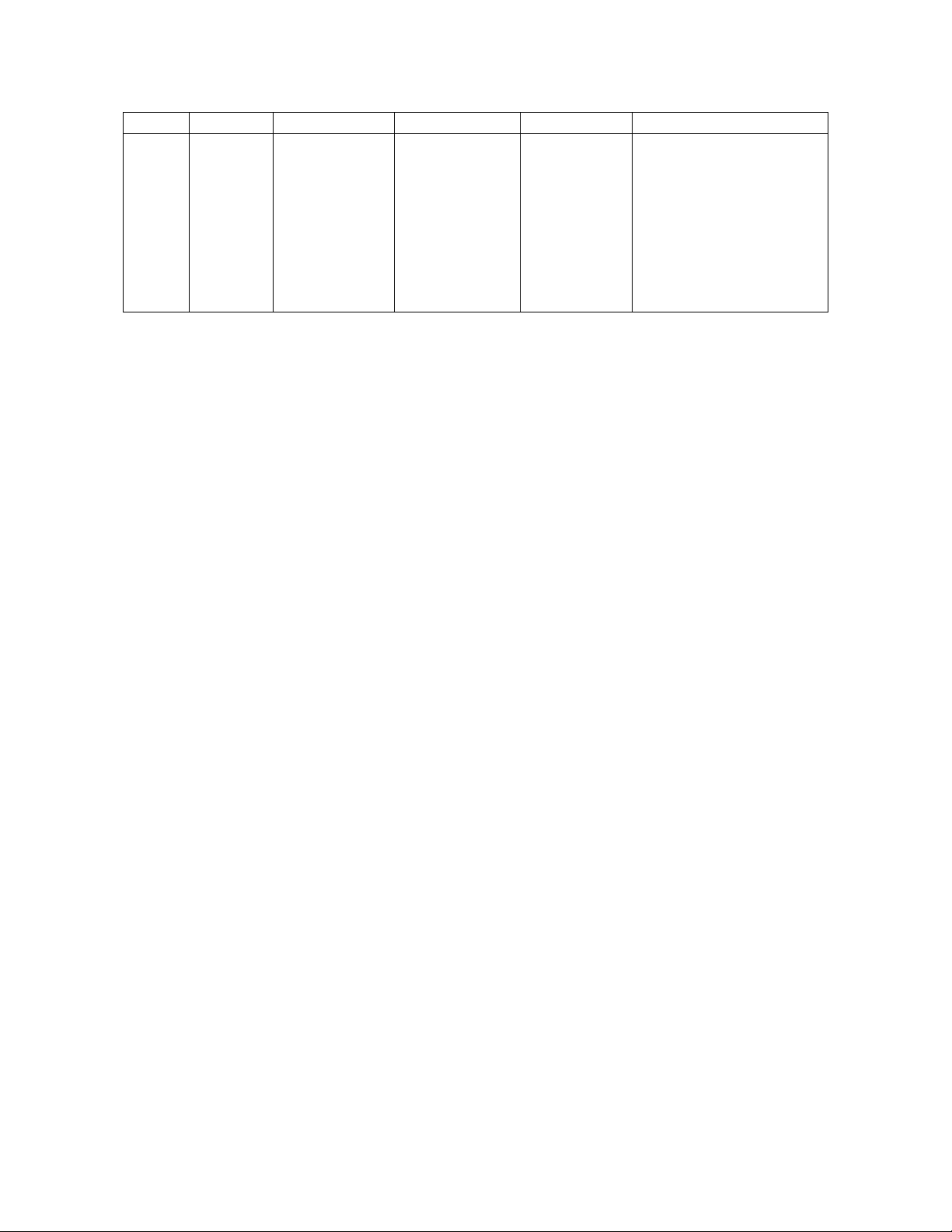

For switching mode regulator standby operation in PCAP2 (SW1 was used in A780), the

control block diagram Figure 4

and control True Table Table 2 can be applied for this

kind of operation.

SWx_MODE11 SWx_MODE10 SWx_MODE01 SWx_MODE00 STANDBYy Pin Mode Voltage

X X 0 0 0 OFF 0

X X 0 1 0 Sync SWx [3:0]

X X 1 0 0 Nonsync SWx [3:0]

X X 1 1 0 Low Power

0 0 X X 1 OFF 0

0 1 X X 1 Sync SWx_DVS [3:0]

1 0 X X 1 Nonsync SWx_DVS [3:0]

1 1 X X 1 Low Power SWx_DVS [3:0]

Table 2 – PCAP2 Switching Mode Regulator Standby Control True Table

Primary SPI

STANDBY1

SWx_MODE1 [1:0]

SWx [3:0]_DVS

SWx_MODE0 [1:0]

SWx [3:0

Secondary SPI

(SWx_MODE_PRI [1:0], SWx_PRI [3:0])

(SWx_MODE [1:0],

SWx_VOLTSEL [3:0])

SWx

Switching

Regulator

STANDBY2

SWx_MODE1 [1:0]

SWx [3:0]_DVS

SWx_MODE0 [1:0]

SWx

3:0

(SWx_MODE_PRI [1:0], SWx_SEC [3:0])

(In Primary VREG_MASK Register)

SWx_SEL

Figure 4 – PCAP2 Switching Mode Regulator Standby Control

There are several items of note in Figure 4

and in Table 2. First is the fact that either SW1

or SW2 can be controlled by either the primary or secondary SPI. For switching mode

regulators control, no OR gate was put into PCAP2 control. This is controlled by the

SW1_SEL and SW2_SEL bits in the VREG_MASK register. Furthermore, either

switcher can be placed in any of the four possible switcher modes arbitrarily, based on

the state of the STANDBY pins (the STANDBY1 pin controls the primary SPI

regulator(s), where as the STANDBY2 pin controls the secondary SPI regulator(s).

Finally, the switching regulator mode control design allows the system to dynamically

change the output voltage of each switcher based on the STANDBY pins.

08/02/2003 Motorola Confidential Proprietary 23 / 126

Page 24

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

Bulverde internal SRAM and PLL power domain, VCC_SRAM and VCC_PLL

respectively, are linear regulators provided by PCAP2. VCC_SRAM power supply is

provided by PCAP2 V3 and VCC_PLL power supply is provided by PCAP2 V8 in A780

power management design. During sleep mode of Bulverde, V3 and V8 needs to be

shutdown for achieving minimum power consumption.

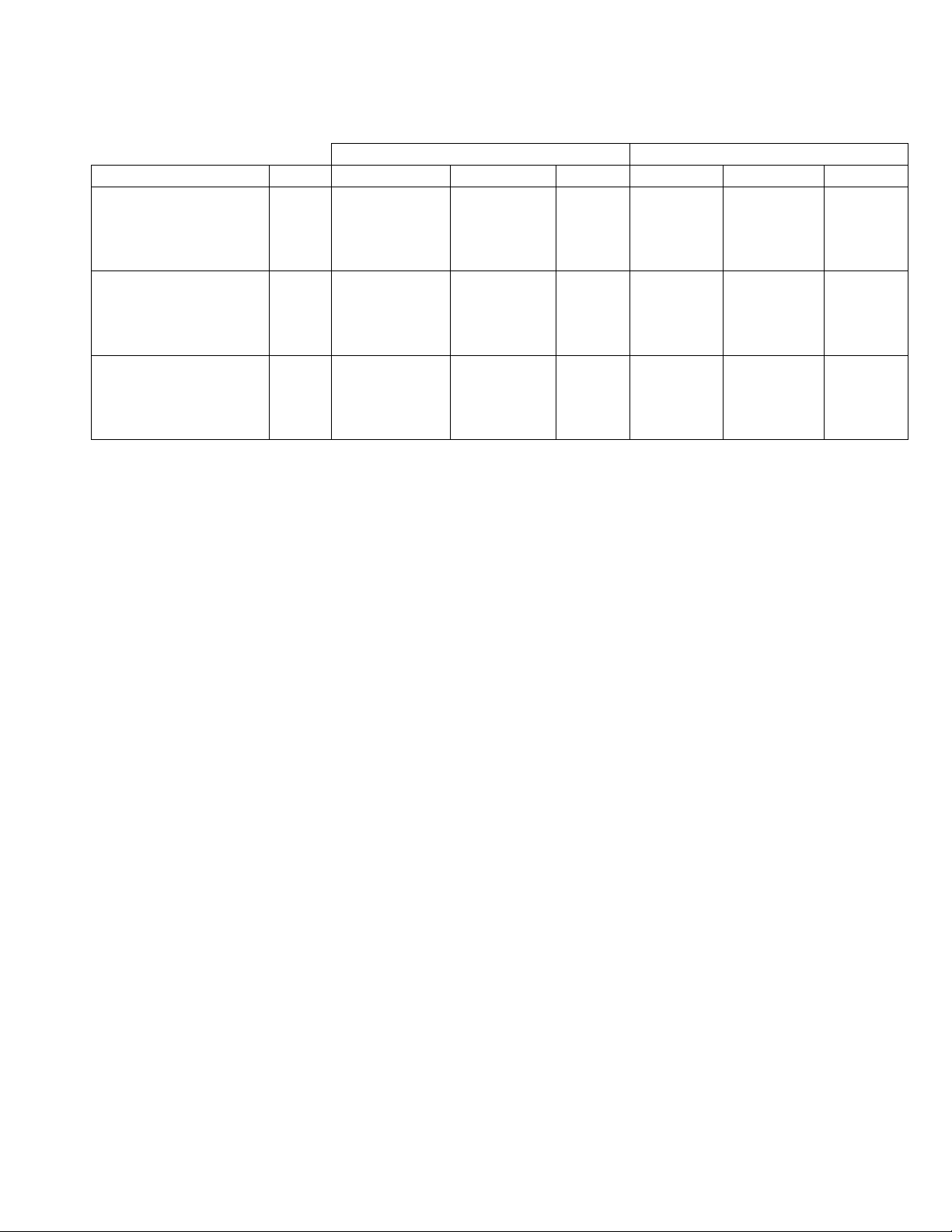

Figure 5

shows a block diagram of standby control for those linear regulators (includes

V3 and V8, but not limited to them in PCAP2) that have standby controllability. Each

linear regulator is controlled via SPI bits in both the primary and secondary SPIs. Mode

decoder logic in each SPI block combines these SPI bits with the STANDBY pins

(STANDBY1 for primary, STANDBY2 for secondary), and outputs Vx_MODE_PRI

[1:0] and Vx_MODE_SEC [1:0]. The truth table for the mode decoder logic is shown

in Table 3

. Note that not all regulators have corresponding EN bits in the secondary SPI.

In these cases, the secondary EN bit is assumed to be a logic 1. when interpreting the

truth table. The regulators that cannot be controlled via STANDBY1 or STANDBY2

are: VSIM, VSIM2, TS_REF, VHOLD, V_VIB, and VFLASH. Some of these regulators

can be placed in a low power mode (VSIM, VSIM2, TS_REF, and VHOLD), but the low

power feature is independent of standby control in that case.

One noteworthy feature of the linear regulator standby control scheme is the mode

OR.ing function. This function simply selects the highest power mode between

Vx_MODE_PRI [1:0] and Vx_MODE_SEC [1:0]. This function can be disabled via the

Vx_SEL bits in the VREG_MASK register. This register is only accessible by the

primary SPI port, and is used by the primary SPI to allow or disallow control from the

secondary SPI port of any set of individual regulators.

STA

NDBY1

Primary SPI

Vx_EN

Vx_LOWPWR

Vx_STDY

Mode

Encoder

Vx_MODE_PRI [1:0]

MODE [1:0] Mode

00 OFF

01 Not Used

10 Low Power

11 ON

Vx_MODE[1:0]

Vx

Regulator

Vx_EN

Vx_LOWPWR

Vx_STDY

Mode

Encoder

Vx_MODE_SEC [1:0]

(In Primary VREG_MASK Register)

Vx_SEL

NDBY2

STA

Secondary SPI

Figure 5 – PCAP2 Linear Mode Regulator Standby Control

08/02/2003 Motorola Confidential Proprietary 24 / 126

Page 25

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

EN bit STBY bit LOWPWR bit STANDBYy Pin Mode Vx_MODE_PRI/SEC [1:0]

0 X X X OFF 00

1 0 0 0 ON 11

1 0 0 1 ON 11

1 0 1 0 Low Power 10

1 0 1 1 Low Power 10

1 1 0 0 ON 11

1 1 0 1 OFF 00

1 1 1 0 ON 11

1 1 1 1 Low Power 10

Table 3 – PCAP2 Linear Mode Regulator Standby Control True Table

To switch off V3 (VCC_SRAM) and V8 (VCC_PLL) when STANDBY2 asserted,

V3_EN and V8_EN need to be clear by primary SPI since those two bits are accessible

only by primary SPI. In A780 design, the primary SPI port of PCAP2 is connected with

Neptune-LTE. So Neptune-LTE software should clear V3_EN and V8_EN after booting

up.

08/02/2003 Motorola Confidential Proprietary 25 / 126

Page 26

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

K

K

SSP

2

K

t

K

3.2 A780 Audio System and PCAP2 Audio Section

3.2.1 A780 Audio System Architecture Block Diagram

A780 phone design supports the voice audio, stereo audio and Bluetooth audio in its

audio system architecture illustrated in Figure 6

illustrated in Figure 6

.

. The SPI port to PCAP2 control is also

Bulverde

-

GPIO [88]

GPIO [38]

GPIO [37]

GPIO [22]

SAP_TXD

SAP_RXD

SAP_FRM

SAP_CLK

SAP_TXD

SAP_RXD

SAP_FRM

SAP_CL

STDA

Neptune-LTE

SRDA

SC2A

SCKA

GPIO [29]

SSP-1

GPIO [25]

GPIO [24]

GPIO [26]

GPIO [52]

SSP-3

GPIO [89]

GPIO [81]

GPIO [83]

AP_SPI_FRM

AP_SPI_CLK

AP_SPI_TXD

AP_SPI_RXD

AP_SPI_CS

AP_AUD_CLK

AP_AUD_TXD

AP_AUD_FRM

SAP_CL

SAP_TXD

SAP_FRM

SAP TXD

SAP FRM

SAP CL

SAP RXD

SEC_MOSI

SEC_CE

SEC_MISO

TX

BITCLK1

RX1

FSYNC1

RX0

FSYNC0

BITCLK0

SEC_SPI_CLK

ASAP TXD

ASAP FS

ASAP CL

ASAP RXD

PCAP2-II

Blue-Tooth

Figure 6 – A780 Audio System Architecture Block Diagram

The alternate functions of Bulverde GPIO assignment for audio and SPI settings shows in

Table 4

.

BT

Headse

08/02/2003 Motorola Confidential Proprietary 26 / 126

Page 27

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

A780 Function

AP SPI - AP_SPI_CLK GPIO[29]

AP SPI - AP_SPI_FRM GPIO[24]

AP SPI - AP_SPI_RXD GPIO[26]

AP SPI - AP_SPI_TXD GPIO[25]

SAP Codec - SAP_CLK GPIO[22]

SAP Codec - SAP_FRM GPIO[37]

SAP Codec - SAP_RXD GPIO[38]

SAP Codec - SAP_TXD GPIO[88]

Stereo Codec - AP_AUD_CLK GPIO[52]

Stereo Codec - AP_AUD_FRM GPIO[83]

Stereo Codec - AP_AUD_RXD GPIO[89]

Stereo Codec - AP_AUD_TXD GPIO[81]

GPIO

Table 4 –Bulverde GPIO Assignment for Audio SSP and SPI

Alternative Input Alternative Output

[ 01 ] [ 10 ] [ 11 ] [ 01 ] [ 10 ] [ 11 ]

AC97_SDATA_IN_0 I2S_SDATA_IN SSPSCLK SSPRXD2 SSPSCLK

CIF_FV SSPSFRM CIF_FV SSPSFRM

SSPRXD CIF_PCLK

CIF_LV CIF_LV SSPTXD

SSPEXTCLK2 SSPSCLK2EN SSPSCLK2 KP_MKOUT[7] SSPSYSCLK2 SSPSCLK2

FFDSR SSPSFRM2 KP_MKIN[3] USB_P2_8 SSPSFRM2 FFTXD

FFRI KP_MKIN[4] USB_P2_3 SSPTXD3 SSPTXD2 PWM_OUT[1]

USBHPWR[0] SSPRXD2 SSPSFRM2 SSPSFRM2

CIF_DD[4] SSPSCLK3 BB_OB_CLK SSPSCLK3

SSPSFRM3 BB_IB_CLK CIF_DD[4] SSPSFRM3

SSPRXD3 AC97_SYSCLK USBHPEN[0] SSPTXD2

CIF_DD[0] SSPTXD3 BB_OB_DAT[0]

08/02/2003 Motorola Confidential Proprietary 27 / 126

Page 28

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

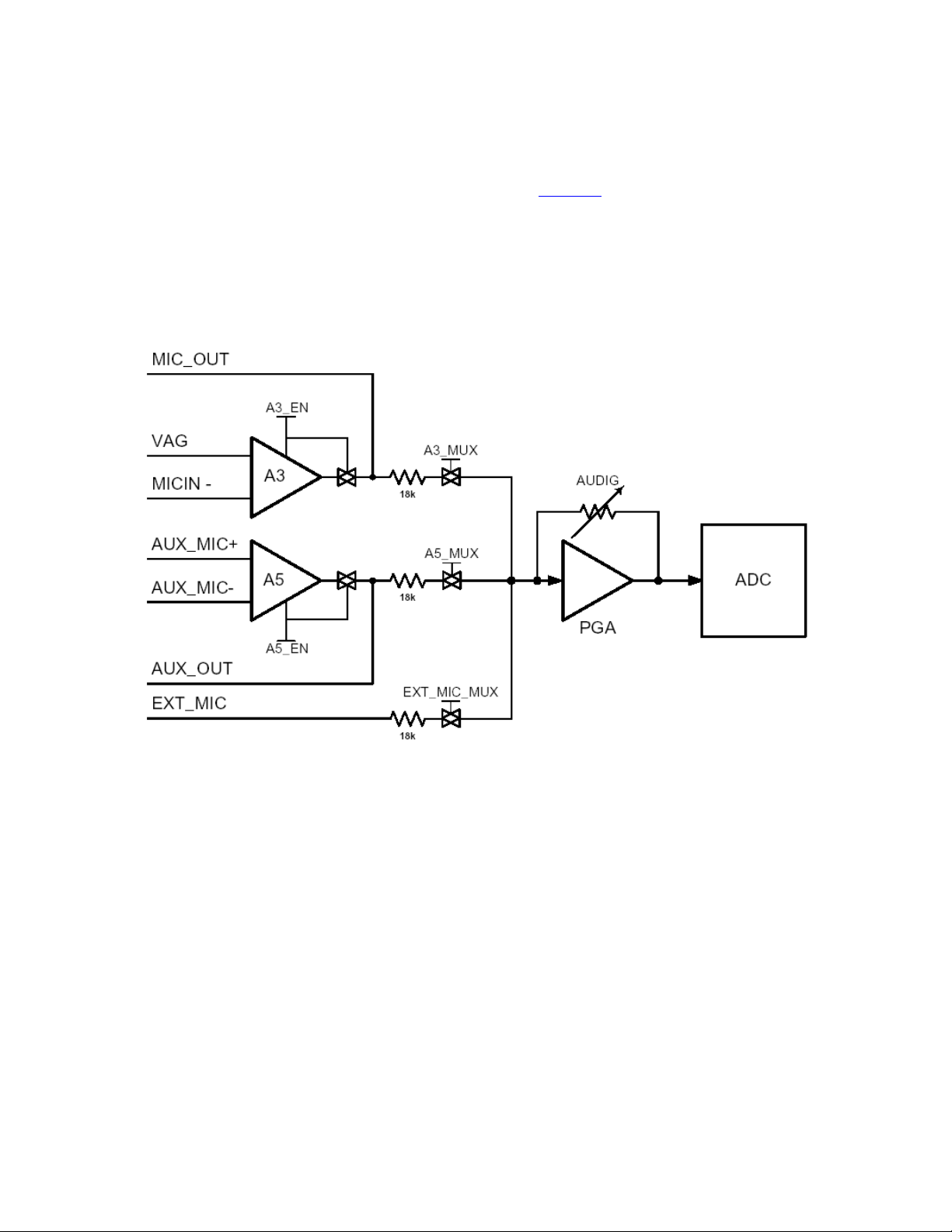

3.2.2 Audio Input Section

PCAP2 Audio Input Section block diagram shows in Figure 7

. Any one of three

equivalent microphone inputs can be selected. These inputs are EXT_MIC, the output of

the differential input microphone amplifier A3 or the output of the differential auxiliary

microphone amplifier, A5. These three inputs are single ended with respect to VAG

(Note: AUX_MIC+ should be DC connected to VAG to avoid an offset relative to the

A/D input). MIC_BIAS is derived from VAG for best noise performance. MB_CAP

bypasses the gain from VAG to MIC_BIAS to keep the noise balanced.

Figure 7 – PCAP2 Audio Input Section Block Diagram

Following the input stage and multiplexer is a selectable gain stage and 30kHz low-pass

anti-aliasing filter. This low-pass filter may be designed to whatever order is needed to

insure that aliased components are not present in the output. The gain of the selectable

gain stage can be selected in 1dB steps from 0dB to +31dB.

Depending on the design of the A/D converter the output of the anti-aliasing filter may be

clamped to keep from overdriving the A/D converter.

The audio input bits control the configuration of the input. These bits select the gain,

enable or disable the input, select between the EXT_MIC, A5 amplifier output, or A3

amplifier output, and select or deselect the CODEC’s high pass input filter. Also, these

bits can select a loop-back mode that takes the digital output of the input A/D converter,

and loops it directly back to the D/A output section for testing.

08/02/2003 Motorola Confidential Proprietary 28 / 126

Page 29

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

The switch shown between A3 output and MIC_OUT and the switch shown between A5

output and AUX_OUT are conceptual. It is possible that the amplifier will be high

impedance when in its powered down state.

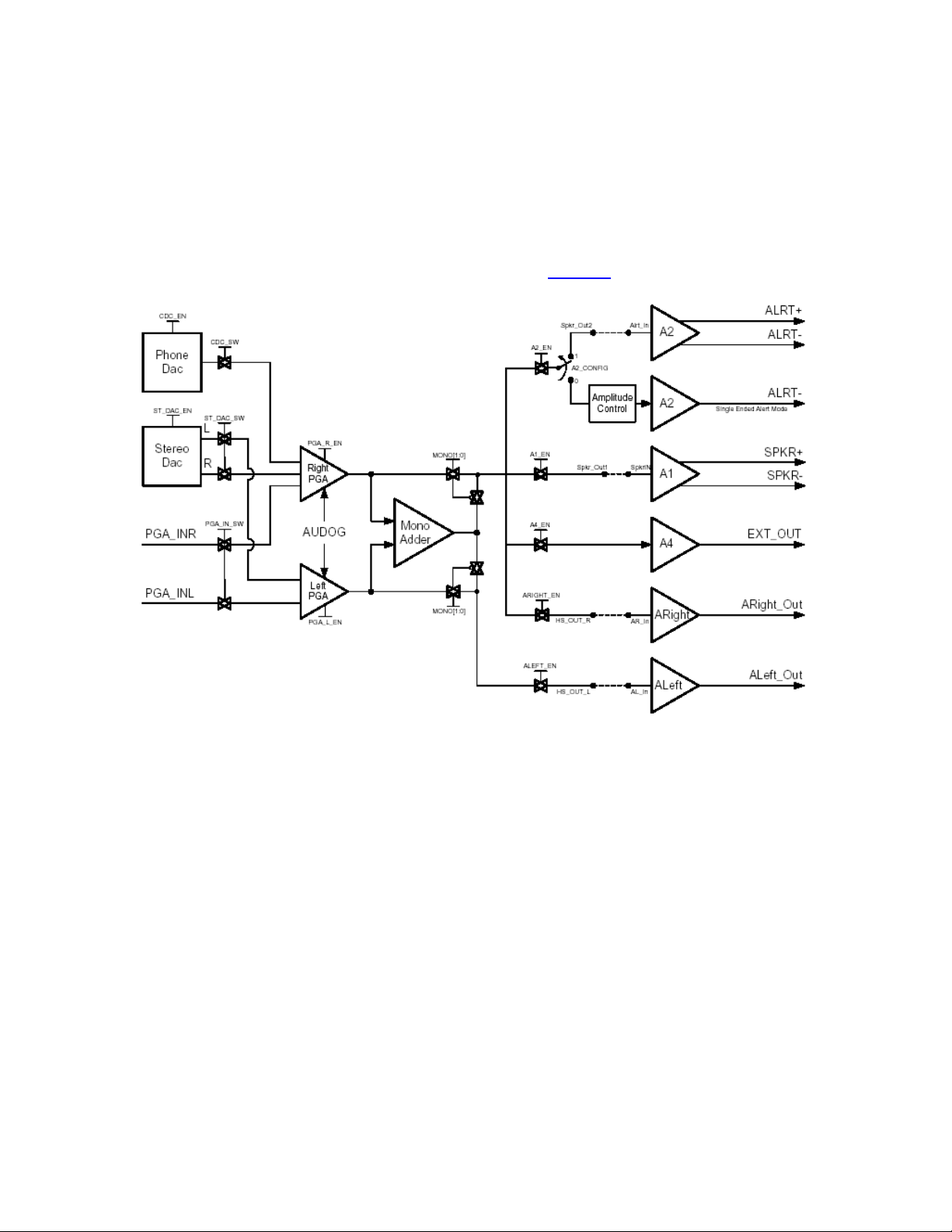

3.2.3 Audio Output Section

PCAP2 Audio Output section block diagram shows in Figure 8

.

Figure 8 – PCAP2 Audio Output Section Block Diagram

It shows that the audio out of the telephone CODEC or the right channel of the stereo

DAC can be routed via the right PGA to any one of four outputs. These outputs are: the

internal earpiece speaker amplifier, A1, the alert amplifier, A2, the external speaker

amplifier, A4, or the dedicated headset right channel speaker amplifier, ARight. All of

these outputs can be simultaneously connected to the right PGA so care should be taken

not enable multiple amplifiers at the same time if this is not desired.

The Mono adder can be used to sum the left and right channels of the stereo DAC or

signals supplied to the left and right PGA inputs. The Mono adder can then attenuate the

summed signals by 0dB, 3dB or 6dB and an identical monophonic signal to any of output

amplifiers mentioned above.

SPKR_OUT1, SPKR_OUT2, HS_OUT_R and HS_OUT_L should maintain their DC

levels even when not selected or if the audio is off.

08/02/2003 Motorola Confidential Proprietary 29 / 126

Page 30

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

SPKR_OUT1, SPKR_OUT2, HS_OUT_R, HS_OUT_L, PGA_INR, and PGA_INL are

all capacitor coupled.

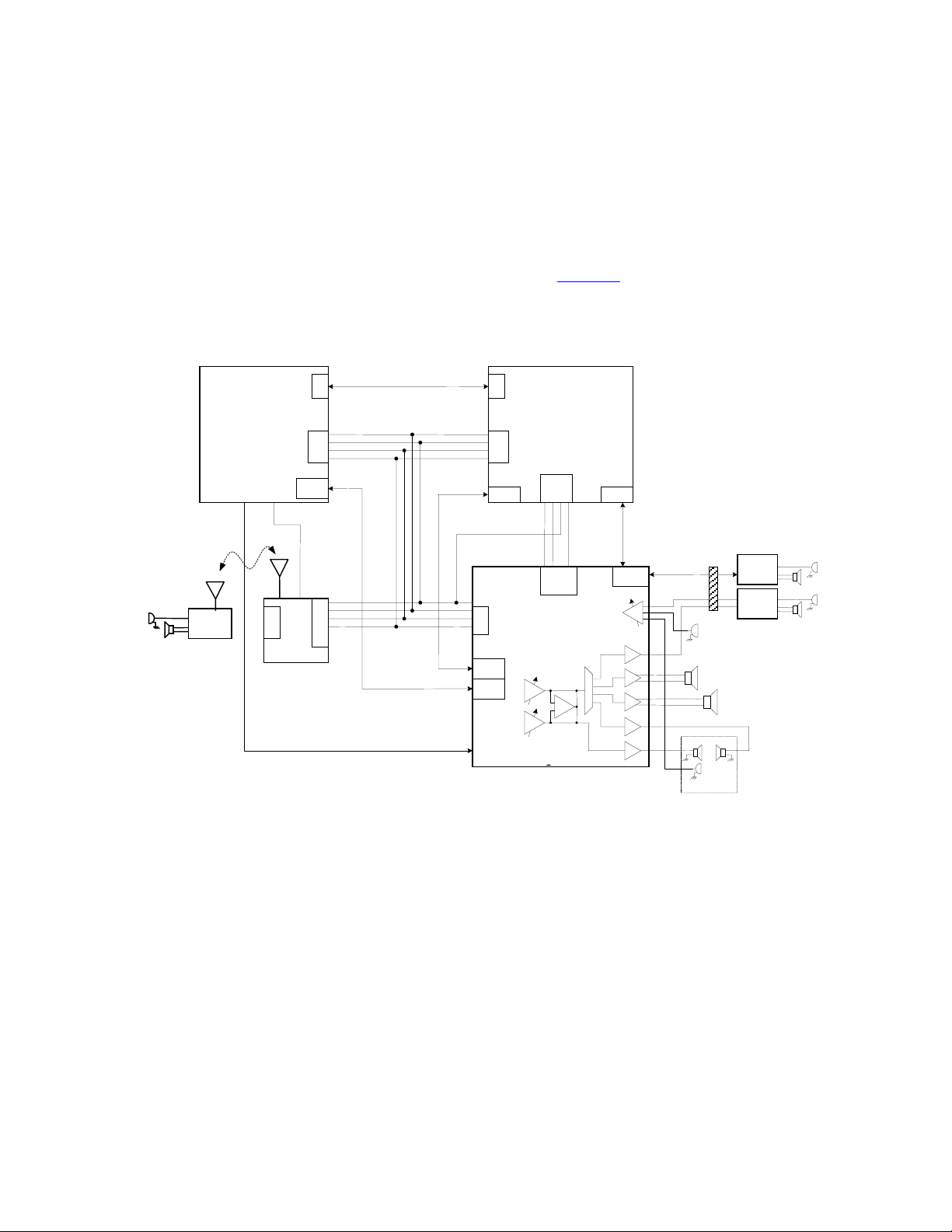

3.2.4 A780 Audio Routing and SPI Control

The audio system of A780 composed of Neptune, Bulverde and PCAP2. Neptune and

Bulverde control the PCAP2 audio portion through the SPI port. A780 audio routing

and SPI control connection block diagram shows in Figure 9

.

Neptune

CKO

TRK

OSC

S

A

P

U

A

R

T

MQ

SPI

SckA

Sc2A

U

Bulverd

A

R

T

Tx

Rx

Rx/Tx

Tx/Rx

BitClk

Fsync

SSP/SSI

SPI

N

S

S

P

ASSP

B

S

c

y

l

n

x

k

c

USB

TxR

R

F

B

c

x

Bluetooth

Headset

CLKIN

S

U

S

S

I

B

Bluetooth

Tx

Rx

Clk

Fs

Tx

S

Rx

S

Bclk

I

Fs

0

SEC

SPI

PRI

SPI

CLKIN

s

l

k

C

O

D

E

C

SSI1

STDAC

R

PGA

Mono

L

PGA

PCAP

XCVR

USB

Audio_In

PGA

A4

A2

A1

AR

AL

Audio_Out

Headset

Handset

Microphone

Loud

Speaker

Earpiece

DIGITAL

(USB)

DHFA

ANALOG

DHFA or

EIHF

Figure 9 – A780 Audio Routing and SPI Control Block Diagram

For detailed A780 audio system architecture description, please refer to ASE document

“Audio Design Document for Adjunct Processor-based Neptune Platform”.

08/02/2003 Motorola Confidential Proprietary 30 / 126

Page 31

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

3.3 A/D Conversion And Channel Allocations

The A/D conversion functions are performed by PCAP2 chipset through the connections

between PCAP2 and Neptune-LTE, PCAP2 and Bulverde via read & write accessing SPI

port. The A/D converter of PCAP2 is a 14-Channel, 10-bit converter with a state machine

to control the various modes of operation. That 14-channel input is split into two groups

and each one with 7-channel.

AD_SEL selects between two groups of 7 input signals. If set to Zero then LiCell,

BATSENSE, B+SENSE, MPBSENSE, AD4, AD5, and AD6 are read and stored into the

PCAP2 registers when the conversion finished. If AD_SEL is set to One then AD7, AD8,

AD9, TSX1, TSX2, TSY1, and TSY2 are read and stored. This is done to shorten the

total read time and to reduce the required storage of converted values.

The ADC will have the ability to execute a conversion in three ways:

1) Enable the conversion with the Start Convert (ASC) bit.

2) Enable the conversion with the rising edge of the ADTRIG signal.

3) MTR standby conversion mode.

In all of the above cases the conversion will begin after a delay set by the ATO register.

This register will be 4-Bit long and will be driven by ADCCLK/256.

Once conversion is initiated all 7 channels will be sequentially converted and stored in

registers if RAND is set to 0.

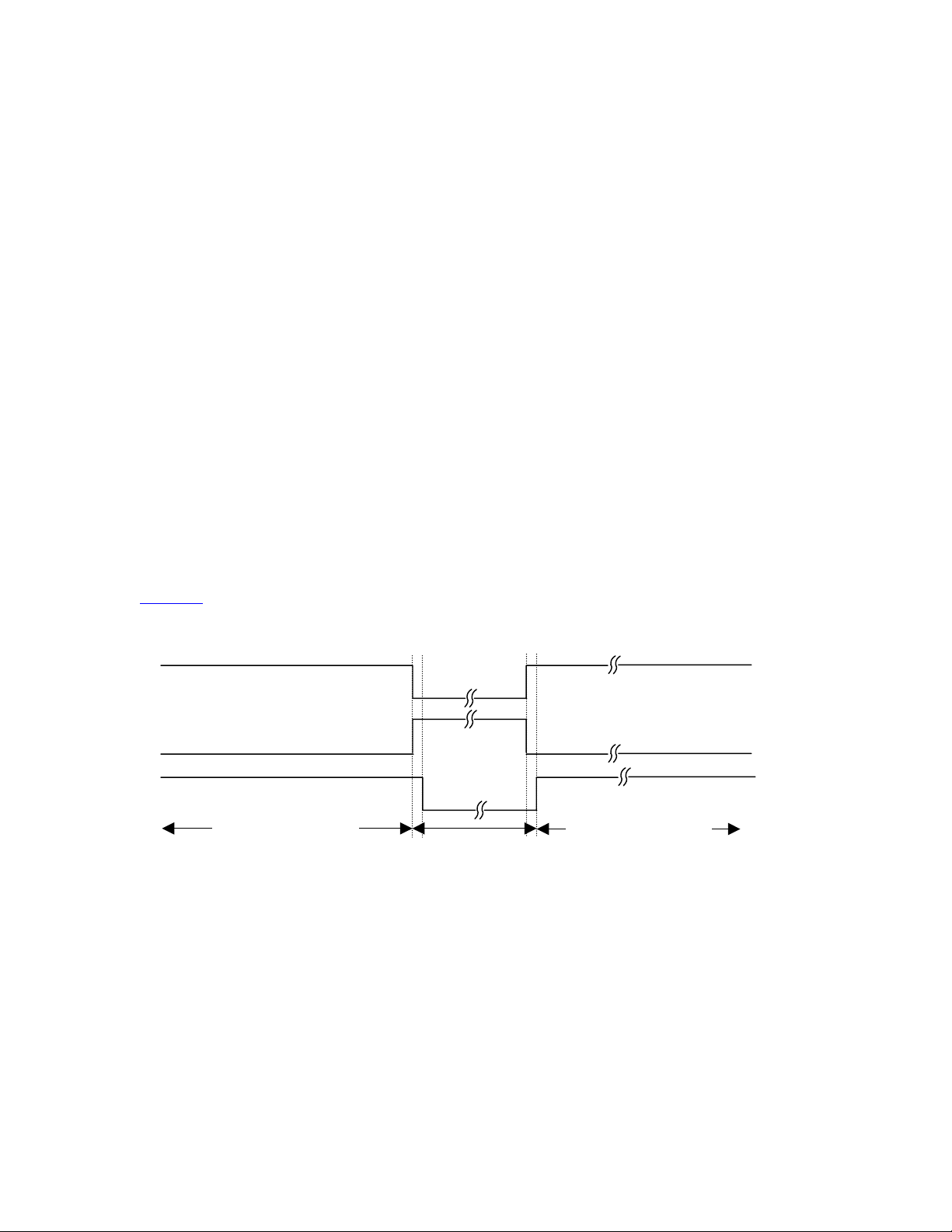

This is shown in the Figure 10

for AD_SEL = 0.

Figure 10 – PCAP2 A/D Conversion Timing Diagram with AD_SEL = 0

08/02/2003 Motorola Confidential Proprietary 31 / 126

Page 32

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

If AD_SEL = 1 then the channels converted are as shown in Figure 11

Figure 11 – PCAP2 A/D Conversion Timing Diagram with AD_SEL = 1

To convert multiple channels starting the conversion with the ASC bit, the following

steps are executed:

1) Enable A/D (ADEN=1). Set RAND to 0.

2) Start conversion at channel 0 by writing a 1 to the start conversion bit (ASC). The

conversion will begin once ATO counts down to zero.

3) Wait for completion (ASC will reset to zero and ADCDONEI will be set when

complete).

4) Write the result address (ADA [2:0]) while writing a 1 to ADEN (so that SPI

doesn’t write to result registers) and 0 to ASC (so that ADC doesn’t restart new

conversions).

5) Read conversion values.

6) Repeat steps 4 and 5 for all channel results.

To convert multiple channels starting the conversion with the rising edge of ADTRIG,

the following steps are executed:

1) Enable A/D (ADEN=1). Sets RAND to 0. Note that ASC will go high with the

rising edge of ADTRIG.

2) The conversion will automatically start at channel 0 once ATO counts down to

zero.

3) Wait for completion (ASC will reset to zero and ADCDONEI will be set when

complete).

4) Write the result address (ADA [2:0]) while writing a 1 to ADEN (so that SPI

doesn’t write to result register) and 0 to ASC (so that ADC doesn’t restart new

conversion).

.

08/02/2003 Motorola Confidential Proprietary 32 / 126

Page 33

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

5) Read conversion values.

6) Repeat steps 4 and 5 for all channel results.

To convert a single channel starting the conversion with the ASC bit, the following steps

are executed:

1) Enable A/D (ADEN=1). Set RAND to 1. Set ADA [2:0] to the desired channel.

2) Start conversion by writing a 1 to the start conversion bit (ASC). The conversion

will begin once ATO counts down to zero.

3) Wait for completion. (ASC will reset to zero and ADCDONEI will be set when

complete). In this mode the A/D will perform 7 conversions of the selected

channel and save the results in ADA [2:0].

4) Write the conversion number 0-6 (ADA [2:0]) while writing a 1 to ADEN (so that

SPI doesn’t write to result registers) and 0 to ASC (so that ADC doesn’t restart

new conversions).

5) Read conversion values.

6) Repeat steps 4 and 5 for all 7 results.

To convert a single channel starting the conversion with the rising edge of ADTRIG, the

following steps are executed:

1) Enable A/D (ADEN = 1). Sets RAND to 1. Set ADA [2:0] to the desired channel.

Note that ASC will go high with the rising edge of ADTRIG.

2) The conversion will automatically start once ATO counts down to zero.

3) Wait for completion. (ASC will reset to zero and ADCDONEI will be set when

complete). In this mode the A/D will perform 7 conversions of the selected

channel save the results in ADA [2:0].

4) Write the conversion number 0 – 6 (ADA [2:0]) while writing a 1 to ADEN (so

that SPI doesn’t write to result registers) and 0 to ASC (so that ADC doesn’t

restart new conversions).

5) Read conversion values.

6) Repeat steps 4 and 5 for all 7 results.

A780 A/D converter allocation listed in Table 5

.

08/02/2003 Motorola Confidential Proprietary 33 / 126

Page 34

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

Address

Internal /

Input

External

AD1 Internal 0 000 Li-Cell Backup cell voltage monitoring 1.5V ~ 4.5V 0.4V ~ 2.3V B2H ~ 3FFH

AD2 Internal 0 001

AD_SEL ADA[2:0] Signal Purpose Condition

BATT_SENSE

Battery terminal voltage monitor

for charge & discharge control

2.0V ~ 5.5V 0.4V ~ 2.3V B2H ~ 3FFH

A/D

Voltage

A/D Count

AD3 Internal 0 010 B+_SENSE

AD4 Internal 0 011 MPBSENSE

AD5 External 0 100 BATT_THERM

AD7 External 0 101 / Not used in A780 design N/A

AD6 External 0 110 CHRG_ID

AD9 External 1 000 / Not used in A780 design N/A N/A N/A

AD8 External 1 001 / Not used in A780 design N/A N/A N/A

AD10 External 1 010 / Not used in A780 design N/A N/A N/A

AD11 External 1 011 TSX1

AD12 External 1 100 TSX2

AD13 External 1 101 TSY1

AD14 External 1 110 TSY2

B+ terminal voltage monitor for

charge & discharge control

EXT_B_ terminal voltage

monitor for charger type

identification and charge control

Connect with battery thermo

voltage for battery pack

temperature monitor during

charge and discharge

Connect with Mini-USB

connector and functions as

accessory ID identify

Connect with resistive touch

panel for X - position reading

Connect with resistive touch

panel for X - position reading

Connect with resistive touch

panel for Y - position reading

Connect with resistive touch

panel for Y - position reading

2.5V ~ 6.5V 0.4V ~ 2.3V B2H ~ 3FFH

2.7V ~ 6.5V 0.4V ~ 2.3V B2H ~ 3FFH

25°C 1.28V 23AH

Mid-Rate 1.254V 22EH

Full-Rate 1.955V 366H

Position dependence

Position dependence

Position dependence

Position dependence

0.4V ~ 2.3V B2H ~ 3FFH

0.4V ~ 2.3V B2H ~ 3FFH

0.4V ~ 2.3V B2H ~ 3FFH

0.4V ~ 2.3V B2H ~ 3FFH

Table 5 – A780 A/D Converter Allocation Table

3.3.1 Detailed Description Of Each A/D Channel

1) Li-Cell Battery A/D (AD1)

The coin cell battery voltage can be monitored at this channel of A/D

converter. This can be used to do the decision for power cut, user off etc

functions. This channel A/D can measure an input voltage in the range of

1.5V minimum to 4.5V maximum. The equation below can be used to scale

08/02/2003 Motorola Confidential Proprietary 34 / 126

Page 35

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

the desired external voltage input range to correspond to the A/D input range

of 0.4V to 2.3V.

V

LI_SENSE

= ((LiCELL) – 0.8625) x 0.62609

2) BATT_SENSE A/D (AD2)

This A/D converter input directly is connected with battery positive pin for

terminal voltage monitoring for both charge & discharge battery gas-gauge

display. This A/D input comes from PCAP2 pin BATTP with which battery

positive pin internally connected. The equation below is calculated to fit the

desired input range from 0.4V to 2.3V.

V

BATT_SENSE

= ((V

BATTERY

) – 1.2862) x 0.5598

3) B+_SENSE A/D (AD3)

This A/D converter input is connected with B+ and is used to do the voltage

monitoring during discharge. Software can use this A/D channel to do the

software shutdown when the battery voltage is too low to provide the power to

the whole phone. The threshold of shutdown is stored in the battery EPROM

and was read back during the phone power up. The equation below is

calculated to fit the desired input range from 0.4V to 2.3V. And the transfer

function for this can be described as below.

V

B+_SENSE

= ((B+) – 1.6361) x 0.47151

4) MPB_SENSE A/D (AD4)

This channel A/D connected internally with EXT_B+. This A/D can be used

to monitor the charger’s type prior to charging. The equation below is

calculated to fit the desired input range from 0.4V to 2.3V.

V

MPB_SENSE

= ((V_MOBPORTB) – 1.8849) x 0.4911

5) BATT_THERM A/D (AD5)

This A/D channel is used to do the monitoring of battery pack temperature.

There is a thermo-resistor built into the battery pack, which can be used to do

the temperature measurement for battery charge and discharge safety use

purpose. This A/D channel is internally connected with AD5 of PCAP2 with

which battery pack thermo-resistor connected. The connection block diagram

shown in Figure 12

.During standby mode operation period, the Standby signal

will disconnect the V2 from the thermo-resistor for power saving. The voltage

input to AD5 should be within 0.4V ~ 2.3V.

08/02/2003 Motorola Confidential Proprietary 35 / 126

Page 36

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

V2

The characteristic of the thermo-resistor

is in Table 6

.

THERM_BIAS

Standby

There is a capacitor connected at AD5

RT

R916

10K

10K

R921

20K

AD5

R920

300K

A/D

PCAP2

with ground for interference proof.

At room temperature, the nominal

resistance of RT is 10KΩ. And the

voltage at AD5 is 1.28V.

When the battery pack is removed from

the board, the voltage at AD5 is 2.70V

roughly.

Figure 12 – Battery Thermistor Connection Block Diagram

Temperature R

°C

No Battery Infinity 2.52 1023 3FF

-40 336.60 2.45 1023 3FF

-35 242.80 2.43 1023 3FF

-30 177.00 2.39 1023 3FF

-25 130.40 2.35 1023 3FF

-20 97.12 2.29 1020 3FC

-15 92.98 2.28 1016 3F8

-10 55.34 2.15 955 3BB

-5 42.34 2.05 913 391

0 32.66 1.95 865 361

5 25.40 1.83 812 32C

10 19.90 1.7 754 2F2

15 15.71 1.56 694 2B6

20 12.49 1.42 632 278

25 10.00 1.28 570 23A

30 8.06 1.15 509 1FD

35 6.53 1.02 452 1C4

40 5.33 0.89 398 18E

45 4.37 0.78 349 15D

50 3.60 0.68 304 130

55 2.99 0.59 264 108

60 2.49 0.52 229 0E5

65 2.08 0.45 198 0C6

70 1.75 0.39 172 0AC

75 1.48 0.33 149 095

80 1.26 0.29 129 081

Thermistor

Voltage A/D Value Hex Value

Ω

K

V (DEC) (HEX)

Table 6 – Battery Thermistor Readings Over Temperature

08/02/2003 Motorola Confidential Proprietary 36 / 126

Page 37

A780 Quad-Band Phone Hardware Interface Document Rev. 0.1

6) CHRG_ID (AD6)

AD6 is used to identify the accessories type when an accessory attached with

Mini-USB connector.

<Need to be finished when EMU bus design lockdown>

7) Touch Panel AD (AD11 ~ AD14)

Those four AD channels are used to measure the position of the touch panel

pressed point. The input voltage was scaled within 0.4V ~ 2.3V according to the

pressed position.

3.3.2 A780 Charge Operation Description

<Need to be finished when EMU bus design lockdown>

4. Neptune-LTE Logic Interfaces

A780 Quad-band design decided to use Neptune-LTE 257-PIN as its base band call

processor chipset IC. Neptune-LTE IC is a digital base band processor for the 2.5 / 2.75G

GSM market. It is a dual-core processor that contains a Synthesizable Onyx DSP core

(566xx), an ARM7TDMI-S micro-controller, and custom peripherals.

Neptune-LTE is available in two packages; 257-Pin Neptune-LTE chipset is used in

A780 Quad-band final design.

For detail Neptune-LTE information, please refer to “Neptune LTE Baseband IC

Specification” document.

Neptune-LTE connects with Bulverde, PCAP2, RF6003 and RF2722 etc to build the

A780 system architecture.

A780 system architecture block diagram shows in Figure 50

PCAP2, RF6003 & RF2722 as a RF modem. And Bulverde controls Blue-tooth, digital