Mosel Vitelic V62C2161024LL-100T, V62C2161024L-85T, V62C2161024L-70T, V62C2161024L-55T, V62C2161024L-100T Datasheet

...

V62C2161024L(L)

Ultra Low Power

64K x 16 CMOS SRAM

Features

• Ultra Low-power consumption

- Active: 35mA I

- Stand-by: 5

µA (CMOS input/output)

CC

at 55ns

1 µA (CMOS input/output, L version)

• 55/70/85/100 ns access time

• Equal access and cycle time

• Single +2.2V to 2.7V Power Supply

• Tri-state output

• Automatic power-down when deselected

• Multiple center power and ground pins for

improved noise immunity

• Individual byte controls for both Read and

Write cycles

• Available in 44 pin TSOP (II) Package

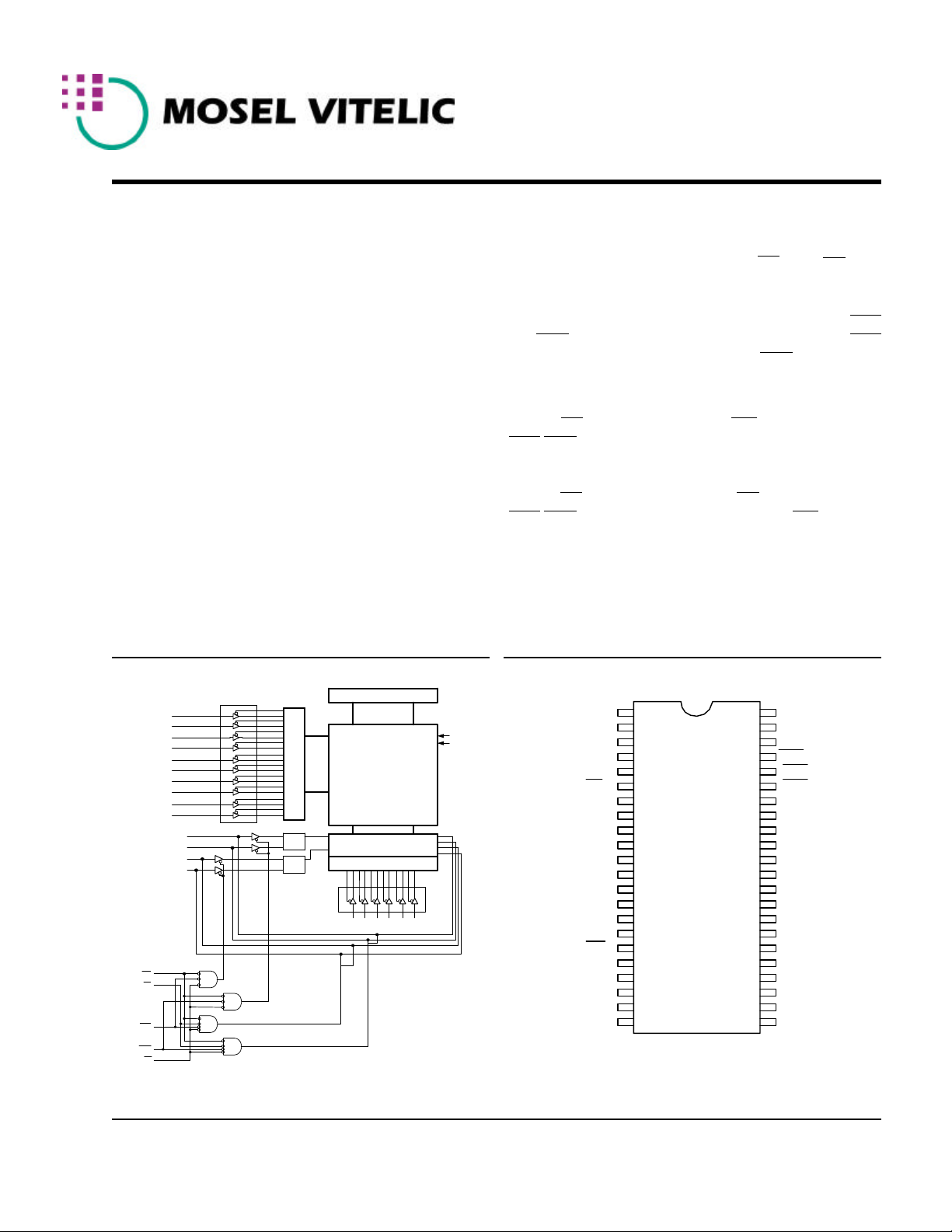

Logic Block Diagram

Functional Description

The V62C2161024L is a Low Power CMOS Static RAM

organized as 65,536 words by 16 bits. Easy memory expansion is provided by an active LOW (CE

) and (OE) pin.

This device has an automatic power-down mode feature

when deselected. Separate Byte Enable controls (BLE

and BHE) allow individual bytes to be accessed. BLE

controls the lower bits I/O1 - I/O8. BHE controls the

upper bits I/O9 - I/O16.

Writing to these devices is performed by taking Chip

Enable (CE

(BLE

) with Write Enable (WE) and Byte Enable

/BHE) LOW.

Reading from the device is performed by taking Chip

Enable (CE

(BLE

) with Output Enable (OE) and Byte Enable

/BHE) LOW while Write Enable (WE) is held

HIGH.

TSOP(II)

BHE

BLE

WE

OE

CE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

I/O1 - I/O8

I/O9 - I/O16

Row Select

Data

Cont

Data

Cont

Pre-Charge Circuit

Memory Array

1024 X 1024

I/O Circuit

Column Select

A10 A11 A12 A13 A14 A15

1

Vcc

Vss

A3

A2

A1

A0

CE

I/O1

I/O2

I/O3

I/O4

Vcc

Vss

I/O5

I/O6

I/O7

I/O8

WE

A15

A14

A13

A12 A11

NC

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

44

A5A4

43

A6

42

A7

OE

41

BHE

40

BLE

39

I/O16

38

I/O15

37

I/O14

36

I/O13

35

Vss

34

Vcc

33

I/O12

32

I/O11

31

I/O10

30

I/O9

29

NC

28

27A9A8

26

A10

25

24

NC

2322

1

REV. 1.1 April 2001 V62C2161024L(L)

V62C2161024L(L)

Absolute Maximum Ratings *

Parameter Symbol Minimum Maximum Unit

Voltage on Any Pin Relative to Gnd Vt -0.5 +4.6 V

Power Dissipation PT − 1.0 W

Storage Temperature (Plastic) Tstg -55 +150

Temperature Under Bias Tbias -40 +85

* Note: Stresses greater than those listed above Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and function operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect reliability.

0

C

0

C

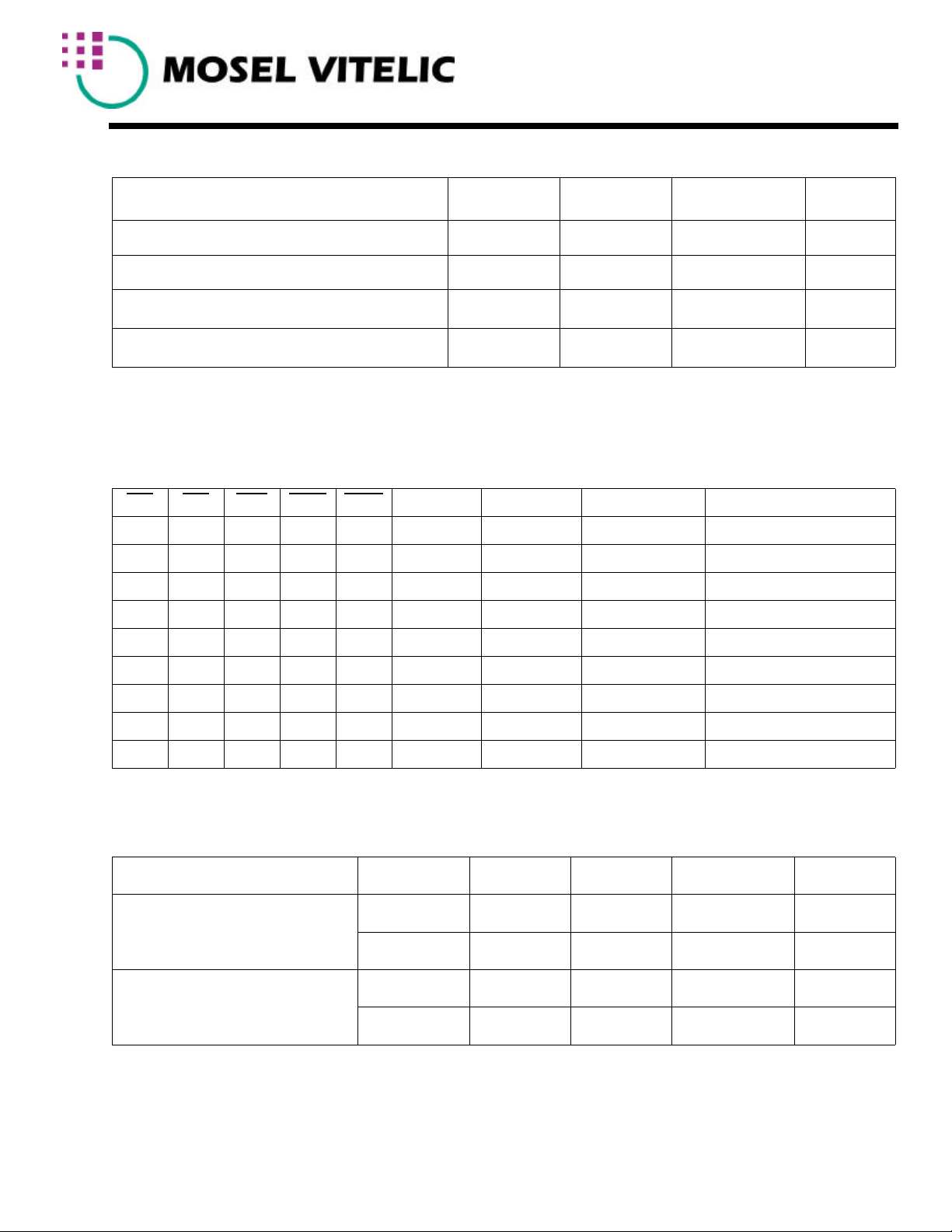

Truth Table

CE OE WE BLE BHE I/O1-I/O8 I/O9-I/O16 Power Mode

H X X X X High-Z High-Z Standby Standby

L L H L H Data Out High-Z Active Low Byte Read

L L H H L High-Z Data Out Active High Byte Read

L L H L L Data Out Data Out Active Word Read

L X L L L Data In Data In Active Word Write

L X L L H Data In High-Z Active Low Byte Write

L X L H L High-Z Data In Active High Byte Write

L H H X X High-Z High-Z Active Output Disable

L X X H H High-Z High-Z Active Output Disable

* Key: X = Don’t Care, L = Low, H = High

Recommended Operating Conditions (T

Parameter Symbol Min Typ Max Unit

Supply Voltage

Input Voltage

* VIL min = -2.0V for pulse width less than tRC/2.

** For Industrial Temperature

REV. 1.1 April 2001 V62C2161024L(L)

= 00C to +700C / -400C to 850C**)

A

V

CC

2.2 2.5 2.7 V

Gnd 0.0 0.0 0.0 V

V

IH

V

IL

2.0 - VCC + 0.2 V

-0.5* - 0.6 V

2

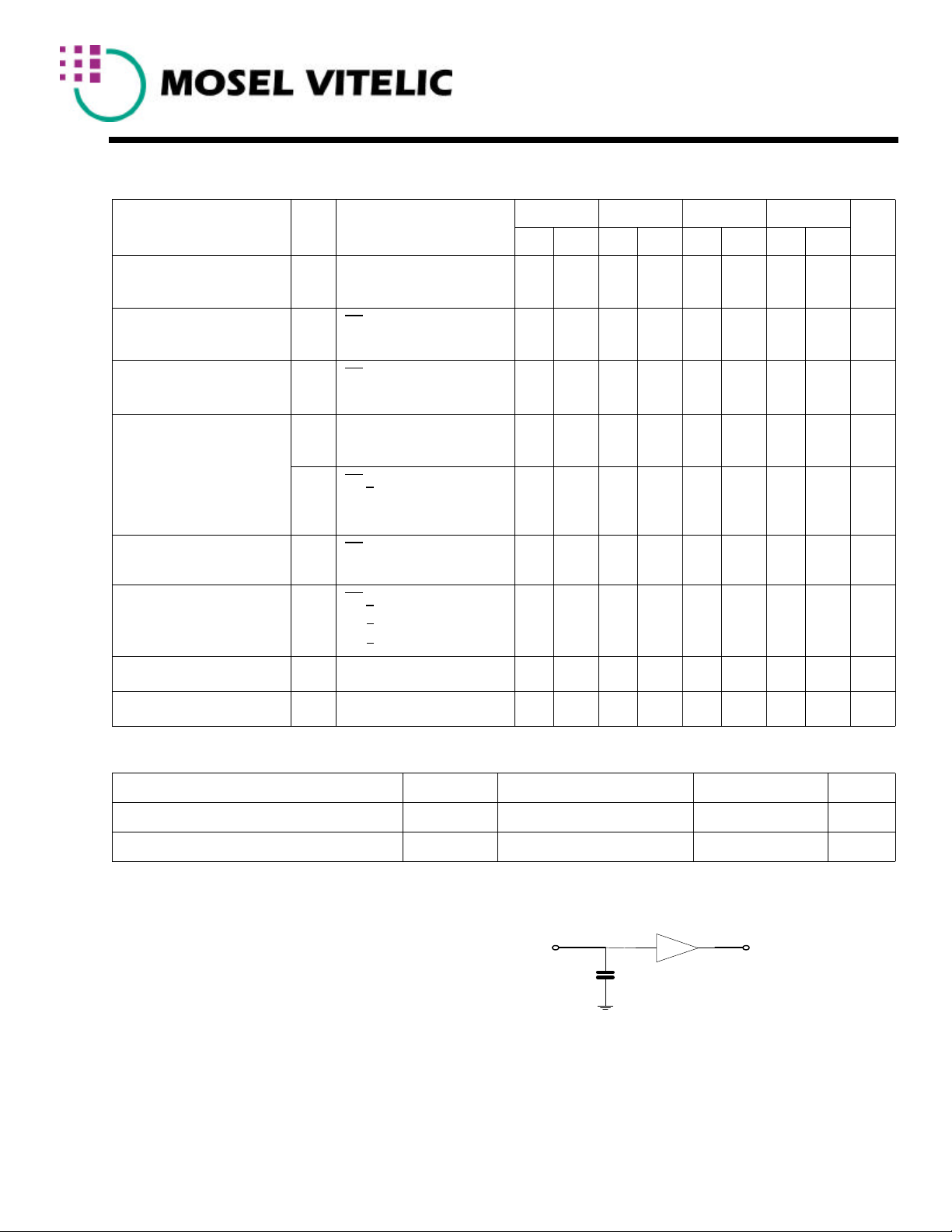

DC Operating Characteristics (V

V62C2161024L(L)

= 2.2 to 2.7V, Gnd = 0V, TA = 00C to +700C / -400C to 850C)

cc

Parameter Sym Test Conditions

Input Leakage Current

Output Leakage

Current

Operating Power

Supply Current

Average Operating

Current

Standby Power Supply

Current (TTL Level)

Standby Power Supply

Current (CMOS Level)

Vcc = Max,

II

II

I

CC

I

CC1

LI

LO

= Gnd to V

V

in

CE = VIH or Vcc= Max,

V

= Gnd to V

OUT

CE = VIL , VIN = V

I

= 0

OUT

I

= 0mA,

OUT

cc

cc

or V

IH

,

IL

Min Cycle, 100% Duty

CE < 0.2V

I

CC2

I

SB

I

SB1

= 0mA,

I

OUT

Cycle Time=1µs, Duty=100%

CE = VIH - 0.5 - 0.5 - 0.5 - 0.5 mA

CE > Vcc - 0.2V L

V

< 0.2V or

IN

V

> Vcc- 0.2V LL

IN

-55 -85 -100

Min Max Min Max Min Max Min Max

-70

Unit

- 1 - 1 - 1 - 1 µA

- 1 - 1 - 1 - 1 µA

- 3 - 3 - 3 - 3

- 35 - 30 - 25 - 25 mA

- 3 - 3 - 3 - 3 mA

-

5

-

5

-

5

-

5

-

1

-

1

-

1

-

1

mA

µA

µA

Output Low Voltage V

Output High Voltage V

Capacitance (f = 1MHz, T

IOL = 2 mA - 0.4 - 0.4 - 0.4 - 0.4 V

OL

IOH = -2 mA 2.0 - 2.0 - 2.0 - 2.0 - V

OH

= 25oC)

A

Parameter* Symbol Test Condition Max Unit

Input Capacitance

I/O Capacitance

* This parameter is guaranteed by device characterization and is not production tested.

AC Test Conditions

Input Pulse Level 0.6V to 2.0V

Input Rise and Fall Time 5ns

Input and Output Timing

Reference Level 1.2V

Output Load Condition

55ns/70ns/85ns C

Load for 100ns C

= 30pf + 1TTL Load

L

= 100pf + 1TTL Load

L

C

in

C

I/O

V

Vin = 0V 7 pF

= V

in

C

Figure A. * Including Scope and Jig Capacitance

= 0V 8 pF

out

*

L

TTL

REV. 1.1 April 2001 V62C2161024L(L)

3

Loading...

Loading...