Mosel Vitelic V58C3643204SAT Datasheet

MOSEL VITELIC

V58C3643204SAT

HIGH PERFORMANCE

3.3 VOLT 2M X 32 DDR SDRAM

4 X 512K X 32

45 50 55 60

PRELIMINARY

System Frequency (f

Clock Cycle Time (t

Clock Cycle Time (t

) 225MHz 200 MHz 183 MHz 166 MHz

CK

) 5 ns 5.5 ns 6 ns

CK3

)4.5ns

CK4

Features

■ 4 banks x 512K x 32 organization

■ High speed data transfer rates wi th system

frequency up to 225 MHz

■ Data Mask for Write Control (DM)

■ Four Banks controlled by BA0 & BA 1

■ Programmable C AS

■ Programmable Wra p Sequence: Sequential

or Interleave

■ Programmable Burst Length:

2, 4, 8 full page for Sequential Type

2, 4, 8 full page for Interleave Type

■ Automatic and Control led Precharge Command

■ Suspend Mode and Power Down Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval: 2048 cycles/16ms

■ Available in 100-pin TQFP

■ SSTL-2 Compatible I/Os

■ Double Data Rate (DDR)

■ Bidirectional Data Strobe (DQs ) for input and

output data, active on both edges

■ On-ChipDLL aligns DQ andDQs transitions with

CLK transitions

■ Differential clock inputs CLK and CLK

■ Power Supply 3.3V ± 0.3V

Latency: 3, 4

Description

The V58C3643204SAT is a four bank DDR

DRAM organized as 4 banks x 512K x 32. The

V58C3643204SAT achieves high speed data

transfer rates by employing a chip architecture that

prefetches multiple bits and then synchronizes the

output data to a system clock

All of the control, address, circuits are synchronized with t he positive edge of an externally supplied clock. I/O transactions are possible on both

edges of DQS.

Operating the four memory bank s in an interleaved fashion al lows random access operation to

occur at a higher rate than is possible with standard

DRAMs. A sequential and gapless data rate is possible depending on burs t length, CAS

speed grade of t he device.

latency and

Device Usage Chart

Operating

Temperature

Range

0°Cto70°C • •••• • • Blank

V58C3643204SAT Rev.1.4 August 2001

Package Outline CLK Cycle Time (ns) Power

Temperature

Mark100-pin TQFP -45 -50 -55 -60 Std. L

1

MOSEL VITELIC

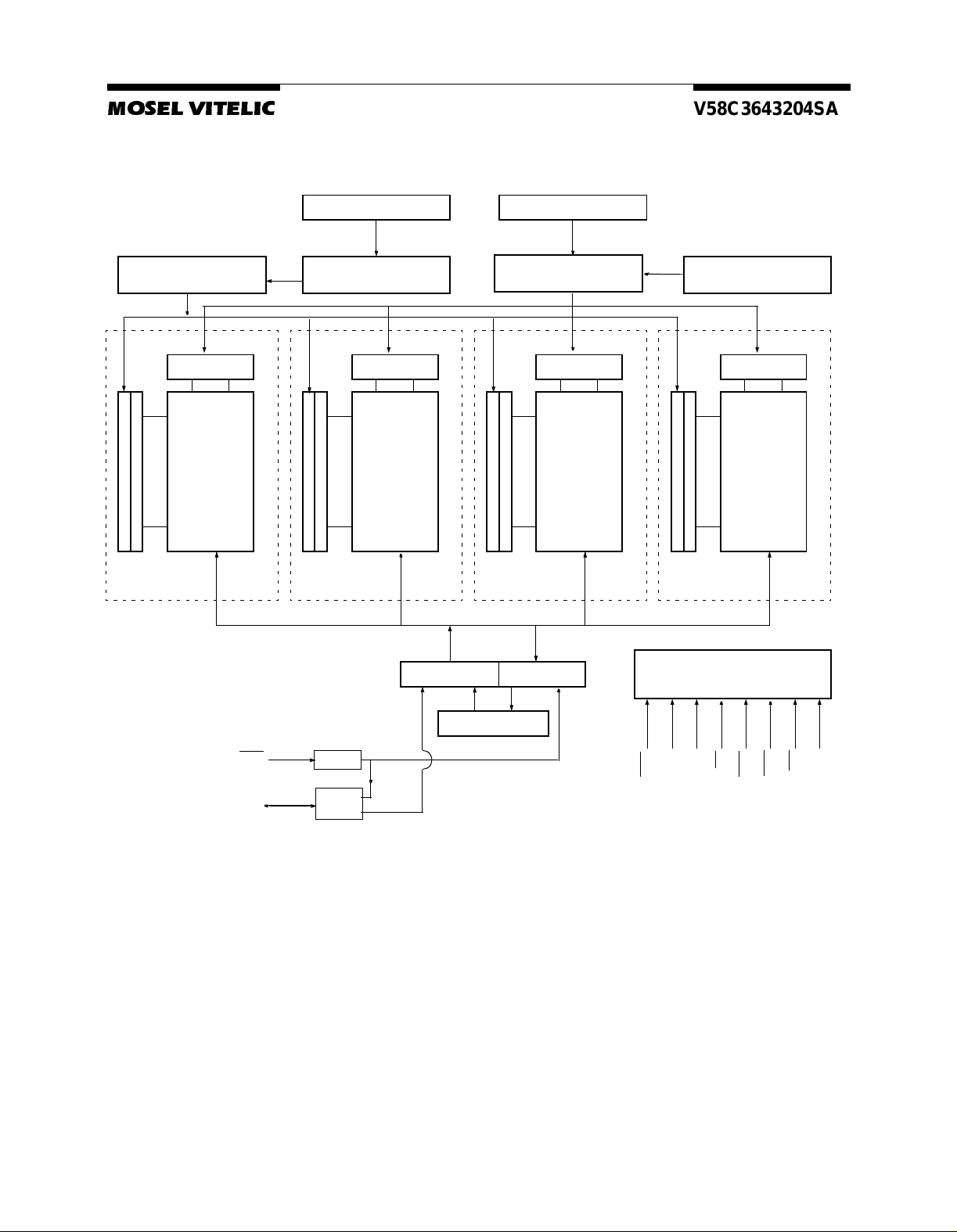

Block Diagram

V58C3643204SAT

Columnaddress

counter

Row decoder

Memory array

Column decoder

Sense amplifier & I(O) bus

Bank 0

Column Addresses

Columnaddress

buffer

Row decoder

Memoryarray

Bank 1

512K x 32

Column decoder

Sense amplifier & I(O) bus

Row Addresses

A0 - A10, BA0,BA1A0 - A7, AP, BA0, BA1

Row addres s

Row decoder

Memory array

Columndecoder

Sense amplifier & I(O) bus

buffer

Bank 2

512K x 32 512K x 32512K x 32

RefreshCounter

Row decoder

Memory array

Bank 3

Column decoder

Sense amplifier & I(O) bus

CLK, CLK

DQS

DLL

Strobe

Gen.

Input buffer Output buffer

DQ0-DQ

Data Strobe

Control logic & timing generator

CLK

CLK

CS

CKE

RAS

WE

CAS

DM0-DM3

V58C3643204SAT Rev.1.4 August 2001

2

MOSEL VITELIC

V58C3643204SAT

DQ29

VSSQ

DQ30

DQ31

VSS

VDDQ

N.C

N.C

N.C

N.C

N.C

VSSQ

RFU

DQS

VDDQ

VDD

DQ0

DQ1

VSSQ

DQ2

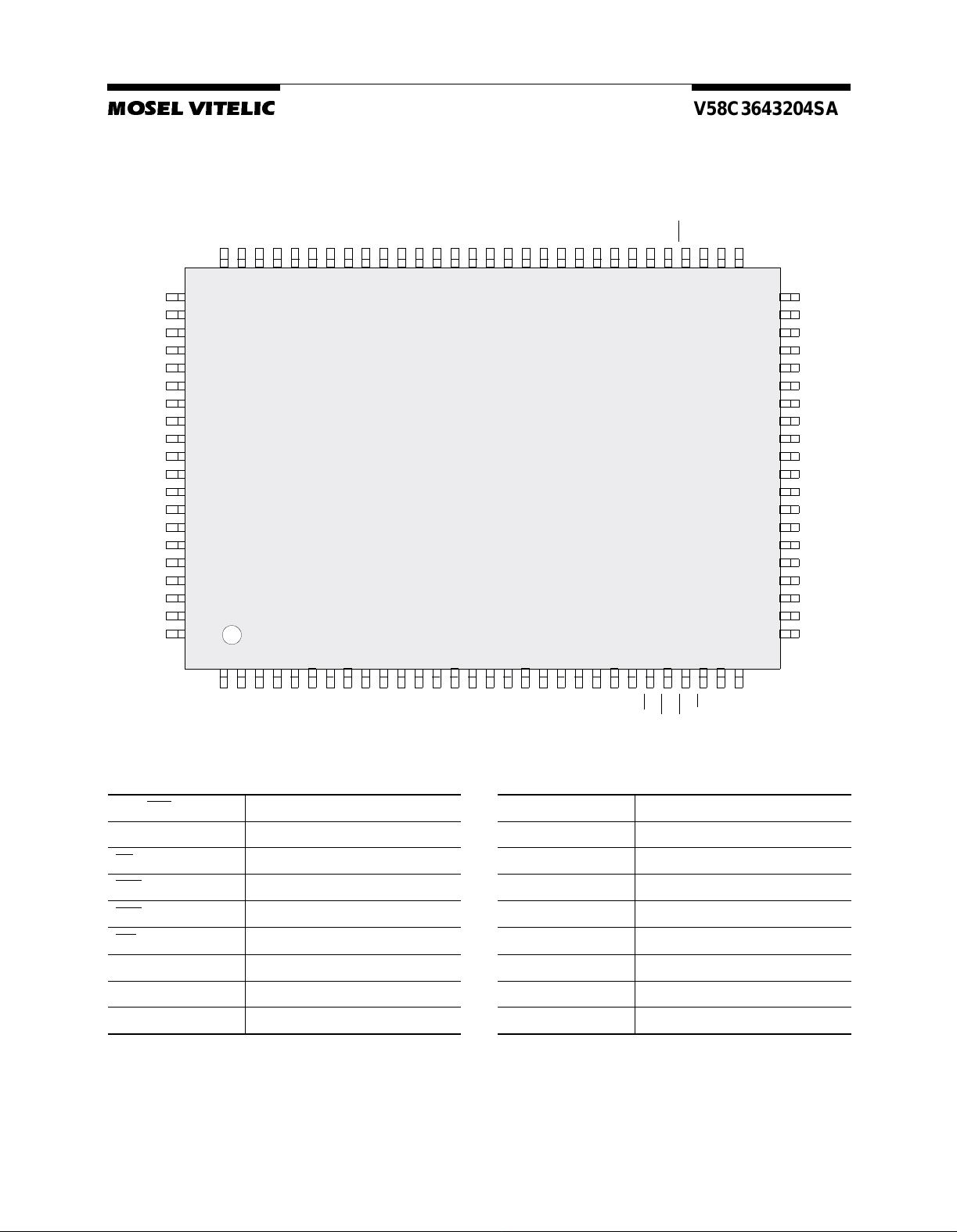

100 Pin TQ FP

Top View

PIN CONFIGURATION

DQ28

VDDQ

DQ27

DQ26

VSSQ

DQ25

DQ24

VDDQ

DQ15

DQ14

VSSQ

DQ13

DQ12

VDDQ

VSS

VDD

DQ11

DQ10

VSSQ

DQ9

DQ8

VDDQ

VREF

DM3

DM1

8079787776757473727170696867666564636261605958575655545352

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1234567891011121314151617181920212223242526272829

100 Pin TQFP

20 x 14 mm

2

0.65mm pin Pitch

CLK

CLK

CKE

MCL

A8(AP)

51

50

A7

49

A6

48

A5

47

A4

46

VSS

45

A9

44

N.C

43

N.C

42

N.C

41

N.C

40

N.C

39

N.C

38

N.C

37

N.C

36

A10

35

VDD

34

A3

33

A2

32

A1

31

A0

30

DQ3

DQ4

DQ5

DQ6

DQ7

VDDQ

VSSQ

VDDQ

DQ16

Pin Names

CLK, CLK DifferentialClock Input

CKE Clock Enable

CS

RAS

CAS

WE

DQS Data Strobe (Bidirectional)

A

0–A10

BA0, BA1 Bank Select

Chip Select

Row Address Strobe

Column Address Strobe

WriteEnable

Address Inputs

CAS

RAS

CS

BA0

BA1

VSS

DQ17

DQ18

VSSQ

VDD

DQ19

VDDQ

DQ20

DQ21

DQ0–DQ

VSSQ

7

DQ22

DQ23

VDDQ

WE

DM0

DM2

Data Input/Output

DM0-DM3 Data Mask

V

V

V

V

DD

SS

DDQ

SSQ

Power(3.3V± 0.3V)

Ground

Powerfor I/O’s(+2.5V)

Ground for I/O’s

NC Not connected

VREF Reference Voltage for Inputs

RFU Reserved for future use.

V58C3643204SAT Rev.1.4 August 2001

3

MOSEL VITELIC

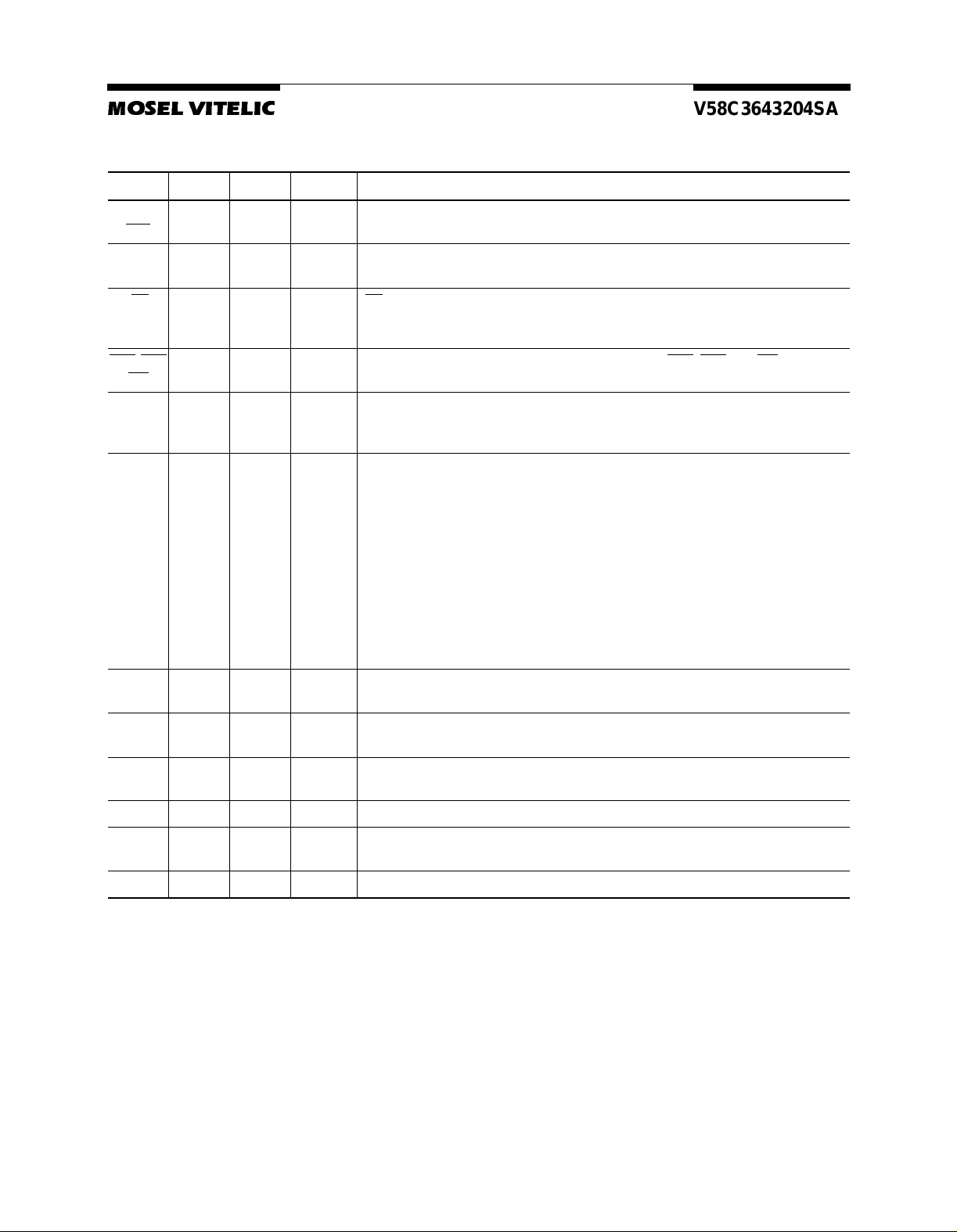

Signal Pin Description

Pin Type Signal Polarity Function

V58C3643204SAT

CLK CLK

CKE Input Level Active High Activatesthe CLK signalwhen high and deactivatesthe CLK signal when low, thereby

CS

RAS

,CASWEInput Pulse Active Low When sampled at the positive rising edge of the clock, CAS,RAS,andWEdefinethe

DQS Input/

A0 - A10 Input Level — Duringa Bank Activate command cycle, A0-A10defines the row address ( RA0-RA10)

Input Pulse Positive

Edge

Input Pulse Active Low CS enables the commanddecoder whenlow and disables the command decoderwhen

Pulse Active High Active on both edges for data input and output.

Output

The systemclock input. All inputsexcept DQs and DMs are sampled on the risingedge

of CLK.

initiates either the Power Down mode, Suspend mode,or the Self Refresh mode.

high. When the command decoder is disabled, new commands are ignored but previous

operations continue.

command to be executedby the SDRAM.

Centeraligned to input data

Edge aligned to output data

when sampledat the risingclock edge.

Duringa Read or Write commandcycle, A0-An defines the columnaddress (CA0-CAn)

when sampled at the rising clock edge. CAn depends from the SDRAM organization:

2M x 32 SDRAM CAn = CA7 (Page)

In addition to the column address, A8 is used to invoke autoprecharge operation at the

endof theburstreador writecycle.If A8is high,autoprechargeis selectedand BA0,BA1

defines the bank to be precharged. If A8 is low, autoprecharge is disabled.

Duringa Precharge command cycle, A8(=AP)is used in conjunction with BA0 and BA1

to controlwhich bank(s) to precharge.If A10 is high, allf our banks will be precharged

simultaneously regardless of state of BA0 and BA1.

BA0,

BA1

DQx Input/

DM0-DM3 Input Pulse Active High InWrite mode, DM has a latencyof zero and operates as a word maskby allowing input

VDD, VSS Supply Power and groundfor the input buffers and the core logic.

VDDQ VSSQ

VREF Input Level — SSTL Reference Voltage for Inputs

Input Level — Selects which bank is to be active.

Level — Data Input/Outputpins operate in the same manner as on conventionalDRAMs.

Output

data to be written if it is low but blocks the write operation if is high.

Supply ——Isolated power supply and ground for the output buffers to provide improved noise

immunity.

V58C3643204SAT Rev.1.4 August 2001

4

Loading...

Loading...