Mosel Vitelic V58C2128804SXT8, V58C2128804SXT75, V58C2128804SXT7, V58C2128804SXT6, V58C2128404SXT8 Datasheet

...

MOSEL VITELIC

1

V58C2128(804/404/164)S

HIGH PERFORMANCE

2.5 VOLT 128 Mbit DDR SDRAM

4 BANKS X 4Mbit X 8 (804)

4 BANKS X 2Mbit X 16 (164)

4 BANKS X 8Mbit X 4 (404)

PRELIMINARY

V58C2128(804/404/164)S Rev.1.6 March 2002

67758

DDR333B DDR266A DDR266B DDR200

Clock Cycle Time (t

CK2

) 7.5 ns 7.5ns 10 ns 10 ns

Clock Cycle Time (t

CK2.5

) 6 ns 7ns 7.5 ns 8 ns

System Frequency (f

CK max

) 167 MHz 143 MHz 133 MHz 125 MHz

Features

■ High speed data transfer rates with system

frequency up to 166 MHz

■ Data Mask for Write Control

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS

Latency: 2, 2.5

■ Programmable Wrap Sequence: Seq uential

or Interleave

■ Programmable Burst Length:

2, 4, 8 for Sequential Type

2, 4, 8 for Interleave Type

■ Automatic and Controlled Precharge Command

■ Power Down Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval: 40 96 cycl e s/64 ms

■ Available in 66-pin 400 mil TSOP

■ SSTL-2 Compatible I/Os

■ Double Data Rate (DDR)

■ Bidirectional Data Strobe (DQS) for input and

output data, active on both edges

■ On-Chip DLL aligns DQ and DQs transitions with

CK transitions

■ Differential clock inputs CK and CK

■ Power Supply 2.5V ± 0.2V

■ QFC

options for FET control. x4 parts.

*Note: DDR 333B Supports PC2700 module with 2.5-3-3 timing

DDR 266A Supports PC2100 module with 2-3-3 timing

DDR 266B Supports PC2100 module with 2.5-3-3 timing

DDR 200 Supports PC1600 module with 2-2-2 timing

Description

The V58C2128(804/404/164)S is a four bank

DD R DRAM o rganized as 4 banks x 4M bi t x 8 (804 ),

4 banks x 2Mbit x 16 (404), or 4 banks x 8Mbit x 4

(164). The V58C2 128(804/404/16 4)S ach ieve s h igh

speed data transfer rates by employing a chip architecture that prefetches multipl e bits and then synchronizes the output data to a system clock.

All of the control, address, circuits are synchronized with the positive edge of an externally supplied clock. I/O transactions are ocurring on both

edges of DQS.

Operating the four memory banks in an interleaved fashion allows random a ccess operation to

occur at a higher rate than is possible with standard

DRAMs. A sequential and gapless data rate is possible depending on burst length, CAS

latency and

speed grade of the device.

Device U sage Chart

Operating

Temperature

Range

Package Outline CK Cycle Time (ns) Power

Temperature

MarkJEDEC 66 TS O P II -6 -7 -75 -8 Std. L

0°C to 70° C • • • • • • • Blank

2

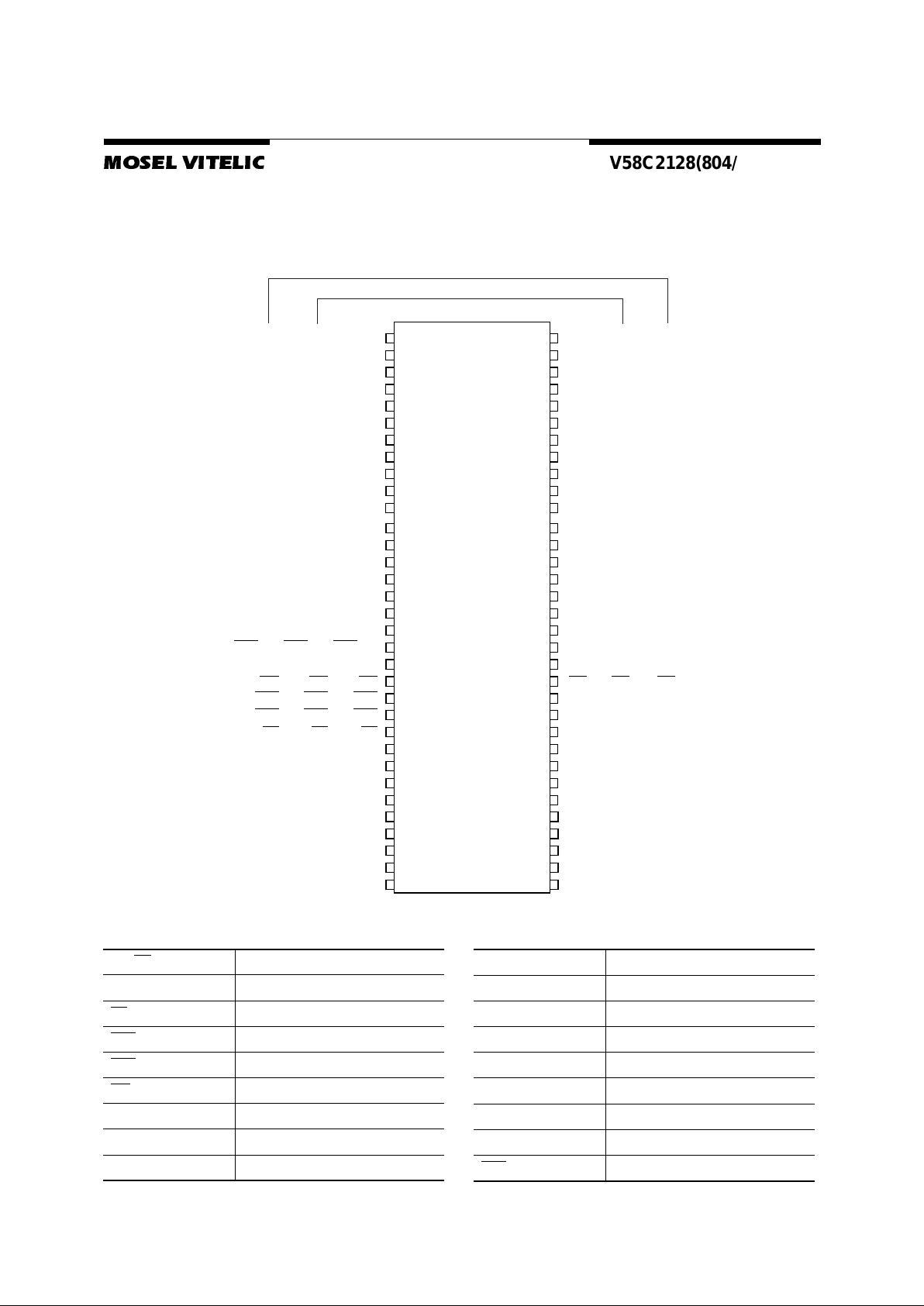

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

66 Pin Plastic TSOP -I I

PIN CONFIGURATION

Top View

1

2

3

4

5

6

9

10

11

12

13

14

7

8

15

16

17

18

19

20

21

22

66

65

64

63

62

61

58

57

56

55

54

53

60

59

52

51

50

49

48

47

46

45

23

24

25

44

43

42

26

27

41

40

28

29

30

31

32

33

39

38

37

36

35

34

V

DD

NC

V

DDQ

NC

DQ

0

V

SSQ

V

DDQ

NC

DQ

1

V

SSQ

NC

NC

NC

NC

V

DDQ

NC

NC

V

DD

NC

WE

CAS

RAS

CS

NC

BA

0

BA1

V

SS

NC

V

SSQ

NC

DQ

3

V

DDQ

V

SSQ

NC

DQ

2

V

DDQ

NC

NC

NC

NC

V

SSQ

DQS

NC

V

REF

V

SS

DM

CK

CK

CKE

NC

NC

A

11

A

9

AP/A10

A0

A

1

A

2

A

3

V

DD

V

DD

DQ

0

VDDQ

NC

DQ

1

V

SSQ

V

DDQ

NC

DQ

3

V

SSQ

NC

NC

NC

DQ

2

V

DDQ

NC

NC

V

DD

NC

WE

CAS

RAS

CS

NC

BA

0

BA1

AP/A10

A0

A

1

A

2

A

3

V

DD

V

DD

DQ

0

V

DDQ

DQ

1

DQ

2

V

SSQ

V

DDQ

DQ

5

DQ

6

V

SSQ

DQ

7

NC

DQ

3

DQ

4

V

DDQ

LDQS

NC

V

DD

Q

FC/NC

NC

WE

QFC/NC QFC/NC

CAS

RAS

CS

NC

BA

0

BA1

AP/A10

A0

A

1

A

2

A

3

V

DD

A

8

A

7

A

6

A

5

A

4

V

SS

A

11

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

A

11

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

V

SS

DQ

7

V

SSQ

NC

DQ

5

V

DDQ

V

SSQ

NC

DQ

4

V

DDQ

NC

NC

NC

DQ

5

V

SSQ

DQS

NC

V

REF

V

SS

DM

CK

CK

CKE

NC

NC

V

SS

DQ

15

V

SSQ

DQ

14

DQ

13

V

DDQ

V

SSQ

DQ

10

DQ

9

V

DDQ

DQ

8

NC

DQ

12

DQ

11

V

SSQ

UDQ

S

NC

V

REF

V

SS

UDM

CK

CK

CKE

NC

NC

66 PIN TSOP (II)

(400mil x 875 mil)

Bank Address

BA0-BA1

Row Address

A0-A11

Auto Precharge

A10

8Mb x 16

16Mb x 8

32Mb x 4

Pin Names

CK, C K Differential Clo ck Inpu t

CKE Clock Enable

CS

Chip Select

RAS

Row Address Strobe

CAS

Column Address Strobe

WE

Write Enable

DQS (UDQS, LDQS) Data Strobe (Bidirectional)

A

0–A11

Address Inputs

BA0, BA1 Bank Select

DQ’s Data Input/Output

DM (UDM, LDM) Data Mask

V

DD

Power (+2.5V)

V

SS

Ground

V

DDQ

Power for I/O’s (+2.5V)

V

SSQ

Ground for I/O’s

NC Not connected

VREF Refer ence Voltage for Inputs

QFC

FET Control

MOSEL VITELIC

V58C2128(804/404/164)S

3

V58C2128(804/404/164)S Rev. 1.6 March 2002

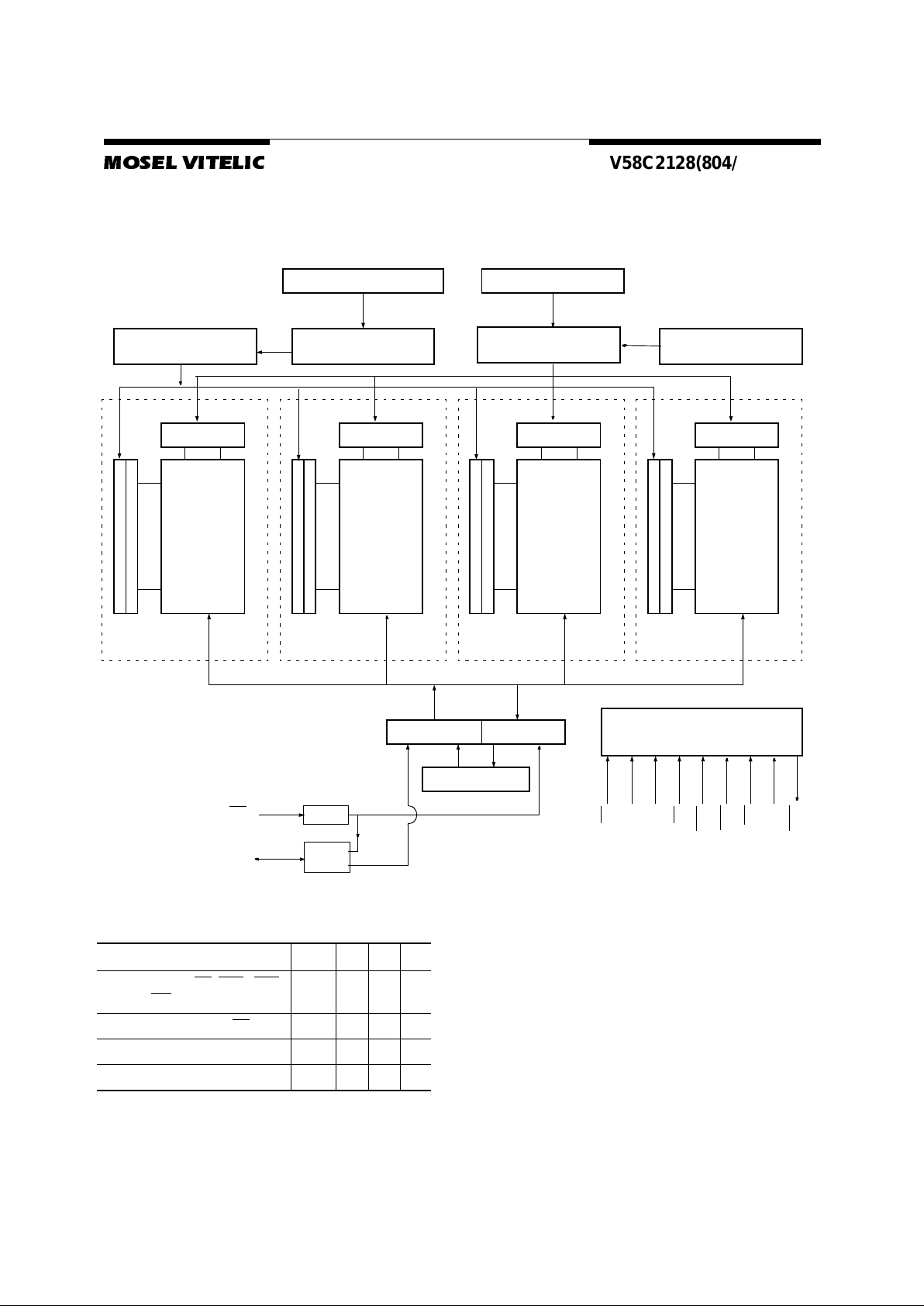

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 1024

x 8

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 1

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 2

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory ar ray

Bank 3

Column decoder

Sense amplifier & I(O) bus

Input buffer Output buffer

DQ0-DQ

3

Column address

counter

Colum n ad dr e ss

buffer

Row address

buffer

Refresh Counter

A0 - A11, BA0, BA1A0 - A9, A11, AP, BA0, BA1

Control logic & timing generator

CK

CKE

CS

RAS

CAS

WE

DM

Row Addresses

Column Addresses

DLL

Strobe

Gen.

Data Strobe

CK, CK

CK

DQS

QFC

4096 x 1024

x 8

4096 x 1024

x 8

4096 x 10 24

x 8

32M x 4

V 58 C 2 128(80/40/16) 4 S X T XX

DDRSDRAM

CMOS

2.5V

128Mb, 4K Refresh

4 Banks

COMPONENT

REV LEVEL

COMPONENT

PACKAGE, T = TSOP

SSTL

SPEED

6 (166MHZ@CL2.5)

MOSEL VITELIC

MANUFACTURED

7 (143MHZ@CL2.5))

75(133MHZ@CL2.5)

x8, x4, x16

8 (125MHZ@CL2.5)

4

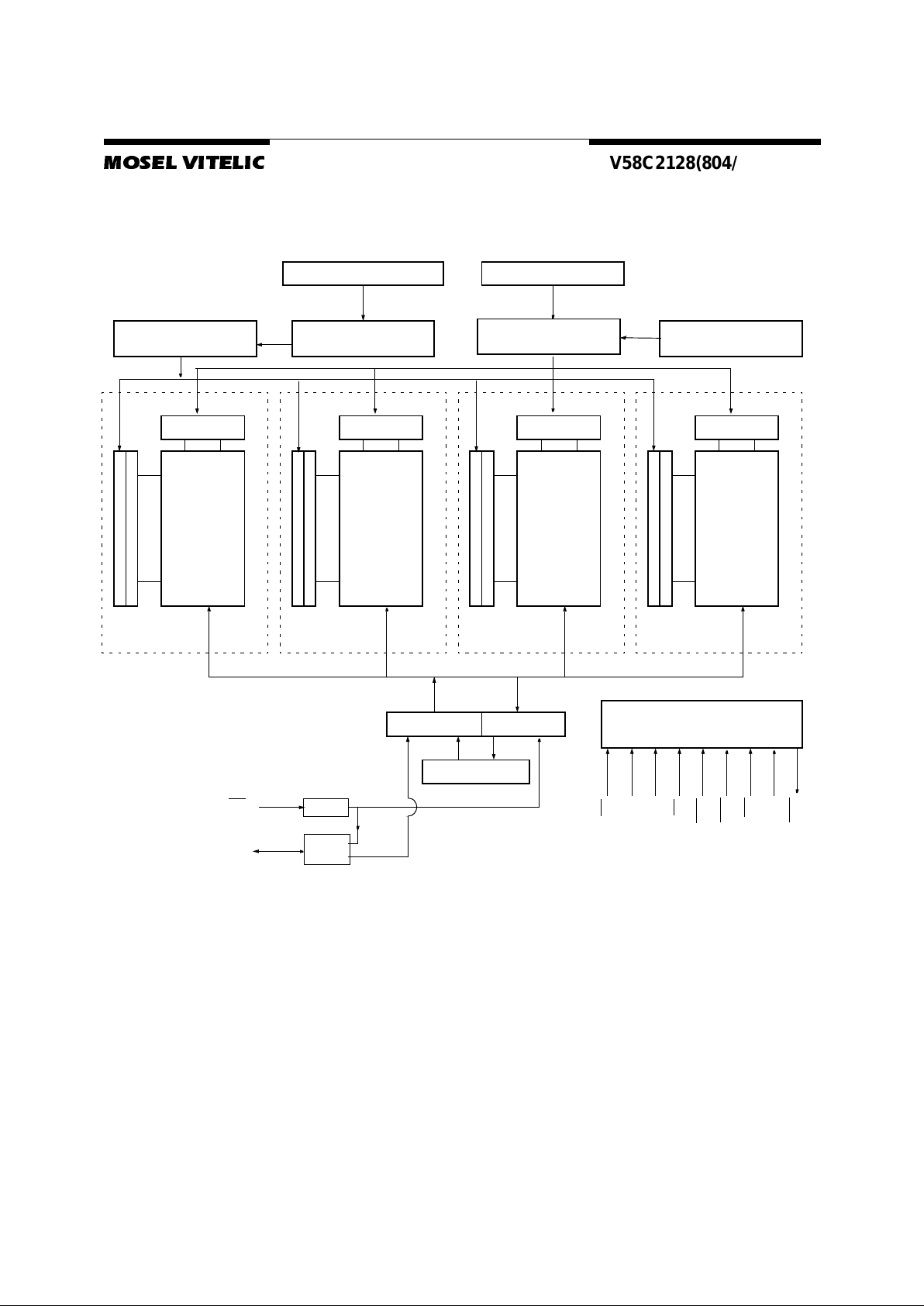

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 512

x 16 bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory ar ray

Bank 1

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 2

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 3

Column decoder

Sense amplifier & I(O) bus

Input buffer Output buffer

DQ0-DQ

7

Column address

counter

Column address

buffer

Row address

buffer

Refresh Counter

A0 - A11, BA0, BA1A0 - A9, AP, BA0, BA1

Contr ol lo gi c & timing generator

CK

CKE

CS

RAS

CAS

WE

DM

Row Addresses

Column Addresses

DLL

Strobe

Gen.

Data Strobe

CK, CK

CK

DQS

QFC

16M x 8

4096 x 51 2

x 16 bit

4096 x 512

x 16 bit

4096 x 512

x 16 bit

5

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 256

x 32 bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory ar ray

Bank 1

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 2

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 3

Column decoder

Sense amplifier & I(O) bus

Input buffer Output buffer

DQ0-DQ

15

Column address

counter

Column address

buffer

Row address

buffer

Refresh Counter

A0 - A11, BA0, BA1A0 - A8, AP, BA0, BA1

Contr ol lo gi c & timing generator

CK

CKE

CS

RAS

CAS

WE

DM

Row Addresses

Column Addresses

DLL

Strobe

Gen.

Data Strobe

CK, CK

CK

DQS

QFC

4096 x 256

x 32 bit

4096 x 256

x 32 bit

4096 x 256

x 32 bit

8M x 16

Capacitance*

TA = 0 to 70°C, VCC = 2.5V ± 0.2V, f = 1 Mhz

*Note: Capacitance is sampled and not 100% tested.

Absol u te M aximum Ratings*

Operating temperature range..................0 to 70 °C

Storage temperature range ................-55 to 150 °C

V

DD

Supply Voltage Relative to VSS.....-1 V to +3.6V

V

DDQ

Supply Voltage Relative to V

SS

......................................................-1V to +3.6V

VREF and Inputs Voltage Relative to V

SS

......................................................-1V to +3.6V

I/O Pins Voltage Relative to V

SS

..........................................-0.5V to V

DDQ

+0.5V

Power dissipation............................ ..............1.6 W

Data out current (short circuit) ...................... 50 mA

*Note: Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage of the device.

Exposure to absolute maximum rating conditions for

extended period s may affect device reliability.

Inpu t Capacit ance

Symbol

Min Max Unit

BA0, BA1, CKE, CS, RAS, (CAS,

A0-A11, WE

)

C

INI

23.0pF

Input Ca pacitance (CK, CK

)C

IN2

23.0pF

Data & DQS I/O Capacitance C

OUT

45pF

Input Capacitance (DM) C

IN3

45.0pF

6

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

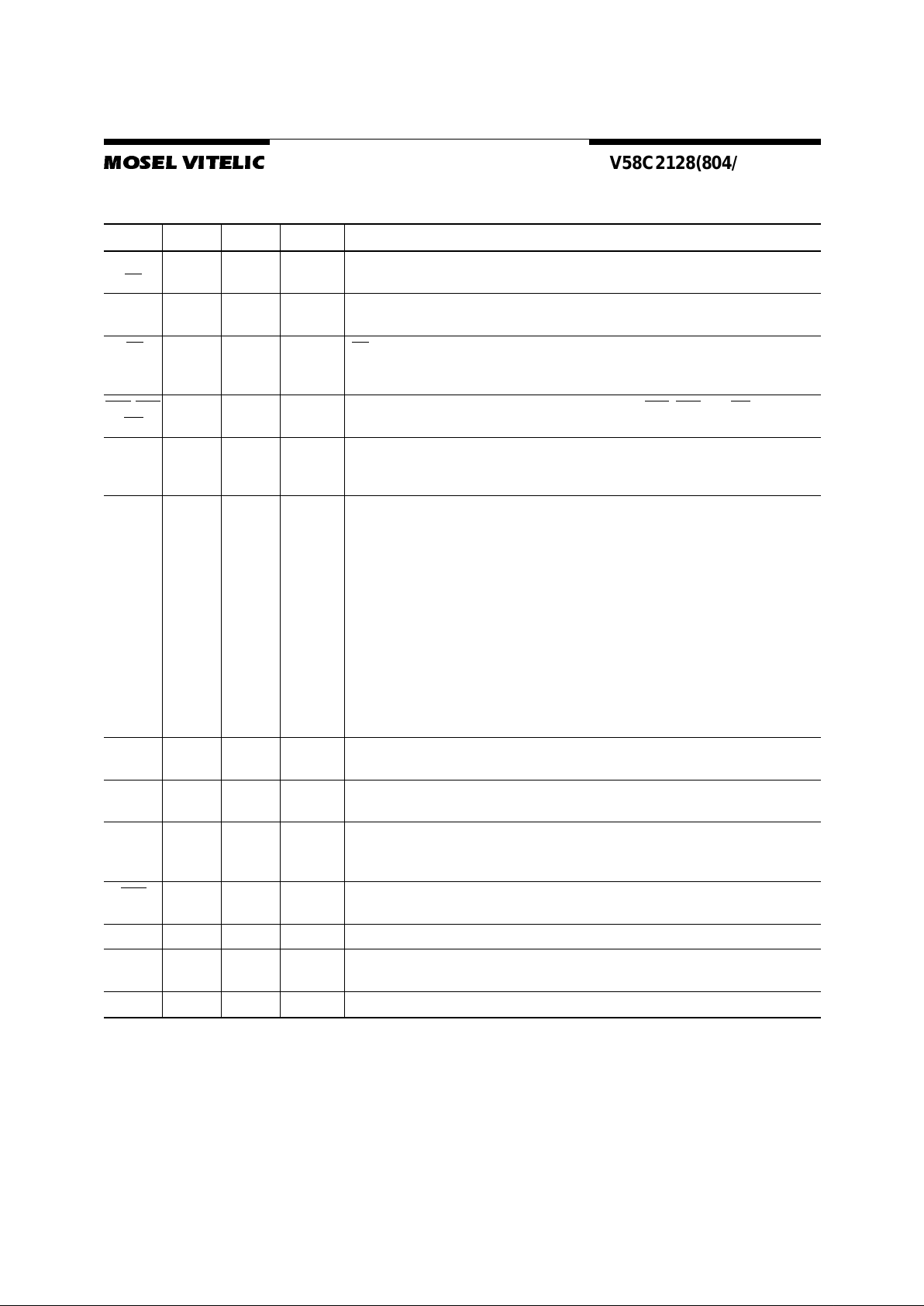

Signal Pi n D escription

Pin Type Signal Polarity Function

CK

CK

Input Pulse Positive

Edge

The system clock input. All inpu ts except DQs and DMs are sampled on the rising edge

of CK.

CKE Input Level Active High Activates the CK signal when high and deactivates the CK signal when low, thereby ini-

tiates either the Power Down mode, or the Self Refresh mode.

CS

Input Pulse Active Low CS enables the command decoder when lo w and disables the comm and decoder when

high. Wh en the co mma nd de co der i s d is ab led, ne w com man ds ar e ign or e d but pr ev ious

operations continue.

RAS

, CAS WEInput Pulse Active Low When sampled at the posit ive rising edge of the clock, CAS, RAS, and WE define the

command to be executed by the SDR AM.

DQS Input/

Output

Pulse A ctive Hi gh Active on both edges for data input and output.

Center aligned to input data

Edge aligned to output data

A0 - A11 Input Level — During a Bank Activate command cycle, A0-A11 defines the row addr ess (RA0- RA11)

when sampled at the rising clock edge.

During a Read or Wr ite command cycle, A0-An defines the c olumn addr ess (CA0- CAn)

when sampled at the rising clock edge.CAn depends on th e SDRAM organizati on:

32M x 4 DDR CAn = CA9, A11

16M x 8 DDR CAn = CA9

8M x 16 DDR CAn = CA8

In addition to the col umn address, A10(=AP) is used to invoke autoprecharge operati on

at the end of the bu rst read or write cycle. If A10 is high, autoprecharge is selected and

BA0, BA1 define s the bank to be precharged. If A10 is low, autoprecharge is disabled.

During a Pr ec har ge comman d c ycl e , A1 0( =AP ) i s us ed in conj un ct io n wi th B A0 a nd BA1

to control which bank(s) to precharge. If A10 is high, all four banks will be precharged

simultaneously regar dless of state of BA0 and BA1.

BA0,

BA1

Input Level — Selects whic h bank is to be active.

DQx Input/

Output

Level — Data Input/Output pins operate in the same manner as on conventional DRAMs.

DM,

LDM,

UDM

Input Pulse Active High In Write mode, DM has a latency of zero and operates as a word mask by allowing input

data to be written if it is low but blocks the write operation if is high for x 16 LDM

corresponds to data on DQ0-D Q7, UDM c orresponds to data on DQ8-D Q 15.

QFC

Output Level Active Low FET Control: Output during every read and write access. Can be used to control isolation

switche s on modules.

VDD, VSS Supply Power an d ground for the inp ut bu ff e rs and the core logic .

VDDQ

VSSQ

Supply — — Isolated power supply and ground for the output buffers to provide improved noise

immunity.

VREF Input Lev el — S ST L R eference Voltage for Inpu ts

7

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Address Bus

CAS

Latency

A6A5A4Latency

0 0 0 Reserve

0 0 1 Reserve

01 0 2

01 1 3

1 0 0 Reserve

Reserve

10 1

1 1 0 2.5

1 1 1 Reserve

Burst Length

A2A1A

0

Latency

Sequential Interleave

0 0 0 Reserve Reserve

001 2 2

010 4 4

011 8 8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

1 1 1 Reserve Reserve

A

7

mode

0

Normal

1

Test

A3Burst Type

0 Sequential

1 Interleave

* RFU(Reserved for future use)

should stay "0" during MRS

cycle.

A8DLL Reset

0No

1 Yes

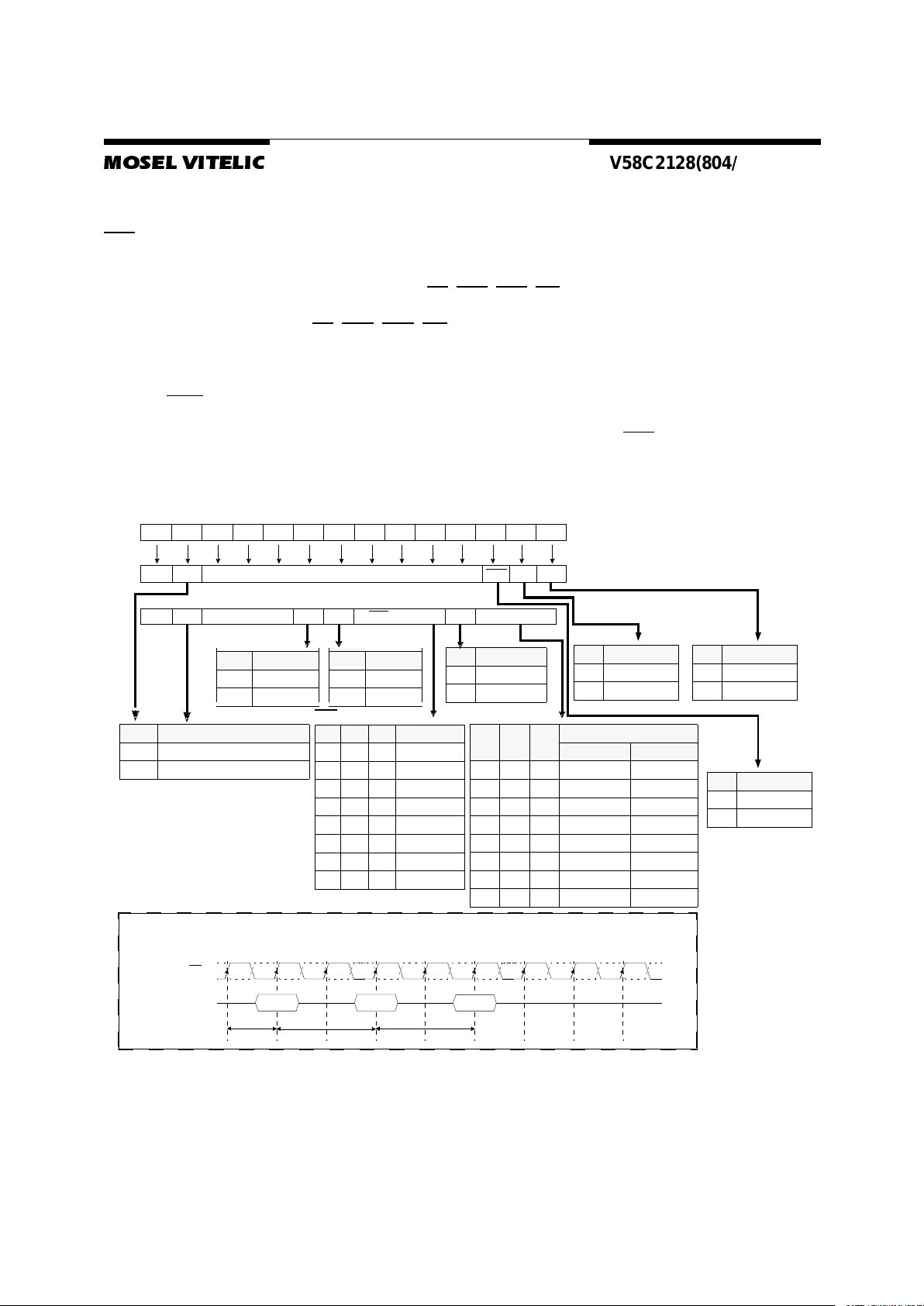

Mode Register Set

0 RFU : Must be set "0"

Extended Mode Register

Mode Register

DLLI/OQFC

A0DLL Enable

0 Enable

1 Disable

A2QFC Contro

l

0 Disable

1 Enable

A1I/O Strength

0 Full

1 Half

BA

0

An ~ A

0

0 (Existing)MRS Cycle

1 Extended Funtions(EMRS)

Command

201 534 867

CK, CK

t

CK

t

MRD

Precharge

All Banks

Mode

Register Set

t

RP

*2

*1

Any

Command

BA1BA0A11A10A9A8A7A6A5A4A3A2A1A

0

0TM

CAS Latency

BT Burst LengthRFU DLL

MRS

MRS

Mode Register Set (MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs

CAS

latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to

make DDR SDRAM useful for a variety of different applicati ons. The default value of the mode register is not

defined, therefore the mode register must be written after EMRS setting for proper DDR SDRAM operation.

The mode register is written by asserting low on CS

, RAS, CAS, WE and BA0 (The DDR SDRAM should be

in all bank precharge with CKE already high prior to writing into the mode register). The state of address pins

A

0

~ A11 in the same cycle as CS, RAS, CAS, WE and BA0 low is written in the mode reg ister. Two cl ock

cycles are required to meet t

MRD

spec. The mode register contents can be changed us ing the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A

0

~ A2, addressing mode

uses A

3

, CAS latency (read latency from column address) uses A4 ~ A6. A7 is a Mosel Vit elic spe cific tes t

mode during production test. A

8

is used for DLL reset. A7 must be set to low for normal MRS operation. Refer

to the table for specific codes for various burst length, addressing modes and CAS

latencies .

1. MRS can be issued only at all banks precharge state.

2. Minimum tRP is required to issue MRS command.

8

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

Mode Register Set Timing

Burst Mode Operation

Burst Mode Operation i s used to pro vide a consta nt flow of data to memory loca tions (Write cycle), or from

memory locations (Read cycle). Two parameters define how the burst mode will operate: burst sequence and

burst length. These p arameters are programma ble and are determined by a ddress bits A

0—A3

during the

Mode Register Set command. B urst t ype defi nes the sequence in whic h the burst data will be delivered or

stored to the SDRA M. Two types of burst sequenc e are supported: sequential and interlea ve. The burst

length controls the number of bits that will be output after a Read command, or the number of bits to be input

after a Write command. The burst length can be programmed to values of 2, 4, or 8. See the Burst Length

and Sequence table below for programming information.

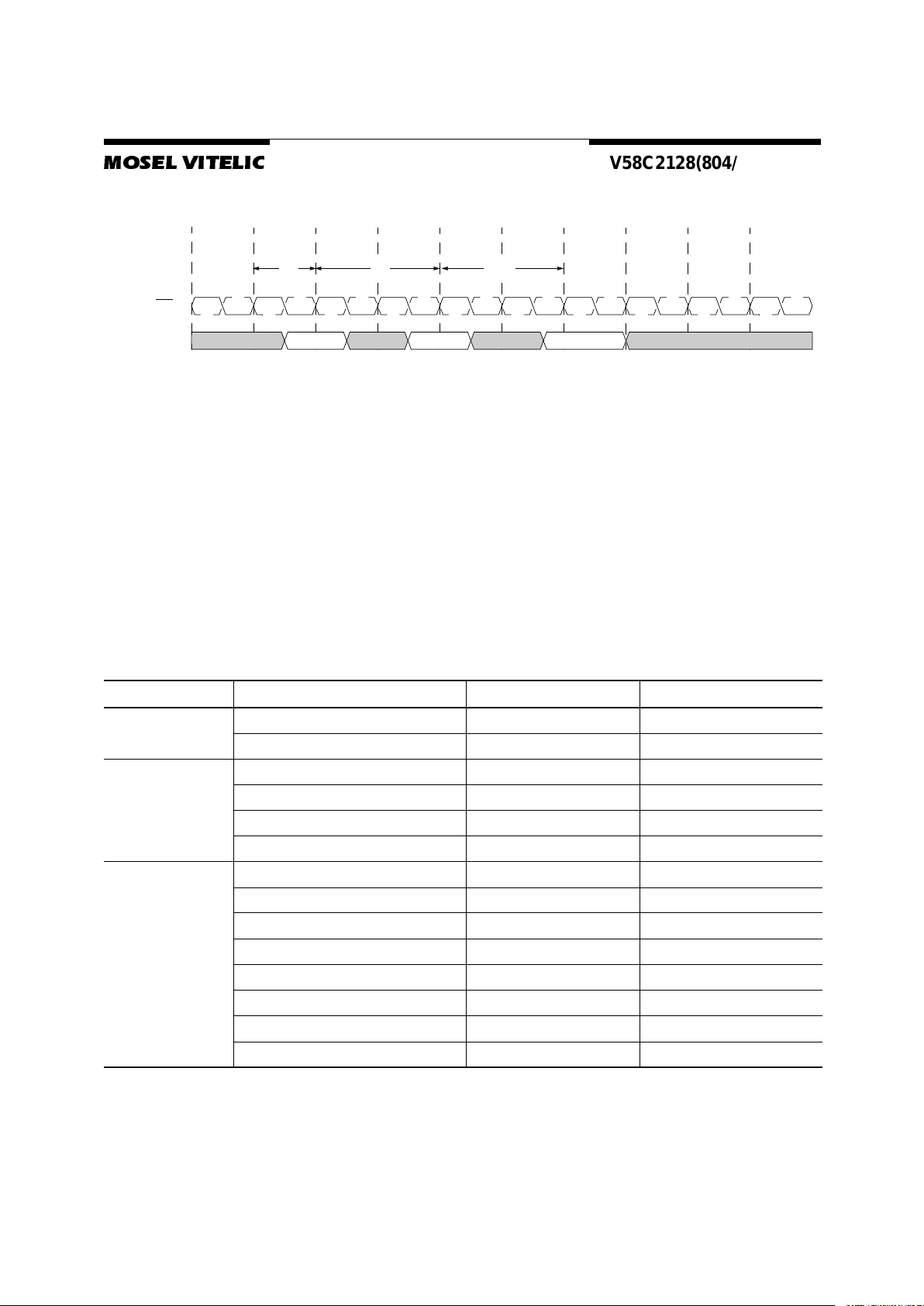

Burst Length and Sequence

Burst Length Starting Length (A2, A1, A0) Sequential Mode Interleave Mode

2

xx0 0, 1 0, 1

xx1 1, 0 1, 0

4

x00 0, 1, 2, 3 0, 1, 2, 3

x01 1, 2, 3, 0 1, 0, 3, 2

x10 2, 3, 0, 1 2, 3, 0, 1

x11 3, 0, 1, 2 3, 2, 1, 0

8

000 0,1, 2, 3, 4, 5, 6, 7 0,1, 2, 3, 4, 5, 6, 7

001 1, 2, 3, 4, 5, 6, 7, 0 1, 0, 3, 2, 5, 4, 7, 6

010 2, 3, 4, 5, 6, 7, 0, 1 2, 3, 0, 1, 6, 7, 4, 5

011 3, 4, 5, 6, 7, 0, 1, 2 3, 2, 1, 0, 7, 6, 5, 4

100 4, 5, 6, 7, 0, 1, 2, 3 4, 5, 6, 7, 0, 1, 2, 3

101 5, 6, 7, 0, 1, 2, 3, 4 5, 4, 7, 6, 1, 0, 3, 2

110 6, 7, 0, 1, 2, 3, 4, 5 6, 7, 4, 5, 2, 3, 0, 1

111 7, 0, 1, 2, 3, 4, 5, 6 7, 6, 5, 4, 3, 2, 1, 0

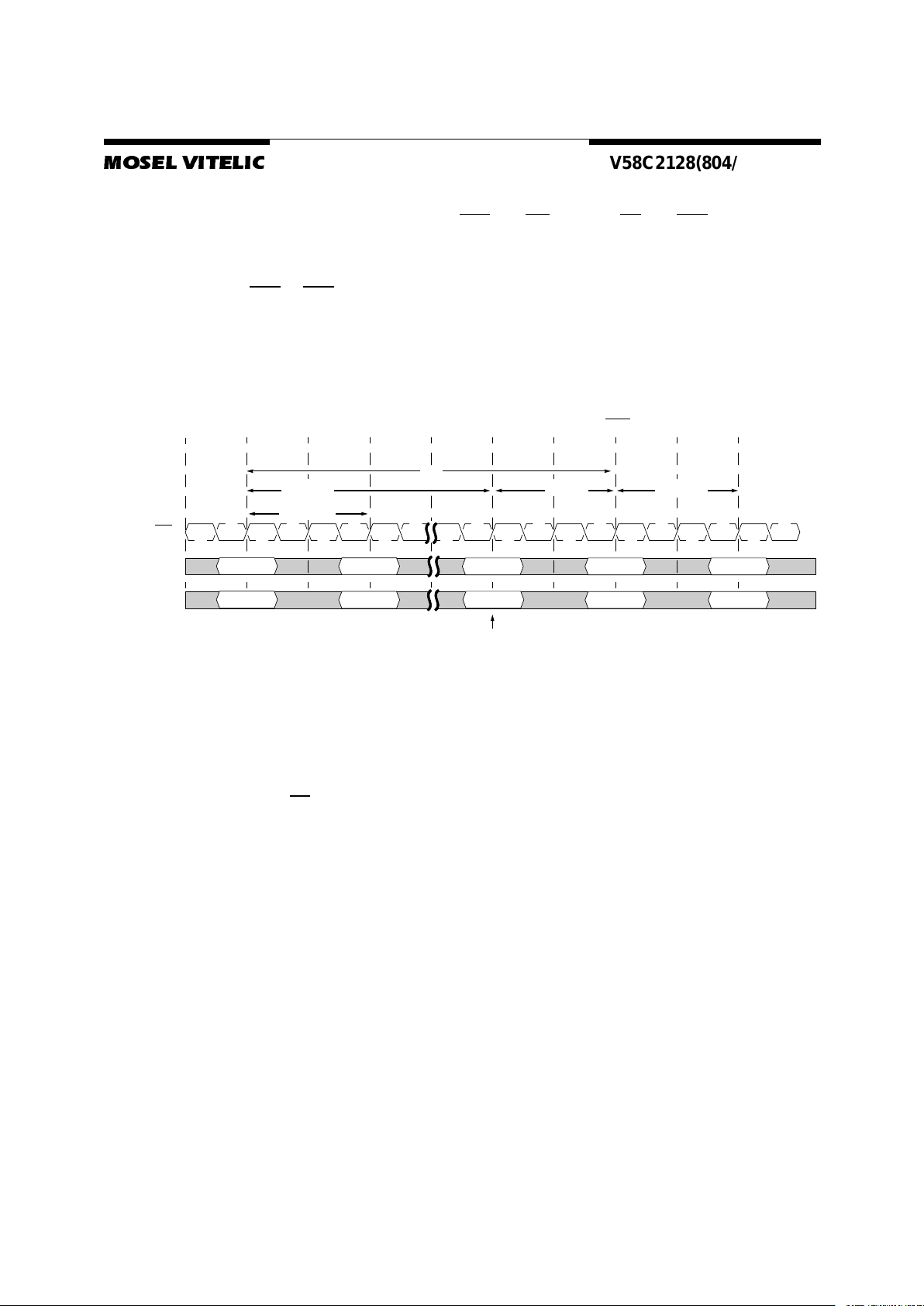

T5T0 T1 T2 T3 T4 T6 T7 T8

t

RP

t

MRD

t

CK

Pre- All

MRS/EMRS

ANY

M

ode Register set (MRS) or Extended Mode Register Set (EMRS) can be issued only when all banks are in the idle state.

CK,

CK

Command

I

f a MRS command is issued to reset the DLL, then an additional 200 clocks must occur prior to issuing any new command

T9

t

o allow time for the DLL to lock onto the clock.

9

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Bank Activate Command

The Bank Activate command is issued by holding CAS and WE high with CS and RAS low at the rising

edge of the clock. The DDR SDRA M ha s four ind epende nt banks, so t wo Bank Select addresses (BA

0

and

BA

1

) are supported. The Bank Activate command must be applied before any Read or Write operation can

be executed. The delay from the B ank Activat e comm and to t he first Read or Write com ma nd mu st m eet or

exceed the minimum RAS

to CAS delay time (t

RCD

min). Once a bank has be en activated, it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval

between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay

time (t

RRD

min).

Bank Activation Timing

Read O p er ati o n

With the DLL enabled, al l devices operat ing at the same frequenc y within a system are ensured t o have

the same timing relationship between DQ and DQS relative to the CK input regardless of device density, process variation, or technology generation.

The data strobe signal (DQS) is driven off chip simultaneously with the output data (DQ) during each read

cycle. The same internal clock phase is used to drive both the output data and data strobe signal off chip to

minimize skew between d ata strobe and o utput data. This internal clock phase is nominally aligned t o the

input differential clock (CK, CK

) by the on-chip DLL. Therefore, when the DLL is enabled and the clock frequency is within the specified range for proper DLL operation, the data strobe (DQS), output data (DQ), and

the system clock (CK) are all nominally aligned.

Since the data strobe and output data are tightly coupled in the system, the data strobe signal may be delayed and used to latch the output data into the receiving device. The tolerance for skew between DQS and

DQ (t

DQSQ

) is tighter than that possible for CK to DQ (tAC) or DQS to CK (t

DQSCK

).

T0 T1 T2 T3 Tn Tn+1 Tn+2 Tn+3 Tn+4 Tn+5

(CAS Latency = 2; Burst Length = Any)

t

RRD

(min)tRP(min)

t

RC

t

RCD

(min)

Begin Precharge Bank A

CK,

CK

B

A/Address

Command

Bank/Col

Read/A

Bank/Row

Activate/A Activate/B

Pre/A

Bank/Row

Activate/A

Bank

Bank/Row

t

RAS

(min)

10

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

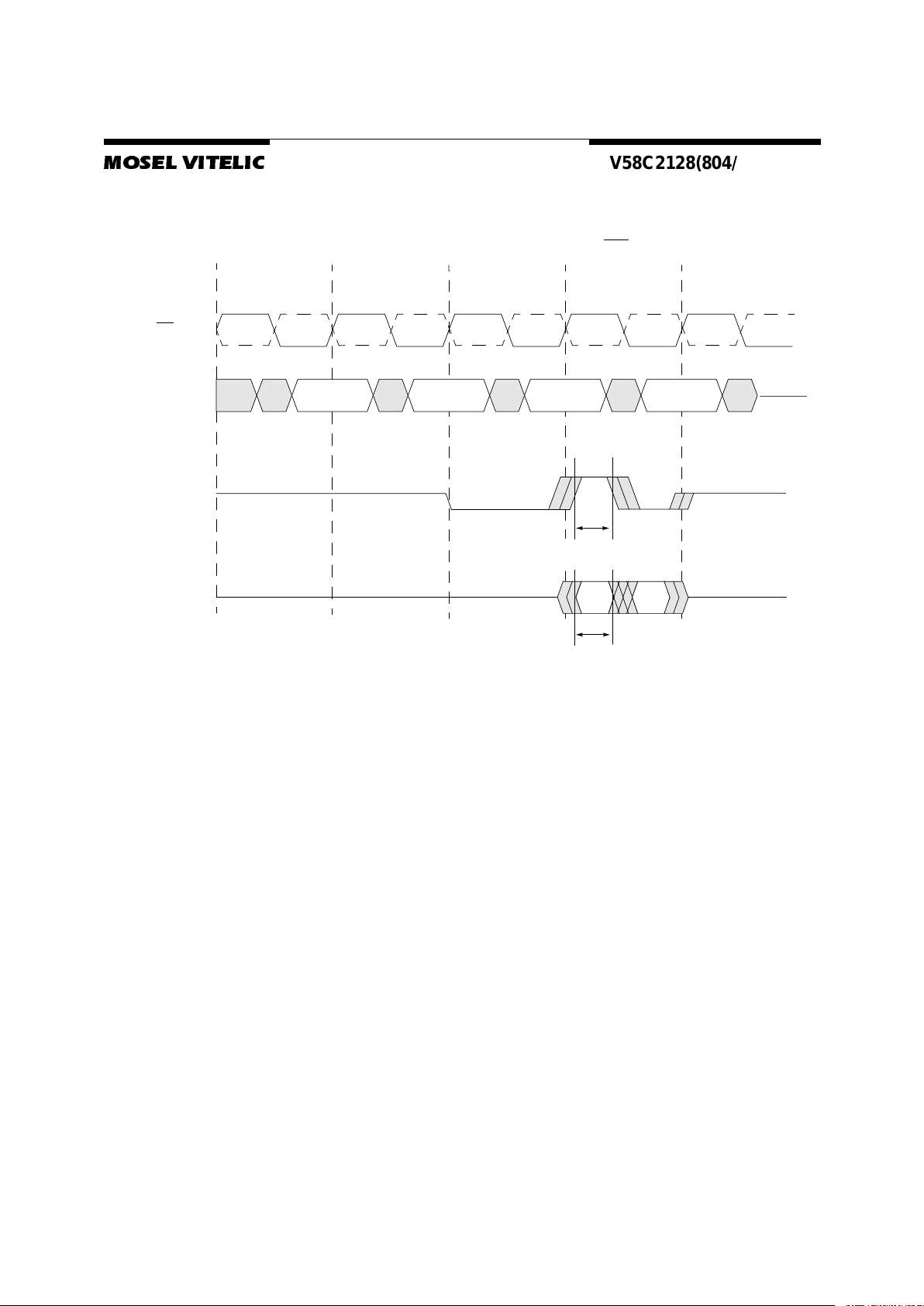

Output Data (DQ) and Data Strobe (DQS) Timing Relative to the Clock (CK)

During Read Cycles

The minimum time during which the output data (DQ) is valid is critical f or the receiving device (i .e., a memory controller device). This al so applies to the data strobe durin g t he read c ycle s ince it is t ightly coupled to

the output data. The minimum data output valid time (t

DV

) and minimum data strobe valid time (t

DQSV

) are derived from the minimum clock high/low time minus a margin for variation in data access and hold time due to

DLL jitter and power supply noise.

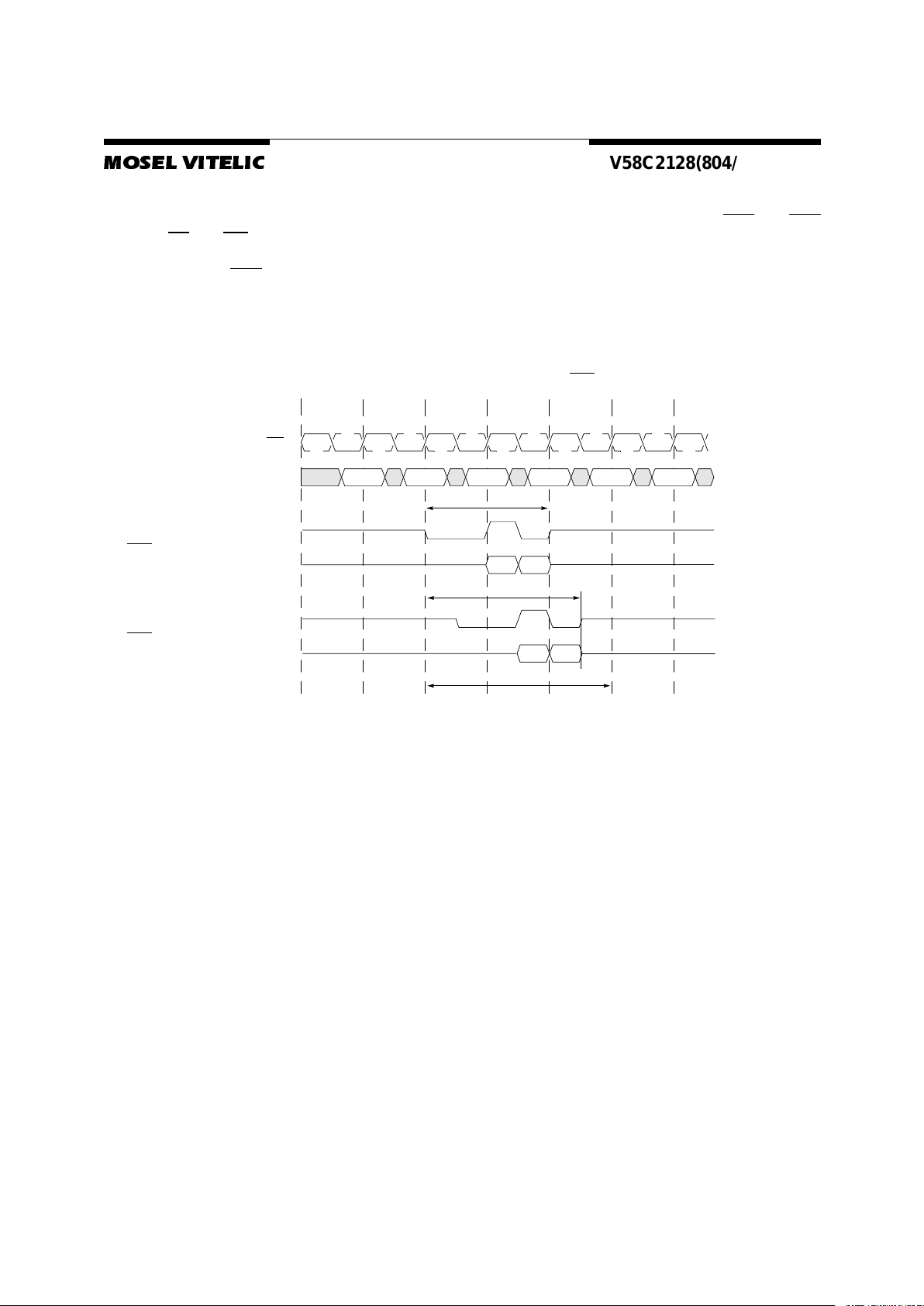

(CAS Latency = 2.5; Burst Length = 4

)

T0 T1 T2 T3 T4

NOP NOPNOP

D

0

CK, CK

C

ommand

DQS

DQ

D

2

t

DQSCK

(max)

t

DQSCK

(min)

D

1

tAC(min)

tAC(max)

D

3

READ NOP

11

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Output Data and Data Strobe Valid Window for DDR Read Cycles

Read Preamble and Po stamble O peration

Prior to a burst of read data and given that the controller is not currently in burst read mode, the data strobe

signal (DQS), must transition from Hi-Z to a valid logic low. The is referred to as the data strobe “read preamble” (t

RPRE

). This transition from Hi-Z to logic low nominally happens one clock cycle prior to the first edge of

valid data.

Once the burst of read data is concluded and given that no subsequent burst read operations are initiated,

the data strobe signal (DQS) transitions from a logic low lev el back to Hi-Z. This is referred to as the data

strobe “read postamble” (t

RPST

). This transition happens nominally one-half clock period after the last edge of

valid data.

Consecutive or “gapless” burst read operations are possible from the same DDR SDRAM device with no

requirement for a data strobe “read” preamble o r postamble in be tween the groups of burst data. The da ta

strobe read preamble is required before the DDR d evice drives the first output data off chip. Similarly, the

data strobe po stambl e i s i nit iated wh en the d evi ce s tops driv ing DQ data at t he t er minati on of read b ur st cy cle s.

D

0

D

1

(CAS Latency = 2; Burst Length = 2)

T0 T1 T2 T3 T4

READ NOP NOPNOP

C

ommand

DQS

DQ

tDV(min)

CK, CK

t

DQSV

(min)

12

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

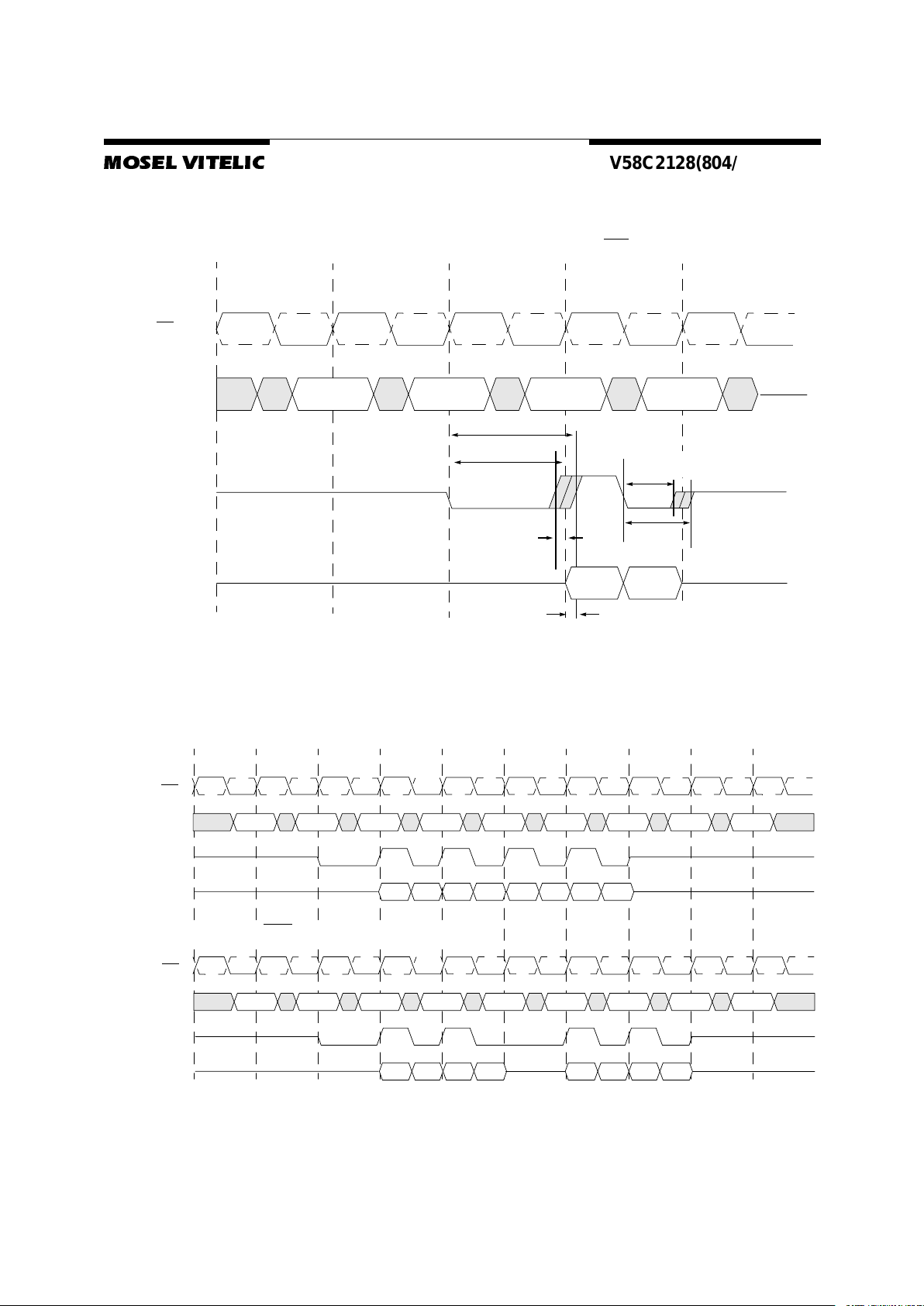

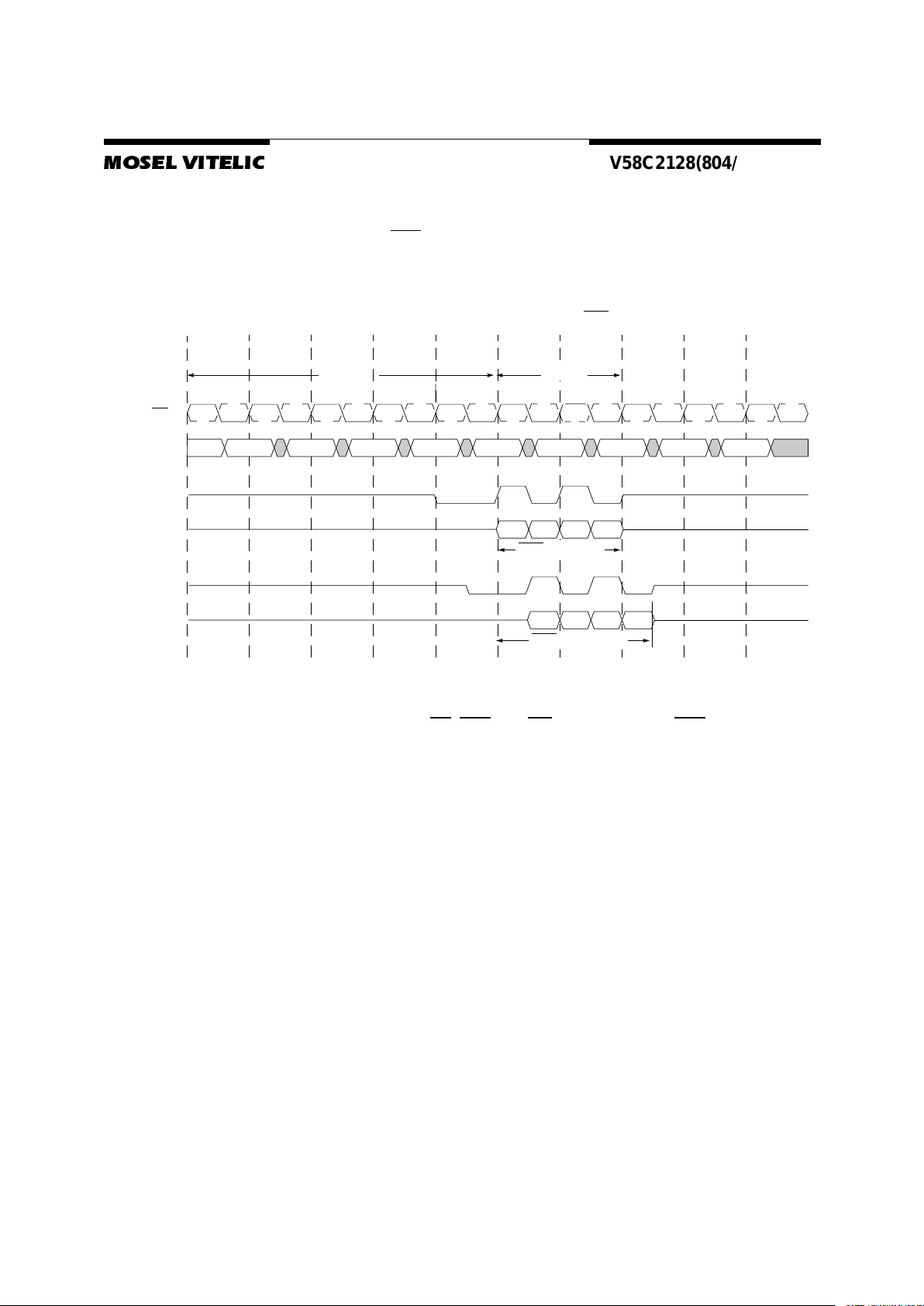

Data Strobe Preamble and Postamble Timings for DDR Read Cycles

Consecutive Burst Read Operation and Effects on the Dat a Strobe Preamble and Posta mble

(CAS Latency = 2; Burst Length = 2)

T0 T1 T2 T3 T4

READ NOP NOPNOP

D

0

D

1

CK, CK

C

ommand

DQS

DQ

t

RPRE

(max)

t

RPST

(min)

t

RPRE

(min)

t

RPST

(max)

t

DQSQ

(max)

t

DQSQ

(min)

NOP Read

B

NOP NOP NOP NOPRead

A

D0AD1

A

NOP

D2

AD3A

Command

DQS

DQ

Burst Read Operation (CAS Latency = 2; Burst Length = 4)

CK, CK

NOP

D0BD1BD2BD3

B

NOP Read

B

NOP NOP NOP NOPRead

A

D0AD1

A

NOP

D2

AD3A

Command

DQS

DQ

Burst Read Operation (CAS Latency = 2; Burst Length = 4)

CK, CK

NOP

D0BD1BD2BD3

B

13

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Auto Pr ech arge Oper ati o n

The Auto Precharge operation can be issu ed by having column address A10 high when a Read or Write

command is issued. If A

10

is low when a Read or Write command is issued, then normal Read or Write burst

operation is executed and the b ank rema ins active at the com pletion of the burst sequence. When the Auto

Precharge command is act ivated, the ac tive bank autom at ically beg ins to p recharge at the earliest possible

moment during the Read or Write cycle once t

RAS

(min) is satisfied.

Read with Auto Precharge

If a Read with Auto Precharge comm and is i nitiated, the DDR SDRAM will enter the precharge operation

N-clock cycles measured from the last data of the burst read cycle where N is equal to the CAS

latency programmed into the device. Once the autoprecharge operation has begun, the bank cannot be reactivated until

the minimum precharge time (t

RP

) has been satisfied.

Read with Autoprecharge Timing

(CAS Latency = 2; Burst Length =

4)

T0 T1 T2 T3 T4 T5 T6 T7 T8

D0D1D2D

3

Begin Autoprecharge

BAACT R w/AP NOPNOP NOP NOP NOP

NOP

CK,

CK

C

ommand

DQS

DQ

t

RAS

(min)

t

P

(min)

Earliest Bank A reactivate

T9

14

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

Read with Autoprecharge Timing as a Function of CAS Latency

T0 T1 T2 T3 T4 T5 T6 T7 T8

NOPRAP NOPNOP NOP NOP BA NOP

CK,

CK

C

ommand

DQS

DQ

t

RAS

(min)

tRP(min)

BA NOP

T9

D0D1D2D

3

DQS

DQ

CAS Latency=2

CAS Latency=2.5

(CAS Latency = 2, 2.5, Burst Length = 4)

D

0D1D2D3

15

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Precharge Timing During Re ad Operati on

For the earliest possible Precharge command without interrupting a Read burst, the Precharge command

may be issued on the rising clock edge which is CAS

latency (CL) clock cycles before the end of the Read

burst. A new Bank Activate (BA) com mand may be issued to the sam e bank after the RAS

precharge time

(t

RP

). A Precharge command can not be issued until t

RAS

(min) is satisfied.

Read with Precharge Timing as a Function of CAS Latency

T0 T1 T2 T3 T4 T5 T6 T7 T8

D0D1D2D

3

NOPRead NOPNOP Pre

A

NOP BA NOP

CK,

CK

C

ommand

DQS

DQ

t

RAS

(min)

tRP(min)

BA NOP

T9

D0D1D2D

3

DQS

DQ

CAS Latency=2

CAS Latency=2.5

(CAS Latency = 2, 2.5, 3; Burst Length = 4)

16

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

Burst Stop Command

The Burst Stop command is valid only during burst read cycles and is initiated by having RAS and CAS

high with CS and WE l ow at the rising edge of the c lock. When th e B urst Stop comm and is i ssue d durin g a

burst Read cycle, both the output data (DQ) and data strobe (DQS) go to a high impedance state after a delay

(L

BST

) equal to the CAS latency programmed into t he device. If the Burst Stop command is issued during a

burst Write cycle, the command will be treated as a NOP command.

Read Terminated by Burst Stop Command Timing

(CAS Latency = 2, 2.5, 3; Burst Length =

4)

T0 T1 T2 T3 T4 T5 T6

BST NOP NOP NOP NOPRead

D

0D1

CK, CK

Command

DQS

DQ

D0D

1

DQS

DQ

C

AS Latency = 2

C

AS Latency = 2.5

L

BST

L

BST

L

BST

17

MOSEL VITELIC

V58C2128(804/404/164)S

V58C2128(804/404/164)S Rev. 1.6 March 2002

Read Interrupted by a Precharge

A Burst Read operation can be interrupted by a precharge of the same bank. The Precharge command to

Output Disable latency is equivalent to the CAS

latency.

Read Interrupted by a Precharge Timing

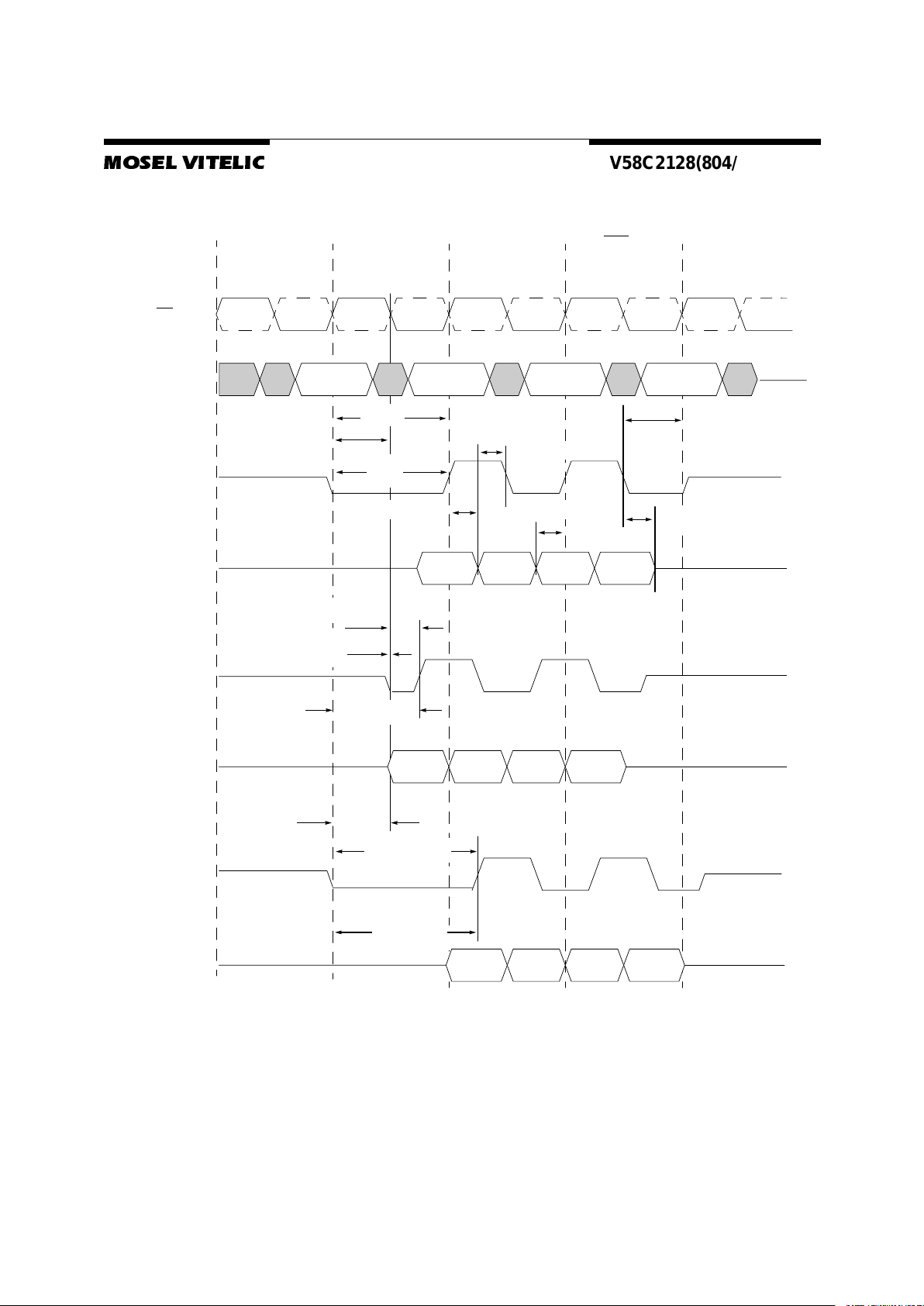

Burst W r it e Op eration

The Burst Write command is issued by having CS, CAS, and WE low while holding RAS high at the rising

edge of the clock. The address inputs determine the starting column address. The memory controller is required to provide an input data strobe (DQS) to the DDR S DRAM to strob e or latch the input data (DQ) and

data mask (DM) into the device. During Write cycles, t he data str obe applied to the DDR S DRAM is required

to be nominally centered within the data (DQ) and data mask (DM) valid windows. The data strobe mu st be

driven high nominally one clock after the write command has been registered. Timing parameters t

DQSS

(min)

and t

DQSS

(max) define the allowable window when the data strobe must be driven high.

Input data for the first Burst Write cycle must be applied one clock cycle after the Write command is

registered into the device (WL=1). The input data valid window is nominally centered around the midpoint of

the data strobe signal. The data window is defined by DQ to DQS s etup time (t

QDQSS

) and DQ to DQS hold

time (t

QDQSH

). All data inputs must be supplied on each rising and falling edge of the data strobe until the burst

length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored.

Write Preamble and Postamb le Operati on

Prior to a burst of write data and given that the controller is not currently in burst write mode, the data strobe

signal (DQS), must transition from Hi-Z to a valid logic low. This is referred to as the data strobe “write preamble”.

This transit ion f rom H i-Z to logic low nominally happens on the falling edge of the c lock af ter the wr ite c ommand has been registered by the device. The preamble is explicitly defined by a setup time (t

WPRES

(min)) and

hold time (t

WPREH

(min)) referenced to the first falling edge of CK after the write command.

T0 T1 T2 T3 T4 T5 T6 T7 T8

D0D1D2D

3

NOPRead NOPNOP Pre

A

NOP BA NOP

CK,

CK

C

ommand

DQS

DQ

t

RAS

(min)

tRP(min)

BA NOP

T9

D0D1D2D

3

DQS

DQ

CAS Latency=2

CAS Latency=2.5

(CAS Latency = 2, 2.5, 3; Burst Length =

8)

18

V58C2128(804/404/164)S Rev. 1.6 March 2002

MOSEL VITELIC

V58C2128(804/404/164)S

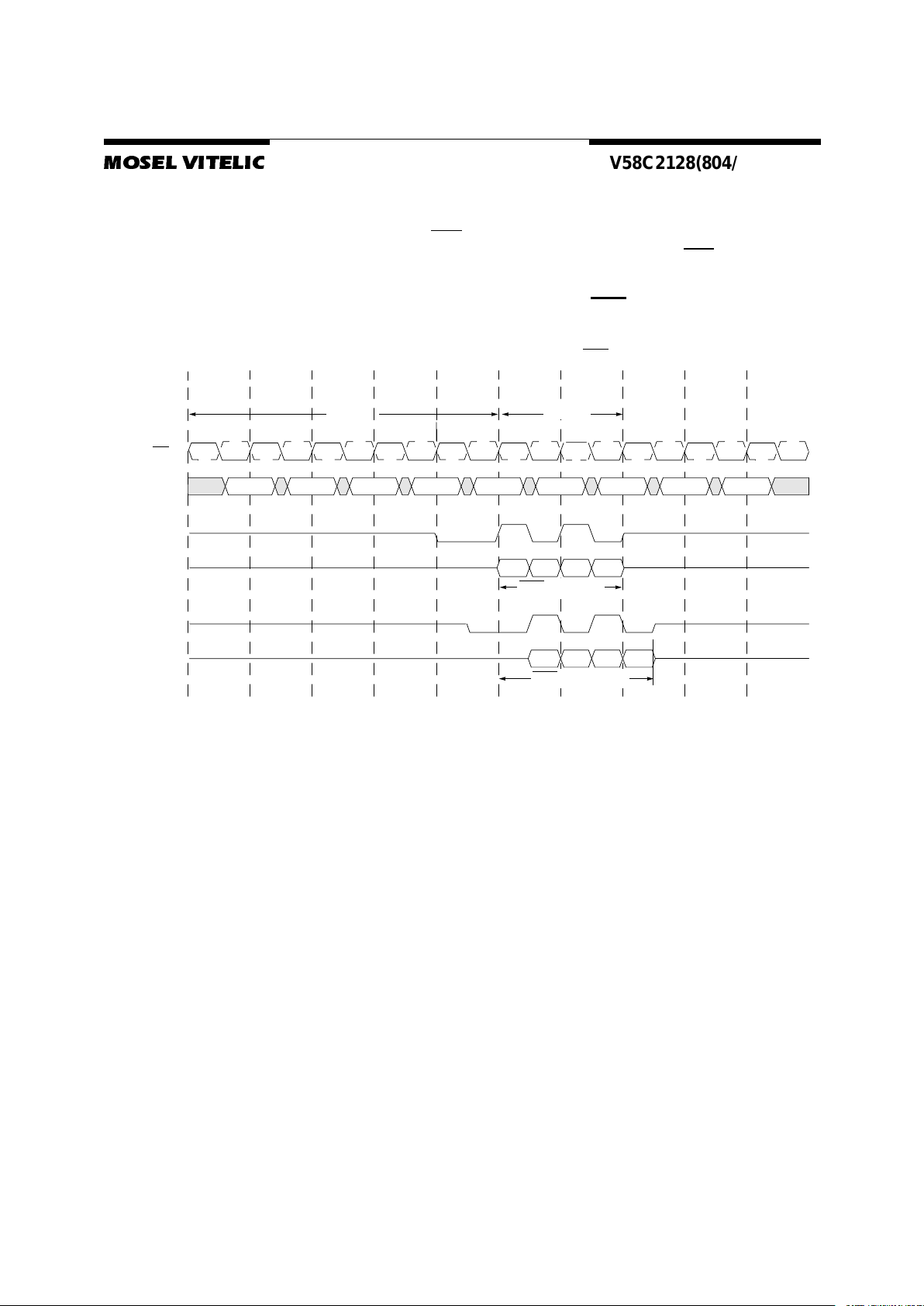

Burst Write Timing

Once the burst of write data is concluded and given that no subsequent burst write operations are initiated,

the data strobe signal (DQS) transitions from a logic low lev el back to Hi-Z. This is referred to as the data

strobe “write postamble”. This transition happens nom inally one-half clock period after the last dat a of the

burst cycle is latched into the device.

(CAS Latency = Any; Burst Length =

4)

T0 T1 T2 T3 T4

WRITE NOP NOPNOP

D

0

D

1

D

2

D

3

CK, CK

C

ommand

D

QS(nom)

DQ(nom)

t

WPRES

t

WPREH

t

DQSS

t

WPST

t

QDQSH

D

0

D

1

D

2

D

3

DQS(min)

DQ(min)

t

DQSS

(min)

D

0

D

1

D

2

D

3

D

QS(max)

DQ(max)

t

WPRES

(min)

t

DQSS

(max)

t

QDQSS

t

QDQSS

t

QDQSH

t

WPREH

(min)

t

WPREH

(max)

t

WPRES

(max)

Loading...

Loading...