Mosel Vitelic V54C365164VDL Datasheet

MOSEL VITELIC

1

V54C365164VD(L)

HIGH PERFORMANCE 225/200/166/143 MHz

3.3 VOLT 4M X 16 SYNCHRONOUS DRAM

4BANKSX1MbitX16

V54C365164VD(L) Rev.1.3 September 2001

PRELIMINARY

45567

System Frequency (f

CK

) 225 MHz 200 MHz 166 MHz 143 MHz

Clock Cycle Time (t

CK3

) 4.5 ns 5 ns 6 ns 7 ns

Clock Access Time (t

AC3

)CASLatency = 3 4.5 ns 5 ns 5.4 ns 5.4 ns

Clock Access Time (t

AC2

)CASLatency = 2 4.5 ns 5 ns 5.5 ns 5.5 ns

Clock Access Time (t

AC1

)CASLatency=1 12ns 12ns 12ns 12ns

Features

■ 4banksx1Mbitx16organization

■ High speed data transfer rat es up to 225 MHz

■ Full Synchronous Dynamic RAM, with all sig nals

referenced to clock rising edg e

■ Single Pulsed RAS

Interface

■ Data Mask for byte Cont rol

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS

Latency:1,2,3

■ Programmable Wrap Sequence: Sequential or

Interleave

■ Programmable Burs t Length:

1, 2, 4, 8 and full page for Sequential Type

1, 2, 4, 8 for Interleave Type

■ Multiple Burst Read with Single Write Operation

■ Automatic and Controlled Precharge Command

■ Random Column Address every CLK ( 1-N Rule)

■ Suspend Mode and Power Down Mode

■ Auto Refresh and Sel f Refresh

■ Refresh Interval: 4096 cycles/64 ms

■ Available in 54 Pin 400 mil TSOP-II

■ LVTTL Interface

■ Single +3.3 V ±0.3 V Power S upply

Description

The V54C365164VD(L) is a four bank Synchronous DRAM organized as 4 banks x 1Mbit x 16. The

V54C365164VD(L) achieves high speed data transfer rates up to 225 MHz by employing a chip arc hitecture that prefetches multiple bits and then

synchronizes the output data to a system clock

All of the control, address, data input and output

circuits are synchronized with the positive edge of

an externally supplied clock.

Operating the four memory banks in an interleaved fashion allows random access operation to

occur at h igher rate than is possible with standard

DRAMs. A sequential and gapless data rate of up to

225 MHz is possible depending on burst length,

CAS

latency and speed grade of the device.

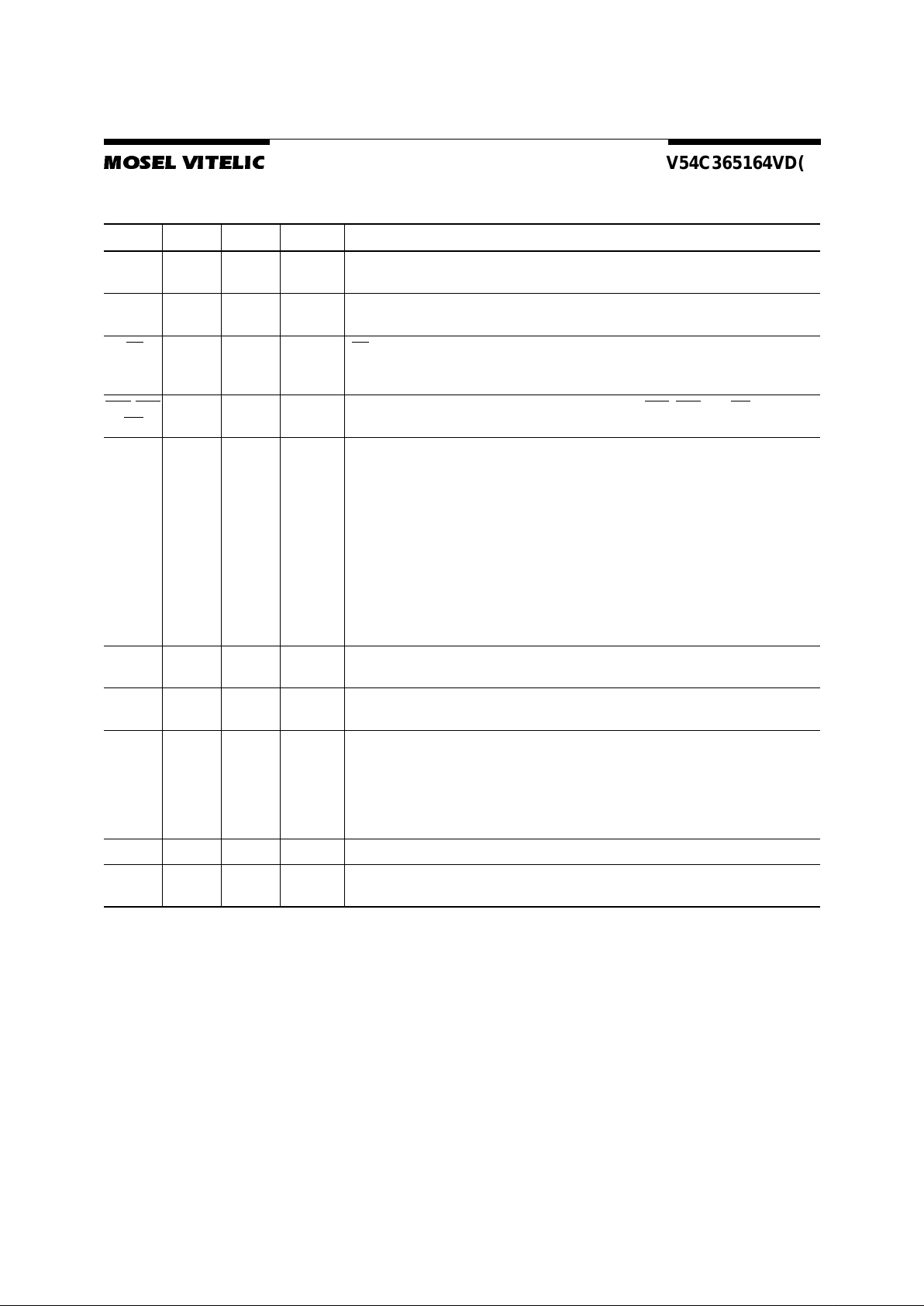

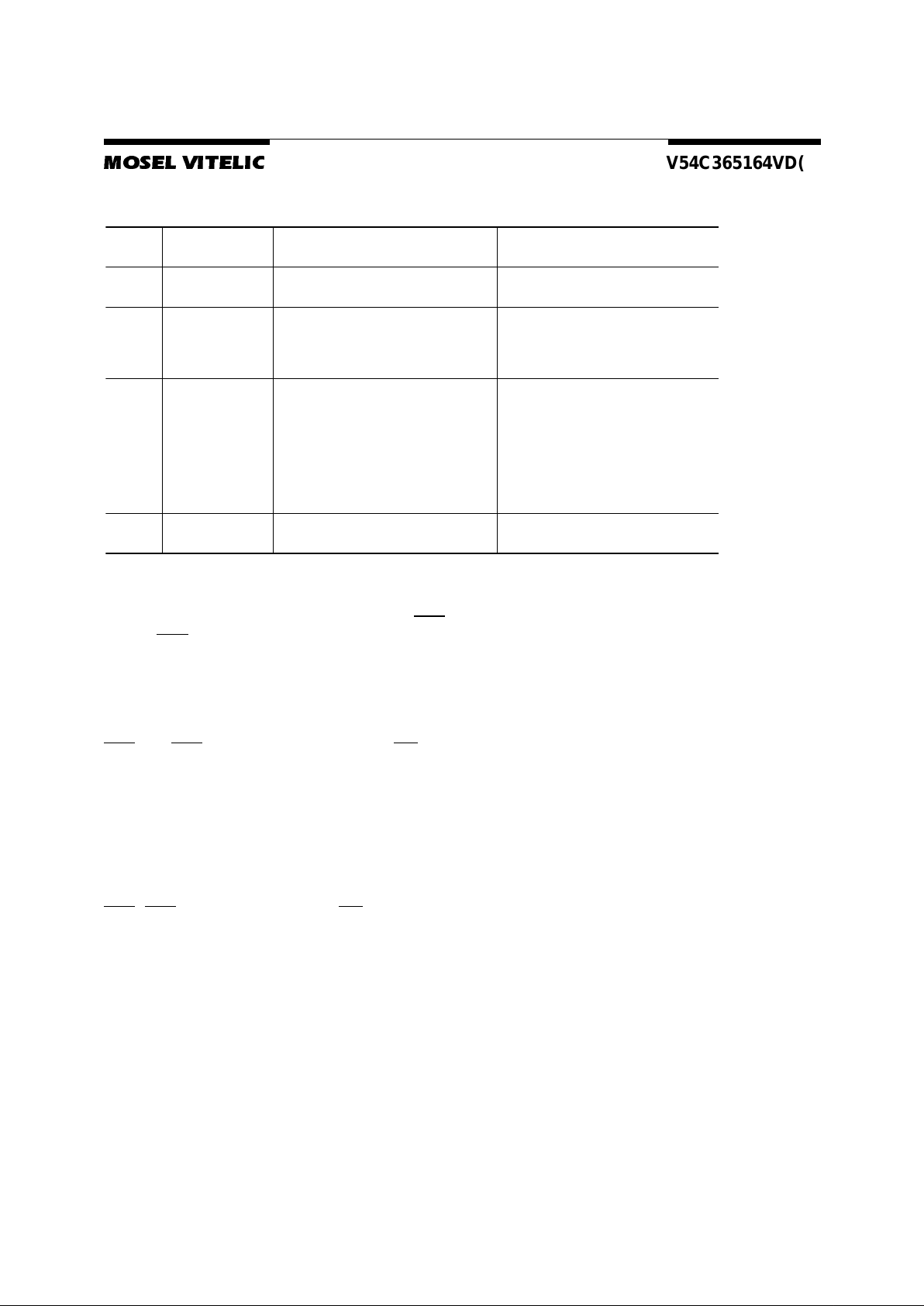

Device Usage Chart

Operating

Temperature

Range

Package Outline Access Time (ns) Power

Temperature

MarkT45567Std.L

0°Cto70°C•••••••Blank

2

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

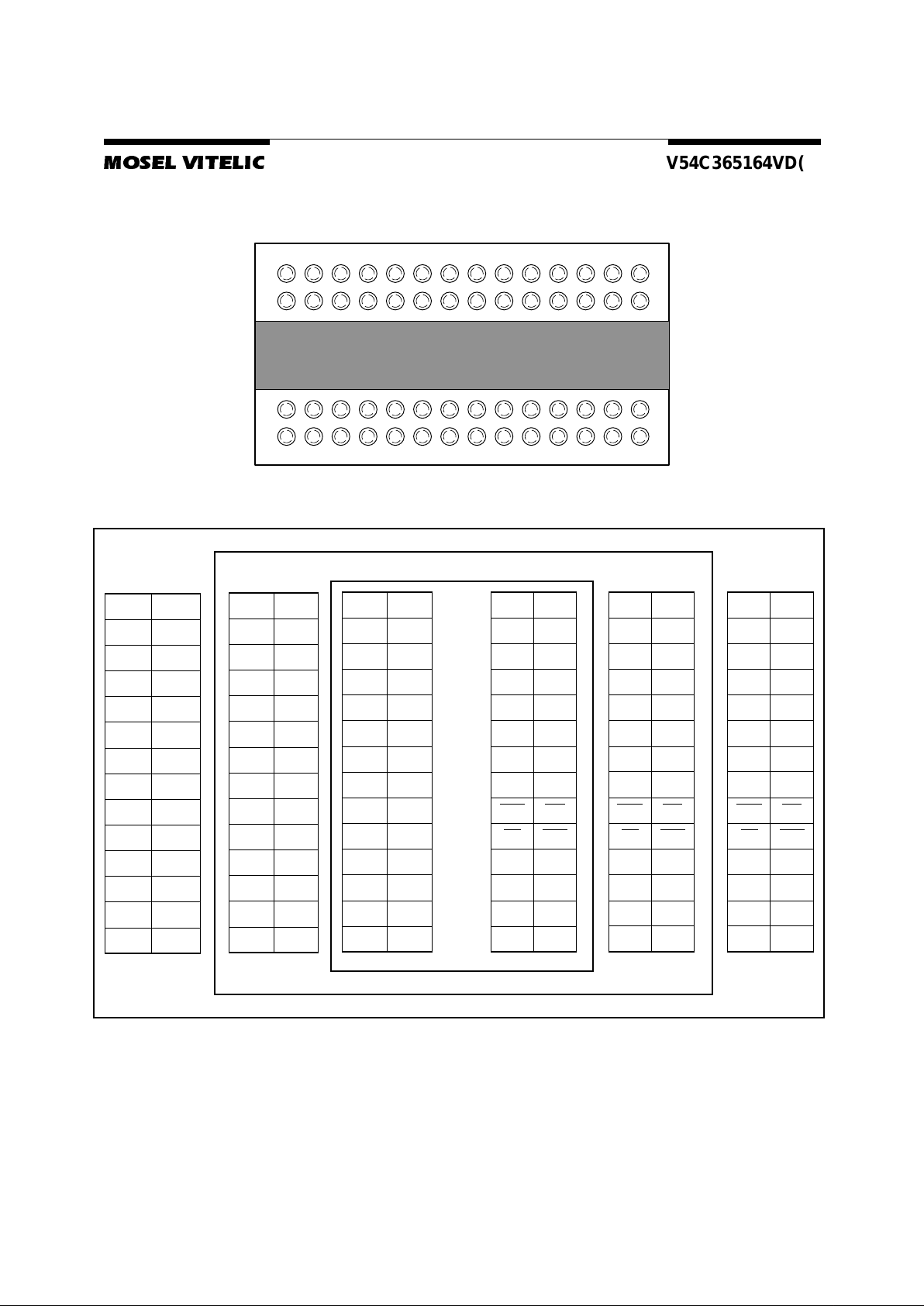

54 Pin Plastic TSOP-II

PIN CONFIGURATION

Top View

Pin Names

V

CC

I/O

1

V

CCQ

I/O

2

I/O

3

V

SSQ

I/O

4

I/O

5

V

CCQ

I/O

6

I/O

7

V

SSQ

I/O

8

V

CC

LDQM

WE

CAS

RAS

CS

BA0

BA1

A

10

A

0

A

1

A

2

A

3

V

CC

V

SS

I/O

16

V

SSQ

I/O

15

I/O

14

V

CCQ

I/O

13

I/O

12

V

SSQ

I/O

11

I/O

10

V

CCQ

I/O

9

V

SS

NC

UDQM

CLK

CKE

NC

A

11

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

365164VA 01

CLK Clock Input

CKE Clock Enable

CS

Chip Select

RAS

Row Ad dress Strobe

CAS

ColumnAddressStrobe

WE

Write Enable

A

0–A11

AddressInputs

BA0, BA1 Bank Select

I/O

1

–I/O

16

Data Input/Output

LDQM, UDQM Data Mask

V

CC

Power(+3.3V)

V

SS

Ground

V

CCQ

Powerfor I/O’s(+3.3V)

V

SSQ

Ground for I/O’s

NC Not connected

Description Pkg. Pin Count

TSOP-II T 54

3

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

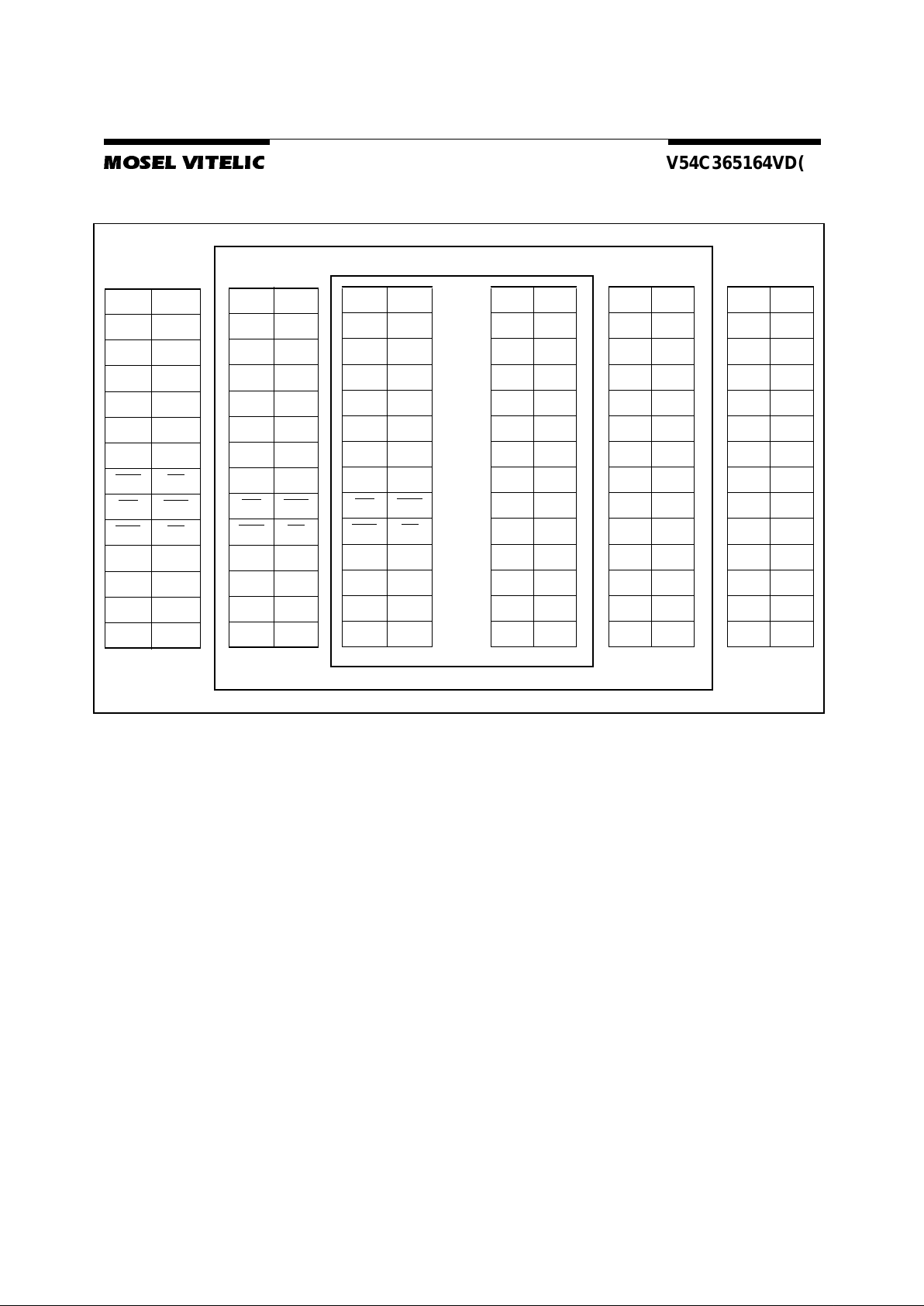

56 Ball Grid Array (or BGA)

WBGA SDRAM (X4/X8/X16) 56 PINS ASSIGNMENT (Top View)

NC VSS

NC VSSQ

VDDQ DQ3

NC NC

NC VSSQ

VDDQ DQ2

VSS NC

DQM NC

CKE CLK

A11 –

A8 A9

A6 A7

A4 A5

NC VSS

DQ7 VSS

NC VSSQ

VDDQ DQ6

DQ5 NC

NC VSSQ

VDDQ DQ4

VSS NC

DQM NC

CKE CLK

A11 –

A8 A9

A6 A7

A4 A5

NC VSS

DQ15 VSS

DQ14 VSSQ

VDDQ DQ13

DQ11 DQ12

DQ10 VSSQ

VDDQ DQ9

VSS DQ8

UDQM NC

CKE CLK

A11 –

A8 A9

A6 A7

A4 A5

NC VSS

VDD NC

VDDQ DQ0

DQ2 DQ1

DQ3 VSSQ

VDDQ DQ4

DQ6 DQ5

DQ7 VSSQ

LDQM VDD

CAS

WE

CS RAS

BA1 BA0

A0 A10

A2 A1

VDD A3

VDD NC

VDDQ DQ0

DQ1 NC

NC VSSQ

VDDQ DQ2

DQ3 NC

NC VSSQ

NC VDD

CAS

WE

CS RAS

BA1 BA0

A0 A10

A2 A1

VDD A3

VDD NC

VDDQ NC

DQ1 NC

NC VSSQ

VDDQ NC

DQ1 NC

NC VSSQ

NC VDD

CAS

WE

CS RAS

BA1 BA0

A0 A10

A2 A1

VDD A3

X4

X8

X16

4

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Bottom View (FROM SOLDER BALL SIDE)

NC VDD

NC VDDQ

NC DQ0

VSSQ NC

NC VDDQ

NC DQ1

VSSQ NC

VDD

NC

WE CAS

RAS CS

BA0 BA1

A10 A0

A1 A2

A3 VDD

NC VDD

DQ0 VDDQ

NC DQ1

VSSQ NC

DQ3 VDDQ

NC DQ3

VSSQ NC

VDD NC

WE

CAS

RAS CS

BA0 BA1

A10 A0

A1 A2

A3 VDD

NC VDD

DQ0 VDDQ

DQ1 DQ2

VSSQ DQ3

DQ4 VDDO

DQ5 DQ6

VSSQ DQ7

VDD LDQM

WE

CAS

RAS CS

BA0 BA1

A10 A0

A1 A2

A3 VDD

VSS DQ15

VSSQ DQ14

DQ13 VDDQ

DQ12 DQ11

VSSQ DQ10

DQ9 VDDQ

DQ8 VSS

NC UDQM

CLK CK E

– A11

A9 A8

A7 A6

A5 A4

VSS NC

VSS DQ7

VSSQ NC

DQ6 VDDQ

NC DQS

VSSQ NC

DQ4 VDDQ

NC VSS

NC DQM

CLK CKS

– A11

A9 A8

A7 A6

A5 A4

VSS NC

VSS NC

VSSQ NC

DQ3 VDDQ

NC NC

VSSQ NC

DQ2 VDDQ

NC VSS

NC DQM

CLK CKE

– A11

A9 A8

A7 A6

A5 A4

VSS NC

X4

X8

X16

MOSEL VITELIC

V54C365164VD(L)

5

V54C365164VD(L) Rev. 1.3 September 2001

Capacitance*

TA=0to70°C, VCC=3.3V± 0.3 V, f = 1 Mhz

*Note:Capacitance is sampled and not 100% tested.

Symbol Parameter

Max. Unit

C

I1

Input Capacitance (A0 to A11) 5 pF

C

I2

Input Capacitance

RAS

,CAS,WE,CS, CLK, CKE, DQM

5pF

C

IO

Output Capacitance (I/O) 6.5 pF

C

CLK

Input Capacitance (CLK) 4 pF

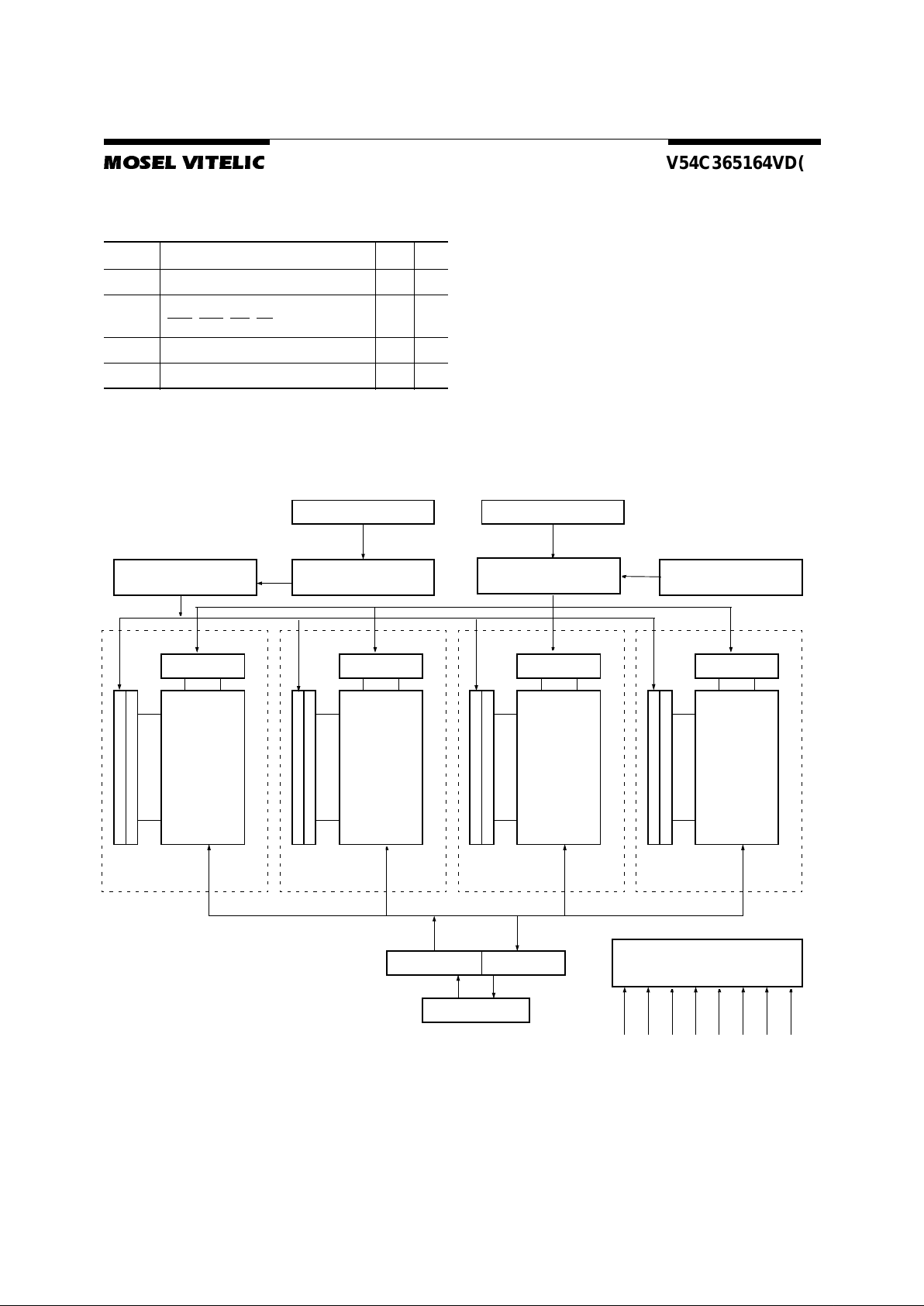

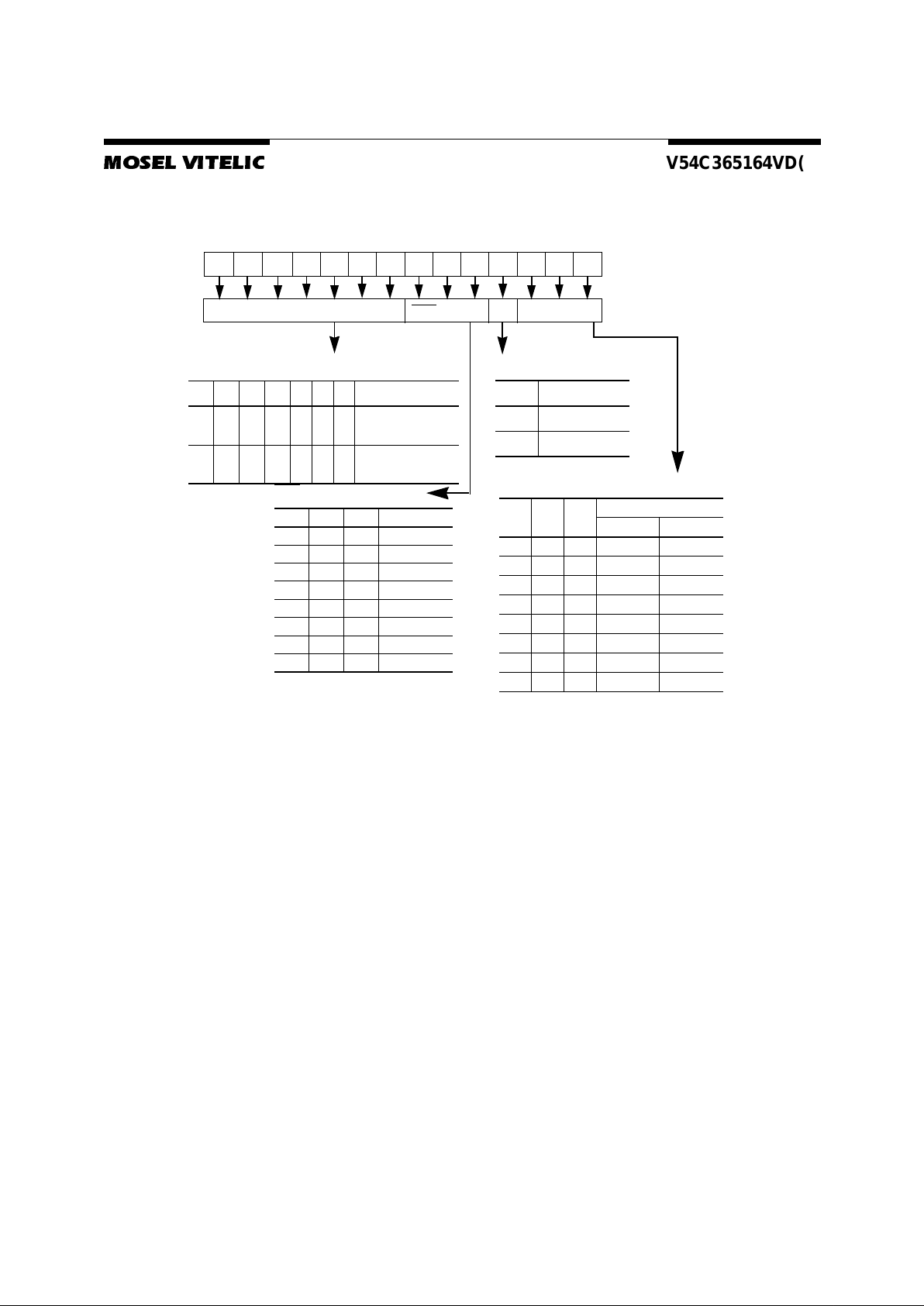

Block Diagram

Row decoder

Memory array

Bank 0

4096 x 256

x16bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memoryarray

Bank 1

4096 x 256

x16bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 2

4096 x 256

x16bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 3

4096 x 256

x16bit

Column decoder

Sense amplifier & I(O) bus

Inputbuffer Output buffer

I/O1-I/O

16

Columnaddress

counter

Columnaddress

buffer

Row address

buffer

RefreshCounter

A0 - A11,BA0, BA1A0 - A7, AP, BA0, BA1

Control logic & timing generator

CLK

CKE

CS

RAS

CAS

WE

LDQM

Row Addresses

Column Addresses

UDQM

6

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Signal Pin Description

Pin Type Signal Polarity Function

CLK Input Pulse Positive

Edge

The system clock input.A ll of the SDRAM inputs are sampled on the rising edge of the

clock.

CKE Input Level ActiveHigh Activatesthe CLK signal when high and deactivates the CLK signal when low, thereby

initiates eitherthePower Down mode,Suspendmode, or the Self Refresh mode.

CS

Input Pulse Active Low CS enables the command decoder when low and disablesthecommand decoderwhen

high. When the command decoder is disabled, new commands are ignored but previous

operations continue.

RAS

,CASWEInput Pulse Active Low When sampled at the positiverising edge of the clock, CAS,RAS,andWEdefinethe

command to be executed by the SDRAM.

A0 - A11 Input Level — During a Bank Activate command cycle, A0-A11defines the row address (RA0-RA11)

when sampledat the rising clock edge.

Duringa Read or Writecommandcycle, A0-An defines the column address (CA0-CAn)

when sampledat the rising clock edge.CAn depends from the SDRAM organization:

4M x 16 SDRAM CA0–CA7 (PageLength = 256 bits)

In additiontothe column address, A10(=AP) is used to invoke autoprecharge operation

at the end of the burst read or write cycle. If A10 is high,autoprecharge is selected and

BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled.

Duringa Prechargecommand cycle,A10(=AP)isusedin conjunction withBA0andBA1

to control which bank(s) to precharge. If A10 is high, all four banks will BA0 and BA1 are

used to define whichbankto precharge.

BA0,

BA1

Input Level — Selects which bank is to be active.

DQx Input

Output

Level — Data Input/Outputpins operate in the same manner as on conventional DRAMs.

DQM

LDQM

UDQM

Input Pulse Active High The Data Input/Output mask places the DQ buffers in a high impedance state when sam-

pledhigh. In Read mode, DQM hasa latencyof two clock cyclesand controls theoutput

buffers likean output enable.In Writemode, DQM has a latencyof zeroand operatesas

a word mask by allowing input data to be written if it is low but blocks the write operation

if DQM is high.

LDQM and UDQM controlsthe lower and upper bytes in a x16 SDRAMs.

VCC, VSS Supply Power and ground for the input buffersand the core logic.

VCCQ

VSSQ

Supply ——Isolated power supply and ground for the output buffers to provide improved noise

immunity.

7

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Operation Definition

All of SDRAM operations are defined by states of control signals CS,RAS,CAS,WE,andDQMatthe

positive edge of the clock. The f oll owing list shows the thruth table for the operation c ommands.

Notes:

1. V = Valid , x = Don’t Care, L = Low Level, H = High Level

2. CKEn signalis input levelwhen commandsare provided,CKEn-1 signal is input level one clock before the commands

are provided.

3. These are stateof bank designated by BS0, BS1 signals.

4. Device state is Full Page Burst operation

5. Power Down Mode can not entry in the burstcycle.When this command assert in the burstmode cycledeviceis clock

suspendmode.

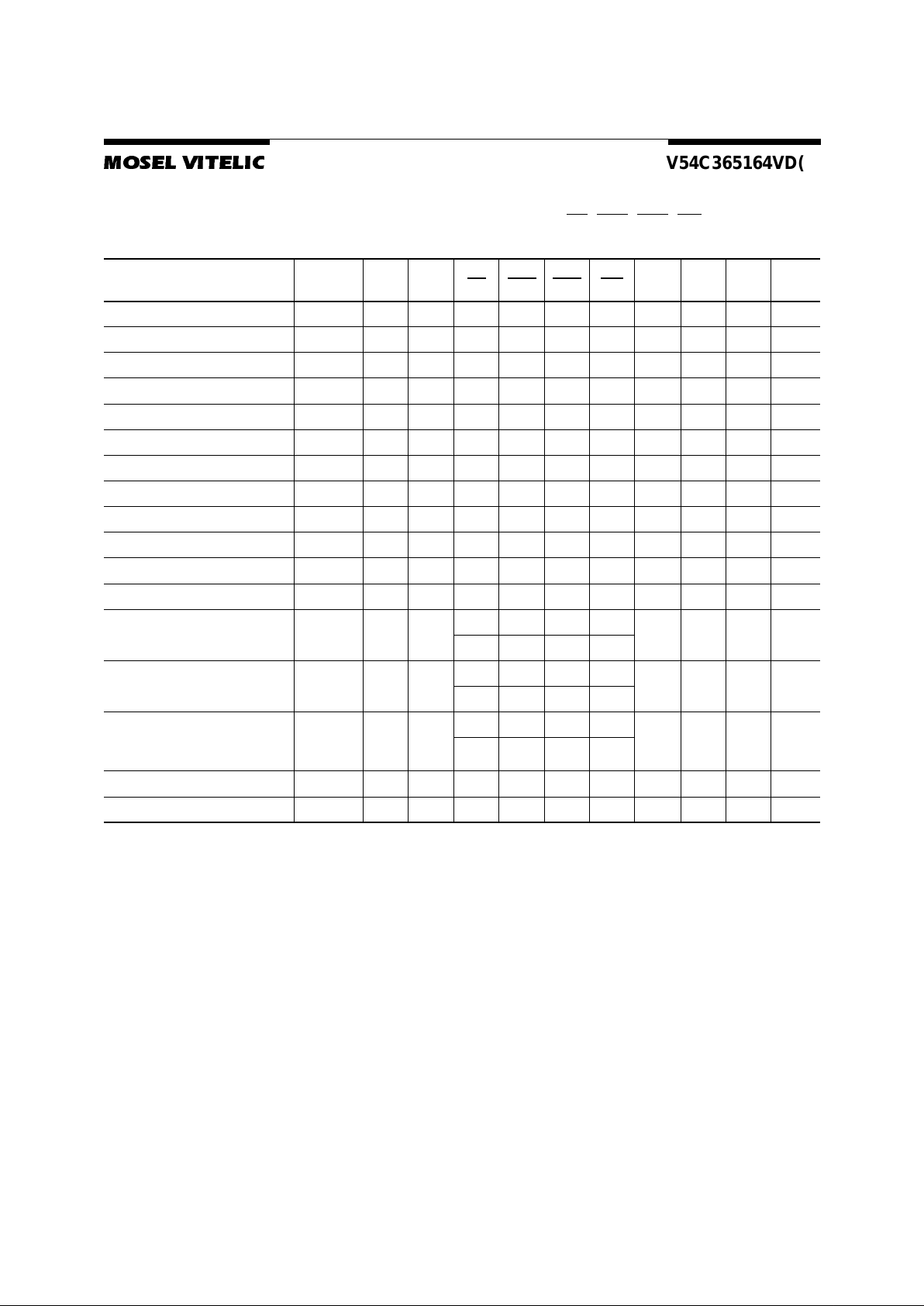

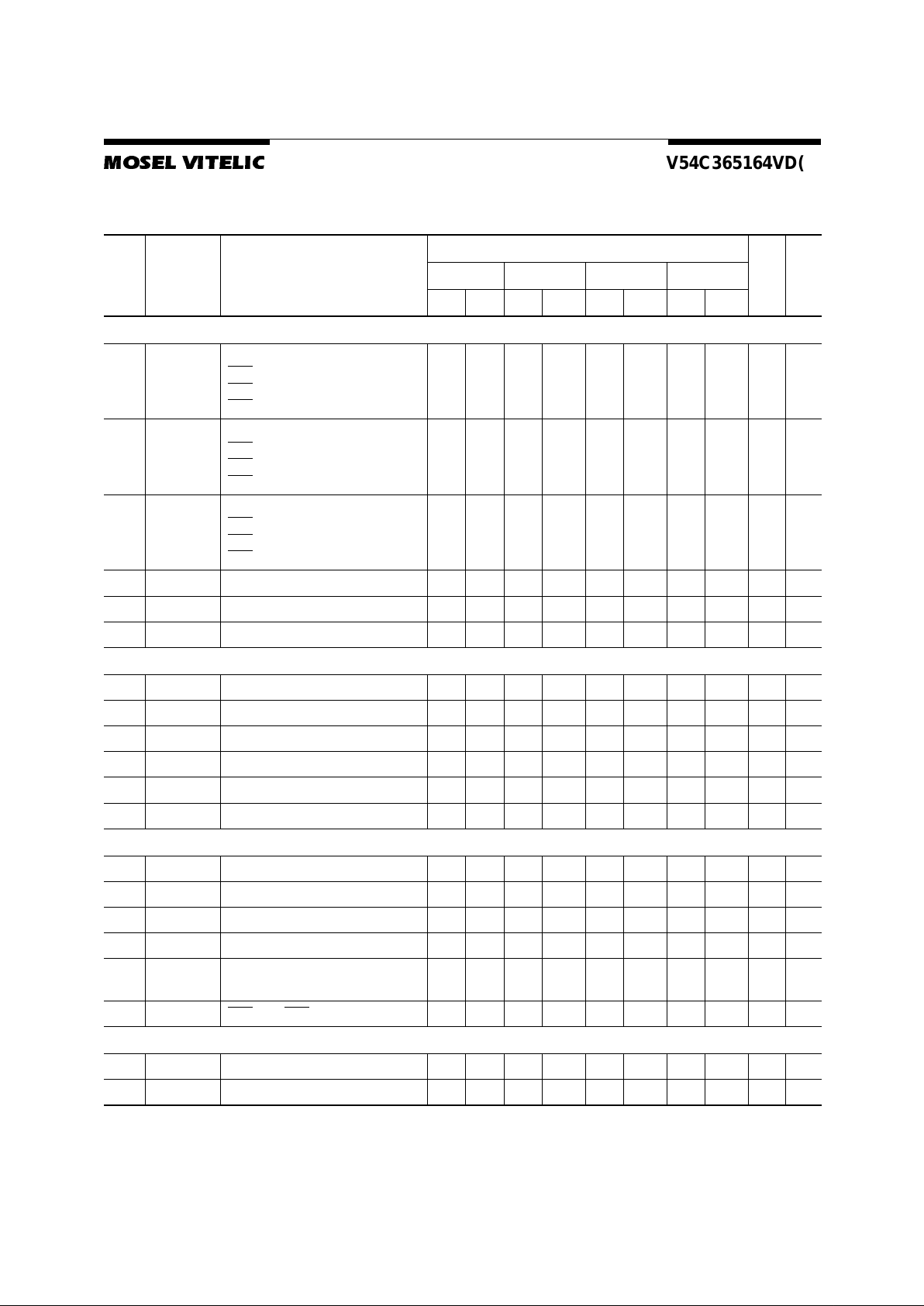

Operation

Device

State

CKE

n-1

CKE

nCSRAS CAS WE DQM

A0-9,

A11 A10

BS0

BS1

Row Activate Idle

3

HXLLHHXVVV

Read Active

3

HXLHLHXVLV

Read w/Autoprecharge Active

3

HXLHLHXVHV

Write Active

3

HXLHLLXVLV

Write with Autoprecharge Active

3

HXLHLLXVHV

RowPrecharge Any HXLLHLXXL V

Precharge All Any H X L L H L X X H X

ModeRegisterSet Idle HXLLLLXVVV

No Operation Any H X L H H H X X X X

Device Deselect Any H X H X X X X X X X

Auto Refresh Idle H H L L L H X X X X

Self Refresh Entry Idle H L L L L H X X X X

Self Refresh Exit Idle

(Self Refr.) L H

HXXX

XXXX

LHHX

Power Down Entry Idle

Active

5

HL

HXXX

XXXX

LHHX

Power Down Exit Any

(Power

Down)

LH

HXXX

XXXX

LHHL

Data Write/OutputEnable Active H X X X X X L X X X

Data Write/OutputDisable Active H X X X X X H X X X

MOSEL VITELIC

V54C365164VD(L)

8

V54C365164VD(L) Rev. 1.3 September 2001

Power On and Initialization

The default power on state of the mode register is

supplier specific and may be undefined. The

following power on and initialization sequ enc e

guarantees the device is preconditioned to each

users specific needs. Like a conventional DRAM,

the Synchronous DRAM must be powered up and

initialized in a predefined manner. During power on,

all VCC an d VCCQ pins must be built up

simultaneously to the specified voltage when the

input signals are held in the “NOP” state. The power

on voltage must not exceed VCC+0.3V on any of

the input pins or VCC supplies. The CLK signal

must be started at the same time. After power on,

an initial pause of 200 µs is required f ollowed by a

precharge of both banks using the pre ch arge

command. To prevent data contention on the DQ

bus du ring power on, it is required that theDQM and

CKE pins be held high during the initial paus e

period. Once all banks have been precharged, the

Mode Register Set Command must be issued to

initialize the Mode Register. A m ini mum of eight

Auto Refresh cycles (CBR) are also required.These

may be done bef ore or after programming the Mode

Register. Failure to fo llow t hes e steps may lead to

unpredictable start-up modes.

Programming the Mode Register

The Mode register designates the operation

mode at the read or write cycle. This register is divided into 4 fields. A Burst Length Field to set the

length of the burst, an Addres s ing Selection bit to

program the column access sequence in a burst cycle (interleaved or sequential), a CAS LatencyField

to set the access time at clock cycle and a Operation mode field to d ifferentiate between normal operation (B urs t read and burst Write) and a special

Burst Read and Single W r ite mode. The mode set

operation must be done bef ore a ny act ivate command after t he initial power up. Any content of the

mode reg ister can be altered by re-executing the

mode set command. All banks must be in precharged state and CKE must be high at least one

clock before the mode set operation. Aft er the mode

register is set, a Standby or NOP com mand is required. Low signals of RAS

,CAS, and WE at the

positive edge of the clock activate the mode set operation. Addres s input data at this timing defines parameters to be set as shown in t he previous table.

Read and Write Operation

When RA S is low and both CAS and WE arehigh

at the positive edge of the clock, a RAS cycle starts.

According to address data, a word line of the selected bank is activated and all of sens e amp lifiers associated t o the wordline are set. A CAS

cycle is

triggered by setting RAS

high a nd CAS low at a

clock timing a fter a necessary delay, t

RCD

,fromthe

RAS

timing. WE is used to define either a read

(WE

=H)orawrite(WE= L) at th is stage.

SDRAM provides a wide variety of fast access

modes. In a single CAS cycle, serial data read or

write operations are allowed at up to a 225 MHz

data rate. The numbers of serial data bits are the

burstlength programmed atthe mode set operation,

i.e., one of 1, 2, 4, 8 and full page. Column addresses are segmented by the burst length and serial

data accesses are done within this boundary. The

first column address to be accessed is supplied at

the CAS t im ing a nd the subs equent addresses are

generated automatically by t he programmed burst

length and its sequence. For example, in a burst

length of 8 with interleave sequence, if the first address is ‘2’, then the rest of the burst sequence is 3,

0, 1, 6 , 7, 4, and 5.

Full page burst operation is only possible using

the sequential burst type and page length is a function of the I/O organisation and column addressing.

Full page burst operation do not self terminate once

the b urst length has been reached. In other words,

unlike burst length of 2, 3 or 8, f ull page burst continues until it is terminated using anot her command.

9

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

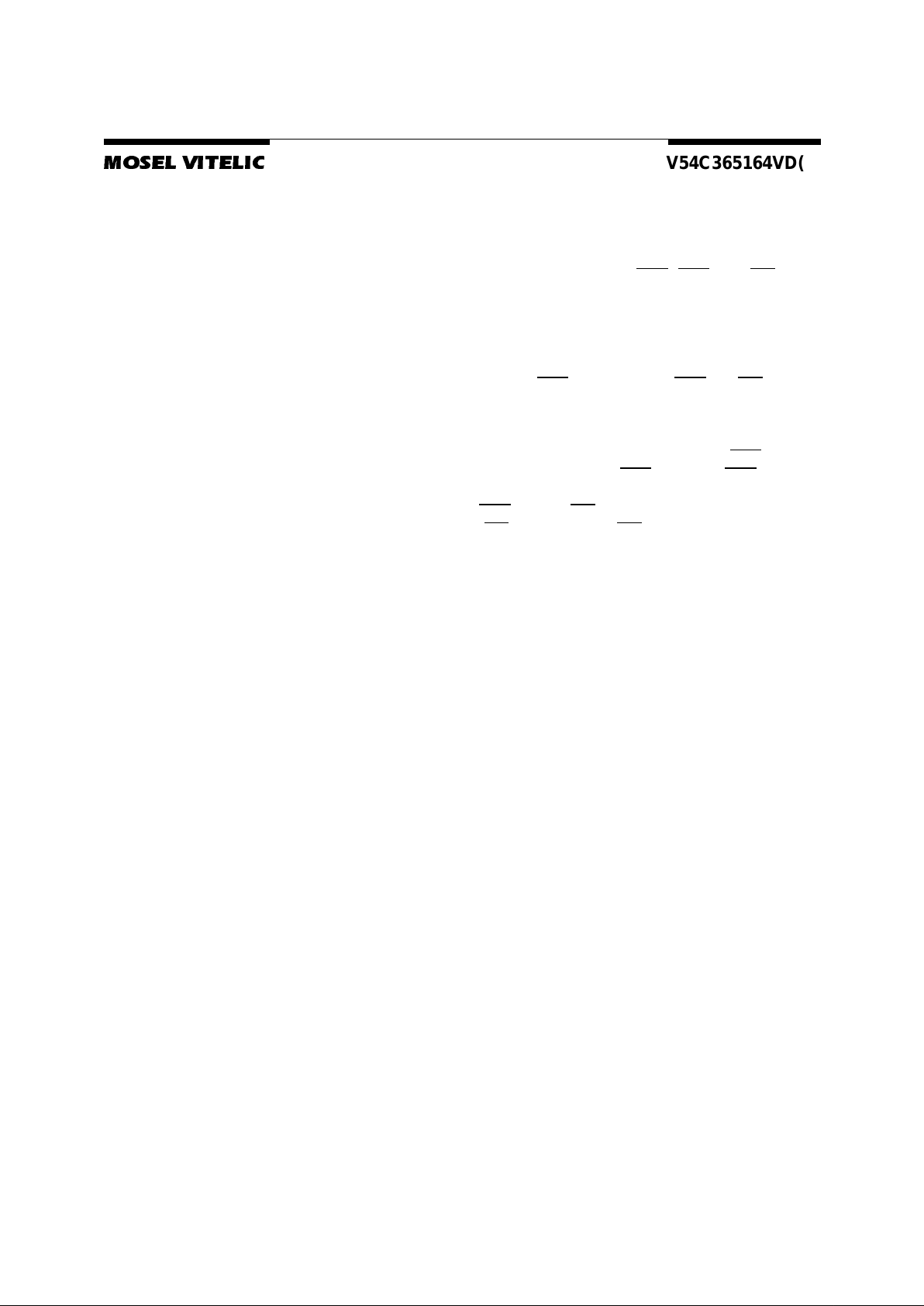

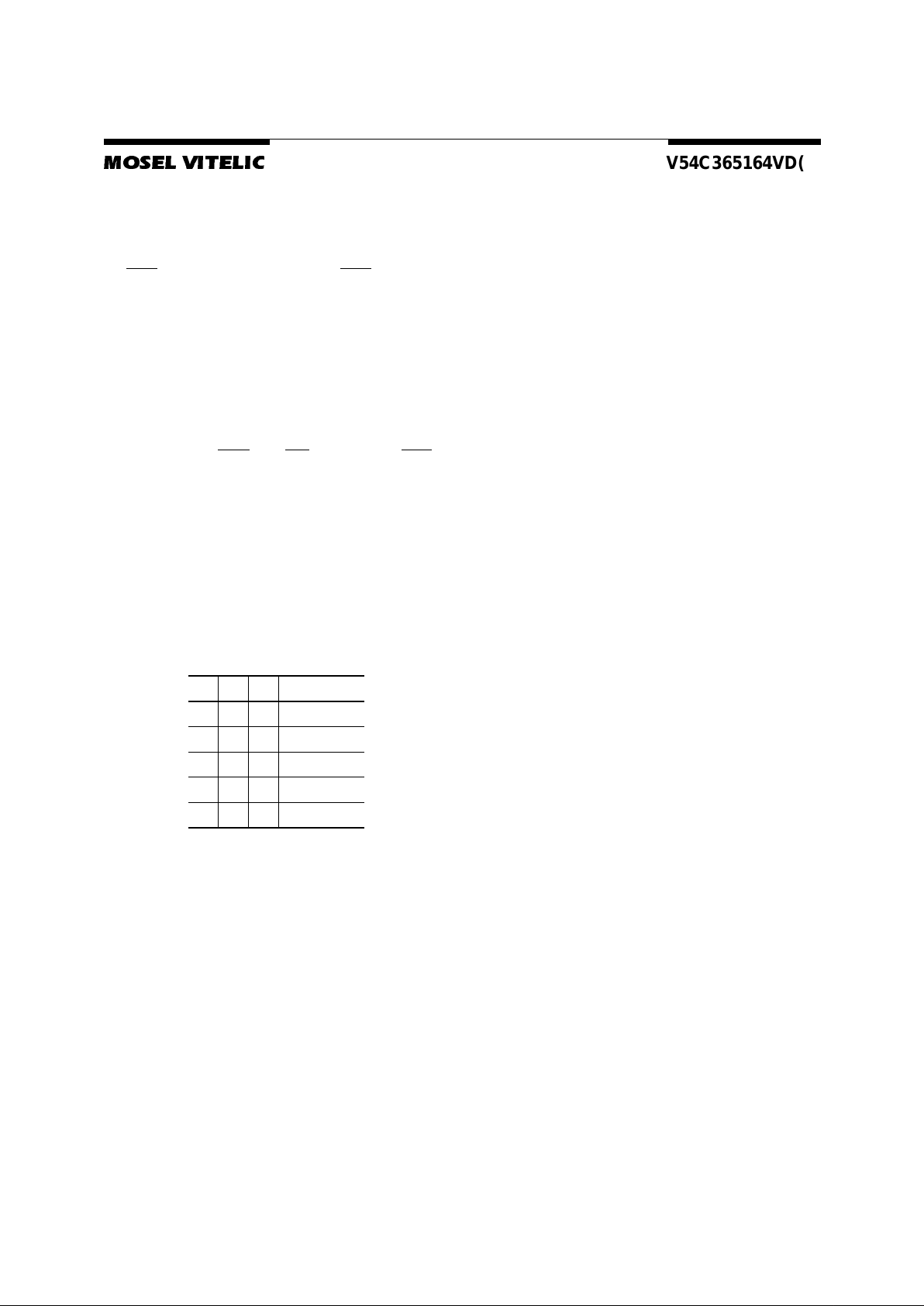

Address Input for Mode Set (Mode Re gister Operation)

A11

A3A4 A2 A1 A0

A10 A9

A8 A7 A6 A5

Address Bus (Ax)

BT Burst LengthCAS Latency

Mode Register

CAS Latency

A6 A5 A4 Latency

0 0 0 Reserve

001 1

010 2

011 3

1 0 0 Reserve

1 0 1 Reserve

1 1 0 Reserve

1 1 1 Reserve

Burst Length

A2 A1 A0

Length

Sequential Interleave

000 1 1

001 2 2

010 4 4

011 8 8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

111FullPageReserve

Burst Type

A3 Type

0 Sequential

1 Interleave

Operation Mode

BA1 BA0 A11 A10 A9 A8 A7 Mode

0000000

Burst Read/Burst

Write

0000100

Burst Read/Single

Write

Operation Mode

BA0BA1

Similar t o the page mode of conventional

DRAM’s, burst read or write accesses on any column address are possible once the RAS cycle latches the sense amplifiers. The maximum t

RAS

or the

refresh interv al time limi ts the number of random c olumn accesses. A new burst acces s can be done

even before the previous burst en ds . The interrupt

operation at every clock cycles is supported. When

the previous burst is interrupted, the remaining addresses are ove rridden by the new address with the

full burst length. An interrupt which ac c ompanies

with an operation change f rom a read t o a write is

possible by exploiting DQM to avoid bus contention.

When two or more banks are activated

sequentially, interleaved bank read or write

operations are possible. With the programmed burst

length, alternate access and precharge operations

on two or more banks can realize fast serial data

access modes among many different pages. Onc e

two or more banks are activated, column to c olumn

interleave operation can be done between different

pages.

MOSEL VITELIC

V54C365164VD(L)

10

V54C365164VD(L) Rev. 1.3 September 2001

Burst Length and Sequence:

Refresh Mode

SDRAM has t w o refresh modes, Auto R ef res h

and S elf Refresh. Auto Ref res h is similarto the CAS

-before-RAS ref res h of conventional DRAMs. All of

banks must be precharged before applying any refresh mode. An on-chip address coun ter increments

the word and the bankaddresses and no bank information is required for bot h refresh modes.

The chi p enters the Auto Refresh mode, wh en

RAS

and CAS are held low and CKE and WE are

held high at a clock timing. The mode restores word

line after the refresh and no ext ernal precharge

command is necessary. A minimum tRC time is required between two automatic refreshes in a burst

refresh mode. The same rule applies to any access

command after the automatic refresh operation.

The chip has an on-chip timer and the Self Refresh mode is available. It enters the mode when

RAS

,CAS, and CK E are low and WE is high at a

clock timing. All of external control signals including

the clock are disabled. Returning CKE to high enables the clock and initiates the refresh exit operation. After the exit command, at least one t

RC

delay

is required prior to any access command.

DQM Function

DQM has two functions for data I/O read and

write operations. During reads, w hen it turns to

“high” at a clock timing, data outputs are disabled

and become high impedance after two clock delay

(DQM Data Disable Latency t

DQZ

). It also provides

a data mask function for writes. When DQM is activated, the write operation at the nex t clock is prohibited (DQM Write Mask Latency t

DQW

= zero clocks).

Suspend Mode

During normalaccess mode, CKEis held high enabling the clock. When CKE is low, it freezes the internal clock and exte nds data read and wri te

operations. One clock delay is required for m ode

entry and ex it (Clock Suspend Latency t

CSL

).

Power Down

In order to reduce st andby power consumption, a

power down mode is available. All banks must be

precharged and the necessary Precharge delay

(trp) must occur before the S DRAM can enter the

Power Down mode. Once the Power Down mode is

initiated by holdi ng CKE low, all of the receiver circuits except CLK and CKE are gated off. The Power

Down mode does not perform any refresh operations, therefore the device can’t rem ain in Power

Down mode longer than the Refresh period (t ref) of

the device. Exit from this mode is performed by taking CKE “high”. One c lock delay is required for

mode entry and exit.

Auto Precharge

Two methods are available to precharge

SDRAMs. In an automatic precharge mode, the

CAS timing accepts one extra address, CA10, to

determine whether the chip restores or not after the

Burst

Length

Starting Address

(A2 A1 A0)

Sequential Burst Addressing

(decimal)

Interleave Bur st Addressing

(decimal)

2 xx0

xx1

0, 1

1, 0

0, 1

1, 0

4x00

x01

x10

x11

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

8 000

001

010

011

100

101

110

111

0 1 2 3 4 5 6 7

1 2 3 4 5 6 7 0

2 3 4 5 6 7 0 1

3 4 5 6 7 0 1 2

4 5 6 7 0 1 2 3

5 6 7 0 1 2 3 4

6 7 0 1 2 3 4 5

7 0 1 2 3 4 5 6

0 1 2 3 4 5 6 7

1 0 3 2 5 4 7 6

2 3 0 1 6 7 4 5

3 2 1 0 7 6 5 4

4 5 6 7 0 1 2 3

5 4 7 6 1 0 3 2

6 7 4 5 2 3 0 1

7 6 5 4 3 2 1 0

Full

Page

nnn Cn, Cn+1, Cn+2,..... not supported

11

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

operation. IfCA10 is high when a Read Command is

issued, the Read with Auto-Precharge function is

initiated. The SDRAM automatically enters the precharge operation one clock before the last data out

for CAS

latencies 2, two clocks for CAS latencies 3

and three clocks for CAS latencies 4. If CAS10 is

high when a Write Command is issued, the Write

with Auto-Prechar ge function is initiated. The

SDRAM automatically enters the pre charge operation a tim e delay equal to t

WR

(Write recovery time)

after the last data in.

Precharge Command

There is also a s eparate precharge command

available. When RAS

and WE are low and CAS is

high at a clock timing, it triggers the precharge operation. Three address bits, BA0, BA1 and A10 are

used to define banks as shown in the following list.

The precharge command can be imposed one clock

before the last data ou t for CAS late ncy = 2, two

clocks before the last data out for CAS latency = 3

and three clocks before the last data out for CAS latency= 4. Writes require a time delay twr from the

last data out to appl y the precharge command.

Bank Selection by Address Bits:

Burst Termination

Once a burst read or write operation has been initiated, there are several methods in which to terminate the burst operation prematurely. These

methods include using another Read or Write Command to interrupt an existing burst operation, use a

Precharge Command to interrupt a burst cycle and

close the active bank , or using the Burst Stop Command to terminate the existing burst operation but

leave the bank open for future Read or Write Commands to t he same page of the active bank. When

interrupting a burst with another Read or Write Command care must be taken to avoid I/ O co ntention.

The Burst Stop Command, however, has the fewest

restrictions making it the easiest method to use

when terminating a burst operation before it ha s

been completed. If a Burst Stop command is iss ued

during a burst write operation, then any residual data

from the burst write cycle will be ignored. Data that

is presented on the I/O pins before the Burst Stop

Command is registered will be written to the

memory.

A10 BA0 BA1

000 Bank0

001 Bank1

010 Bank2

011 Bank3

1 X X all Banks

12

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Absolute Maximum Ratings*

Operating temperature range ..................0 to 70 °C

Storage temperature range ............... -55 to 150 °C

Input/output volt age ..................-0.3 to (V

CC

+0.3)V

Power supply voltage ..........................-0.3 to 4.6 V

Power dissipation .............................................1 W

Data out current (short circuit)......................50 mA

*Note: Stresses above thoselistedunder “Absolute Maximum

Ratings” may cause permanent damage of the device.

Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

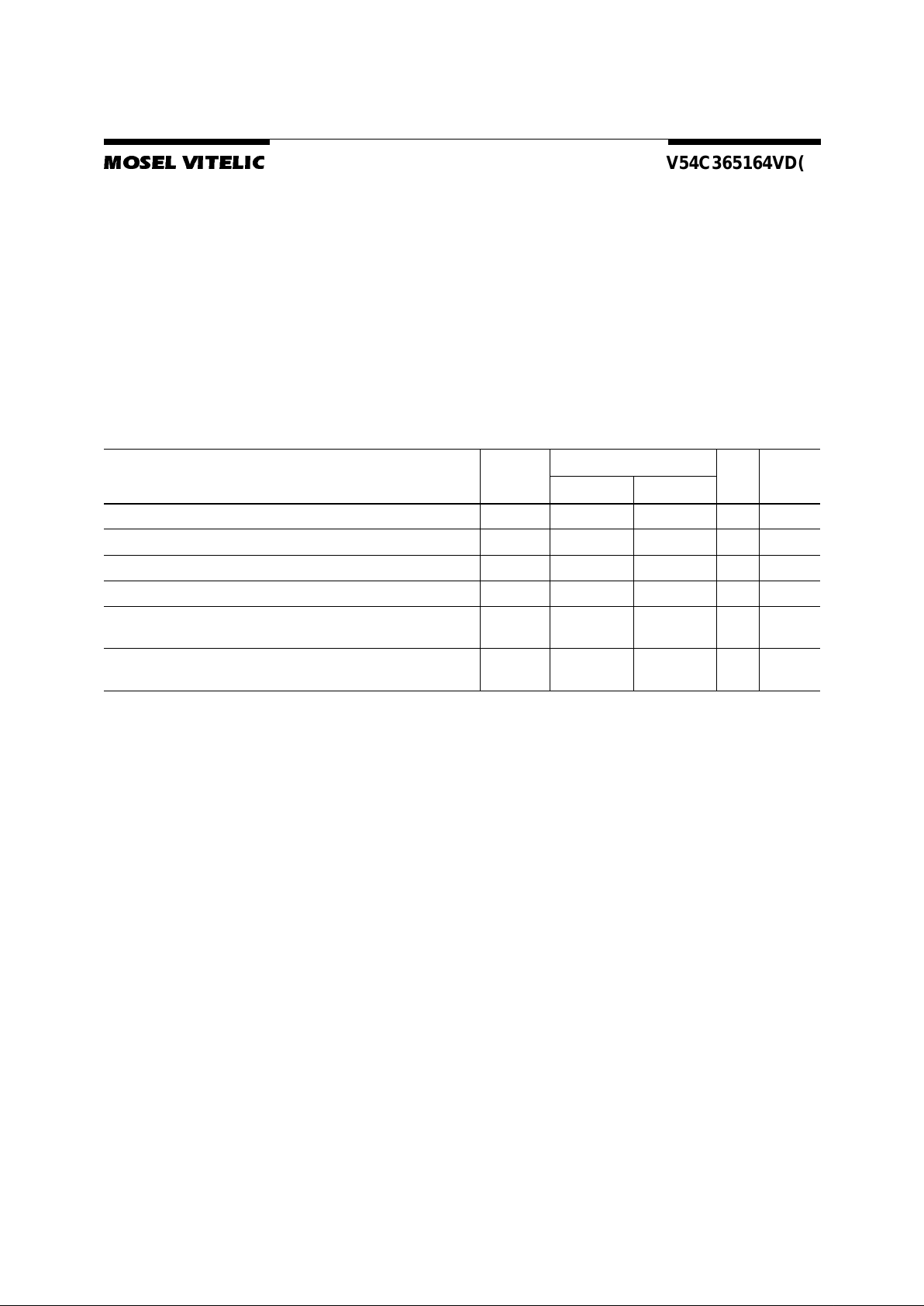

Recommended O peration and Cha racteristics for LV-TTL

TA=0to70°C; VSS=0V;VCC,V

CCQ

=3.3V± 0.3 V

Note:

1. All voltages are referenced to V

SS

.

2. V

IH

may overshootto VCC+ 2.0 V for pulse width of < 4ns with3.3V.VILmay undershoot to -2.0 V for pulse width < 4.0 ns with

3.3V.Pulsewidthmeasured at 50% points with amplitudemeasured peak to DC reference.

Parameter Symbol

Limit Values

Unit Notesmin. max.

Inputhighvoltage V

IH

2.0 Vcc+0.3 V 1, 2

Input low voltage V

IL

– 0.3 0.8 V 1, 2

Output highvoltage (I

OUT

= – 2.0 mA) V

OH

2.4 – V

Output low voltage(I

OUT

=2.0mA) V

OL

– 0.4 V

Input leakagecurrent, any input

(0 V < V

IN

< 3.6 V, all other inputs = 0 V)

I

I(L)

– 55µA

Output leakage current

(DQ is disabled,0 V < V

OUT<VCC

)

I

O(L)

– 55µA

13

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

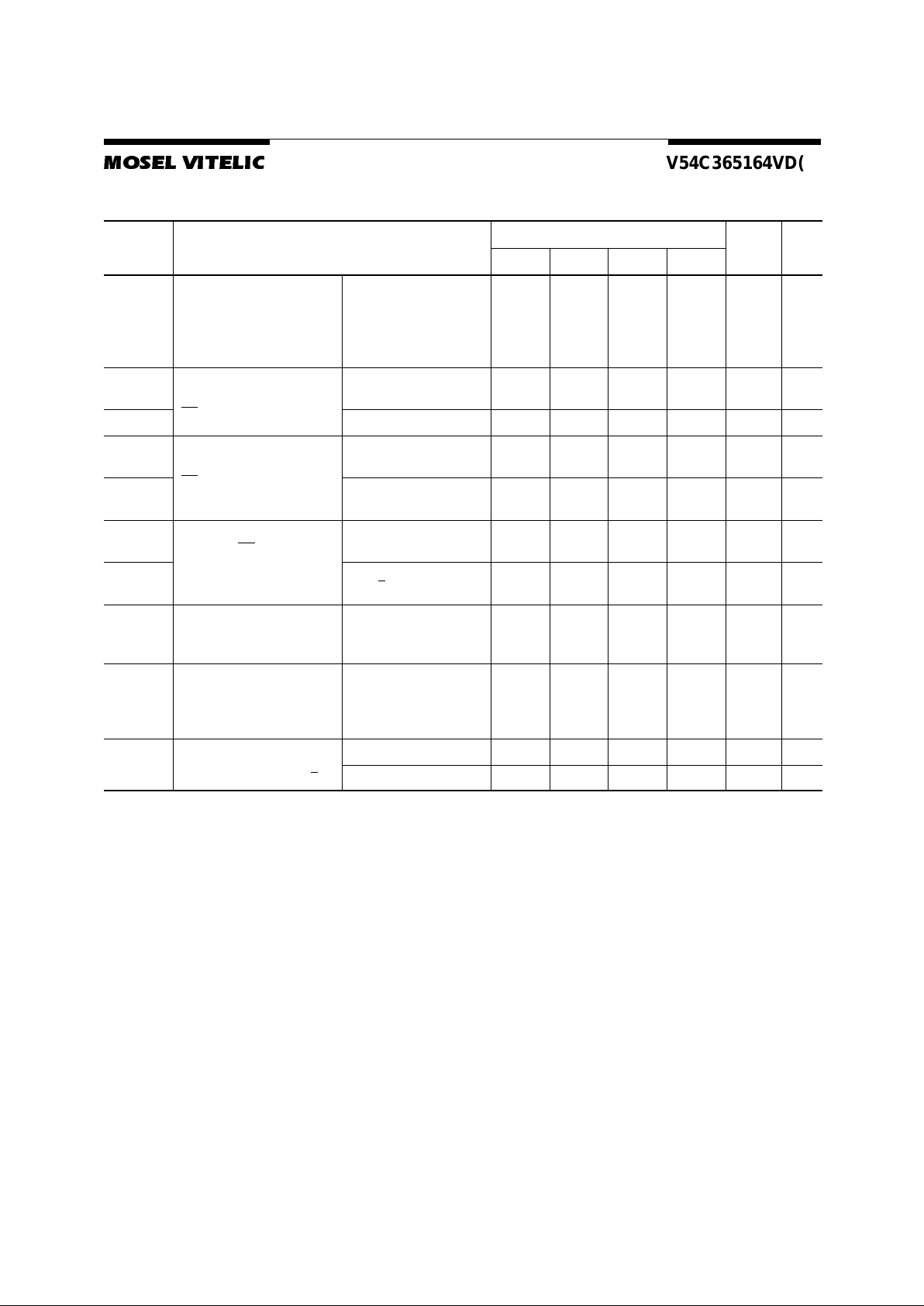

Operating Currents (T

A

=0to70°C, VCC=3.3V± 0.3V)

(Recommended Operating Conditions unless otherwise noted)

Notes:

7. These parametersdependon the cyclerate and these values are measured by the cycle rate under the minimumvalueof t

CK

and

t

RC

. Input signals are changedone time duringtCK.

8. These parameter depend on output loading. Specified values are obtained with output open.

Symbol Parameter & Test Condition

Max.

Unit Note-45-5-6-7

ICC1 Operating Current

t

RC=tRCMIN.,tRC=tCKMIN

.

Active-precharge command

cycling,

without Burst Operation

1 bank operation 188 180 165 150 mA 7

ICC2P Precharge StandbyCurrent

in Power Down Mode

CS

=VIH,CKE≤ V

IL(max)

tCK=min. 2222mA7

ICC2PS t

CK

=Infinity 1111mA7

ICC2N Precharge StandbyC urrent

in Non-Power Down Mode

CS

=VIH,CKE≥ V

IL(max)

tCK=min. 70655545mA

ICC2NS t

CK

=Infinity 5555mA

ICC3 No Operating Current

t

CK

=min,CS=V

IH(min)

bank ; active state ( 4 banks)

CKE ≥ V

IH(MIN.)

80 75 65 55 mA

ICC3P CKE <

V

IL(MAX.)

(Powerdownmode)

8888mA

ICC4 Burst Operating Current

t

CK

=min

Read/Write command cycling

145 140 130 120 mA 7,8

ICC5 Auto Refresh Current

t

CK

=min

Auto Refresh command cycling

180 175 165 150 mA 7

ICC6 Self Refresh Current

SelfRefreshMode, CKE<

0.2V

1111mA

L-version 500 500 500 500 µA

14

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

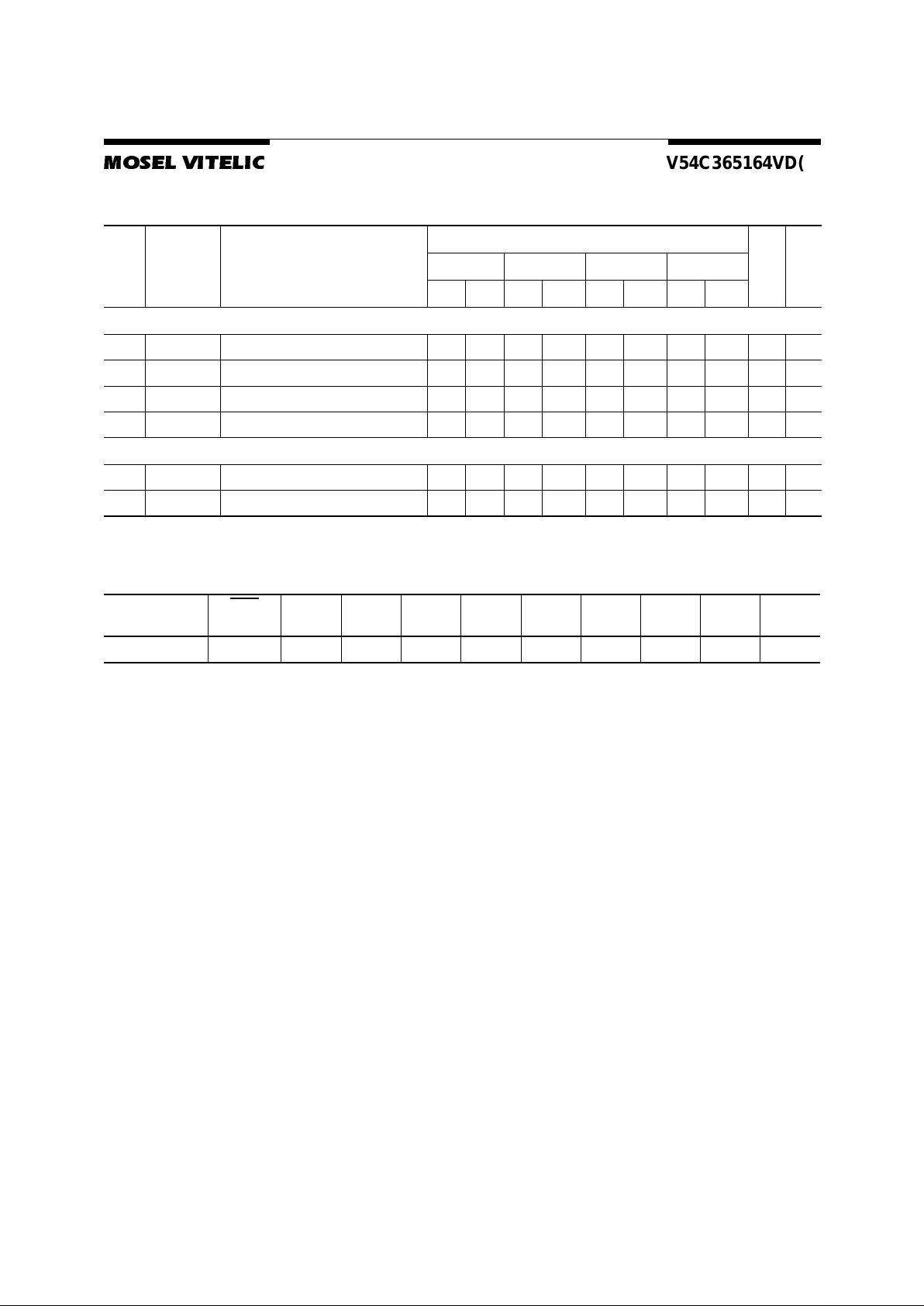

AC Cha racteristics

1,2, 3

TA=0to70°C; VSS=0V;VDD=3.3V±0.3V,tT=1ns

# Symbol Parameter

Limit Values

Unit Note

-45 -5 -6 -7

Min. Max. Min. Max. Min. Max. Min. Max.

Clock and Clock Enable

1tCKClockCycle Time

CAS

Latency = 3

CAS

Latency = 2

CAS

Latency = 1

4.5

10

12

–

–

–

5

10

12

–

–

–

6

10

12

–

–

–

7

10

12

–

–

–

s

ns

ns

ns

2t

CK

ClockFrequency

CAS

Latency = 3

CAS

Latency = 2

CAS

Latency = 1

–

–

–

225

100

83

–

–

–

200

100

83

–

–

–

166

100

83

–

–

–

143

100

83

MHz

MHz

MHz

3t

AC

Access Time from Clock

CAS

Latency = 3

CAS

Latency = 2

CAS

Latency = 1

–

–

–

4.5

4.5

11

–

_

–

5

5

11

–

_

–

5.4

5.5

11

–

_

–

5.4

5.5

11

ns

ns

ns

2, 4

4t

CH

ClockHigh Pulse Width 2.5 – 2.5 – 2.5 – 2.5 – ns

5t

CL

Clock Low Pulse Width 2.5 – 2.5 – 2.5 – 2.5 – ns

6t

T

TransitionTim 0.3 1.2 0.3 1.2 0.3 1.2 0.3 1.2 ns

Setup and Hold Times

7tISInputSetup Time 1.5 – 1.5 – 1.5 – 1.5 – ns 5

8t

IH

Input Hold Time 0.8 – 0.8 – 0.8 – 0.8 – ns 5

9t

CKS

CKE Setup Time 1.5 – 1.5 – 1.5 – 1.5 – ns 5

10 t

CKH

CKE Hold Time 0.8 – 0.8 – 0.8 – 0.8 – ns 5

11 t

RSC

Mode Register Set-up Time 9 – 10 – 12 – 14 – ns

12 t

SB

PowerDownModeEntryTime 045050607ns

Common Parameters

13 t

RCD

Row to Column Delay Time 14 – 15 – 20 – 20 – ns 6

14 t

RP

Row PrechargeTime 14 – 15 – 20 – 20 – ns 6

15 t

RAS

Row Active Time 38 100K 40 100K 40 100K 42 100K ns 6

16 t

RC

Row Cycle Time 60 – 60 – 60 – 60 – ns 6

17 t

RRD

Activate(a)to Activate(b) Command

Period

9 – 10 – 12 – 14 – ns 6

18 t

CCD

CAS(a) to CAS(b) Command Period 1 – 1 – 1 – 1 – CLK

Refresh Cycle

19 t

REF

RefreshPeriod (4096 cycles) – 64 — 64 — 64 — 64 ms

20 t

SREX

Self Refresh Exit Time 10 – 10 — 10 — 10 — ns

15

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Frequency vs. AC Parameter Relationship Table

-45 / -5 / -6 / -7

Read Cycle

21 t

OH

Data OutH old Time 2.5 -1 2.5 – 2.5 – 2.7 – ns 2

22 t

LZ

Data Out to Low Impedance Time 1 – 1 – 1 – 1 – ns

23 t

HZ

DataOuttoHighImpedanceTime – 4.5 – 5 – 5.4 – 5.4 ns 7

24 t

DQZ

DQM Data Out Disable Latency – 2 – 2 – 2 – 2CLK

Write Cycle

25 t

WR

WriteRecovery Time 2 – 2 – 2 – 2 – CLK

26 t

DQW

DQM Write Mask Latency 0 1 0 1 0 – 0 – CLK

Frequency

CAS

Latency t

RC

t

RAS

t

RP

t

RRD

t

RCD

t

CCD

t

CDL

t

RDL

Unit

83MHz(12ns)1 54222111CLK

# Symbol Parameter

Limit Values

Unit Note

-45 -5 -6 -7

Min. Max. Min. Max. Min. Max. Min. Max.

AC Cha racteristics (Cont’d)

16

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

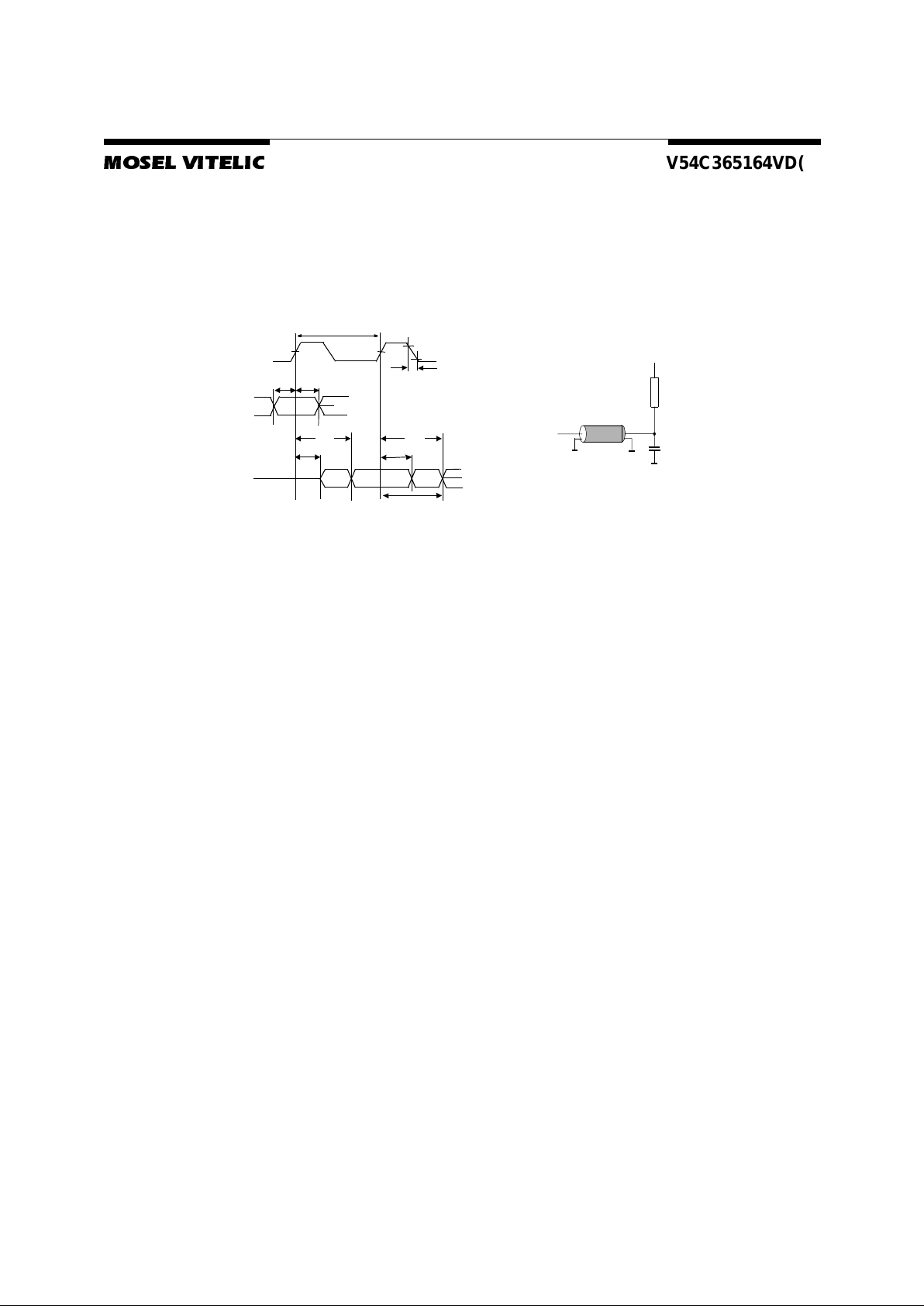

Notes for AC Parameters:

1. For proper power-up see the operation section of this data sheet.

2. AC timing tests have V

IL

= 0.8V andVIH= 2.0V with the timingreferencedto the 1.4 V crossoverpoint. The transition

timeismeasuredbetweenV

IH

and VIL.AllACmeasurementsassume tT= 1nswith the AC output loadcircuitshown

in Figure 1.

4. If clock rising time is longer than 1 ns, a time (t

T

/2 – 0.5) ns has to be added to this parameter.

5. If t

T

is longer than 1 ns, a time (tT– 1) ns has to be added to this parameter.

6. These parameter account for the number of clock cycle and depend on the operating frequency of the clock, as

follows:

the number of clock cycle = specified value of timing period (counted in fractions as a whole number)

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.

Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command

is registered.

7. Referenced to the time which the output achieves the open circuit condition, not to output voltage levels

1.4V

1.4V

tCS tCH

tAC

tAC

tLZ

tOH

tHZ

CLK

COMMAND

OUTPUT

50 pF

I/O

Z=50Ohm

+1.4V

50 Ohm

VIH

VIL

t

T

Figure1.

tCK

17

V54C365164VD(L) Rev. 1.3 September 2001

MOSEL VITELIC

V54C365164VD(L)

Timing Diagrams

1. Bank Activate Command Cycle

2. Burst Read Operation

3. Read Interrupted by a Read

4. Read to Write Interval

4.1ReadtoWriteInterval

4.2 Minimum Read to Write Interval

4.3 Non-Minimum Read to Write Interval

5. Burst Write Operation

6. Write and Read Interrupt

6.1 Write Interrupted by a Write

6.2 Write Interrupted by Read

7. Burst Write & Read with Auto-Precharge

7.1 Burst Wri te with Auto-Prec harge

7.2 Burst Read with Auto-Precharge

8. Burst Termination

8.1 Termination of a Ful l Page Burst Write Operation

8.2 Termination of a Ful l Page Burst Write Operation

9. AC- Parameters

9.1 AC Parameters for a Write T im ing

9.2 AC Parameters for a Read Timing

10. Mode Register S et

11. Power on Sequenc e and Auto Refresh (CBR)

12. Clock Suspension (using CKE)

12.1 Clock S us pens ion During Bu rst Read CAS

Latency = 2

12. 2 Clock Suspension D uring Burst Read CAS

Latency = 3

12. 3 Clock Suspension During Burst Write CAS

Latency = 2

12. 4 Clock Suspension During Burst Write CAS

Latency = 3

13. Power Down Mode and Clock Suspend

14. Self R ef resh (Entry and Exit)

15. Auto Refresh (CBR)

Loading...

Loading...