Mosel Vitelic V54C3256164VBLT8PC, V54C3256164VBLT7PC, V54C3256164VBLC8PC, V54C3256164VBLC8, V54C3256164VBLC7PC Datasheet

...

MOSEL VITELIC

1

V54C3256164VBUC/T

LOW POWER 256Mbit SDRAM

3.3 VOLT, 54-BALL SOC BGA

54-PIN TSOPII 16M X 16

V54C3256164VBUC/T Rev. 1.1 February 2003

PRELIMINARY

67PC78PC

System Frequency (f

CK

) 166 MHz 143 MHz 143 MHz 125 MHz

Clock Cycle Time (t

CK3

) 6 ns 7 ns 7 ns 8 ns

Clock Access Time (t

AC3

) CAS Latency = 3 5.4 ns 5.4 ns 5.4 ns 6 ns

Clock Access Time (t

AC2

) CAS Latency = 2 5.4 ns 5.4 ns 6 ns 6 ns

Features

■ 4 banks x 4Mbit x 16 organization

■ High speed data transfer rates up to 166 MHz

■ Full Synchronous Dynamic RAM, with all signals

referenced to clock rising edge

■ Single Pulsed RAS

Interface

■ Data Mask for Read/Write Control

■ Four Banks controlled by BA0 & BA1

■ Programmable CAS

Latency: 2, 3

■ Programmable Wrap Sequence: Sequential or

Interleave

■ Programmable Burst Length:

1, 2, 4, 8 for Sequential Type

1, 2, 4, 8 for Interleave Type

■ Multiple Burst Read with Single Write Operation

■ Automatic and Controlled Precharge Command

■ Random Column Address every CLK (1-N Rule)

■ Power Down Mode

■ Auto Refresh and Self Refresh

■ Refresh Interval: 8192 cycles/64 ms

■ Available in 54-Ball SOC BGA/ 54-Pin TSOP II

■ LVTTL Interf a ce

■ Single +3.3 V ±0.3 V Power Supply

■ Low Power Self Refresh Current

■ L-version 1.0mA

■ U-version 0.6mA

Description

The V54C3256164VBUC/T is a low power four

bank Synchronous DRAM organized as 4 banks x

4Mbit x 16. The V54C3256164VBUC/T achieves

high speed data transfer rates up to 16 6 MHz by

employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a

system clock

All of the control , address, data input and output

circuits are synchronized with the positive edge of

an externally supplied clock.

Operating the four memory banks in an interleaved fashion allows random access operation to

occur at higher rate t han is possible with standard

DRAMs. A sequential and gapless data rate of up to

166 MHz is possible depending on burst length,

CAS

latency and speed grade of the device.

The V54C3256164VBU C/T is ideally suited for

high performance, low power systems such as

PDA, mobile phone, DSC, and other battery backup

applications.

Device U sage Chart

Operating

Temperature

Range

Package Out-

line Access Time (ns) Power

Temperature

MarkC/T 6 7PC 7 8PC Std. L U T

0°C to 70°C • ••••••••Blank

2

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

V 54 C 3 25616 4 V B U X

Mosel Vitelic

Manufactured

Synchronous

DRAM Family

C=CMOS Family

3.3V, LVTTL Interface

256Mb(8K Refresh)

4 Banks

V=LVTTL

Component Rev Level

Special

Feature

L=Low Power

C= 54Ball SOC BGA

T= 54Pin TSOP Package

Device

Number

Speed

6 ns

7 ns

8 ns

B=0.14um

U=Ultra Low Power

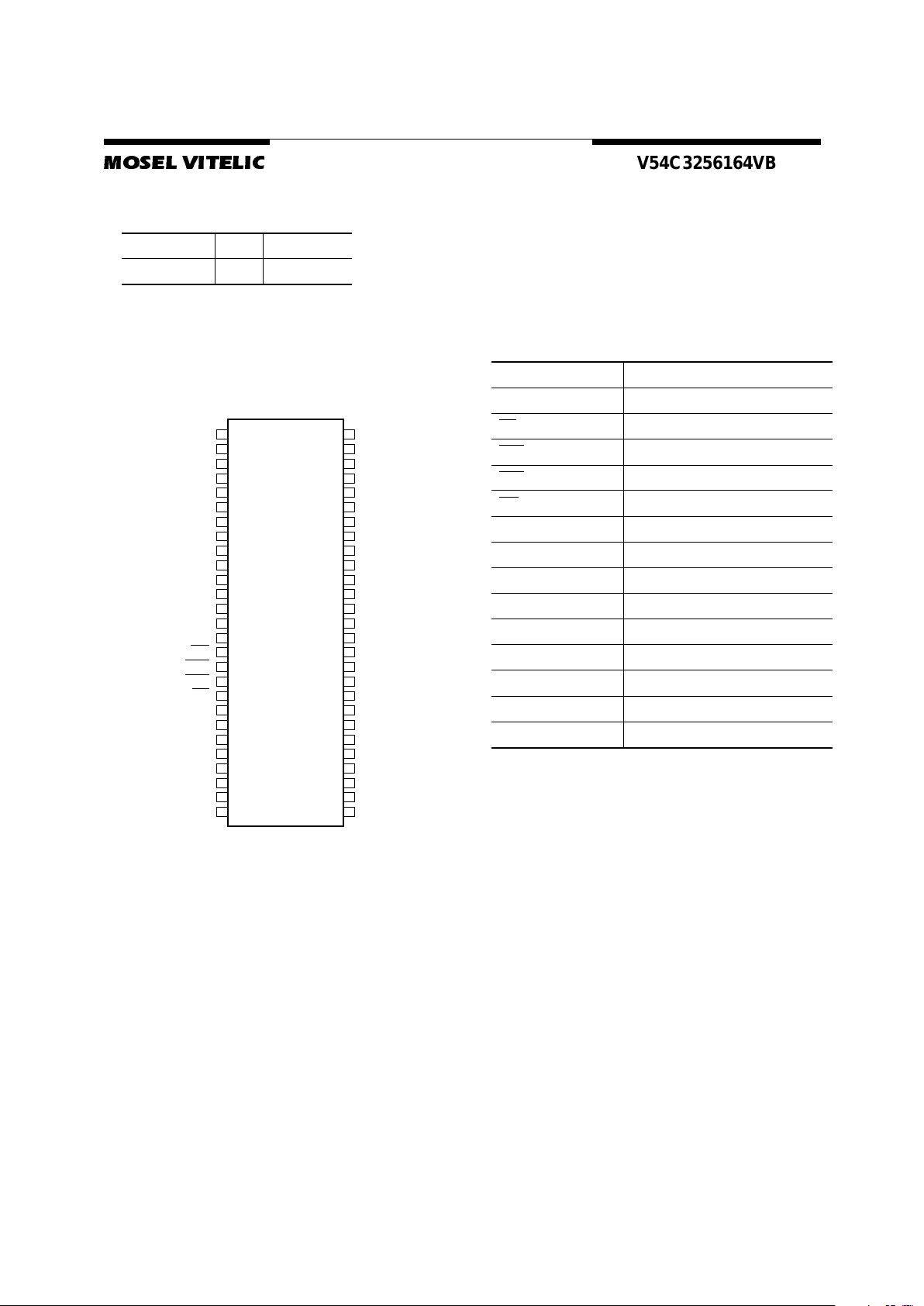

Description Pkg. Pin Count

SOC BGA C 54

A

B

C

D

E

F

G

H

J

:

Ball Existing

: Depopulated Ball

Top View

(See the balls through the package)

54B SOC BGA

1 2 3 7 8 9

A

B

C

D

E

F

G

H

J

x16

VSS

DQ14

DQ12

DQ10

DQ8

UDQM

DQ15

DQ13

DQ11

DQ9

NC

CLK

A11

A7

A5

VSSQ

VCCQ

VSSQ

VCCQ

VSS

CKE

A9

A6

A4

A12

A8

VSS

VCCQ

VSSQ

VCCQ

VSSQ

VCC

CAS

DQ0

DQ2

DQ4

DQ6

LDQM

RAS

BA1

A1

A2

VCC

DQ1

DQ3

DQ5

DQ7

WE

BA0

A0

A3

CS

A10

VCC

8

2

7

1

354

6

9

3

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

54 Pin Plastic TSOP -I I

PIN CONFIGURATION

Top View

Pin Names

V

CC

I/O

1

V

CCQ

I/O

2

I/O

3

V

SSQ

I/O

4

I/O

5

V

CCQ

I/O

6

I/O

7

V

SSQ

I/O

8

V

CC

L

DQM

WE

CAS

RAS

CS

BA0

BA1

A

10

A

0

A

1

A

2

A

3

V

CC

V

SS

I/O

16

V

SSQ

I/O

15

I/O

14

V

CCQ

I/O

13

I/O

12

V

SSQ

I/O

11

I/O

10

V

CCQ

I/O

9

V

SS

NC

UDQ

M

CLK

CKE

A

12

A11

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

356164V-01

CLK Clock Input

CKE Clock Enable

CS

Chip Select

RAS

Row Address Strobe

CAS

Column Address Strobe

WE

Write Enable

A

0–A12

Address Inputs

BA0, BA1 Bank Select

I/O

1

–I/O

16

Data Input/Output

LDQM, UDQ M Data Mask

V

CC

Power (+3.3V)

V

SS

Ground

V

CCQ

Power for I/O’s (+3.3V)

V

SSQ

Ground for I/O’s

NC Not connected

Description Pkg. Pin Count

TSOP-II T 54

MOSEL VITELIC

V54C3256164VBUC/T

4

V54C3256164VBUC/T Rev1.1 February 2003

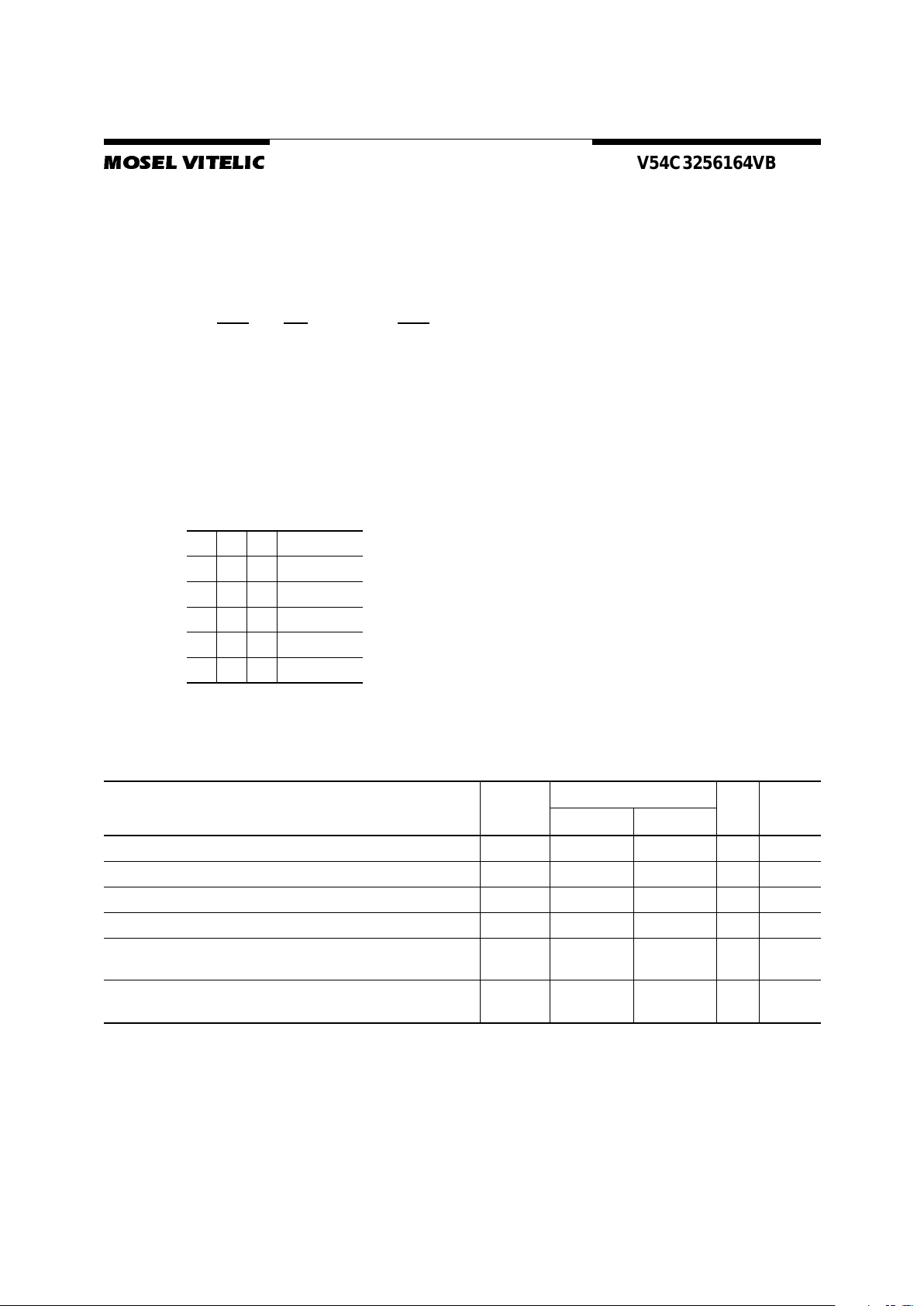

Capacitance*

TA = 0 to 70°C, VCC = 3.3 V ± 0.3 V, f = 1 Mhz

*Note:Capacitance is sampled and not 100% tested.

Absolute Maximum Ratings*

Operatin g tempe r a tu re r a n ge..................0 to 70 °C

Storage temperature range................-55 to 150 °C

Input/ou tp u t vo lt a g e....... ...........-0.3 to (V

CC

+0.3) V

Power supply volt a g e.................. ........-0.3 to 4.6 V

Power dissipation..............................................1 W

Data out current (short circuit).......................50 mA

*Note: Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage of the device.

Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Symbol Parameter

Max. Unit

C

I1

Input Ca pacitance (A0 to A12) 5 pF

C

I2

Input Capacitance

RAS

, CAS, WE, CS, CLK, CKE, DQM

5pF

C

IO

Output Capacitance (I/O) 6.5 pF

C

CLK

Input Capacitance (CLK) 4 pF

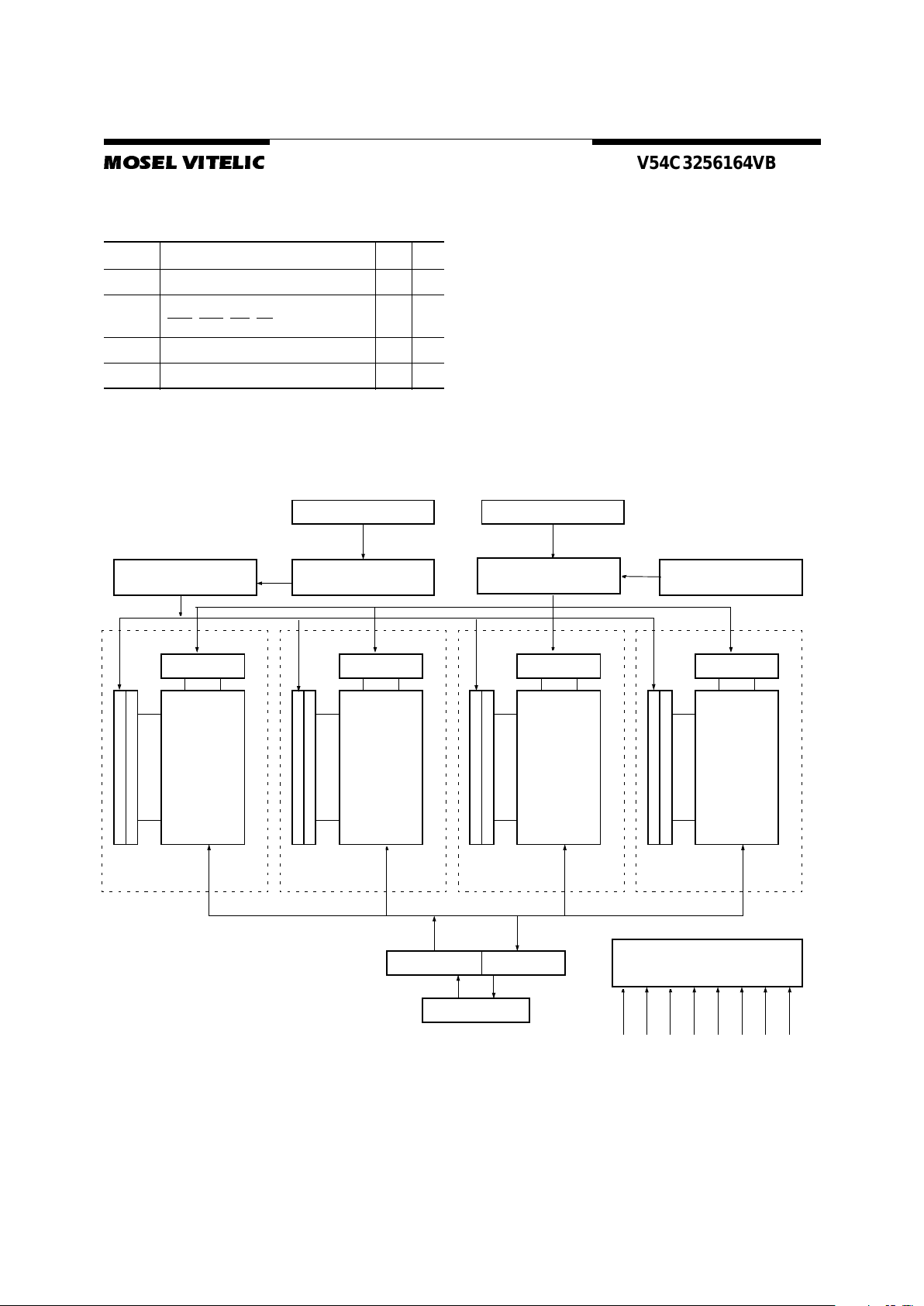

Block Diagram

Row decoder

Memory array

Bank 0

8192 x 512

x 16 bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory ar ray

Bank 1

8192 x 512

x16 bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 2

8192 x 51 2

x 16 bit

Column decoder

Sense amplifier & I(O) bus

Row decoder

Memory array

Bank 3

8192 x 512

x 16 bit

Column decoder

Sense amplifier & I(O) bus

Input buffer Output buffer

I/O1-I/O

16

Column address

counter

Column address

buffer

Row address

buffer

Refresh Counter

A0 - A12, BA0, BA1A0 - A8, AP, BA0, BA1

Control logic & timing generato r

CLK

CKE

CS

RAS

CAS

WE

LDQM

Row Addresses

Column Addresses

UDQM

x16 Configuration

5

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

Signal Pi n D escrip t i o n

Pin Type Signal Polarity Function

CLK Input Pulse Positive

Edge

The system clock input. All of the SDRAM inputs are sampled on the rising edge of the

clock.

CKE Input Level Active High Activates th e CLK signal when hi gh and deactivate s the CLK signal when low, thereby

initiates either the Power Down mode or the Self Refresh mode.

CS

Input Pulse Active Low CS enables t he comm and decoder when low and disables th e comman d decod er when

high. Wh en the co mma nd de co der i s d is ab led, ne w com man ds ar e ign or e d but pr ev ious

operations continue.

RAS

, CAS WEInput Pulse Active Low When sampled at the positive rising ed ge of the cl ock, CAS, RAS, and WE define the

command to be executed by the SDRAM.

A0 - A11 Input Level — During a Bank Acti vate command cycle, A0-A12 defines the row add ress (RA0-RA12)

when sampled at the rising clock edge.

During a Read or Write command cycle, A0-An def ines the column address (C A0-CAn)

when sampled at the rising clock edge.CAn depends from the SDRAM organization:

• 16M x 16 SDRAM CA0–CA8.

In addition to the column address, A10(=AP) is used to invoke autoprechar ge operation

at the end of the burst read or write cycle. If A10 is h igh, autoprecha rge is selected and

BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is di sabled.

During a Pr ec har ge comman d c ycl e , A1 0( =AP ) i s us ed in conj un ct io n wi th B A0 a nd BA1

to control which bank(s) to precharge. If A10 is high, all four banks will BA0 and BA1 are

used to define which bank to precharge.

BA0,

BA1

Input Level — Selects which bank is to be active.

DQx Input

Output

Level — Data Input/Output pi ns operate in the same manner as on convention al DRAMs.

LDQM

UDQM

Input Pulse Active High The Data Input/Output mask places the DQ buffers in a high impedance state when sam-

pled high . In Re ad mode, DQ M has a lat en cy of t wo cl oc k cyc le s an d co ntr ols the out put

buffer s li ke an ou tput e na ble. I n Wr i te mo de , DQ M ha s a lat en cy of zer o and o pe rat es as

a word mask by allowing input data to be written if it is low but blocks the write operation

if DQM is high.

VCC, VSS Supply Power an d ground for the inp ut bu ff e rs and the core logic .

VCCQ

VSSQ

Supply — — Isolated power supply and ground for the output buffers to provide improved noise

immunity.

6

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

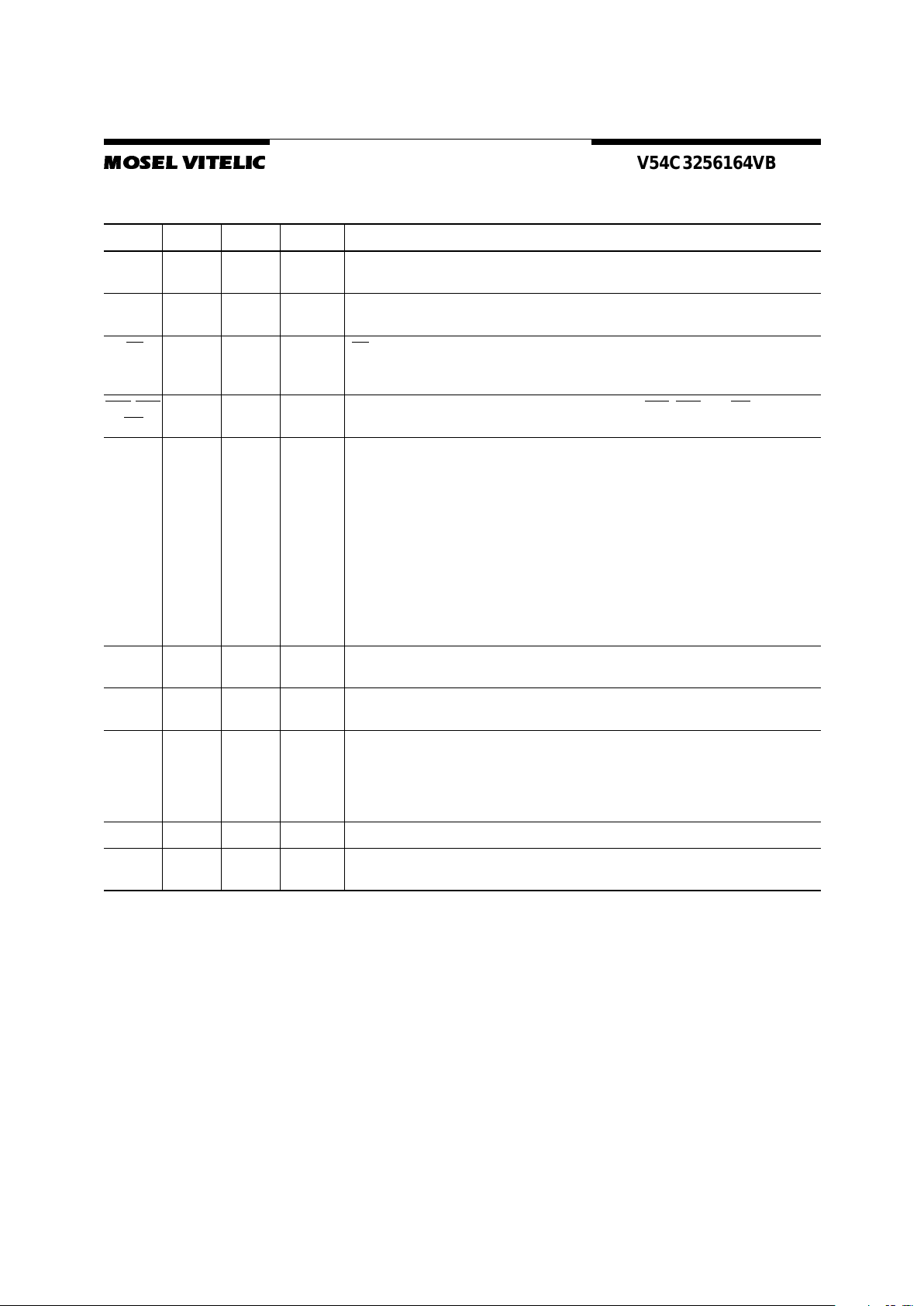

Operation Definition

All of SDRAM operations are defined by states of c ontrol signals CS, RAS, CAS, WE, and DQM at the

positive edge of the clock. The following list shows the thruth table for the operation commands.

Notes:

1. V = Valid , x = Don’t Care, L = Low Level, H = H igh Lev el

2. CKEn signal is input level when commands are provided, CKEn-1 si gnal is input level one clo c k before the commands

are provided.

3. These are state of bank designated by BS0, BS1 signals.

4. Power Down Mode can n ot entry in the burs t cycle.

Operation

Device

State

CKE

n-1

CKE

nCSRAS CAS WE DQM

A0-9,

A11,

A12 A10

BS0

BS1

Row Activate Idle3 HXLLHHXVVV

Read Active

3

HXLHLHXVLV

Read w/Autoprecharge Active

3

HXLHLHXVHV

Write Active

3

HXLHLLXVLV

Write with Autoprecharge Active

3

HXLHLLXVHV

Row Precharge Any H X L L H L X X L V

Precharge All Any H X L L H L X X H X

Mode Register Set Idle H X L L L L X V V V

No Operation Any H X L H H H X X X X

Device Dese lect Any H X H X X X X X X X

Auto Refresh Idle H H L L L H X X X X

Self Refresh Entry Idle H L L L L H X X X X

Self Refresh Exit Idle

(Sel f Refr.) L H

HXXX

XXXX

LHHX

Power Down Entry Idle

Active

4

HL

HXXX

XXXX

LHHX

Power Down Exit Any

(Power

Down)

LH

HXXX

XXXX

LHHL

Data Write/Output Enable Active H X X X X X L X X X

Data Write/Output Disable Active H X X X X X H X X X

7

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

Power On and Initialization

The default power on state of the mode register is

supplier specific and may be undefined. The

following power on and initialization sequence

guarantees the device is preconditioned to each

users specific needs. Like a conventional DRAM,

the Synchronous DRAM mu st be powered up and

initialized in a predefined manner. During power on,

all VCC and VCCQ pins must be built up

simultaneously to the specified voltage when the

input signals are held in the “NOP” state. The power

on voltage must not exceed VCC+0.3V on any of

the input pins or VCC supplies. The CLK signal

must be started at the same time. After power on,

an initial pause of 200 µs is requi red followed by a

precharge of both banks using the precharge

command. To preven t data contention on the DQ

bus during power on, it is required that the DQM and

CKE pins be held high during the initial pause

period. Once all banks have bee n precharged, the

Mode Register Set Command must be issued to

initialize the Mode Register. A minimum of eight

Auto Refresh cycles (CBR) are also required.These

may be done before or after programming the Mode

Register. Failure to follow these steps may lead to

unpredictable start-up modes.

Programming the Mode Register

The Mode register designates the operation

mode at the read or write cycle. This register is divided into 4 fields. A Burst Length Field to set the

length of the b urst, an Addressing S election bit to

program the column access sequence in a burst cycle (interleaved or sequential), a CAS Latency Field

to set the access time at clock cycle and a Operation mode field to differentiate between normal operation (Burst read an d burst Write) and a spec ial

Burst Read and Sing le Write mode. The mode set

operation must be done before any activate command after the initial power up. Any content of the

mode register can be altered by re-executing the

mode set command. All banks must be in precharged state and CKE must be high at least one

clock before the mode set operation. After the mode

register is set, a Standby or N OP command is required. Low signals of RAS

, CAS , and WE at the

positive edge of the clock activate the mode set operation. Address input data at this timing defines parameters to be set as shown in the previous table.

Read and Write Operation

When RAS is low and both CAS and WE are hig h

at the positive edge of the clock, a RAS cycle starts.

According to address data, a word line of the selected bank is activated and all of sense amplifiers associated to the wordline are set. A CAS

cycle is

triggered by setting RAS

high and CAS low at a

clock timing after a necessary delay, t

RCD

, from th e

RAS

timing. WE is used to define either a read

(WE

= H) or a write (WE = L) at this stage.

SDRAM provides a wide variety of fast access

modes. In a single CAS cycle, serial data read or

write operations are allowed at up to a 125 MHz

data rate. The numbers of serial data b its are the

burst length programmed at the mode set operation,

i.e., one of 1, 2, 4, 8 . Column addresses are segmented by the burst length and serial data accesses

are done within this boundary. T he first colum n address to be accessed is supplied at the CAS timing

and the subsequent addresses are generated automatically by the programmed burst length and its

sequence. For example, in a burst length of 8 with

interleave sequence, if the first address is ‘2’, then

the rest of the burst sequence is 3, 0, 1, 6, 7, 4, and

5.

MOSEL VITELIC

V54C3256164VBUC/T

8

V54C3256164VBUC/T Rev1.1 February 2003

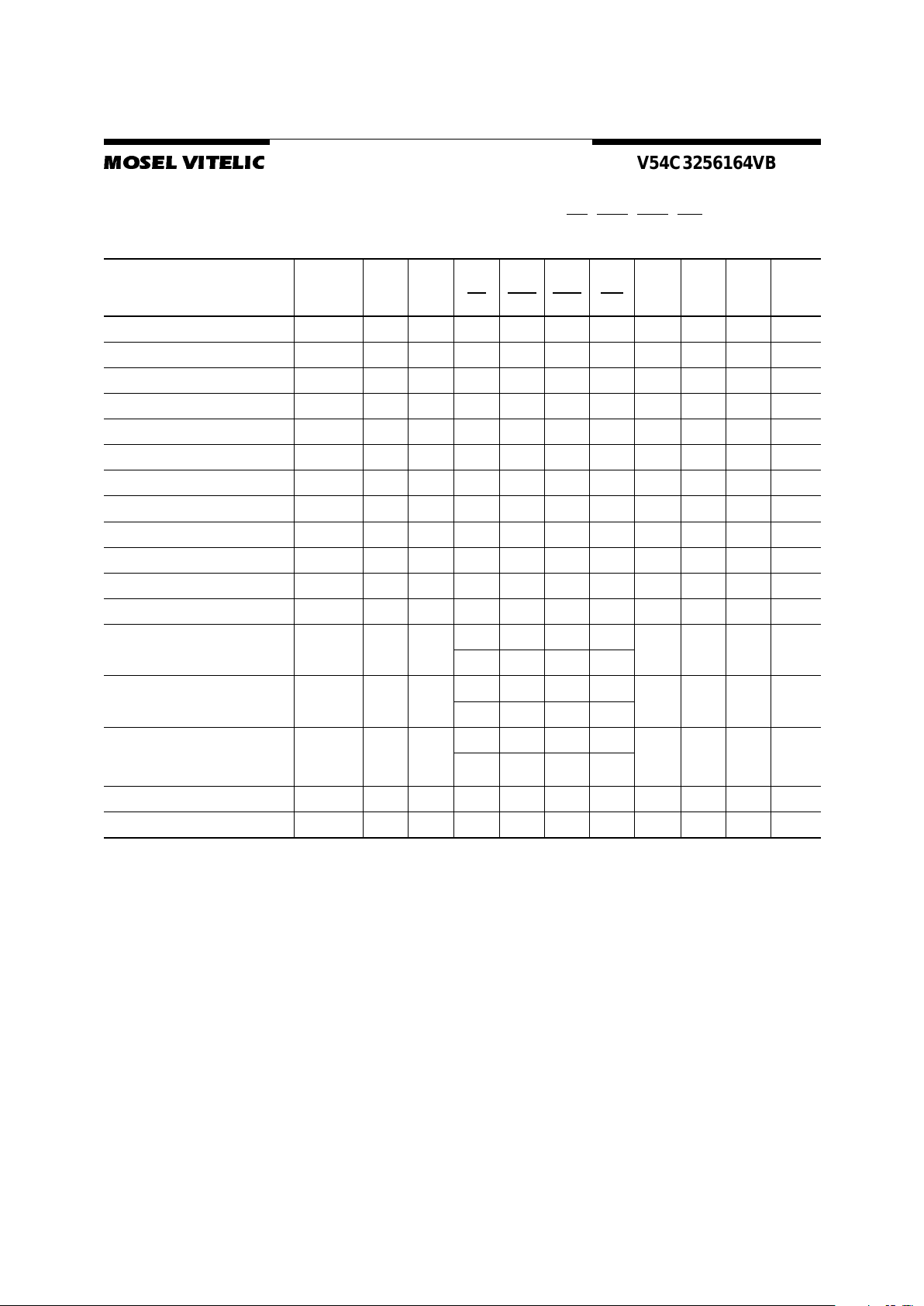

Address Input for Mode Set (Mode Register Operation)

Similar to the page mode of conventional

DRAM’s, burst read or write accesses on any column address are possible once the RAS cycle

latches the sense amplifiers. The maximum t

RAS

or

the refresh interval time limits the number of random

column accesses. A new burst access can be done

even before the previous burst ends. The interrupt

operation at every clock cycles is supported. When

the previous burst is interrupted, the remaining addresses are overridden by the new address with the

full burst length. An interrupt which accompanies

with an operation change from a read to a write is

possible by exploiting DQM to avoid bus contention.

When two or more banks are activated

sequentially, interleaved bank read or write

operations are possible. With the programmed

burst length, alternate access and precharge

operations on two or more banks can real ize fast

serial data access modes among many different

pages. Once two or more banks are activated,

column to column interleave operation can be done

between different pages.

A11

A3A4 A2 A1 A0

A10 A9

A8 A7 A6 A5

Address Bus (Ax)

BT Burst LengthCAS Latency

Mode Register

CAS Latency

A6 A5 A4 Latency

0 0 0 Reserve

0 0 1 Reserve

010 2

011 3

1 0 0 Reserve

1 0 1 Reserve

1 1 0 Reserve

1 1 1 Reserve

Burst Length

A2 A1 A0

Length

Sequential Interleave

000 1 1

001 2 2

010 4 4

011 8 8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

1 1 1 Reserve Reserve

Burst Type

A3 Type

0 Sequential

1 Interleave

Operation Mode

BA1 BA0 A11 A10 A9 A8 A7 Mode

0000000

Burst Read/Burst

Write

0000100

Burst Read/Single

Write

Operation Mode

BA0BA1

9

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

Burst Length and Sequence:

Refresh Mode

SDRAM has two refresh modes, Auto Refresh

and Self Refresh. Auto Refresh is similar to the CAS

-before-RAS refresh of conventional DRAMs. All of

banks must be precharged before ap plying any refresh mode. An on-chip address counter increments

the word and the bank addresses and no bank information is required for both refresh modes.

The chip enters the Auto Refresh mode, when

RAS

and CAS are held low and CKE and WE are

held high at a clock timing. The mode restores word

line after the refresh and no external precharge

command is necessary. A m inimum tRC t ime is required between two automatic refreshes in a burst

refresh mode. The same rule applies to any access

command after the automatic refresh operation.

The chip has an on-chip timer and the Self Refresh mode is available. It enters the mode when

RAS

, CAS, and CKE are low and WE is high at a

clock timing. All of external control signals including

the clock are disabled. Returning CKE to hi gh enables the clock and initiates the refr esh exit operation. After the exit command, at least one t

RC

delay

is required prior to any access command.

DQM Function

DQM has two functions for data I/O read and

write operations. During reads, when it turns to

“high” at a clo ck timing, data outputs are disabled

and become high impedanc e after two clock delay

(DQM Data Disable Latency t

DQZ

). It also provides

a data mask function for writes. When DQM is activated, the write operation at the next clock is prohibited (DQM Write Mask Latency t

DQW

= zero clocks).

Power Do wn

In order to reduce standby power consumption, a

power down mode is available. All banks m ust be

precharged and the necessary Precharge delay

(trp) must occur bef ore the SDRAM can en ter the

Power Down mode. Once the Power Down mode is

initiated by holding CKE low, all of the receiver circuits except CLK and CKE are gated off. The Power

Down mode does not perform any refresh operations, therefore the device can’t remain in Power

Down mode longer than the Refresh period (tref) of

the device. Exit from this mode is performed by taking CKE “high”. One clock delay is required for

mode entry and exit.

Auto Pr ech arge

Two methods are available to precharge

SDRAMs. In an automatic precharge mode, the

CAS timing accepts one extra address, CA10, to

determine whether the chip restores or not after the

operation. If CA10 is high whe n a Read Com mand

is issued, the Read with Auto-Pre charge function

is initiated. The SDRAM automatically enters the

precharge operation one clock bef ore the last data

out for CAS

latencies 2, two clocks for CAS latencies 3 and three clocks for CAS latencies 4. If CA10

is high when a Write Command is issued, the Write

Burst

Length

Starting Address

(A2 A1 A0)

Sequential Burst Addressing

(decimal)

Interleave Bur st Addressing

(decimal)

2 xx0

xx1

0, 1

1, 0

0, 1

1, 0

4x00

x01

x10

x11

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

8 000

001

010

011

100

101

110

111

0 1 2 3 4 5 6 7

1 2 3 4 5 6 7 0

2 3 4 5 6 7 0 1

3 4 5 6 7 0 1 2

4 5 6 7 0 1 2 3

5 6 7 0 1 2 3 4

6 7 0 1 2 3 4 5

7 0 1 2 3 4 5 6

0 1 2 3 4 5 6 7

1 0 3 2 5 4 7 6

2 3 0 1 6 7 4 5

3 2 1 0 7 6 5 4

4 5 6 7 0 1 2 3

5 4 7 6 1 0 3 2

6 7 4 5 2 3 0 1

7 6 5 4 3 2 1 0

MOSEL VITELIC

V54C3256164VBUC/T

10

V54C3256164VBUC/T Rev1.1 February 2003

with Auto-Precharge function is initiated. The

SDRAM automatically enters the precharge o peration a time delay equal to t

WR

(Write recovery time)

after the last data in.

Precha r g e C o mmand

There is also a separate precharge command

available. When RAS

and WE are low and CAS is

high at a clock timing, it triggers the precharge

operation. Three address bits, BA0, BA1 and A10

are used to define banks as shown in the following

list. The precharge comma nd can be i mposed o ne

clock before the last data ou t for CAS latency = 2,

two clocks before the last data out for CAS latency

= 3. Writes require a time delay t wr from the last

data out to apply the precharge command.

Bank Selection by Address Bits:

Burst Termination

Once a burst read or write operation has been initiated, there are several methods in whi ch t o terminate the burst operation prematurely. These

methods include using another Read or Write Command to interrupt an existing burst operation, use a

Precharge Command to interrupt a burst cycle and

close the active bank, or using the Burst Stop Command to terminate the existing burst operation b ut

leave the bank open fo r future Re ad or Write Commands to the same page of the act ive bank. When

interrupting a burst with another Read or Write

Command care must be taken to avoid I/O contention. The Burst Stop Command, however, has the

fewest restrictions making it th e easiest method to

use when terminating a burst operation before it has

been completed. If a Burst Stop command is issued

during a burst write operation, then any residual

data from the burst write cycle will be ignored. Data

that is presented on the I /O pins before the Burst

Stop Command is registered will be written to the

memory.

A10 BA0 BA1

0 0 0 Bank 0

0 0 1 Bank 1

0 1 0 Bank 2

0 1 1 Bank 3

1XX all Banks

Recommended Operation and Characteristics for LV-TTL

TA = 0 to 70 °C; VSS = 0 V; VCC,V

CCQ

= 3.3 V ± 0.3 V

Note:

1. All voltages are referenced to V

SS

.

2. V

IH

may overshoot to VCC + 2.0 V for pulse width of < 4ns wit h 3.3V. VIL may unde rshoot to -2.0 V for pulse width < 4.0 ns with

3.3V. Pu lse width measur ed at 50% points with amplitude m easured peak to DC reference.

Parameter Symbol

Limit Values

Unit Notesmin. max.

Input hi gh voltage V

IH

2.0 Vcc+0. 3 V 1, 2

Input lo w volt ag e V

IL

– 0.3 0.8 V 1, 2

Output high voltage (I

OUT

= – 4.0 mA) V

OH

2.4 – V

Output low voltage (I

OUT

= 4.0 mA) V

OL

–0.4V

Input le ak age curren t, any input

(0 V < V

IN

< 3.6 V, all other inputs = 0 V)

I

I(L)

– 5 5 µA

Output leakage current

(DQ is disabled, 0 V < V

OUT

< VCC)

I

O(L)

– 5 5 µA

11

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

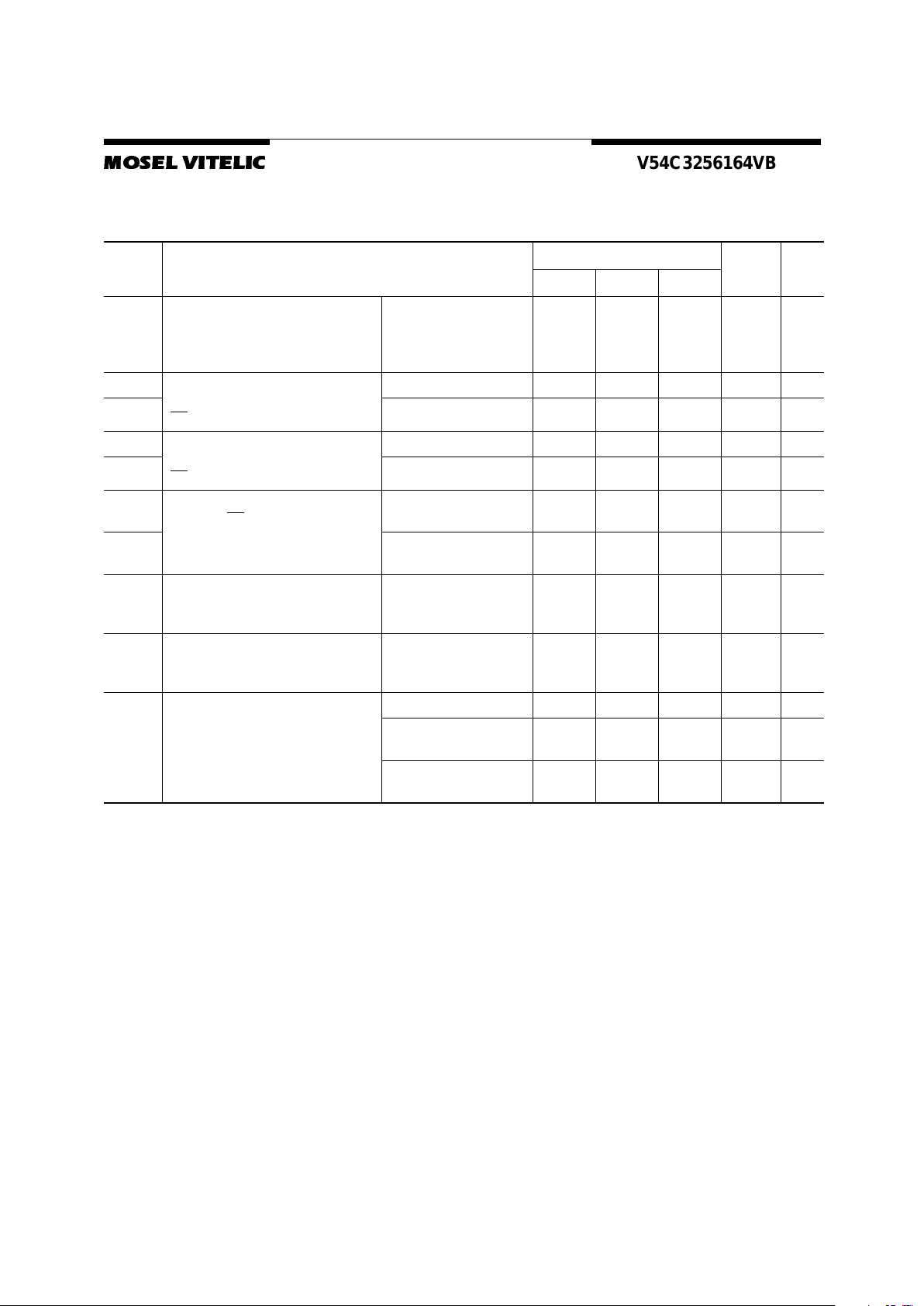

Opera ti n g Cu r r en ts (T

A

= 0 to 70°C, VCC = 3.3V ± 0.3V)

(Recommended Operating Conditions unle ss otherwise noted)

Notes:

7. These parameters depend on the cycle rate and these values are measured by the cycle rate und er the mi nimum value of t

CK

and

t

RC

. Input signals are changed one time during tCK.

8. These pa rameter depend on output loading. Specified values are obtained with output open.

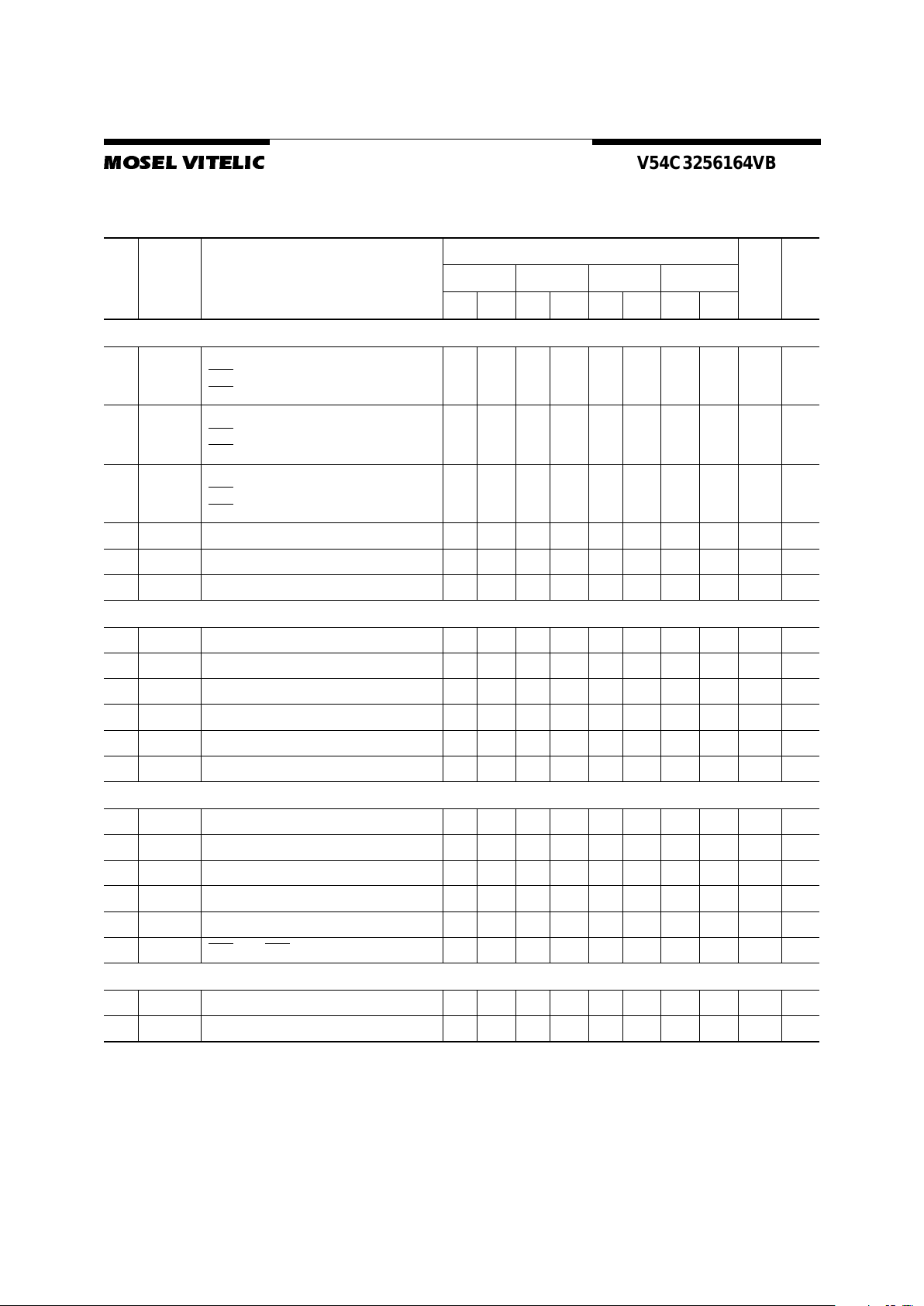

Symbol Parameter & Test C on dition

Max.

Unit Note-6 -7 / -7PC -8PC

ICC1 Operating Current

t

RC

= t

RCMIN.

, t

RC

= t

CKMIN

.

Active- precharge command cycling,

without Burst Operation

1 bank operation 90 80 80 mA 7

ICC2P Precharge Standby Current

in Power Down Mode

CS

=VIH, CKE≤ V

IL(max)

tCK = min. 2 2 2 mA 7

ICC2PS t

CK

= Infinity 1 1 1 m A 7

ICC2N Precharge Standby Current

in Non-Power Down Mode

CS

=VIH, CKE≥ V

IL(max)

tCK = min. 55 45 35 mA

ICC2NS t

CK

= Infinity 5 5 5 m A

ICC3N No Operating Cur rent

t

CK

= min, CS = V

IH(min)

bank ; ac tive state ( 4 banks)

CKE ≥ V

IH(MIN.)

65 55 45 mA

ICC3P CKE ≤ V

IL(MAX.)

(Power down mode)

10 10 10 mA

ICC4 Burst Operating Current

t

CK

= min

Read/Write command cycling

170 150 120 mA 7,8

ICC5 Auto Refresh Current

t

CK

= min

Auto Refresh command cycling

270 240 220 mA 7

ICC6 Self Refresh Current

Self Refresh Mode, CKE≤ 0.2V

333mA

L-version

(B component rev)

1.0 1.0 1.0 mA

U-version

(B component rev)

0.6 0.6 0.6 mA

12

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

AC Characteristics

1,2, 3

T

A

= 0 to 70 °C; VSS = 0 V; VDD = 3.3 V ± 0.3 V, tT = 1 ns

# Symbol Parameter

Limit Values

Unit Note

-6 -7PC -7

-8PC

Min. Max. Min. Max. Min. Max. Min. Max.

Clock and Clock Enable

1tCKClock Cycle Time

CAS

Latency = 3

CAS

Latency = 2

6

7.5––77.5––710––810––

s

ns

ns

2t

CK

Clock Frequency

CAS

Latency = 3

CAS

Latency = 2

––166

133––

143

133––

143

100––

125

100

MHz

MHz

3t

AC

Access Time from Clock

CAS

Latency = 3

CAS

Latency = 2

–_5.4

5.4–_

5.4

5.4–_

5.46–

_

6

6

ns

ns

2, 4

4t

CH

Clock High Pulse Width 2.5–2.5–2.5–3–ns

5t

CL

Clock Low Pulse Width 2.5–2.5–2.5–3–ns

6t

T

Transitio n Tim 0.3 1.2 0.3 1 .2 0 .3 1. 2 0.5 1 0 ns

Setup and Hold Times

7tISInput Setup Time 1.5–1.5–1.5–2–ns5

8t

IH

Input Hold Time 0.8–0.8–0.8–1–ns5

9t

CKS

Input Setup Time 1.5–1.5–1.5–2–ns5

10 t

CKH

CKE Hold Time 0.8–0.8–0.8–1–ns5

11 t

RSC

Mode Register Set -up Time 12 – 14 – 14 – 16 – ns

12 t

SB

Power Down Mode Entry Time 06070708ns

Common Parameters

13 t

RCD

Row to Column Delay Time 12 – 15 – 15 – 20 – ns 6

14 t

RP

Row Precharge T ime 15 – 15 – 15 – 20 – ns 6

15 t

RAS

Row Active Time 40 100K 42 100K 42 100K 45 100k ns 6

16 t

RC

Row Cycle Time 60 – 60 – 60 – 60 – ns 6

17 t

RRD

Activate(a) to Activate(b) Command Period 12 – 14 – 14 – 16 – ns 6

18 t

CCD

CAS(a) to CAS(b) Command Period 1 – 1 – 1 – 1 – CLK

Refresh Cycle

19 t

REF

Refres h Period (8192 cycles) — 64 — 64 — 64 — 64 ms

20 t

SREX

Self Ref res h E x it Tim e 1 — 1 — 1 — 1 — CL K

13

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

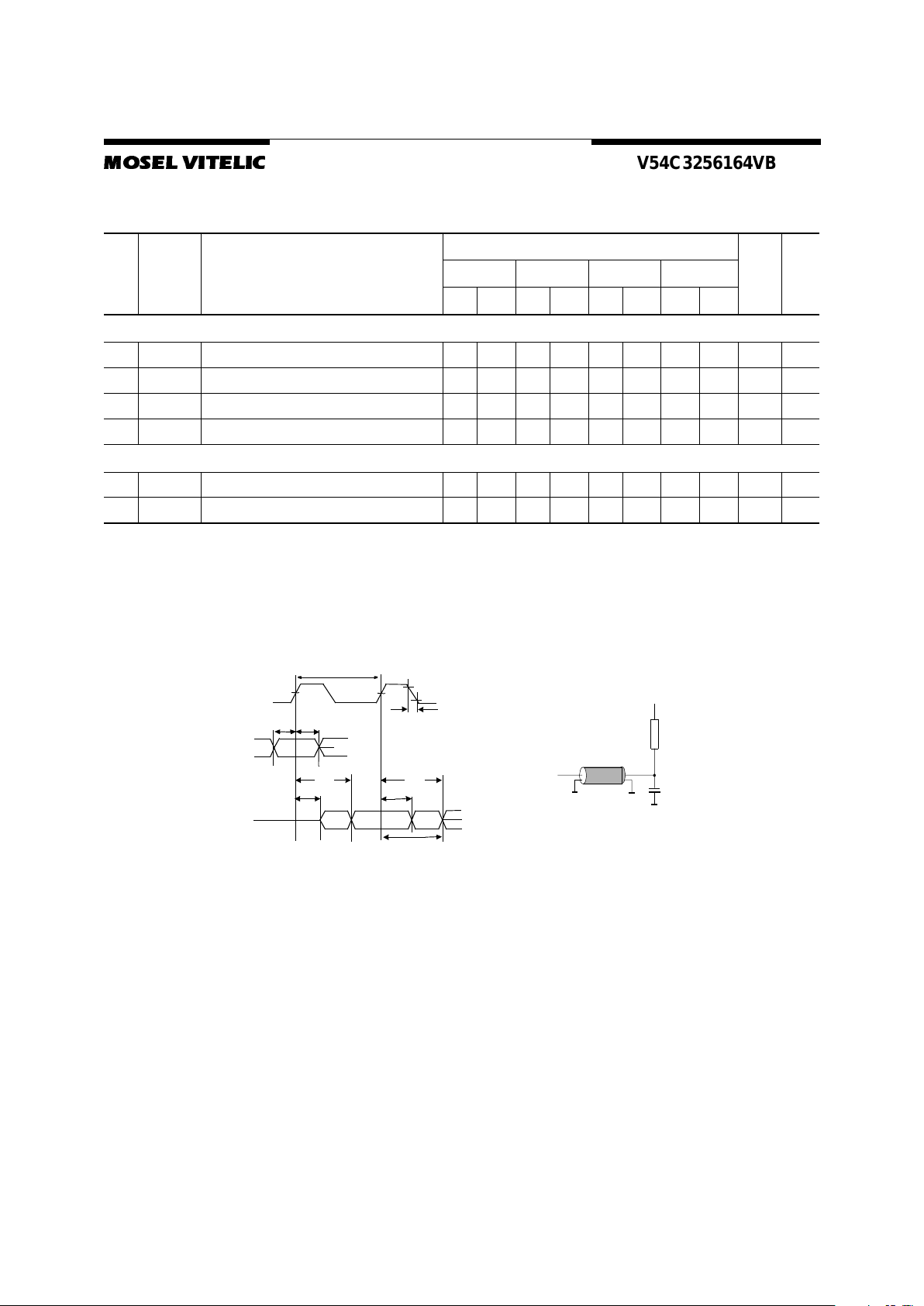

Notes for AC Parameters:

1. For proper power-up see the operation section of this data sheet.

2. AC timing tests have V

IL

= 0.8V and VIH = 2.0V with the timi ng refere nced to the 1.4 V cr ossover poi nt. The tr ansition

time is measure d between V

IH

and VIL. All AC measur ements assume t

T

= 1ns with the AC ou tput load ci rcuit sho wn

in Figure 1.

4. If clock rising time is longer than 1 ns, a time (t

T

/2 – 0.5) ns has to be added to this param eter .

5. If t

T

is longer than 1 ns, a time (t

T

– 1) ns has to be added to this parameter .

6. These parameter account for the number of clock cycle and depend on the operating freque ncy of the clock, as

follows:

the number of clock cyc le = specified value of timing period (counte d in fr actions as a whole number)

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.

Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command

is registered.

7. Referenced to the time which the output achieves the open circuit condition, not to output vol tage levels

Read Cycle

21 t

OH

Data Out Hold Time 3–3–3–3–ns2

22 t

LZ

Data Out to Low Impedance Time 1–1–1–0–ns

23 t

HZ

Data Out to High Impedance Time 36373738ns7

24 t

DQZ

DQM Data Out Disable Latency – 2 – 2 – 2 – 2 CLK

Write Cycle

25 t

WR

Write Recovery Time 2–2–2– 2 –CLK

26 t

DQW

DQM Write Mask Latency 0 – 0 – 0 – 0 – CLK

# Symbol Parameter

Limit Values

Unit Note

-6 -7PC -7

-8PC

Min. Max. Min. Max. Min. Max. Min. Max.

1.4V

1.4V

tCS tCH

tAC

tAC

tLZ

tOH

tHZ

CLK

COMMAND

OUTPUT

50 pF

I/O

Z=50 Ohm

+ 1.4 V

50 Ohm

VIH

VIL

t

T

Figure 1.

tCK

AC Characteristics (Cont ’d)

14

V54C3256164VBUC/T Rev. 1.1 February 2003

MOSEL VITELIC

V54C3256164VBUC/T

Timing Diagrams

1. Bank Activate Command Cycle

2. Burst Read Operation

3. Read Interrupted by a Read

4. Read to Write Interval

4.1 Read to Write Interval

4.2 Minimum Read to Write Interval

4.3 Non-Minimum Read to Write Interval

5. Burst Write Operation

6. Write and Read Interrupt

6.1 Write Interrupted by a Write

6.2 Write Interrupted by Read

7. Burst Write & Read with Auto-Precharge

7.1 Burst Write with Auto-Precharge

7.2 Burst Read with Auto-Precharge

8. Burst Termination

8.1 Termination of a Burst Write Operation

8.2 Termination of a Burst Write Operation

9. AC- Parameters

9.1 AC Parameters for a Write Timing

9.2 AC Parameters for a Read Timing

10. Mode Register Set

11. Power on Sequence and Auto Refresh (CBR)

12. Power Down Mode

13. Self Refresh (Entry and Exit)

14. Auto Refresh (CBR)

Loading...

Loading...