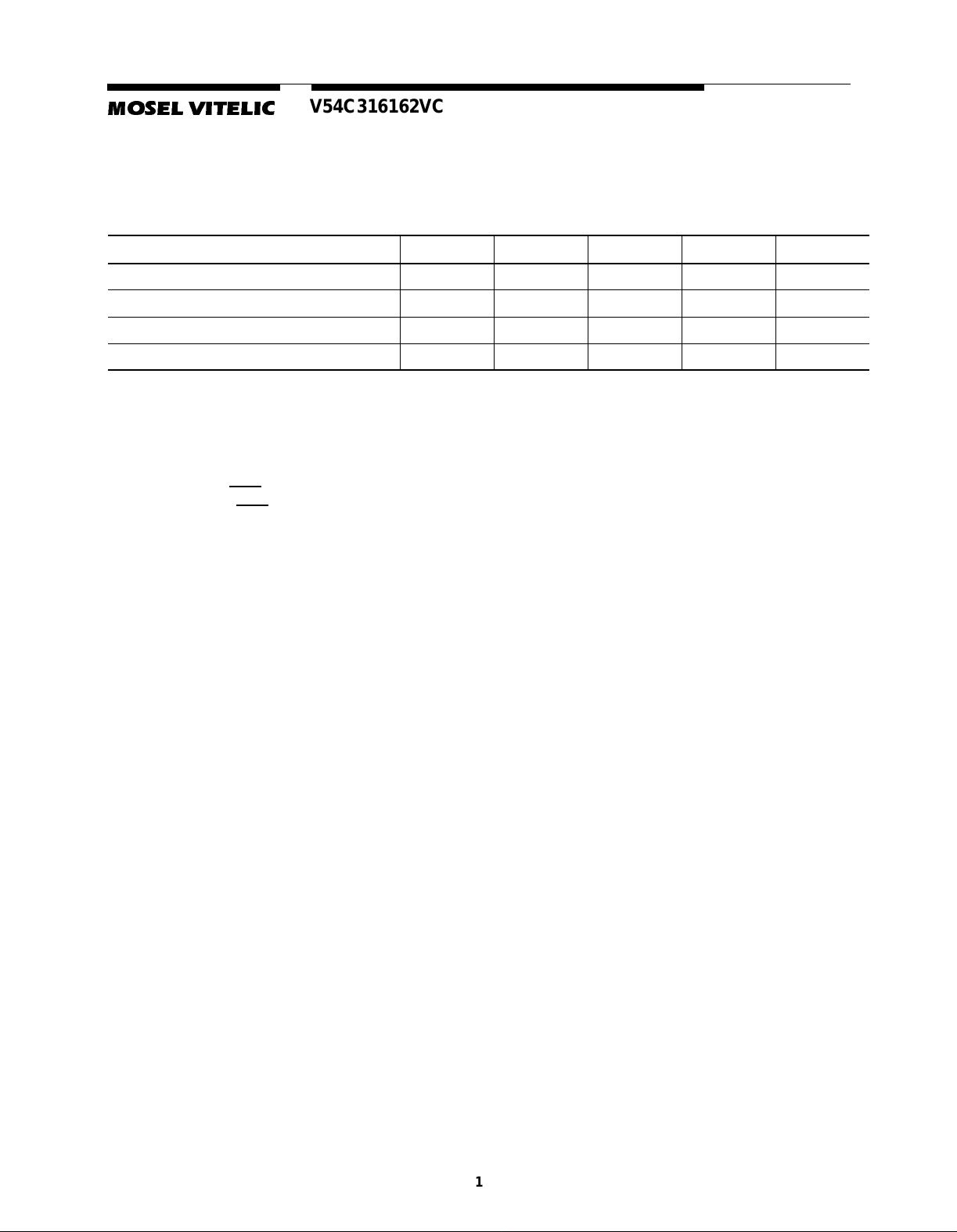

Mosel Vitelic V54C316162VC-7, V54C316162VC-6, V54C316162VC-55, V54C316162VC-5, V54C316162VC Datasheet

MOSEL VITELIC

V54C316162VC

200/183/166/143 MHz 3.3 VOLT, 2K REFRESH

ULTRA HIGH PERFORMANCE

1M X 16 SDRAM 2 BANKS X 512Kbit X 16

V54C316162VC -5 -55 -6 -7 Unit

Clock Frequency (tCK) 200 183 166 143 MHz

Latency 3333clocks

CycleTime(t

Access Time (t

)55.567ns

CK

) 5 5.3 5.5 5.5 ns

AC

Features

■ JEDEC Standard 3.3V Po w er Supply

■ The V54C316162VC is ideally suited for high

performance graphi c s peripheral applica tions

■ Single Pulsed RAS

■ Programmable CAS Latency: 2, 3

■ All Inputs are sampled atthe positive goingedge

of clock

■ Programmable Wrap Sequence: Sequential or

Interleave

■ Programmable B urst Length: 1, 2, 4, 8 and Full

Page for Sequential and 1, 2, 4, 8 for Interleave

■ UDQM & LDQM for byte masking

■ Auto & Self Refresh

■ 2K Refresh Cycles/32 ms

■ Burst Read with Single Write Operat ion

Interface

Description

The V54C316162VC is a 16,777,216 bits synchronous high dat a rate DRAM org anized as 2 x

524,288 words by 16 bits. The device is designed to

comply with JEDEC standards set for synchronous

DRAM products, both electrically and mechanically.

Synchronous design allows precise cycle control

with the system clock. The CAS latency, burst

length and burst sequence must be programmed

into device prior to access operation.

V54C316162VC Rev. 1.4 December 2001

1

MOSEL VITELIC

V54C316162VC

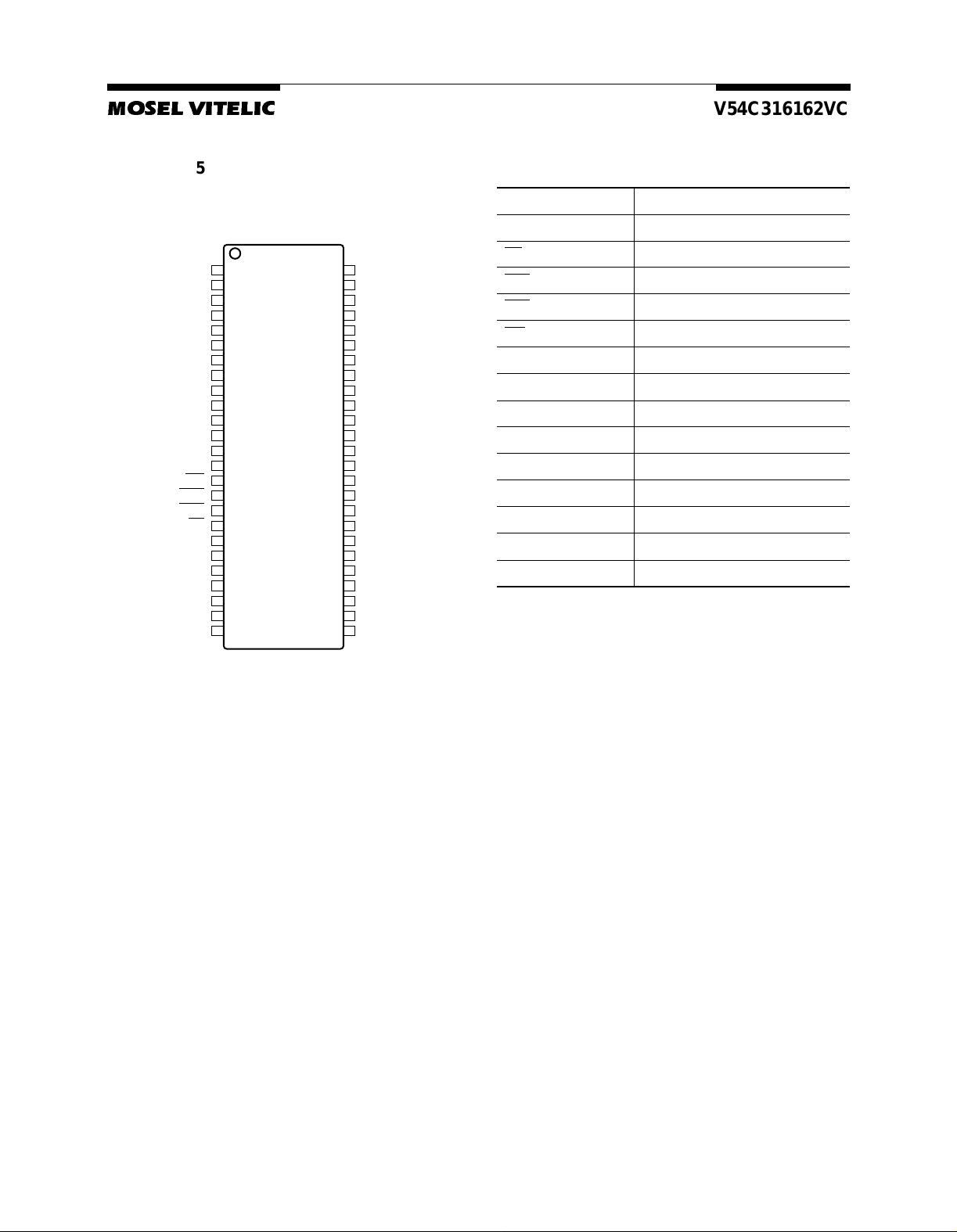

50 Pin Plastic TSOP-II PIN CON FIGURATION

Top View

V

V

SSQ

V

CCQ

V

SSQ

V

CCQ

LDQM

CAS

RAS

V

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

WE

A

CC

CS

BA

A

A

A

A

CC

1

2

1

3

2

4

5

3

6

4

7

8

5

9

6

10

11

7

12

8

13

14

15

16

17

18

19

20

10

21

0

22

1

23

2

24

3

25

V54C316162V-01

Pin Names

CLK Clock Input

CKE Clock Enable

CS

V

50

SS

I/O

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

16

I/O

15

V

SSQ

I/O

14

I/O

13

V

CCQ

I/O

12

I/O

11

V

SSQ

I/O

10

I/O

9

V

CCQ

NC

UDQM

CLK

CKE

NC

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

RAS

CAS

WE

A

0–A10

BA Bank Select

I/O

–I/O

1

16

LDQM, UDQM Data Mask

V

CC

V

SS

V

CCQ

V

SSQ

NC Not connected

Chip Select

Row Address Strobe

ColumnAddress Strobe

Write Enable

AddressInputs

Data Input/Output

Power(+3.3V)

Ground

Power for I/O’s (+3.3V)

Ground for I/O’s

V54C316162VC Rev. 1.4 December 2001

2

MOSEL VITELIC

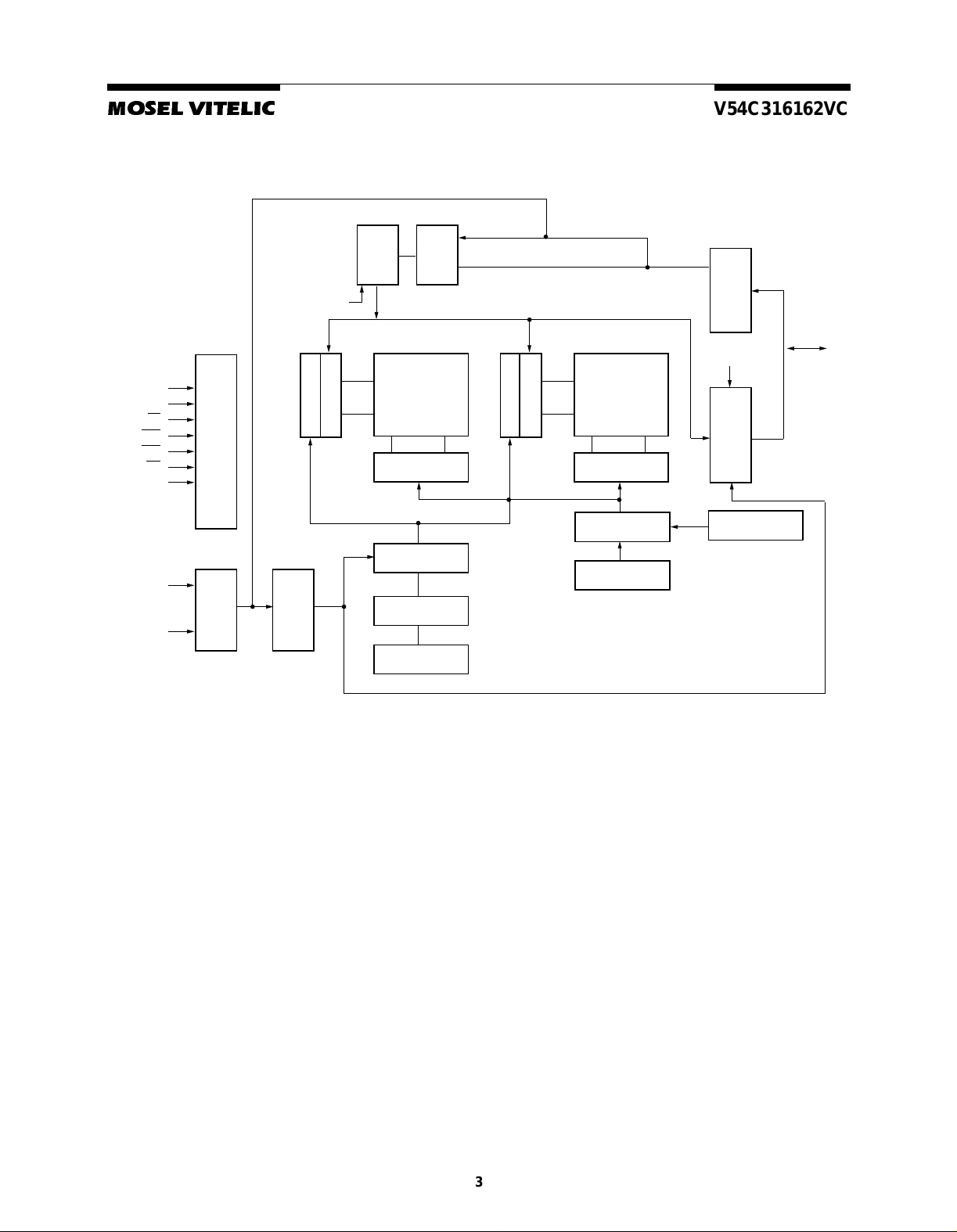

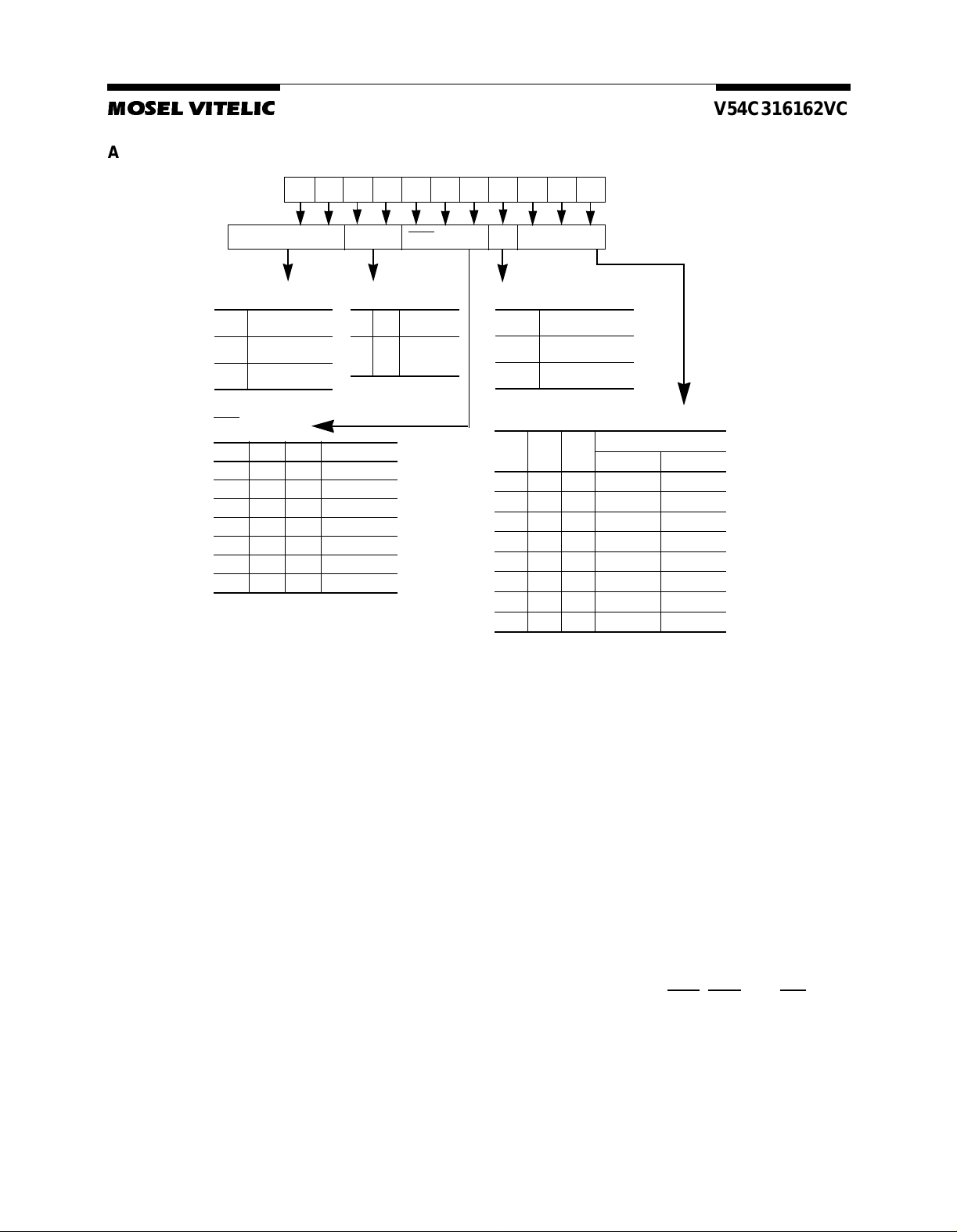

Block Diagram

V54C316162VC

CLK

CKE

CS

RAS

CAS

WE

DQMi

CLK

Address

Timing

Register

Register

Programming

DQMi

Sense Amplifier

Column Decoder

Latency 8

Burst Length

Write

Control

Logic

Memory Array

Bank 0

512k x 16

Row

Decoder

Column Address

Counter

Column Address

Buffer

A0-A7, BA

Column Addresses

MUX

Sense Amplifier

Column Decoder

Memory Array

Bank 1

512k x 16

Row

Decoder

Row Address

Buffer

A

, BA

0-A10

Row Addresses

Input

UDQM

LDQM

Output

Buffer

Buffer

Refresh

Counter

I/O

-I/O

1

V54C316162V-02

16

V54C316162VC Rev. 1.4 December 2001

3

MOSEL VITELIC

V54C316162VC

Signal Pin Description

Pin Name Input Function

CLK Clock Input Systemclock input.Activeonthepositiverising edgetosample allinptus

CKE Clock Enable Activates the CLK signal when high and deactivatesthe CLK when low.

CKE low initiates the power down mode, suspend mode, or the self

refresh mode

CS

Chip Select Disables or enablesdeviceoperation by maskingor enablingall inputs

except CLK, CKE and DQMi

RAS

Row Address Strobe Latches row addresses on the positive edge of CLK with RAS low.

Enablesrow access & precharge

CAS

Column Address Strobe Latches column addresses on the positive edge of CLK with CAS low.

Enablescolumnaccess

WE

A

0-A10

WriteEnable Enableswriteoperation

Address During a bank activate command, A0-A10defines the row address.

During a read or write command, A

addition to the column addressA

define the bank to be precharged. A

duringa precharge cycle, If A

if A

is low, the BA is used to decide which bank to precharge. If A10is

10

10

defines the column address. In

0-A7

isused to invokeautoprechargeBA

10

islow, autoprechargeis disabled

10

is high, both bank will be precharged ,

high, all banks will be precharged.

BA Bank Select Selectswhichbank to activate. BA low select bank A and high selects

bank B

I/O

1

-I/O

16

Data Input/Output Data inputs/output are multiplexed on the same pins

UDQM, LDQM Data Input/Output Mask Makes data output Hi-Z. Blocks data input when DQM is active

VDD/VSS Power Supply/Ground Power Supply. +3.3V ± 0.3V/ground

VDDQ/VSSQ Data Output Power/Ground Provides isolated power/groundto DQs for improvednoiseimmunity

NC No Connection

V54C316162VC Rev. 1.4 December 2001

4

MOSEL VITELIC

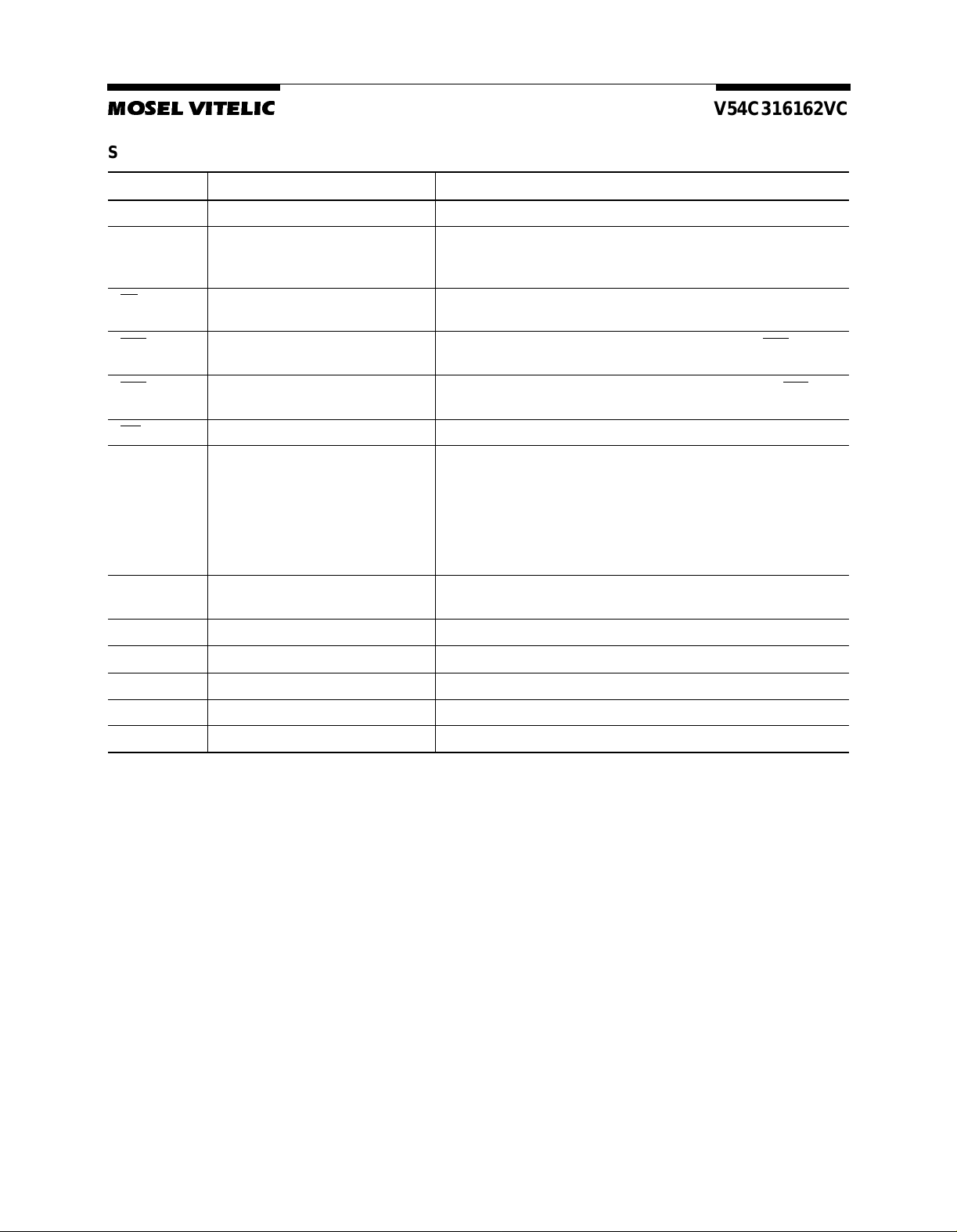

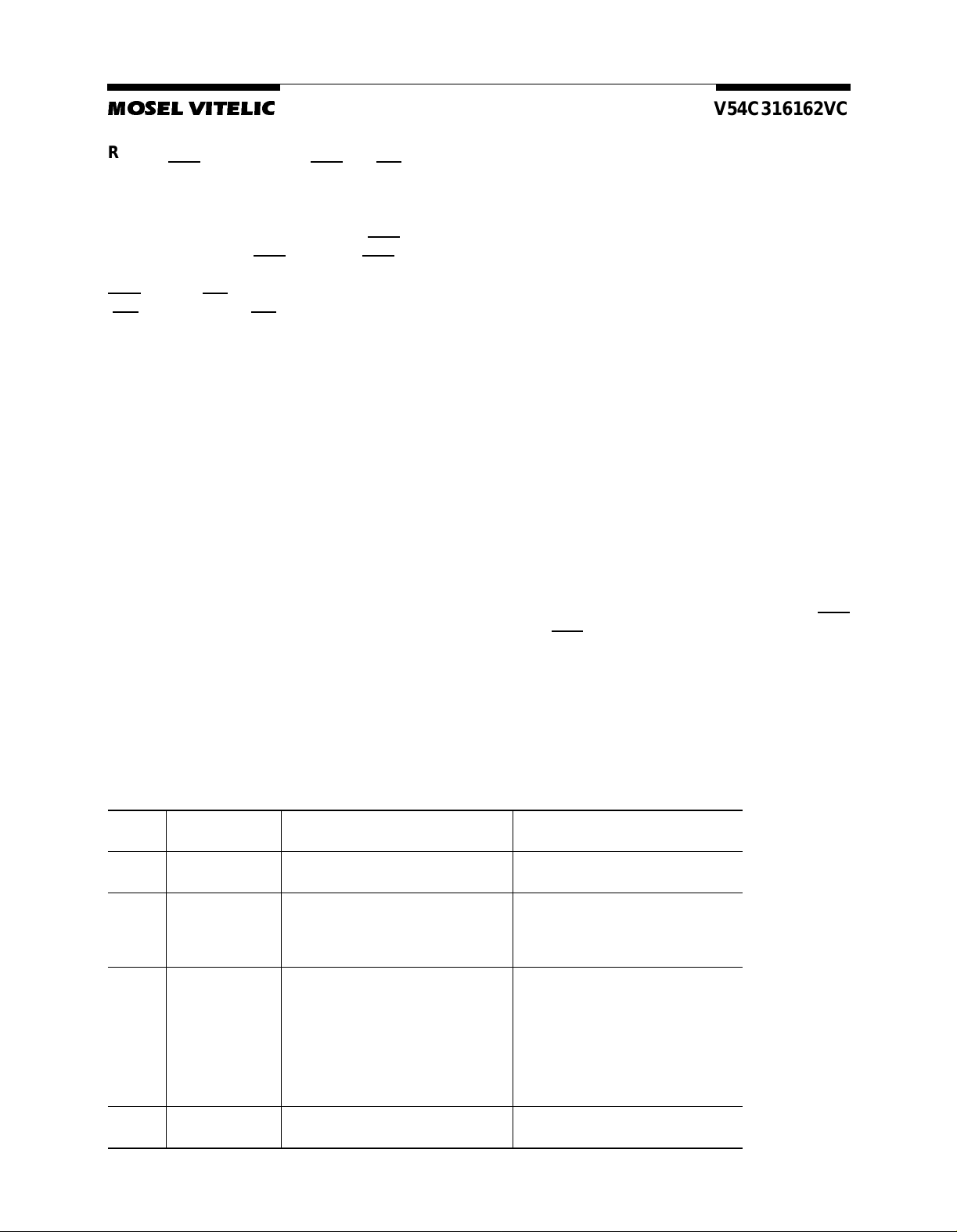

Address Input for Mode Set (Mode Re gister Operation)

V54C316162VC

A10

A9

A8 A7 A6 A5

Write Burst Length

Write Burst Length

A9 Length

0Burst

1 Single Bit

CAS Latency

A6 A5 A4 Latency

000 Reserve

001 Reserve

010 2

011 3

101 Reserve

110 Reserve

111 Reserve

Test

Mode

Test Mode

A8 A7 Mode

00

Mode Reg

Set

A3A4 A2 A1 A0

BT Burst LengthCAS Latency

Burst Type

A3 Type

0 Sequential

1 Interleave

Burst Length

A2 A1 A0

000 1 1

001 2 2

010 4 4

011 8 8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

1 1 1 Full Page Reserve

Address Bus (Ax)

Mode Register

Length

Sequential Interleave

Power O n and Initialization

The default power on state of t he mode register is

supplier specific and may be undefined. The

following power on and initialization sequence

guarantees the device is preconditioned to each

users specific needs. Like a convent ional DRAM,

the Synchronous DRAM must be powered up and

initialized in a predefined manner. During power on,

all VCC and VCCQ pins m ust be built up

simultaneously to the specified v oltage when the

input signals are held in the “NOP” state. The power

on voltage must not exceed VCC+0.3 V on any of

the input pins or VCC supplies. The CLK signal

must be s tarted at the same time. After power on,

an initial pause of 200 µs is required followed by a

precharge of both banks using the precharge

command. To prevent data contention on the DQ

bus during power on, it isrequired that the DQM and

CKE pins be held high during the i nitial pause

period. Once all bank s have been precharged, the

Mode Register Set Command must be issued to

initialize the Mode Register. A mini mum of eight

Auto Refresh cycles (CBR) are also required.These

may be done before or after programming the Mode

Register. Failure to follow these st eps may lead to

unpredictable start-up modes.

Programming the Mode Register

The Mode register designates the operation

mode at the read or write cycle. Th is register is di vided into 4 fields. A Burst Length Field to set the

length of the burst , an A ddres s ing Selection bit to

program the column access sequence in a burst

cycle (interleaved or sequential), a CAS Latency

Fieldto set the access time at clockcycle and a Operation m ode field to differentiate between normal

operation (Burst read and burst Write) and a special

Burst Read and Single Write mode. The m ode set

operation must be done before any activate c ommand after the initial power up. Any content of the

mode register can be altered by re-executing the

mode set command. All banks must be in precharged state and CKE must be high at least one

clock before the mode set operation. After themode

register is set, a Standby or NOP command is

required. Lo w signals of RAS

positive edge of the clock activate the mode set

operation. Address input dat a at this timing defines

parameters tobe set asshown in the previous table.

,CAS, and WE at the

V54C316162VC Rev. 1.4 December 2001

5

MOSEL VITELIC

V54C316162VC

Read and Write Operation

When RAS is low and both CAS an d WE are high

at the positive edge of the clock, a RAS cycle starts.

According to address data, a word line of the s elected bank is activated and all of sense amplifiers associated to the wordline are set. A CAS

triggered by s et ting RAS

high and CAS low at a

clock timing after a neces s ary delay, t

RAS

timing. W E is us ed to define either a read

(WE

=H)orawrite(WE= L ) at this stage.

SDRAM provides a wide variety of fast access

modes. In a single CAS cycle, serial data read or

write operations are allowed at up to a 166 MHz

data rat e. The numbers of serial data bits are the

burst lengthprogram meda t the mode set operation,

i.e., one of 1, 2, 4, 8 and full page. Column addresses are segmented by the burst length and serial

data accesses are done within this boundary. The

first column address to be accessed is s upplied at

the CAS timing and the subsequent addresses are

generated automatically by the programmed burst

length and its sequence. For example, in a burst

length of 8 w ith interleave sequence, if the first address is ‘2’, t hen the rest of the burst sequence is 3,

0, 1, 6, 7, 4, and 5.

Full page burst operation is only possible using

the sequential burst type and page length is a function of the I/O organi sation and column addressing.

Full page burst operation do not self terminate once

the burst length has been reached. In other words,

unlike burst l ength of 2, 4 or 8, full page burst continues until it is terminated using another command.

,fromthe

RCD

cycle is

Similar t o the page mode of conventional

DRAM’s, burst read or write accesses on any column address a re possible once the RAS cycle

latches the sense amplifiers. The maximu m t

RAS

or

therefresh interval time limits t he number of random

column accesses. A new burs t access can be done

even before the previous b urst ends. The interrupt

operation a t every c lock cycles is supported. When

the previous burs t is interrupted, the remaining addresses are overridden by the new address with the

full burst length. An interrupt which accompanies

with an operation change from a read t o a write is

possible by exploiting DQM to av oid bus contention.

When two or more banks are activated

sequentially, interleaved bank read or write

operations are possible. With the programmed

burst length, alternate access and precharge

operations on t w o or more banks can realize f as t

serial data access modes among many different

pages. Once two or more banks are activated,

column to c olum n interleave operation can be done

between different pages.

Refresh Mode

SDRAM has two refresh modes, Auto Refresh

and S elf Ref r es h. Auto Refresh is similar tothe CAS

-before-RAS refresh of conventional DRAMs. All of

banks must be precharged before applying any refresh m ode. Anon-chip address counter increments

the wordand the bank addresses and no bank information is required for both refres h modes.

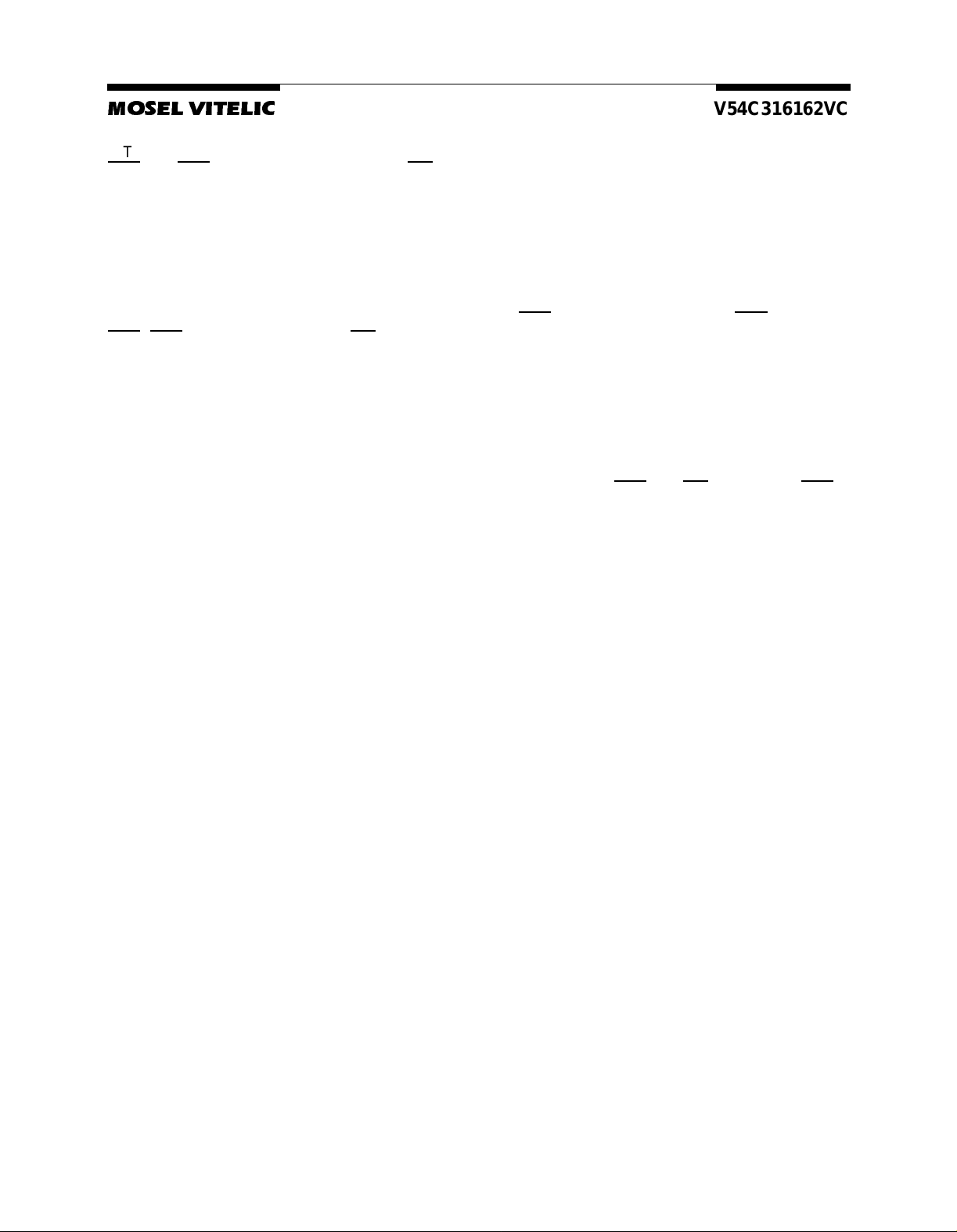

Burst Length and Sequence:

Burst

Length

Page

V54C316162VC Rev. 1.4 December 2001

Starting Address

(A2 A1 A0)

2 xx0

xx1

4x00

x01

x10

x11

8 000

001

010

011

100

101

110

111

Full

nnn Cn, Cn+1, Cn+2,..... not supported

Sequential Burst Addressing

(decimal)

0 1 2 3 4 5 6 7

1 2 3 4 5 6 7 0

2 3 4 5 6 7 0 1

3 4 5 6 7 0 1 2

4 5 6 7 0 1 2 3

5 6 7 0 1 2 3 4

6 7 0 1 2 3 4 5

7 0 1 2 3 4 5 6

0, 1

1, 0

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

Interleave Bur st Addressing

(decimal)

0, 1

1, 0

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

0 1 2 3 4 5 6 7

1 0 3 2 5 4 7 6

2 3 0 1 6 7 4 5

3 2 1 0 7 6 5 4

4 5 6 7 0 1 2 3

5 4 7 6 1 0 3 2

6 7 4 5 2 3 0 1

7 6 5 4 3 2 1 0

6

MOSEL VITELIC

V54C316162VC

The chip enters the Auto Refresh mode, when

RAS

and CAS are held low a nd CKE and WE are

held high at a clock timing. The mode restores word

line after the refresh and no external precharge

command is necess ary . A m inimum tRC time is required between t wo automatic refreshes in a burst

refresh mode. The same rule applies to any access

command after the automatic refres h operation.

The chi p has an on-chip timer and the Self Refresh mode is available. It enters the mode when

RAS

,CAS, and CKE are low and WE is high at a

clock timing. All of external control signals including

the clock are disabled. Returning CKE to high enables the clock and initiates th e refresh exit operation. After the exit command, at least one t

RC

delay

is required prior to any access command.

DQM Function

DQM has two functions for data I/O read a nd

write operations. During reads, when it turns to

“high” at a clock tim ing, data outputs are disabled

and become high impedance after two clock delay

(DQM Data Disable Latency t

). It also provides

DQZ

a d ata mask function for writes. When DQM is activated, the w rite operation at the next clockis prohibited (DQM Write Mask Latencyt

= zero clocks).

DQW

DQM is used for device selection, byte selection

and bus control in a memory system. LDQM controls DQ0 to DQ7, UDQM controls DQ8 to DQ15.

Suspend Mode

Duringnormala ccess mode, CKE is held high enabling the clock. W hen CKE is low, it freezes the internal clock and extends data read and write

operations. One clock delay is required for mode

entry and exit (Clock Suspend L aten cy t

CSL

).

Power Down

In order to reduce standby po wer c onsumption, a

power down mode is available. All banks must be

precharged and the neces s ary Precharge delay

(trp) must occur bef ore the SDRAM can enter the

Power Down mo de. Once the Power Down mode is

initiated by holding CKE low, all of the receiver circuits except CLK andCKE are gated off. The Power

Down mode does not perform any refresh operations, therefore the device can’t remain in P ower

Down mode longer th an the Refresh period (tref) of

the device. Exit from this mode is p erformed by taking CKE “high”. One clock delay is required for

mode ent ry and exit.

Auto Precharge

Two methods are available to precharge

SDRAMs. In an automatic precharge mode, the

CAS timing accepts one extra address, A

, to de-

10

termine whether t he chip restores or not after the

operation. If A

is high when a Read Command is

10

issued, the Read with Au to-Precharge function is

initiated. The SDRAM automatically enters the precharge operation one clock before the last data out

for CAS

If A

latencies2, two clocks for CAS latencies 3.

is high wh en a Write Command is i ssue d, the

10

Write with Auto-Precharge function is initiated.

The SDRAM aut omatically enters the precharge operation a time delay equal to t

(Write recovery

WR

time) after the last data in.

Precharge Command

There is also a separate precharge command

available. When RAS

and WE are low and CAS is

high at a clock timing, it triggers the precharge operation. With A

being low, the BA is used select

10

bank toprecharge. The precharge command c an be

imposed one clock before the last data out for CAS

latency = 2, two clock s before the last data out for

CAS latency = 3. Writes require a time delay twr

from the last data out to apply the precharge c ommand. If A

is high, all banks will be precharged.

10

Burst Termination

Once a burst read or write operation has been initiated, there are several methods in which to terminate the burst operation prematurely. These

methods include using another Read or Write Command to interrupt an existing burst operation, u se a

Precharge Command to interrupt a burst cycle and

close the active bank, or using the B urs t Stop Command to terminate the existing burst operation but

leave the bank open for future Read or Write Commands to t he sam e page of the active bank. When

interrupting a burst with another Read or Write

Command care must be taken to avoid I/O contention. The Burst Stop Command, however, has the

fewest restrictions making it the easiest method to

use when terminatinga burst operation before i t has

been completed. If a Burst Stop command is issued

during a bu rst write operation, then any residual

data from the burst write cycle will be ignored. Data

that is presented on the I/O pins before the Burst

Stop Command is registered will be written to the

memory.

V54C316162VC Rev. 1.4 December 2001

7

Loading...

Loading...