Mosel Vitelic V53C517405A-60T, V53C517405A-60K, V53C517405A-50T, V53C517405A-50K Datasheet

MOSEL VITELIC

1

V53C517405A

4M X 4 EDO PAGE MODE

CMOS DYNAMIC RAM

V53C517405A Rev. 1.1 March 1998

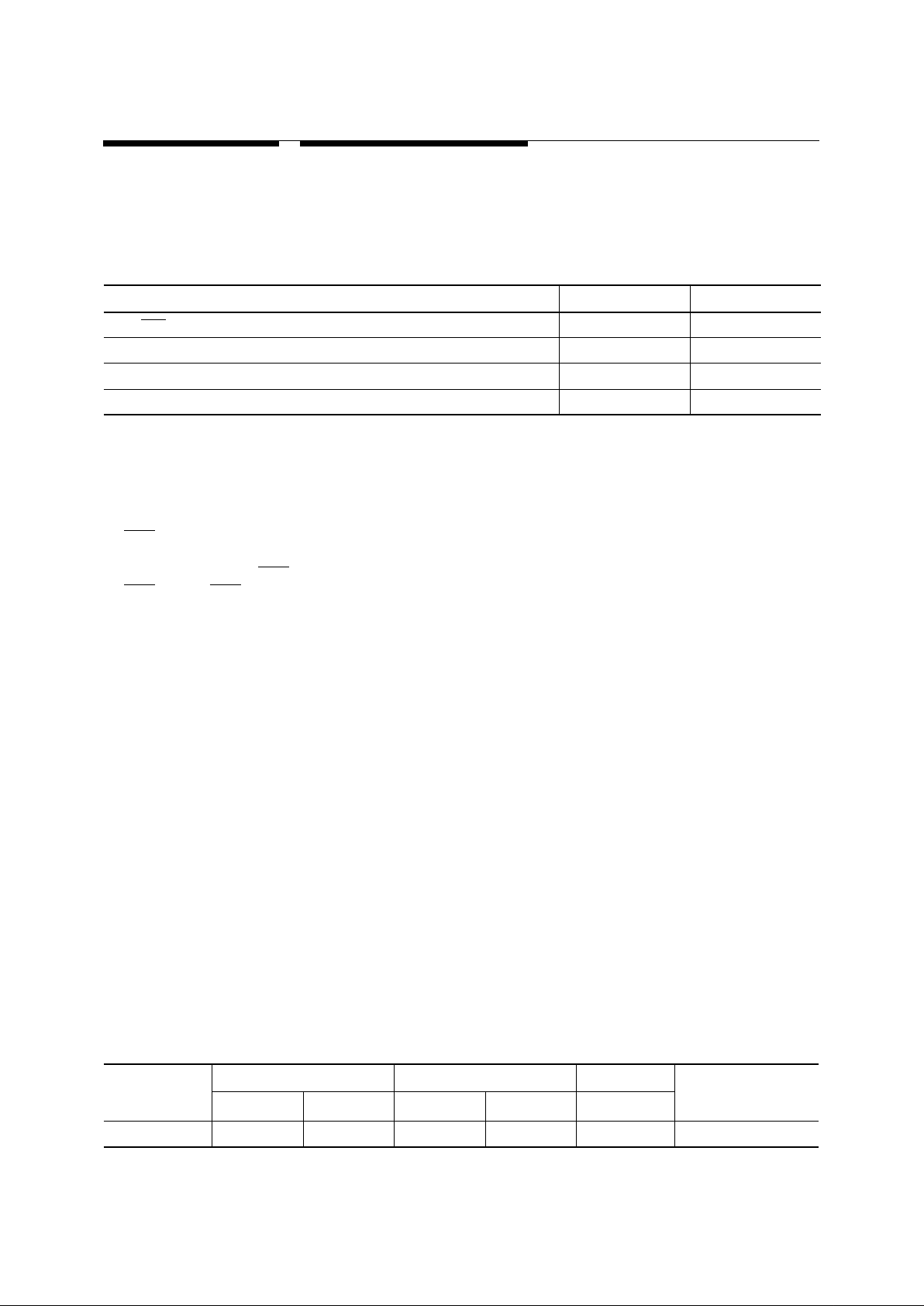

V53C517405A 50 60

Max. RAS

Access Time, (t

RAC

) 50 ns 60 ns

Max. Column Address Access Time, (t

CAA

) 25 ns 30 ns

Min. Extended Data Out Page Mode Cycle Time, (t

PC

) 20 ns 25 ns

Min. Read/Write Cycle Time, (t

RC

) 84 ns 104 ns

Features

■

4M x 4-bit organization

■

EDO Page Mode for a sustained data rate

of 50 MHz

■

RAS

access time: 50, 60, 70 ns

■

Low power dissipation

■

Read-Modify-Write, RAS-Only Refresh,

CAS

-Before-RAS Refresh, Hidden Refresh

■

Refresh Interval: 2048 cycles/32 ms

■

Available in 24/26-pin 300 mil SOJ,

and 24/26-pin 300 mil TSOP-II

■

Single +5 V ± 10% Power Supply

■

TTL Interface

Description

The V53C517405A is a 4,194,304 x 4 bit highperformance CMOS dynamic random access

memory. The V53C517405A offers Page mode

operation with Extended Data Output. The

V53C517405A has a symmetric address, 11-bit row

and 11-bit column.

All inputs are TTL compatible. EDO Page Mode

operation allows random access up to 2048 x 4 bits,

within a page, with cycle times as short as 20ns.

These features make the V53C517405A ideally

suited for a wide variety of high performance

computer systems and peripheral applications.

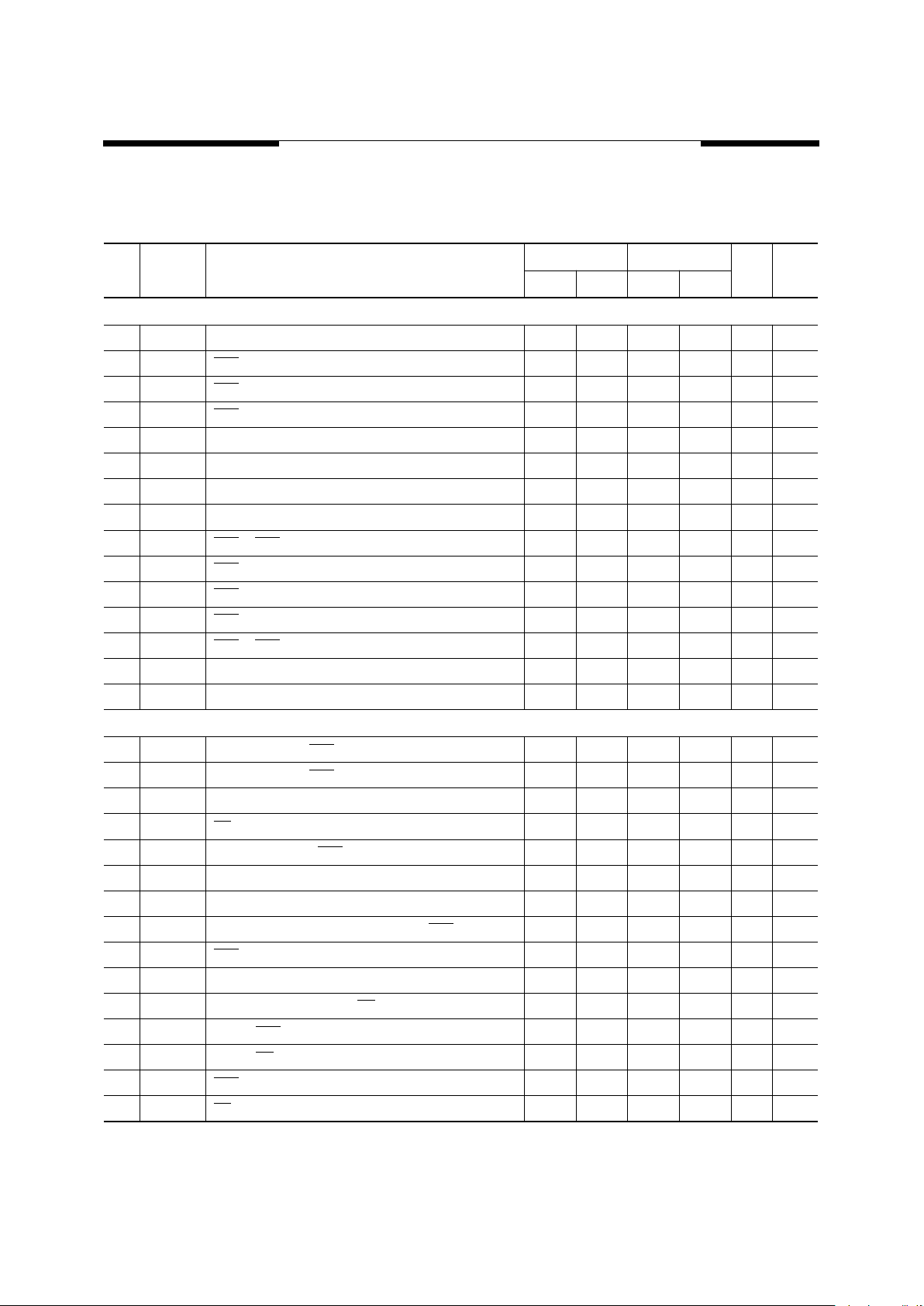

Device Usage Chart

Operating

Temperature

Range

Package Outline Access Time (ns) Power

Temperature

MarkK T 50 60 Std.

0 °

C to 70 ° C•••• • Blank

2

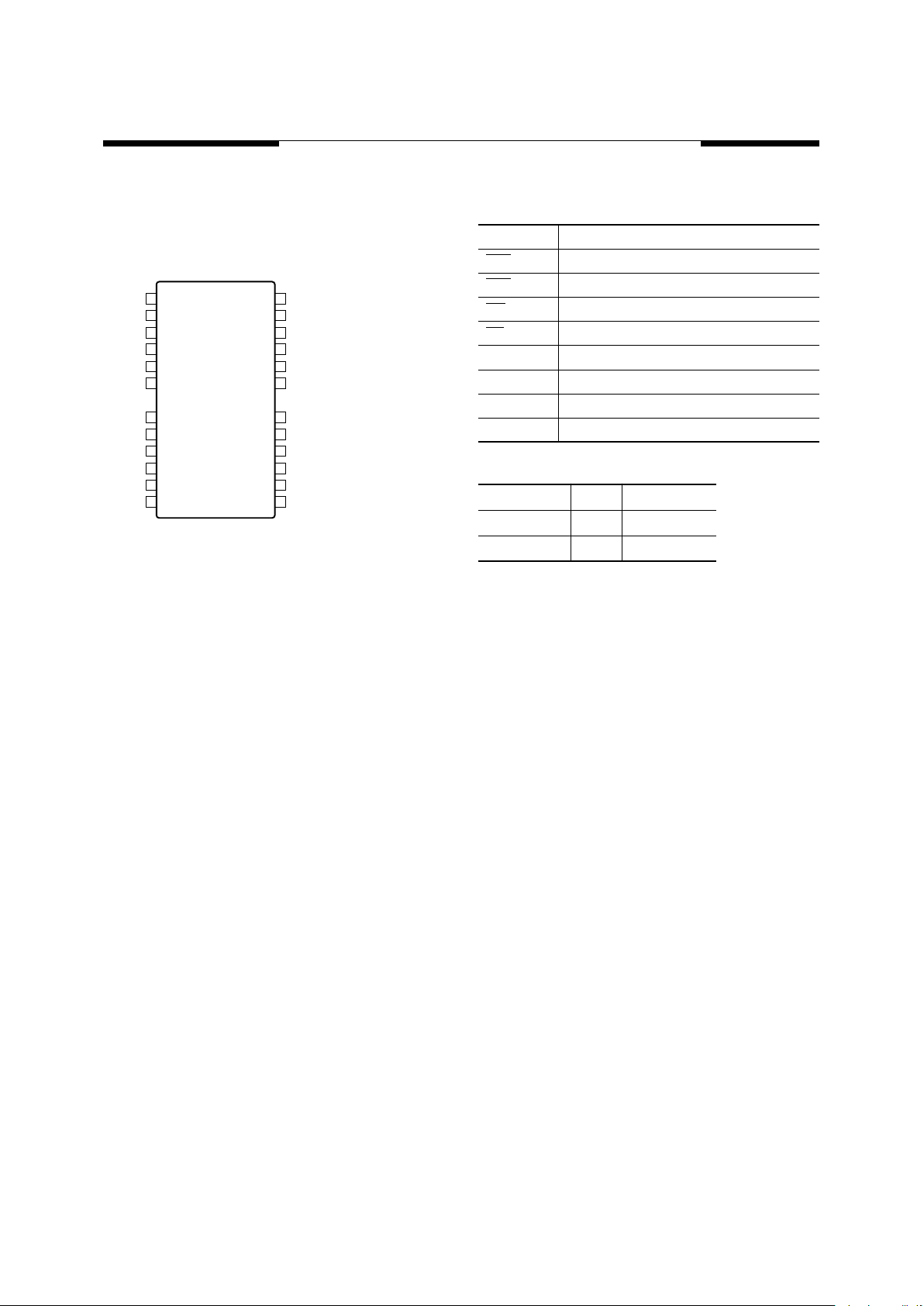

MOSEL VITELIC

V53C517405A

V53C517405A Rev. 1.1 March 1998

V

CC

I/O

1

I/O

2

WE

RAS

NC

A

10

A

0

A

1

A

2

A

3

V

CC

V

SS

I/O

4

I/O

3

CAS

OE

A

9

A

8

A

7

A

6

A

5

A

4

V

SS

5

6

8

9

10

11

12

1

2

3

4

24

23

22

21

19

18

17

16

15

13 14

511740502-02

26

25

Pin Names

A

0

–A

10

Row, Column Address Inputs

RAS Row Address Strobe

CAS Column Address Strobe

WE Write Enable

OE Output Enable

I/O

1

–I/O

4

Data Input, Output

V

CC

+5V Supply

V

SS

0V Supply

NC No Connect

Description Pkg. Pin Count

SOJ K 24/26

TSOP-II T 24/26

24/26 Pin Plastic SOJ /TSOP-II

PIN CONFIGURATION

Top View

MOSEL VITELIC

V53C517405A

3

V53C517405A Rev. 1.1 March 1998

Absolute Maximum Ratings*

Operating temperature range ..................0 to 70 ° C

Storage temperature range ............... -55 to 150 ° C

Input/output voltage.......-0.5 to min (V

CC

+0.5, 7) V

Power supply voltage ............................-1.0V to 7V

Power dissipation .......................................... 1.0 W

Data out current (short circuit)......................50 mA

*

Note: Operation above Absolute Maximum Ratings can

adversely affect device reliability.

Capacitance*

T

A

= 25 ° C, V

CC

= 5 V ± 10%, V

SS

= 0 V, f = 1 MHz

*Note: Capacitance is sampled and not 100% tested.

Symbol Parameter Min. Max. Unit

C

IN1

Address Input — 5 pF

C

IN2

RAS

, CAS, WE, OE — 7 pF

C

OUT

Data Input/Output — 7 pF

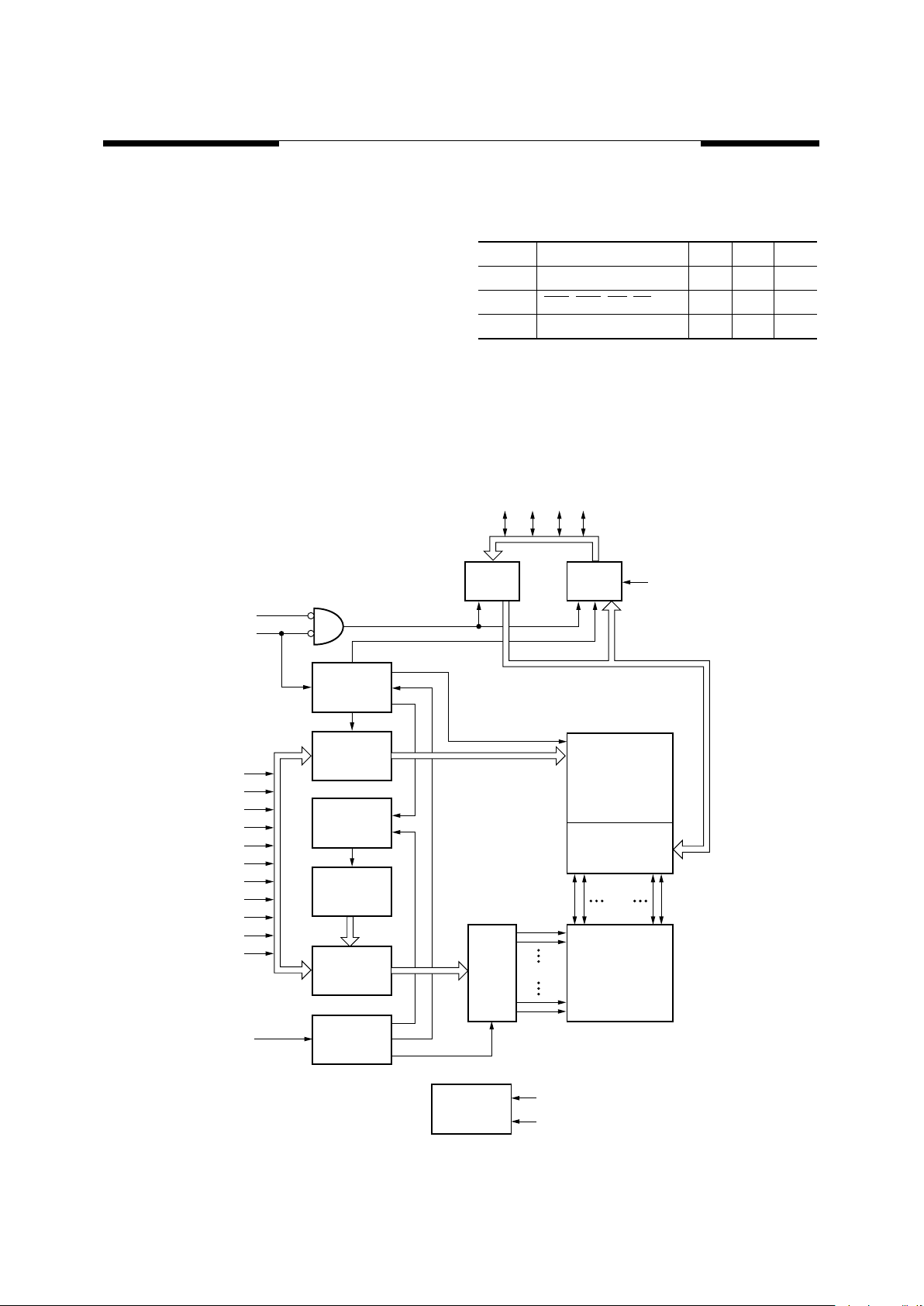

Block Diagram

No. 2 Clock

Generator

Data In

Buffer

Data Out

Buffer

Column

Address

Buffers (11)

Refresh

Controller

Row

Decoder

Refresh

Counter (11)

No. 1 Clock

Generator

Voltage Down

Generator

Row

Address

Buffers (11)

11

4

I/O1 I/O2 I/O3 I/O4

4

OE

11

11 11

4

2048

VCC

VCC (internal)

2048

x4

Memory Array

2048 x 2048 x 4

Sense Amplifier

I/O Gating

Column

Decoder

A0

CAS

WE

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

RAS

11

511740500-03

4096 x 4

4

V53C517405A Rev. 1.1 March 1998

MOSEL VITELIC

V53C517405A

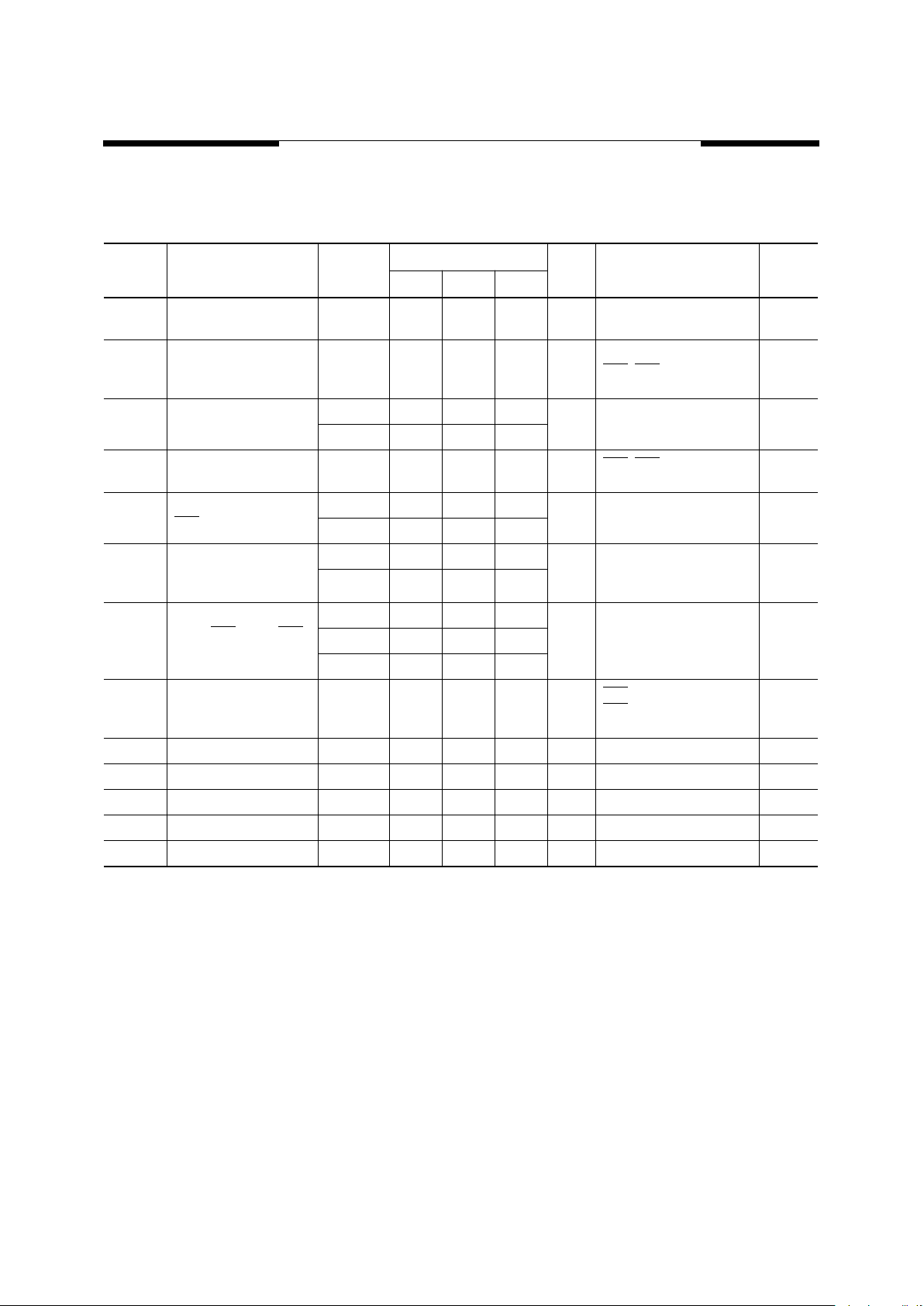

DC and Operating Characteristics

(1-2)

T

A

= 0 ° C to 70 ° C, V

CC

= 5 V ± 10%, V

SS

= 0 V, t

T

= 2ns, unless otherwise specified.

Symbol Parameter

Access

Time

V53C517405A

Unit Test Conditions NotesMin. Typ. Max.

I

LI

Input Leakage Current

(any input pin)

–10 10 µ A V

SS

≤

V

IN

≤

V

CC

+ 0.5V 1

I

LO

Output Leakage Current

(for High-Z State)

–10 10 µ A V

SS

≤

V

OUT

≤

V

CC

+ 0.5V

RAS

, CAS at V

IH

other input ≥ V

SS

1

I

CC1

V

CC

Supply Current,

Operating

50 80 mA t

RC

= t

RC

(min.) 2, 3, 4

60 70

I

CC2

V

CC

Supply Current,

TTL Standby

2 mA RAS

, CAS at V

IH

other inputs ≥ V

SS

I

CC3

V

CC

Supply Current,

RAS

-Only Refresh

50 80 mA t

RC

= t

RC

(min.) 2, 4

60 70

I

CC4

V

CC

Supply Current,

EDO Page Mode

Operation

50 35 mA Minimum Cycle 2, 3, 4

60 30

I

CC5

V

CC

Supply Current,

during CAS

-before-RAS

Refresh

50 120 mA 2, 4

60 110

70 100

I

CC6

V

CC

Supply Current,

CMOS Standby

1.0 mA RAS

≥ V

CC

– 0.2 V,

CAS

≥ V

CC

– 0.2 V

other input ≥ V

SS

1

V

CC

Power Supply Voltage 4.5 5.0 5.5 V

V

IL

Input Low Voltage –0.5 0.8 V 1

V

IH

Input High Voltage 2.4 V

CC

+0.5 V 1

V

OL

Output Low Voltage 0.4 V I

OL

= 4.2 mA 1

V

OH

Output High Voltage 2.4 V I

OH

= –5 mA 1

5

MOSEL VITELIC

V53C517405A

V53C517405A Rev. 1.1 March 1998

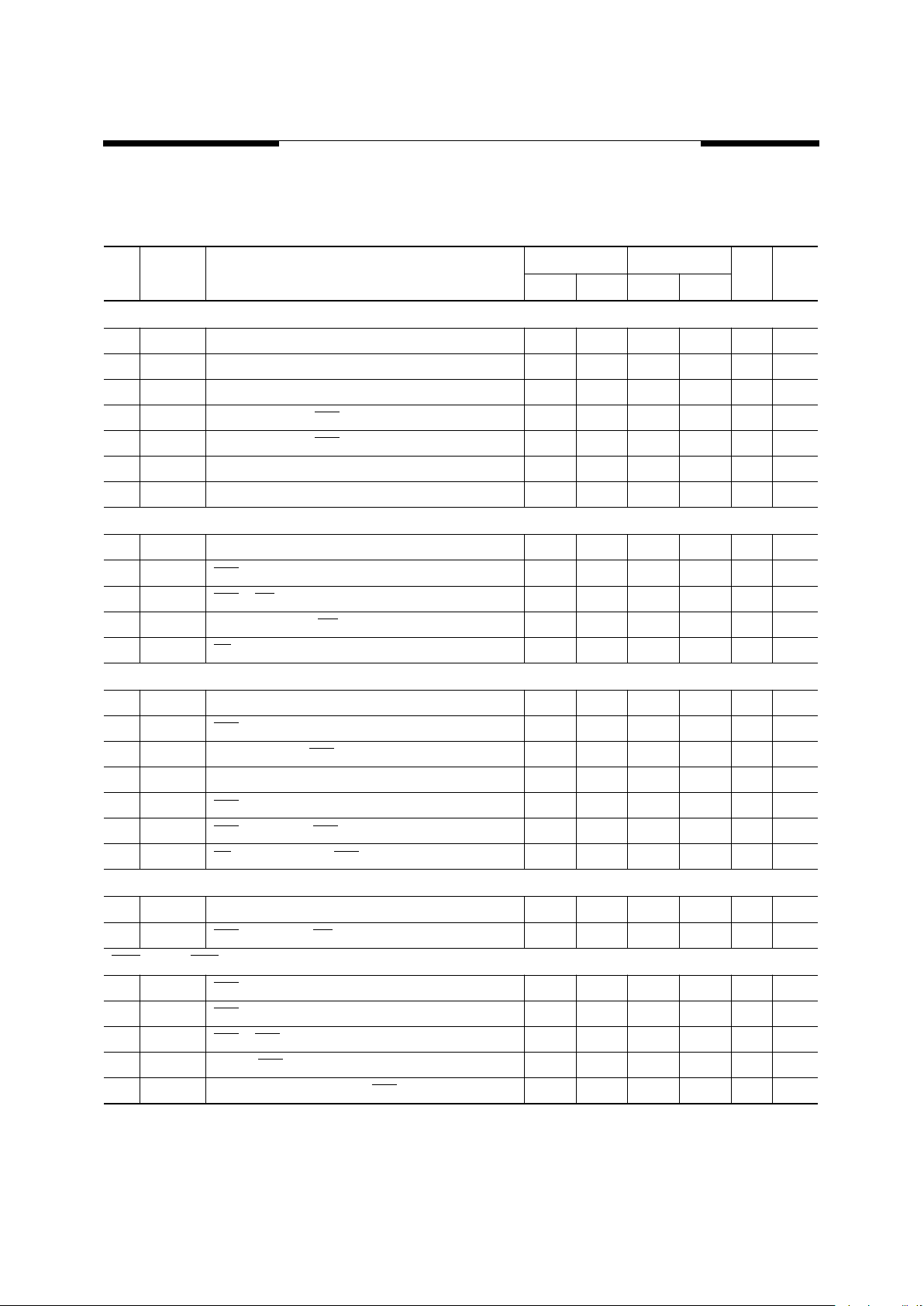

AC Characteristics

(5, 6)

T

A

= 0 to 70 ˚C,V

CC

= 5 V ± 10 %, t

T

= 2 ns

# Symbol Parameter

-50 -60

Unit Notemin. max. min. max.

Common Parameters

1 t

RC

Random read or write cycle time 84 – 104 – ns

2 t

RP

RAS

precharge time 30 – 40 – ns

3 t

RAS

RAS pulse width 50 10k 60 10k ns

4 t

CAS

CAS pulse width 8 10k 10 10k ns

5 t

ASR

Row address setup time 0 – 0 – ns

6 t

RAH

Row address hold time 8 – 10 – ns

7 t

ASC

Column address setup time 0 – 0 – ns

8 t

CAH

Column address hold time 8 – 10 – ns

9 t

RCD

RAS to CAS delay time 12 37 14 45 ns

10 t

RAD

RAS to column address delay 10 25 12 30 ns

11 t

RSH

RAS hold time 13 15 – ns

12 t

CSH

CAS hold time 40 50 – ns

13 t

CRP

CAS to RAS precharge time 5 – 5 – ns

14 t

T

Transition time (rise and fall) 1 50 1 50 ns 7

15 t

REF

Refresh period – 32 – 32 ms

Read Cycle

16 t

RAC

Access time from RAS – 50 – 60 ns 8, 9

17 t

CAC

Access time from CAS – 13 – 15 ns 8, 9

18 t

CAA

Access time from column address – 25 – 30 ns 8,10

19 t

OEA

OE access time – 13 – 15 ns

20 t

RAL

Column address to RAS lead time 25 – 30 – ns

21 t

RCS

Read command setup time 0 – 0 – ns

22 t

RCH

Read command hold time 0 – 0 – ns 11

23 t

RRH

Read command hold time referenced to RAS 0 – 0 – ns 11

24 t

CLZ

CAS to output in low-Z 0 – 0 – ns 8

25 t

OFF

Output buffer turn-off delay 0 13 0 15 ns 12

26 t

OEZ

Output turn-off delay from OE 0 13 0 15 ns 12

27 t

DZC

Data to CAS low delay 0 – 0 – ns 13

28 t

DZO

Data to OE low delay 0 – 0 – ns 13

29 t

CDD

CAS high to data delay 10 – 13 – ns 14

30 t

ODD

OE high to data delay 10 – 13 – ns 14

6

V53C517405A Rev. 1.1 March 1998

MOSEL VITELIC

V53C517405A

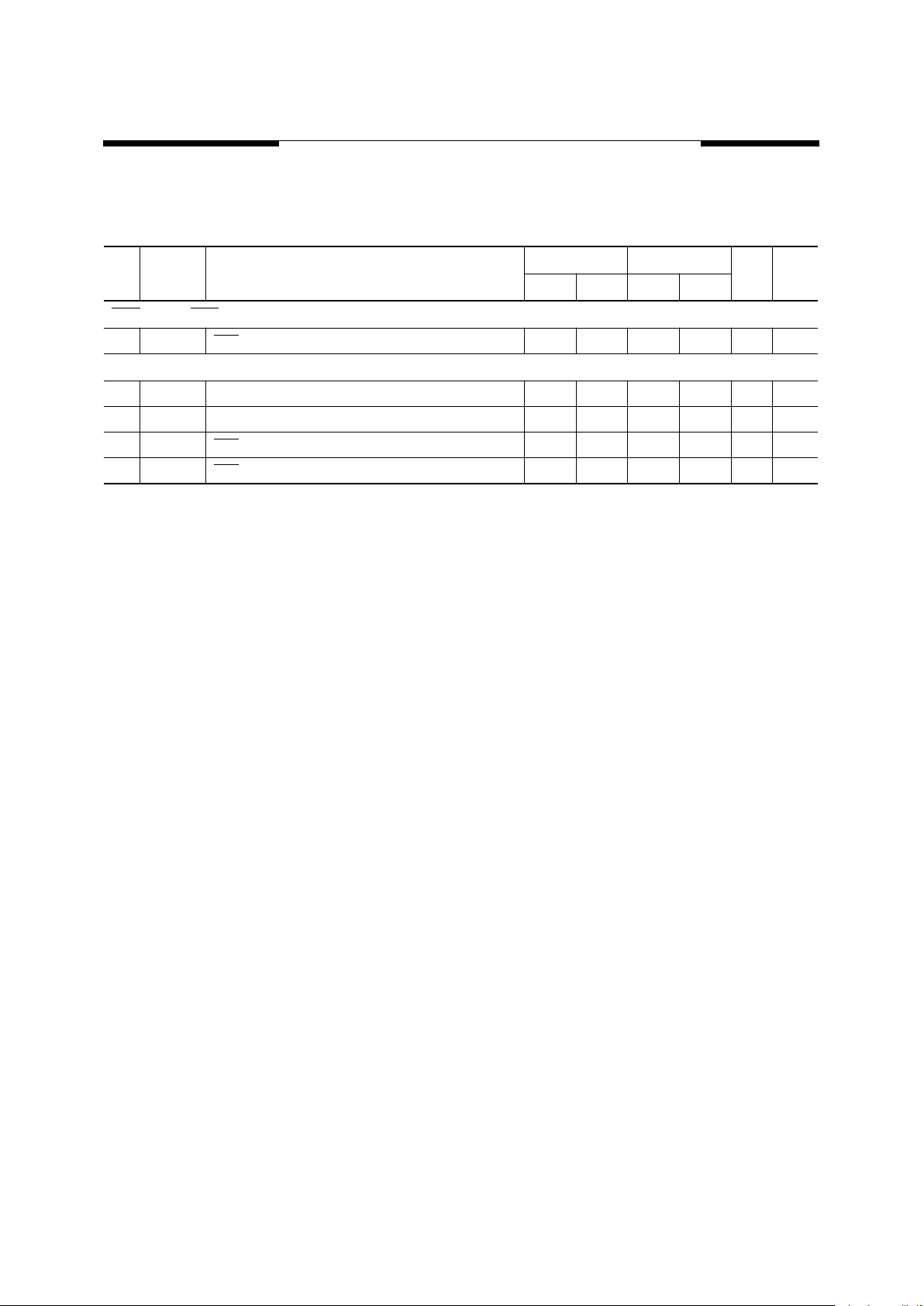

Write Cycle

31 t

WCH

Write command hold time 8 – 10 – ns

32 t

WP

Write command pulse width 8 – 10 – ns

33 t

WCS

Write command setup time 0 – 0 – ns 15

34 t

RWL

Write command to RAS lead time 8 – 10 – ns

35 t

CWL

Write command to CAS lead time 8 – 10 – ns

36 t

DS

Data setup time 0 – 0 – ns 16

37 t

DH

Data hold time 8 – 10 – ns 16

Read-modify-Write Cycle

38 t

RWC

Read-write cycle time 113 – 138 – ns

39 t

RWD

RAS to WE delay time 64 – 77 – ns 15

40 t

CWD

CAS to WE delay time 27 – 32 – ns 15

41 t

AWD

Column address to WE delay time 39 – 47 – ns 15

42 t

OEH

OE command hold time 10 – 13 – ns

EDO Page Mode Cycle

43 t

PC

EDO page mode cycle time 20 – 25 – ns

44 t

CP

CAS precharge time 8 – 10 – ns

45 t

CPA

Access time from CAS precharge – 27 – 32 ns 7

46 t

COH

Output data hold time 5 – 5 – ns

47 t

RASP

RAS pulse width in EDO mode 50 200k 60 200k ns

48 t

RHPC

CAS precharge to RAS Delay 27 – 32 – ns

49 t

OES

OE setup time prior to CAS 5 – 5 ns

EDO Page Mode Read-modify-Write Cycle

50 t

PRWC

EDO page mode read-write cycle time 58 – 68 – ns

51 t

CPWD

CAS precharge to WE 41 – 49 – ns

CAS-before-RAS Refresh Cycle

52 t

CSR

CAS setup time 10 – 10 – ns

53 t

CHR

CAS hold time 10 – 10 – ns

54 t

RPC

RAS to CAS precharge time 5 – 5 – ns

55 t

WRP

Write to RAS precharge time 10 – 10 – ns

56 t

WRH

Write hold time referenced to RAS 10 – 10 – ns

AC Characteristics

(5, 6)

TA = 0 to 70 ˚C,VCC = 5 V ± 10 %, tT = 2 ns

# Symbol Parameter

-50 -60

Unit Notemin. max. min. max.

7

MOSEL VITELIC

V53C517405A

V53C517405A Rev. 1.1 March 1998

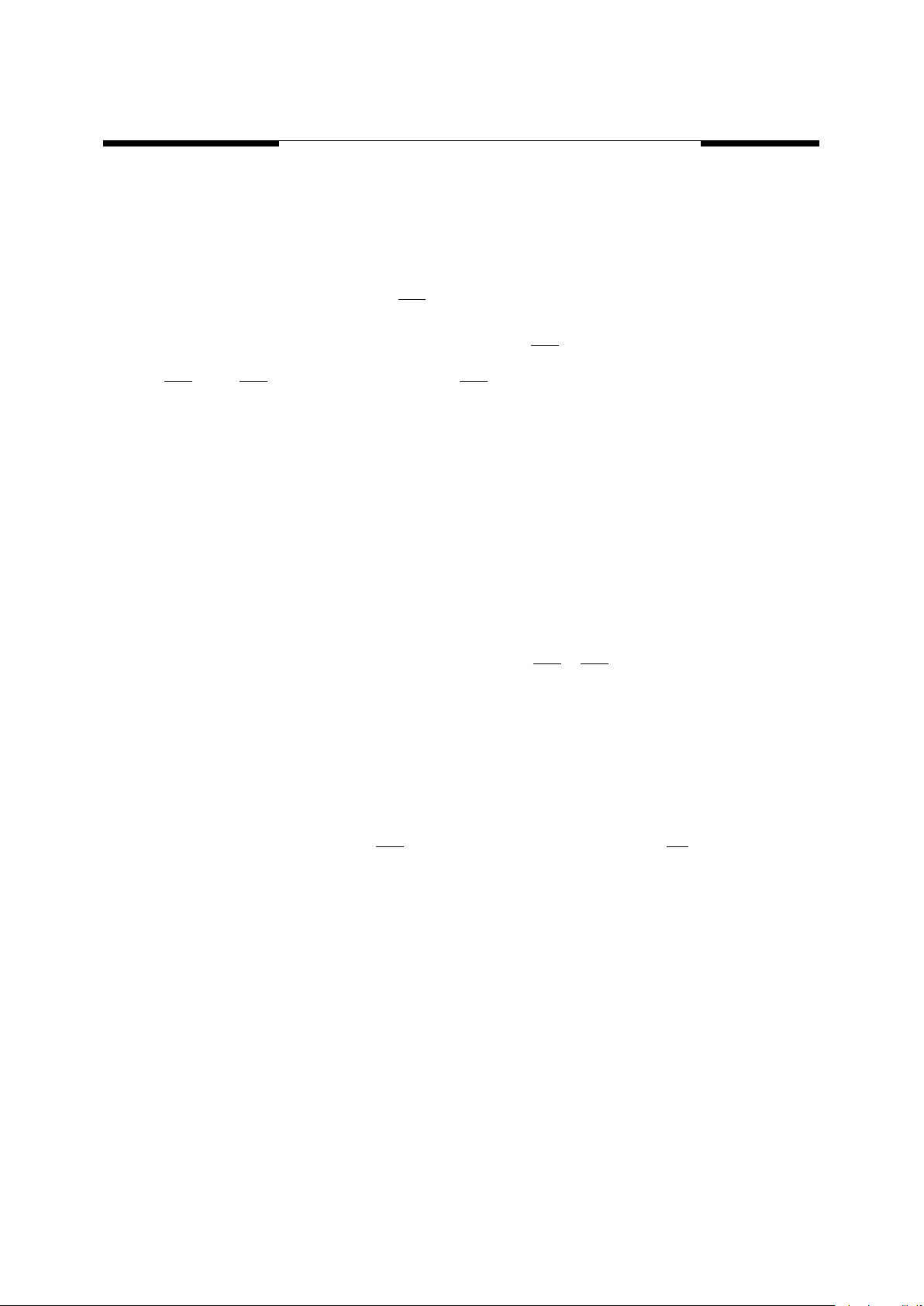

CAS-before-RAS Counter Test Cycle

57 t

CPT

CAS precharge time 35 – 40 – ns

Test Mode

61 t

WTS

Write command setup time 10 – 10 – ns

62 t

WTH

Write command hold time 10 – 10 – ns

63 t

CHRT

CAS hold time 30 – 30 – ns

64 t

RAHT

RAS hold time in test mode 30 – 30 – ns

AC Characteristics

(5, 6)

TA = 0 to 70 ˚C,VCC = 5 V ± 10 %, tT = 2 ns

# Symbol Parameter

-50 -60

Unit Notemin. max. min. max.

8

V53C517405A Rev. 1.1 March 1998

MOSEL VITELIC

V53C517405A

Notes:

1) All voltages are referenced to VSS.

2) I

CC1

, I

CC3

, I

CC4

and I

CC5

depend on cycle rate.

3) I

CC1

and I

CC4

depend on output loading. Specified values are obtained with the output open.

4) Address can be changed once or less while RAS

= VIL. In case of I

CC4

it can be changed once or less during a EDO

page mode cycle

5) An initial pause of 200 µs is required after power-up followed by 8 RAS

cycles of which at least one cycle has to be

a refresh cycle, before proper device operation is achieved. In case of using the internal refresh counter, a minimum

of 8 CAS

-before-RAS initialization cycles instead of 8 RAS cycles are required.

6) AC measurements assume t

T

= 2 ns.

7) V

IH (min.)

and V

IL (max.)

are reference levels for measuring timing of input signals. Transition times are also measured

between V

IH

and VIL.

8) Measured with the specified current load and 100 pF at V

OL

= 0.8 V and VOH = 2.0 V. Access time is determined by

the latter of t

RAC

, t

CAC

, t

CAA,tCPA

, t

OEA

. t

CAC

is measured from tristate.

9) Operation within the t

RCD (max.)

limit ensures that t

RAC (max.)

can be met. t

RCD (max.)

is specified as a reference point

only. If t

RCD

is greater than the specified t

RCD (max.)

limit, then access time is controlled by t

CAC

.

10) Operation within the t

RAD (max.)

limit ensures that t

RAC (max.)

can be met. t

RAD (max.)

is specified as a reference point

only. If t

RAD

is greater than the specified t

RAD (max.)

limit, then access time is controlled by t

CAA

.

11) Either t

RCH

or t

RRH

must be satisfied for a read cycle.

12) t

OFF (max.)

, t

OEZ (max.)

define the time at which the output achieves the open-circuit conditions and are not referenced

to output voltage levels. t

OFF

is referenced from the rising edge of RAS or CAS, whichever occurs last.

13) Either t

DZC

or t

DZO

must be satisfied.

14) Either t

CDD

or t

ODD

must be satisfied.

15) t

WCS

, t

RWD

, t

CWD

and t

AWD

are not restrictive operating parameters. They are included in the data sheet as electrical

characteristics only. If t

WCS

> t

WCS (min.)

, the cycle is an early write cycle and data out pin will remain open-circuit

(high impedance) through the entire cycle; if t

RWD

> t

RWD (min.)

, t

CWD

> t

CWD (min.)

and t

AWD

> t

AWD (min.)

, the cycle

is a read-write cycle and I/O will contain data read from the selected cells. If neither of the above sets of conditions

is satisfied, the condition of I/O (at access time) is indeterminate.

16) These parameters are referenced to the CAS

leading edge in early write cycles and to the WE leading edge in read-

write cycles.

Loading...

Loading...