Mosel Vitelic V53C16126HT50, V53C16126HT45, V53C16126HT40, V53C16126HT35, V53C16126HT30 Datasheet

...

MOSEL VITELIC

1

V53C16126H

HIGH PERFORMANCE

128K X 16 BIT FAST PAGE MODE

CMOS DYNAMIC RAM

V53C16126H Rev. 1.3 February 1998

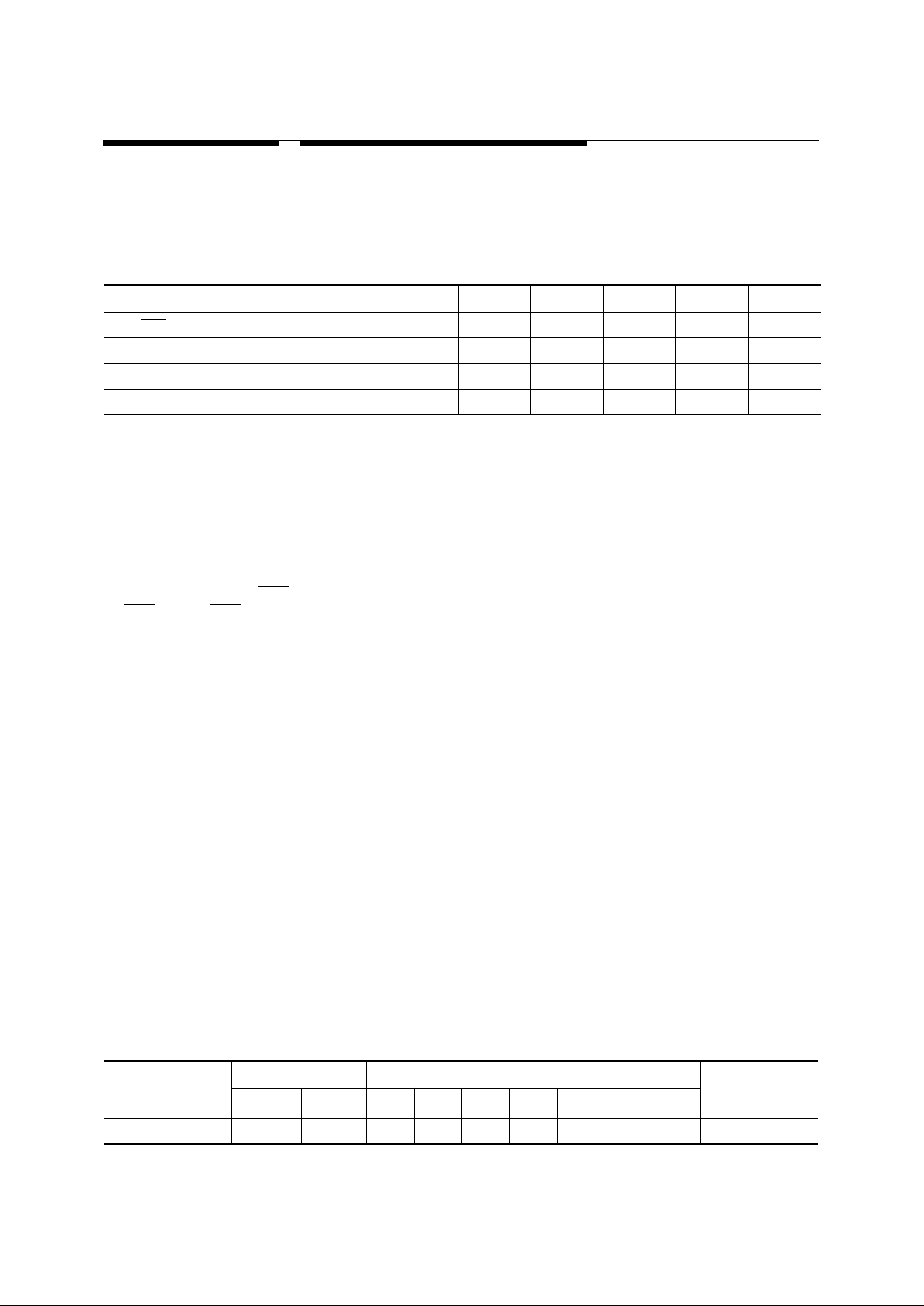

HIGH PERFORMANCE 30 35 40 45 50

Max. RAS

Access Time, (t

RAC

) 30 ns 35 ns 40 ns 45 ns 50 ns

Max. Column Address Access Time, (t

CAA

) 16 ns 18 ns 20 ns 22 ns 24 ns

Min. Fast Page Mode Cycle Time, (t

PC

) 19 ns 21 ns 23 ns 25 ns 28 ns

Min. Read/Write Cycle Time, (t

RC

) 65 ns 70 ns 75 ns 80 ns 90 ns

Features

■

128K x 16-bit organization

■

Fast Page Mode for a sustained data rate

of 53 MHz

■

RAS

access time: 30, 35, 40, 45, 50ns

■

Dual CAS Inputs

■

Low Power Dissipation

■

Read-Modify-Write, RAS

-Only Refresh,

CAS-Before-RAS Refresh

■

Refresh Interval: 512 cycles/8 ms

■

Available in 40-pin 400 mil SOJ and 40/44L-pin

400 mil TSOP-II packages

■

Single +5V ± 10% Power Supply

■

TTL Interface

Description

The V53C16126H is a 131,072 x 16 bit high

performance CMOS dynamic random access

memory. The V53C16126H offers Fast Page mode

with dual CAS

inputs. The V53C16126H has

asymmetric address, 9-bit row and 8-bit column.

All inputs are TTL compatible. Fast Page Mode

operation allows random access up to 256 x 16

bits, within a page, with cycle times as short as

19ns.

The V53C16126H is ideally suited for a wide

variety of high performance computer systems and

peripheral applications.

Device Usage Chart

Operating

Temperature

Range

Package Outline Access Time (ns) Power

Temperature

MarkK T 30 35 40 45 50 Std.

0 °

C to 70 ° C • • ••••• • Blank

2

V53C16126H Rev. 1.3 February 1998

MOSEL VITELIC

V53C16126H

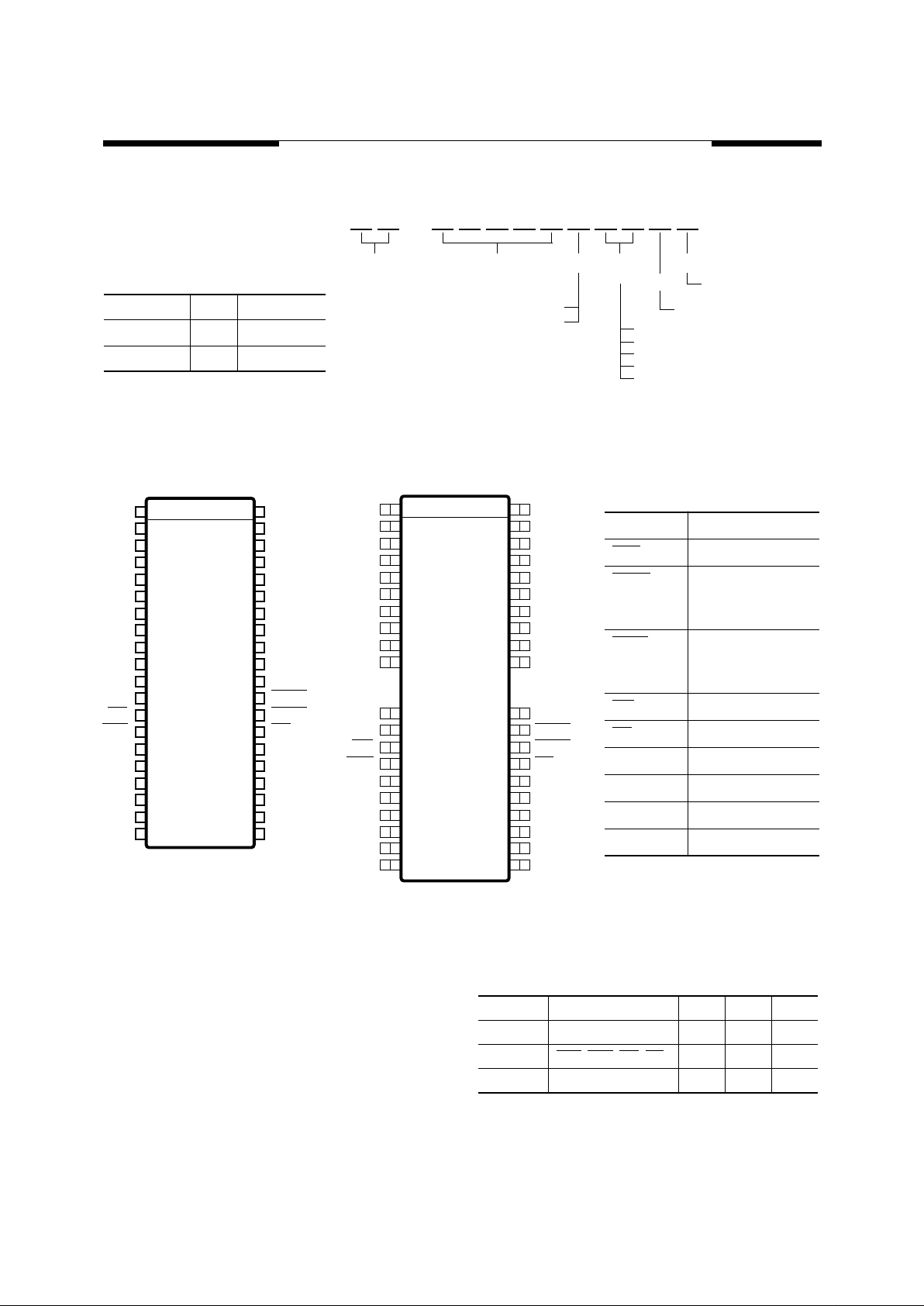

Vss

I/O16

I/O15

I/O14

I/O13

Vss

I/O12

I/O11

I/O10

I/O9

NC

LCAS

UCAS

OE

A8

A7

A6

A5

A4

Vss

5

6

7

8

9

10

11

12

Vcc

I/O1

I/O2

I/O3

I/O4

Vcc

I/O5

I/O6

I/O7

I/O8

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

40

39

38

37

36

35

34

33

32

31

30

29

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

16126H-02

5

6

7

8

9

10

Vcc

I/O1

I/O2

I/O3

I/O4

Vcc

I/O5

I/O6

I/O7

I/O8

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

16126H-03

43

44

42

41

40

39

38

37

36

35

13

14

15

16

17

18

19

20

21

22

32

31

30

29

28

27

26

25

24

23

Vss

I/O16

I/O15

I/O14

I/O13

Vss

I/O12

I/O11

I/O10

I/O9

NC

LCAS

UCAS

OE

A8

A7

A6

A5

A4

Vss

FAMILY DEVICE PKG

(t

RAC

)

SPEED

PWR.

V 5 3 C 1 2 6

45 (45 ns)

50 (50 ns)

30 (30 ns)

35 (35 ns)

40 (40 ns)

TEMP.

BLANK (0°C to 70°C)

BLANK (NORMAL)

(SOJ)K

(TSOP-II)T

H16

16126H-01

Description Pkg. Pin Count

SOJ K 40

TSOP-II T 40/44L

Absolute Maximum Ratings*

Ambient Temperature

Under Bias................................ –10 ° C to +80 ° C

Storage Temperature (plastic)..... –55 ° C to +125 ° C

Voltage Relative to V

SS

.................–1.0 V to +7.0 V

Data Output Current .....................................50 mA

Power Dissipation..........................................1.0 W

*Note: Operation above Absolute Maximum Ratings can

adversely affect device reliability.

Capacitance*

T

A

= 25 ° C, V

CC

= 5 V ± 10%, V

SS

= 0 V

*Note: Capacitance is sampled and not 100% tested

Symbol Parameter Typ. Max. Unit

C

IN1

Address Input 3 4 pF

C

IN2

RAS

, CAS, WE, OE 4 5 pF

C

OUT

Data Input/Output 5 7 pF

40-Pin Plastic SOJ

PIN CONFIGURATION

Top View

40/44L-Pin Plastic TSOP-II

PIN CONFIGURATION

Top View

Pin Names

A

0

–A

8

Address Inputs

RAS

Row Address Strobe

UCAS Column Address

Strobe/Upper Byte

Control

LCAS

Column Address

Strobe/Lower Byte

Control

WE

Write Enable

OE Output Enable

I/O

1

–I/O

16

Data Input, Output

V

CC

+5V Supply

V

SS

0V Supply

NC No Connect

MOSEL VITELIC

V53C16126H

3

V53C16126H Rev. 1.3 February 1998

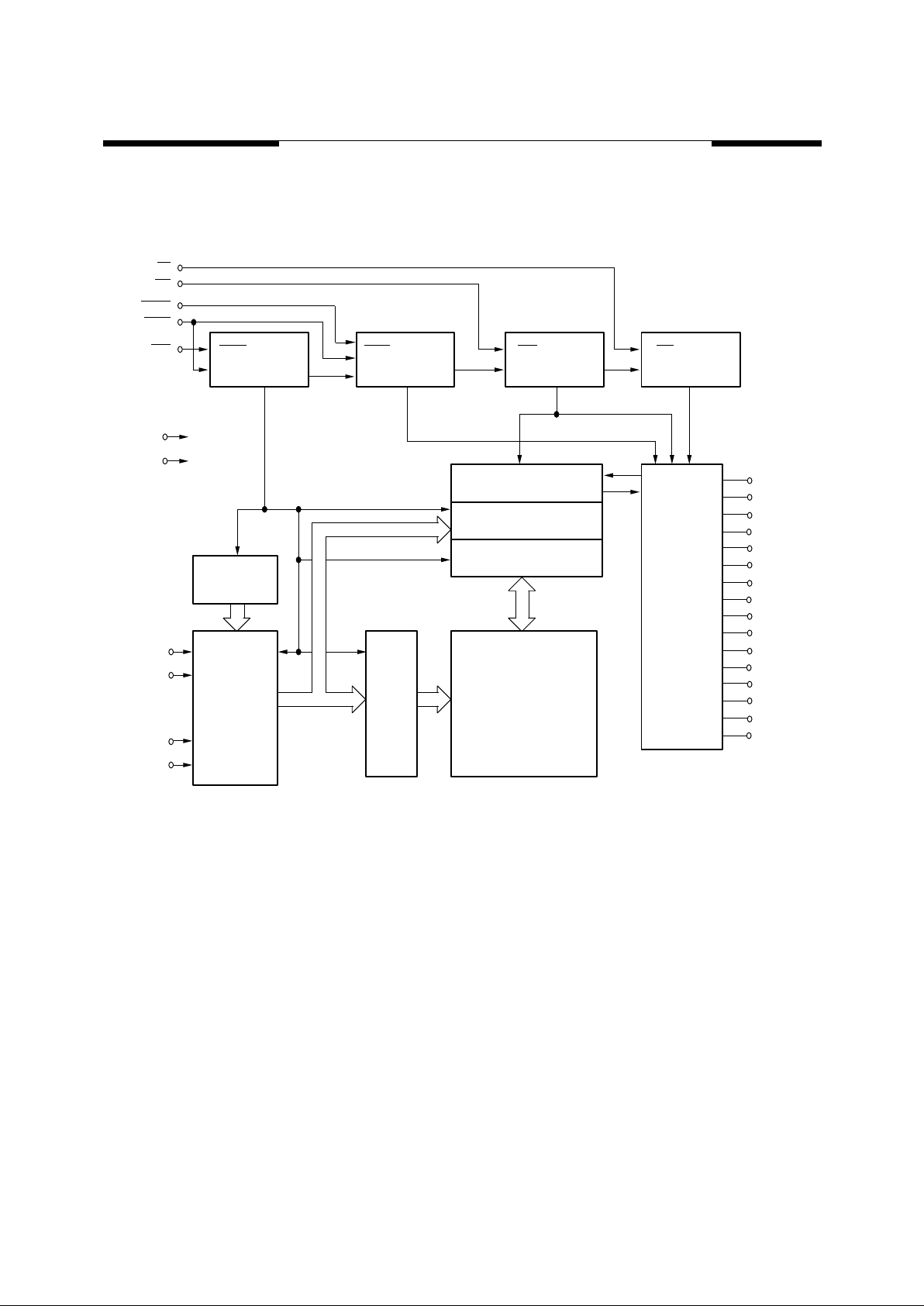

Block Diagram

A

0

A

1

A

7

A

8

SENSE AMPLIFIERS

REFRESH

COUNTER

V

CC

V

SS

9

512

256 x 16

I/O

1

ADDRESS BUFFERS

AND PREDECODERS

ROW

DECODERS

MEMORY

ARRAY

512 x 256 x 16

COLUMN DECODERS

DATA I/O BUS

Y0–Y

7

X0– X

8

I/O

BUFFER

I/O

2

I/O

3

I/O

4

OE CLOCK

GENERATOR

WE CLOCK

GENERATOR

CAS CLOCK

GENERATOR

RAS CLOCK

GENERATOR

OE

WE

LCAS

RAS

•

•

•

I/O

5

I/O

6

I/O

7

I/O

8

I/O

9

I/O

10

I/O

11

I/O

12

I/O

13

I/O

14

I/O

15

I/O

16

UCAS

128K x 16

16126H-04

4

V53C16126H Rev. 1.3 February 1998

MOSEL VITELIC

V53C16126H

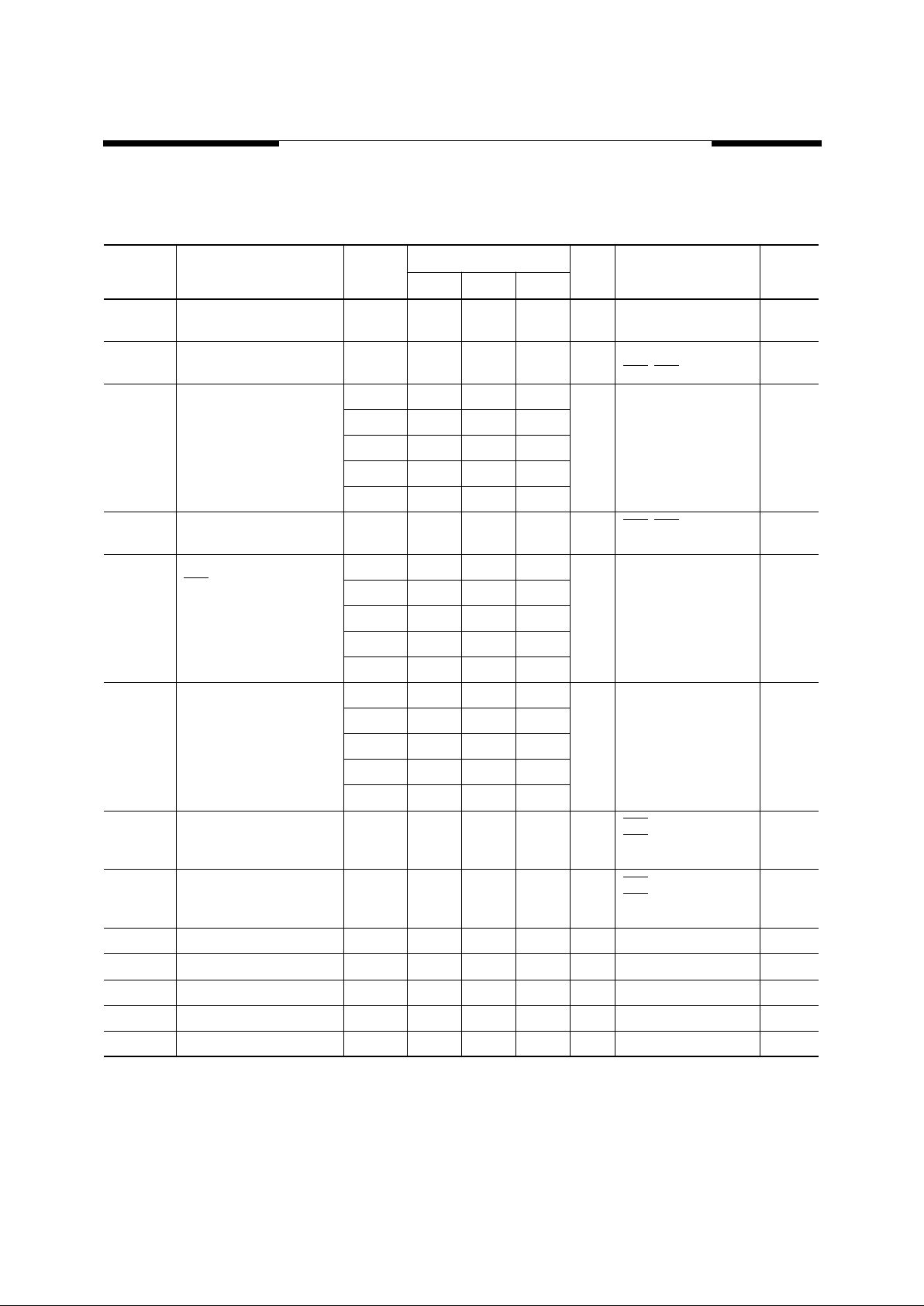

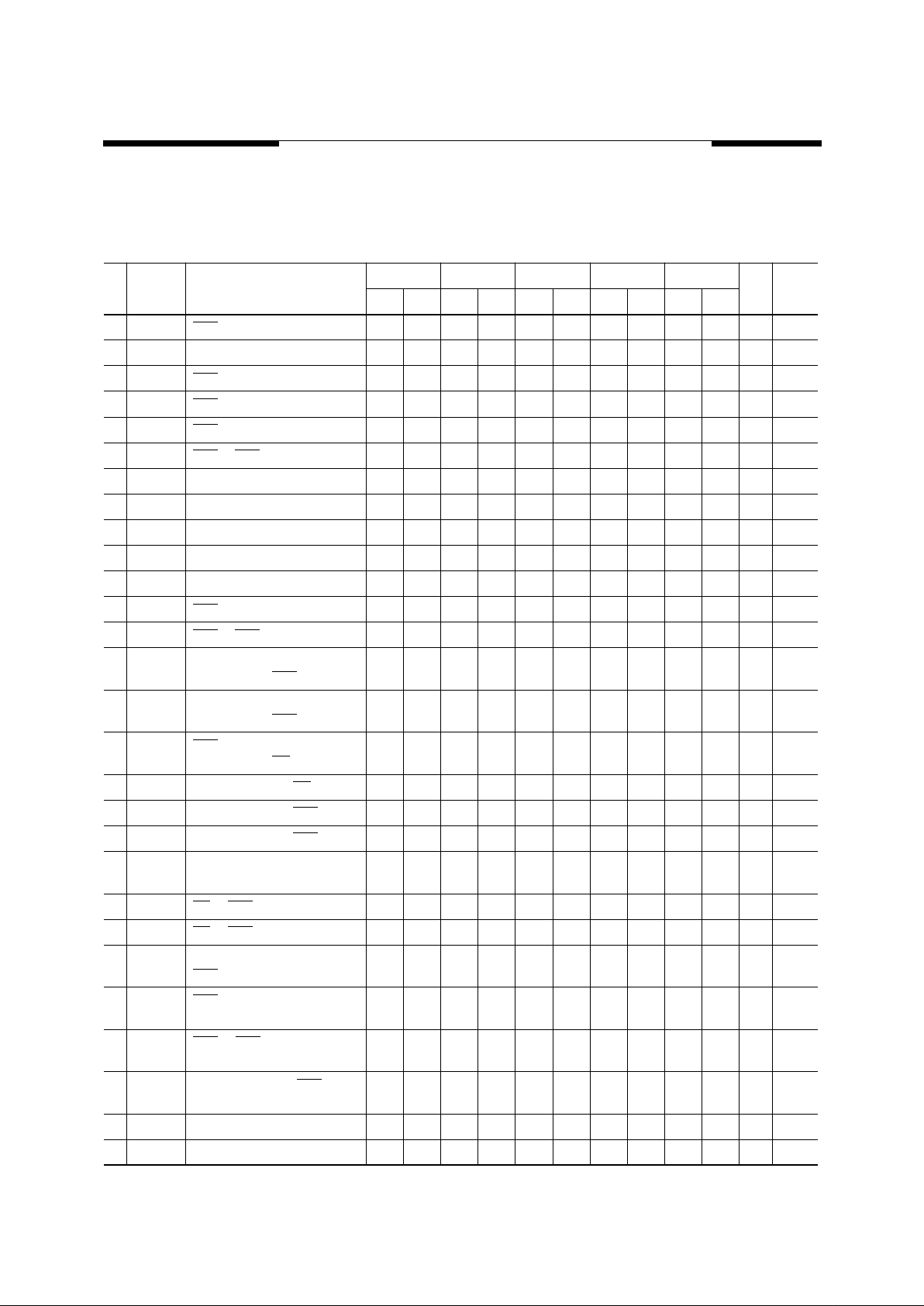

DC and Operating Characteristics

(1-2)

T

A

= 0 ° C to 70 ° C, V

CC

= 5 V ± 10%, V

SS

= 0 V, unless otherwise specified.

Symbol Parameter

Access

Time

V53C16126H

Unit Test Conditions NotesMin. Typ. Max.

I

LI

Input Leakage Current

(any input pin)

–10 10

µ

A V

SS

≤

V

IN

≤

V

CC

I

LO

Output Leakage Current

(for High-Z State)

–10 10

µ

A V

SS

≤

V

OUT

≤

V

CC

RAS

, CAS at V

IH

I

CC1

V

CC

Supply Current,

Operating

30 200 mA t

RC

= t

RC

(min.) 1, 2

35 190

40 180

45 170

50 160

I

CC2

V

CC

Supply Current,

TTL Standby

2 mA RAS

, CAS at V

IH

,

other inputs ≥ V

SS

I

CC3

V

CC

Supply Current,

RAS

-Only Refresh

30 200 mA t

RC

= t

RC

(min.) 2

35 190

40 180

45 170

50 160

I

CC4

V

CC

Supply Current,

Fast Page Mode Operation

30 190 mA Minimum Cycle 1, 2

35 180

40 170

45 160

50 150

I

CC5

V

CC

Supply Current,

Standby Output Enable

other inputs ≥ V

SS

2 mA RAS

= V

IH

CAS

= V

IL

1

I

CC6

V

CC

Supply Current,

CMOS Standby

1 mA RAS

≥ V

CC

– 0.2 V,

CAS

≥ V

CC

– 0.2 V,

All other inputs ≥ V

SS

V

CC

Supply Voltage 4.5 5.5 V

V

IL

Input Low Voltage –1 0.8 V 3

V

IH

Input High Voltage 2.4 V

CC

+ 1 V 3

V

OL

Output Low Voltage 0.4 V I

OL

= 4.2 mA

V

OH

Output High Voltage 2.4 2.4 V I

OH

= –5 mA

MOSEL VITELIC

V53C16126H

5

V53C16126H Rev. 1.3 February 1998

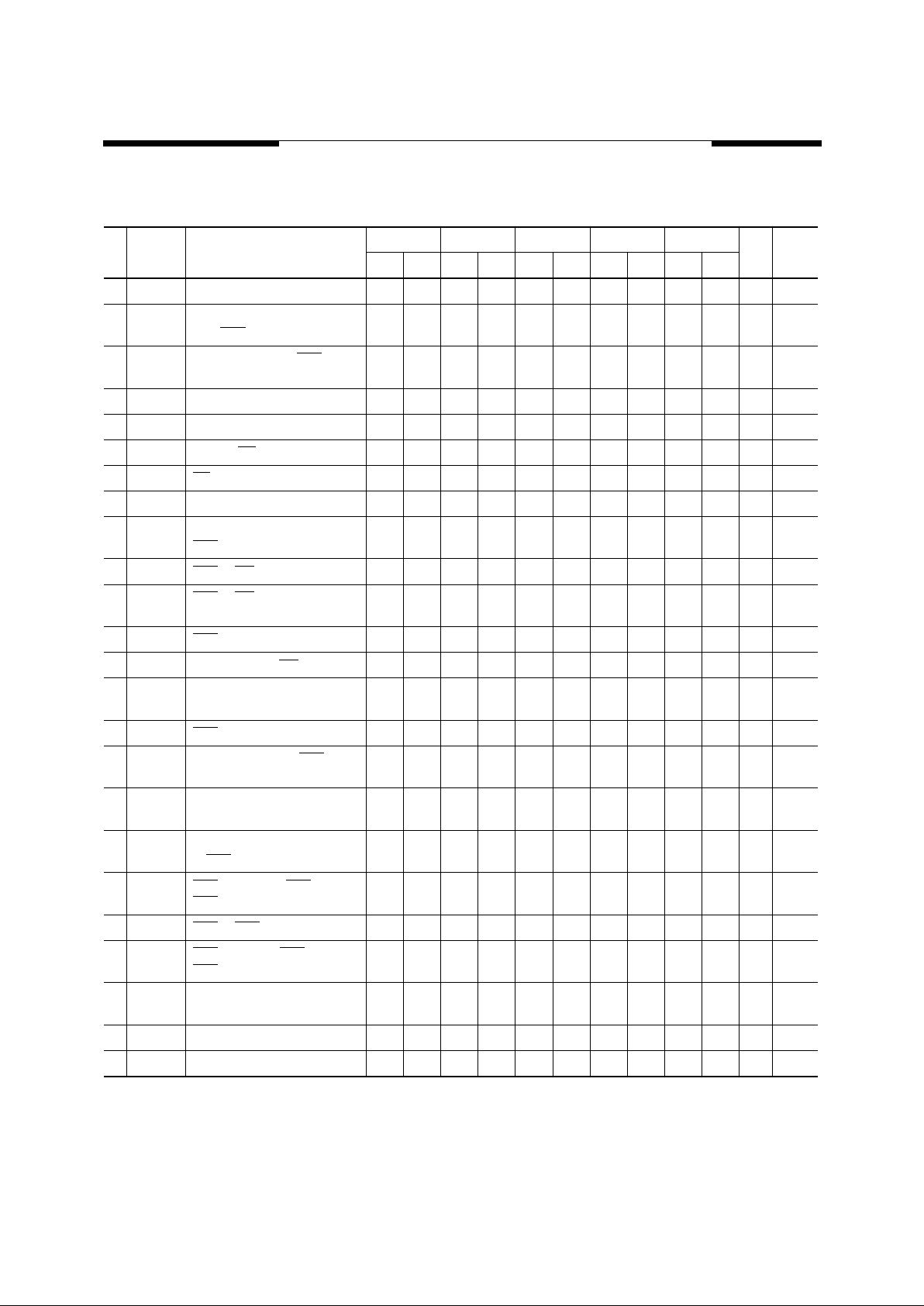

AC Characteristics

T

A

= 0 ° C to 70 ° C, V

CC

= 5 V ± 10%, V

SS

= 0V unless otherwise noted

AC Test conditions, input pulse levels 0 to 3V

# Symbol Parameter

30 35 40 45 50

Unit NotesMin. Max. Min. Max. Min. Max. Min. Max. Min. Max.

1 t

RAS

RAS Pulse Width 30 75K 35 75K 40 75K 45 75K 50 75K ns

2 t

RC

Read or Write Cycle Time 65 70 75 80 90 ns

3 t

RP

RAS Precharge Time 25 25 25 25 30 ns

4 t

CSH

CAS Hold Time 30 35 40 45 50 ns

5 t

CAS

CAS Pulse Width 5 6 7 8 9 ns

6 t

RCD

RAS to CAS Delay 15 20 16 24 17 28 18 32 19 36 ns

7 t

RCS

Read Command Setup Time 0 0 0 0 0 ns 4

8 t

ASR

Row Address Setup Time 0 0 0 0 0 ns

9 t

RAH

Row Address Hold Time 5 6 7 8 9 ns

10 t

ASC

Column Address Setup Time 0 0 0 0 0 ns

11 t

CAH

Column Address Hold Time 5 5 5 6 7 ns

12 t

RSH (R)

RAS Hold Time (Read Cycle) 10 10 10 10 10 ns

13 t

CRP

CAS to RAS Precharge Time 5 5 5 5 5 ns

14 t

RCH

Read Command Hold Time

Referenced to CAS

0 0 0 0 0 ns 5

15 t

RRH

Read Command Hold Time

Referenced to RAS

0 0 0 0 0 ns 5

16 t

ROH

RAS Hold Time

Referenced to OE

6 7 8 9 10 ns

17 t

OAC

Access Time from OE 10 11 12 13 14 ns 12

18 t

CAC

Access Time from CAS 10 11 12 13 14 ns 6,7,14

19 t

RAC

Access Time from RAS 30 35 40 45 50 ns 6, 8, 9

20 t

CAA

Access Time from Column

Address

16 18 20 22 24 ns 6,7,10

21 t

LZ

OE or CAS to Low-Z Output 0 0 0 0 0 ns 16

22 t

HZ

OE or CAS to High-Z Output 0 5 0 6 0 6 0 7 0 8 ns 16

23 t

AR

Column Address Hold Time from

RAS

26 28 30 35 40 ns

24 t

RAD

RAS to Column Address

Delay Time

10 14 11 17 12 20 13 23 14 26 ns 11

25 t

RSH (W)

RAS or CAS Hold Time in

Write Cycle

10 10 10 10 10 ns

26 t

CWL

Write Command to CAS

Lead Time

10 11 12 13 14 ns

27 t

WCS

Write Command Setup Time 0 0 0 0 0 ns 12, 13

28 t

WCH

Write Command Hold Time 5 5 5 6 7 ns

6

V53C16126H Rev. 1.3 February 1998

MOSEL VITELIC

V53C16126H

29 t

WP

Write Pulse Width 5 5 5 6 7 ns

30 t

WCR

Write Command Hold Time

from RAS

26 28 30 35 40 ns

31 t

RWL

Write Command to RAS

Lead Time

10 11 12 13 14 ns

32 t

DS

Data in Setup Time 0 0 0 0 0 ns 14

33 t

DH

Data in Hold Time 5 5 5 6 7 ns 14

34 t

WOH

Write to OE Hold Time 5 5 6 7 8 ns 14

35 t

OED

OE to Data Delay Time 5 5 6 7 8 ns 14

36 t

RWC

Read-Modify-Write Cycle Time 100 105 110 115 130 ns

37 t

RRW

Read-Modify-Write Cycle

RAS Pulse Width

65 70 75 80 87 ns

38 t

CWD

CAS to WE Delay 26 28 30 32 34 ns 12

39 t

RWD

RAS to WE Delay in ReadModify-Write Cycle

50 54 58 62 68 ns 12

40 t

CRW

CAS Pulse Width (RMW) 44 46 48 50 52 ns

41 t

AWD

Col. Address to WE Delay 32 35 38 41 42 ns 12

42 t

PC

Fast Page Mode Read

or Write Cycle Time

19 21 23 25 28 ns

43 t

CP

CAS Precharge Time 3 4 5 6 7 ns

44 t

CAR

Column Address to RAS

Setup Time

16 18 20 22 24 ns

45 t

CAP

Access Time from Column

Precharge

19 21 23 25 27 ns 7

46 t

DHR

Data in Hold Time Referenced

to RAS

26 28 30 35 40 ns

47 t

CSR

CAS Setup Time CAS- beforeRAS Refresh

10 10 10 10 10 ns

48 t

RPC

RAS to CAS Precharge Time 0 0 0 0 0 ns

49 t

CHR

CAS Hold Time CAS-beforeRAS Refresh

7 8 8 10 12 ns

50 t

PCM

Fast Page Mode Read-ModifyWrite Cycle Time

56 58 60 65 70 ns

51 t

T

Transition Time (Rise and Fall) 1.5 50 1.5 50 1.5 50 1.5 50 1.5 50 ns 15

52 t

REF

Refresh Interval (512 Cycles) 8 8 8 8 8 ms 17

# Symbol Parameter

30 35 40 45 50

Unit NotesMin. Max. Min. Max. Min. Max. Min. Max. Min. Max.

AC Characteristics

(Cont’d)