Page 1

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

Stratix II GX Embedded Gigabit

Ethernet MAC / PHY

User's Guide

1

Page 2

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

Contents

1 DESIGN KIT INSTALLATION.........................................................................................................3

1.1 PLATFORM SPECIFIC JAVA RUNTIME INSTALLATION ......................................................................3

1.2 DESIGN KIT INSTALLATION ............................................................................................................3

2 DESIGN FLOW................................................................................................................................4

3 GENERATING THE MAC/PHY CORE............................................................................................5

3.1 OVERVIEW ...................................................................................................................................5

3.2 CORE CONFIGURATION OPTIONS ..................................................................................................6

3.3 DESIGN KIT DATABASE .................................................................................................................7

3.4 SIMULATION ENVIRONMENT ..........................................................................................................7

3.5 RUNNING SIMULATION USING MODELSIM SE.................................................................................8

Overview..........................................................................................................................................8

Testbuilder Options..........................................................................................................................9

3.6 RUNNING SIMULATION USING MODELSIM PE OR MODELSIM AE....................................................13

Overview........................................................................................................................................13

Simulation Options.........................................................................................................................13

3.7 DESIGN IMPLEMENTATION WITH QUARTUS II ................................................................................16

3.8 VQM NETLIST GENERATION .......................................................................................................16

3.9 FULL TIMING GATE LEVEL SIMULATION........................................................................................17

4 CONTACT .....................................................................................................................................18

List of Figures

Figure 1: Design Flow Overview.............................................................................................................5

Figure 2: MAC Core Configuration Panel ...............................................................................................6

Figure 3: Testbench Setup Overview......................................................................................................8

Figure 4: Running Testbuilder Overview.................................................................................................9

Figure 5: Testbuilder Panel...................................................................................................................10

Figure 6: VQM Netlist Generation.........................................................................................................17

List of Tables

Table 1: Core Configuration Options ......................................................................................................7

Table 2: Design Kit Directory Structure...................................................................................................7

Table 3: Simulation Options..................................................................................................................10

Table 4: MAC Configuration Options....................................................................................................12

Table 5: Testbuilder Simulation Control................................................................................................13

Table 6: Simulation Options..................................................................................................................13

Table 7: MAC Configuration Options....................................................................................................15

2

Page 3

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

1 Design Kit Installation

1.1 Platform Specific JAVA Runtime Installation

To be able to run the MAC Design Kit delivery and configuration tool, a Java runtime must be

present on the system. The design kit needs the Java Runtime Environment Version 1.2.x

(JRE1.2) or later.

To determine if and which Java version is installed on your system, open a Shell and type "java

-version". If you get errors then the runtime is not installed. If the version is lower than 1.3.x a

newer package must be installed.

A platform specific package (The runtime standard edition 1.3, JRE 1.3, is sufficient) can be

downloaded from the Sum Microsystems WEB site:

http://java.sun.com/j2se.

To install the runtime environment, follow the instructions included in the download package:

• Windows platform: Execute the self-extracting archive.

• Solaris/Linux: Extract the package in a directory and add the bin directory to the PATH

environment variable.

1.2 Design Kit Installation

A single executable Java delivery and configuration utility, common to all platforms, is provided,

ethpack.jar. The utility generates all the required design files as well as the required scri pts for

simulation and implementation.

After unzipping the distribution in any directory

• Windows users:

1. Double-click on the ethpack.jar file found in the distribution top directory

• UNIX (Solaris/Linux) users:

1. Goto the installation directory: $> cd <installation directory>

2. Execute the Java application: $> java -jar ethpack.jar

1

, the Java application can be started immediately:

1

Use the extract feature of your unzip tool. Avoid using drag&drop as it does not preserve the directory structure.

3

Page 4

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

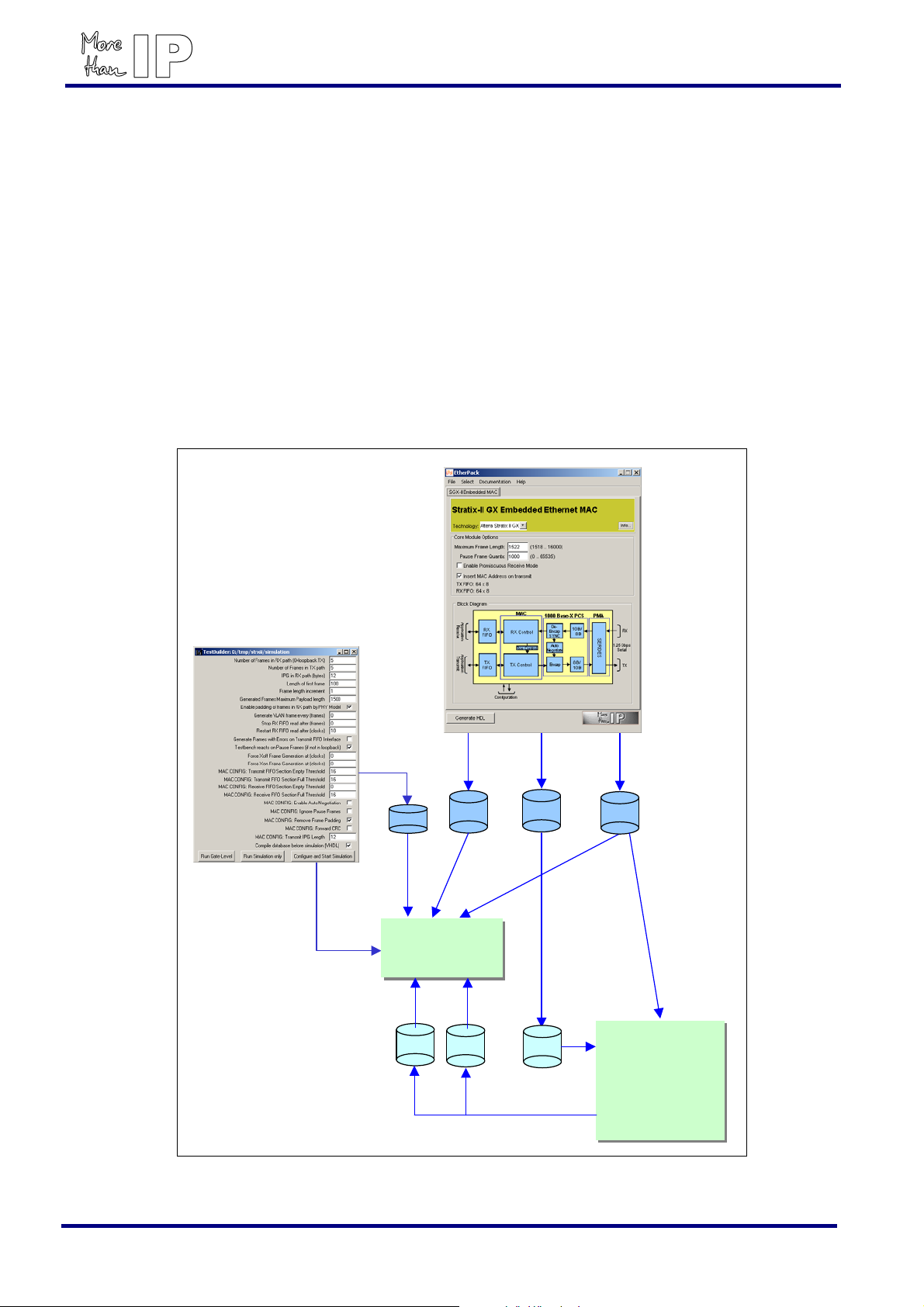

2 Design Flow

The different steps of the Embedded Gigabit Ethernet MAC-PHY Design are:

• Core generation

• RTL Simulation

• Synthesis

• Implementation using Quartus II

• Gate-Level Simulation – Not available with Evaluation License

The design kit provides scripts for ease of use, fast design and verification / implementation turnaround.

The tools primarily supported are:

• Simulation: Modelsim Version 5.7a or higher

• Synthesis: Altera Quartus II V5.1 or higher

• Implementation: Altera Quartus II V5.1 or higher

4

Page 5

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

3 Generating the MAC/PHY Core

3.1 Overview

After the Core configuration utility is installed, start the utility and when the panel is available:

1. Select the Core options on the panel

2. Press the "Generate HDL" button.

3. A new window appears prompting you for a key. Type LbNH-sC79 and press “Enter”.

4. A new window appears which can be used to navigate through the file system to select

an existing directory or create a new working directory. After pressing the "open" button

finally creates the database.

MorethanIP TestBuilder

Simulation

Control

Testbench

Configuration

VHO SDF

ModelSim

ModelSim

VHDL

Testbench

User Constraints

Constraint

Template

VHDL

Design FILES

Quartus

Quartus

Figure 1: Design Flow Overview

5

Page 6

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

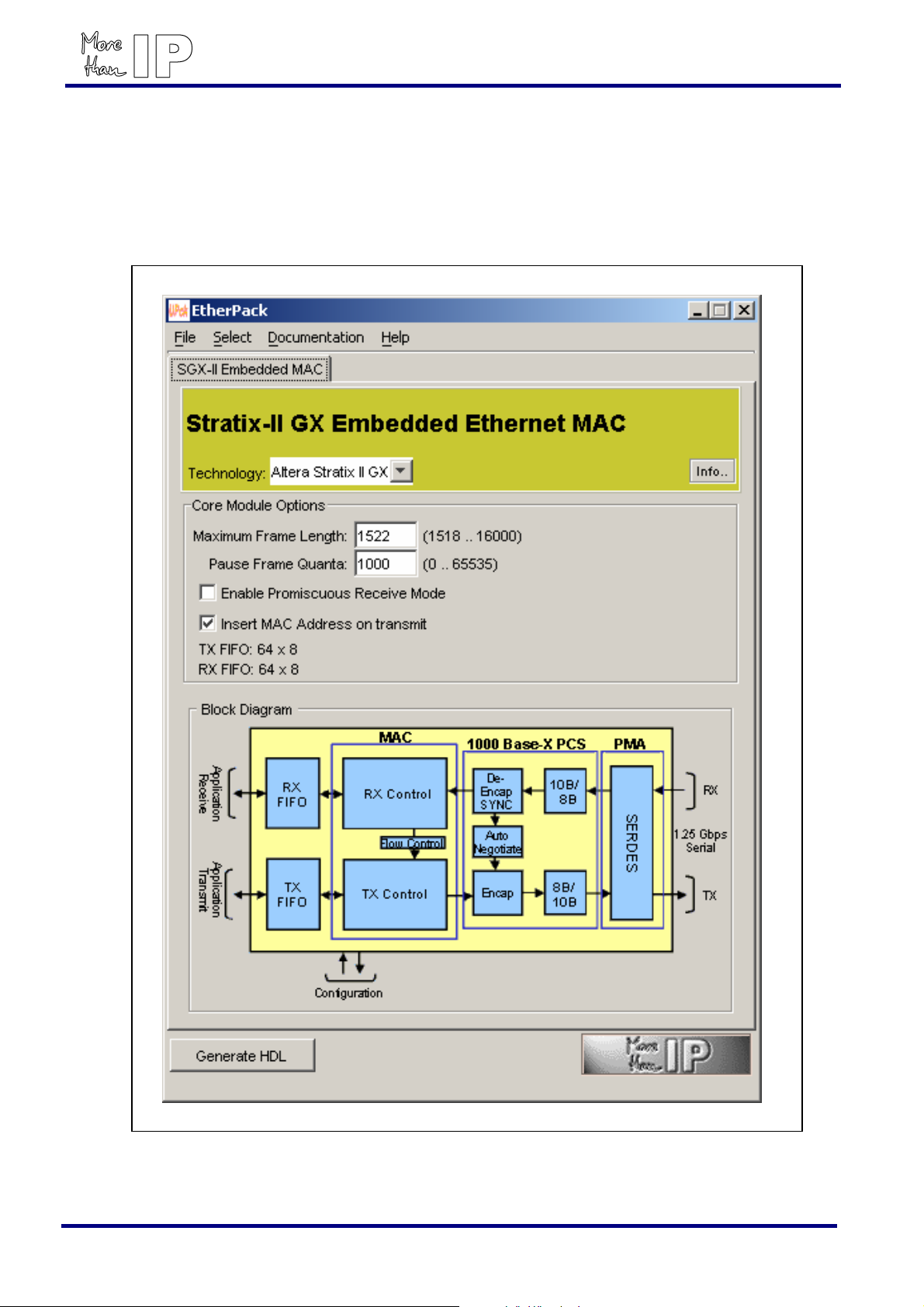

3.2 Core Configuration Options

The Core is fully configurable and a user friendly GUI is provided to simplify configuration. To

optimize the core for the intended application environment, several options are available which can

be modified before the actual database is generated as described before.

Figure 2: MAC Core Configuration Panel

6

Page 7

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Table 1: Core Configuration Options

Option Description

Technology The Core is optimized for Altera Stratix II GX devices.

User's Guide

Version 1.0 - October 2005

Maximum Frame Length

Pause Frame Quanta

Enable Promiscuous

Receive Mode

Insert MAC Address on

Transmit

3.3 Design Kit Database

Table 2: Design Kit Directory Structure

Directory Description

models Ethernet Frame generator and monitor models.

quartus

Maximum Frame Length. Defines a 14-Bit maximum frame length used by

the MAC receive logic to check frames.

Receive Pause Quanta. 16-Bit value sets, in increment of 512 Ethernet bit

times, the pause quanta used in each Pause Frame sent to the remote

Ethernet device.

When selected, all frames are received without Unicast address filtering.

If select the MAC overwrites the source MAC address with the MAC set on

the Core signal mac_addr. If disabled, the source MAC address received

from the transmit application transmitted is not modified by the MAC.

Contains the netist for Altera Stratix implementation and a script

to control the Altera Quartus design software.

simulation

source

Scripts to configure and execute RTL and Gate-Level Simulation

as well the Modelsim integrated TestBuilder.

Encrypted VHDL design source files, testbench and

configuration files.

3.4 Simulation Environment

A complete testbench is provided (File testbench.vhd in directory source/testbench/vhdl)

which implements the Core together with a simulation control state machine and the following

drivers and monitors.

• GMII Ethernet Frame Generator: Configurable Ethernet Gigabit Ethernet frame generator

with GMII interface.

• GMII Ethernet Frame Monitor: Gigabit Ethernet frame monitor with GMII interface.

• Ethernet Frame Generator (FIFO mode): Configurable Ethernet frame generator

simulating a user application connected to the MAC transmit FIFO interface.

• Ethernet Monitor (FIFO mode): Ethernet frame checker simulating a user application

connected to the MAC receive FIFO interface.

• PCS: 1000Base-X PCS function that decodes / encodes data from / to the MAC / PHY

Core and controls the Auto-Negotiation process within the testbench.

7

Page 8

mtip_sim_pack.vhd

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

Testbench

Ethernet Frame

Ethernet Frame

Generator

Generator

(FIFO mode)

(FIFO mode)

Ethernet

Ethernet

Monitor

Monitor

(FIFO mode)

(FIFO mode)

Unit Under Test (uut)

Transmit

FIFO

Receive

FIFO

TX

RX

Testbench

Testbench

Control

Pause Control

Figure 3: Testbench Setup Overview

3.5 Running Simulation Using Modelsim SE

Overview

PCS

Model

GMII

GMII

Ethernet Frame

Ethernet Frame

Monitor

Monitor

GMII

GMII

Ethernet Frame

Ethernet Frame

Generator

Generator

To simplify the evaluation process and to allow designers to quickly generate custom simulation

scenarios, a graphical utility (Testbuilder) is provided. Testbuilder operates as a Modelsim plugin, which is used to set simulation options, compile the complete design and run the simulation

process.

To start Testbuilder in the Modelsim command window:

1. Change to Modelsim working directory

cd <Design Kit Root>/simulation

2. Run the Modelsim macro

do testbuilder.do

8

Page 9

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

1

Figure 4: Running Testbuilder Overview

2

Important note:

The system variable QUARTUS_ROOTDIR should be set to the Quartus software

installation directory so that the Altera libraries can be linked during RTL or Gate level

simulations.

Testbuilder Options

A single VHDL configuration file configures the Testbench:

• source/package/vhdl/mtip_sim_pack.vhd

The file can be modified to implement different simulation scenarios. To ease the configuration,

a graphical tool, TestBuilder is provided that modifies the configuration file. TestBuilder is a

TCL/TK extension written for the ModelSim Simulator, which is fully integrated in the ModelSim

framework.

9

Page 10

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

Simulation

Control

Core

Configuration

Figure 5: Testbuilder Panel

Table 3: Simulation Options

Option Unit Description Default

Number of Frames in RX path Frames

Number of Frames in TX path Frames

IPG in RX path Bytes

Modelsim

Control

Sets the number of frames that are generated by

the Ethernet frame Generator connected to the

Receive PHY interface.

If set to 0, a Serdes loopback test is performed

with the Core pin loop_ena set to '1'.

Sets the number of frames that are generated by

the frame Generator connected to the Core

transmit FIFO interface.

Sets the inter-packet gap (IGP) used by the

Ethernet Frame generator when generating

frames to the RX PHY interface.

5

5

12

Length of first frame Bytes

Defines the payload length of the first frame

generated by the Ethernet and FIFO models.

10

100

Page 11

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Frame length increment Bytes

Generated Frames max.

payload length

Enable Padding of Frames in

RX Path

Boolean

Bytes

User's Guide

Version 1.0 - October 2005

Frame payload length increment. During

simulation frames are generated starting from

"length of first frame" incrementing with each

frame generated.

Defines the payload maximum length used by the

Ethernet Generator models. This value specifies

the wrap around for the frame length of generated

frames. I.e. if the frame length increment would

exceed this value it wraps around to zero. Can be

used to test frame length error detection, when set

to any value larger than the MAC length

configuration.

If enabled, RX PHY Generator model generated

frames are padded to 64 octets in length (normal

mode). If disabled, no padding occurs and

erroneous frames will be sent to the MAC RX.

1

1500

True

Enable VLAN frames for all

tests

Stop RX FIFO read after Frames

Restart RX FIFO read after

Generate Frames with Errors

on Transmit FIFO Interface

Boolean

RX FIFO

clocks

Boolean

If enabled, all frames sent/received will be VLAN

type of frames

Inhibits the Testbench RX FIFO monitor reading

the RX FIFO, after this amount of frames has

been sent to the RX.

Can be used to test Flow-Control behaviour. If

more frames are received, the FIFO will get filled.

When the threshold level is reached, a PauseFrame will be generated by the MAC TX. If set to

0, the RX FIFO read is never paused.

Number of clock cycles, the RX FIFO should not

be read after it has been stopped. Only relevant if

the previous configuration (read stop) was set to a

non-null value.

After this number of RX FIFO clock cycles, the RX

FIFO will be emptied again.

Enable Transmit Error Generation the Core

Transmit Interface. When selected, the transmit

FIFO signal ff_tx_err is asserted with

ff_tx_eop to signal an Error. When disabled,

the FIFO error is signalled, ff_tx_err is never

set to '1'.

False

0

10

False

Testbench reacts on Pause

Frames

Boolean

If enabled (true) the Testbench will stop the RX

(PHY) Frame generator, if the MAC sends a

Pause Frame. This simulates a usual flow-control

chain correctly.

If disabled (False) Pause Frames sent by the

MAC are ignored by the Testbench and the RX

(PHY) Frame generator will never pause. This can

be used to test the MACs FIFO overflow behavior.

This option has no effect, if loopback mode is

enabled (i.e. Frame generation in RX path is set

0).

11

True

Page 12

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Force Xoff Frame Generation

at (clocks)

Force Xon Frame Generation

at (clocks)

Table 4: MAC Configuration Options

Option Unit Description Default

Integer

Integer

User's Guide

Version 1.0 - October 2005

XOFF Pause Frame Generation. Set the time for

to generate a XOFF Frame with the Core

command pin xoff_gen. When set to 0, XOFF

Frame generation is disabled.

XON Pause Frame Generation. Set the time for to

generate a XON Frame with the Core command

pin xon_gen. When set to 0, XON Frame

generation is disabled.

0

0

MAC CONFIG: Transmit FIFO

Section Empty Threshold

MAC CONFIG: Transmit FIFO

Section Full Threshold

MAC CONFIG: Receive FIFO

Section Empty Threshold

MAC CONFIG: Receive FIFO

Section Full Threshold

MAC CONFIG: Enable Auto-

Negotiation

Integer

Integer

Integer

Integer

Boolean

Set the Transmit FIFO Section empty threshold

to any value between 0 and 63 (Maximum

memory depth).

Set the Transmit FIFO Section full threshold to

any value between 0 and 63 (Maximum memory

depth).

Set the Receive FIFO Section empty threshold

to any value between 0 and 63 (Maximum

memory depth).

Set the Receive FIFO Section full threshold to

any value between 0 and 63 (Maximum memory

depth).

Enable Auto-Negotiation. When selected, the

Core performs auto-negotiation to check the link

with the Link Partner before simulation starts.

After simulation, the Auto-Negotiation is

restarted with the Core signal an_enable set to

'0'. When disabled, non Auto-Negotiation is

performed.

16

16

0

16

True

MAC CONFIG: Ignore Pause

Frames

MAC CONFIG: Remove

Frame Padding

MAC CONFIG: Forward CRC Boolean

MAC CONFIG: Transmit IPG

Length

Boolean

Boolean

Integer

Ignore Pause Frames. When enabled, received

Pause Frames are ignored, when disable,

Pause Frames are decoded.

Enable Receive Padding Remove. When

enabled, Frames are provided on the Client

Interface without padding, when disabled,

Frames are provided on the Client Interface with

padding.

Enable CRC Forwarding. When selected, CRC

is passed transparently from the Transmit Client

Interface to line and, is preserved on the

Received Client Interface.

Transmit Inter-Packet Gap. Defined, in Bytes,

the IPG between transmitted Frames.

12

False

True

False

12

Page 13

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Version 1.0 - October 2005

Table 5: Testbuilder Simulation Control

Testbuilder Panel Option Description

User's Guide

Compile Database before

Simulation (VHDL)

Run Simulation Only

Configure and Start Simulation

Run Gate-Level

When running a simulation, a set of waveforms is displayed; error and information messages are

issued in the Modelsim standard output.

When enabled, the Core simulation database is refreshed with the Core

configuration options. The option must be enabled at least once after a

new Core database was generated.

When selected, starts the RTL simulation with all the options defined in

the Testbuilder panel ignored (Previous configuration used).

When selected, the options defined on the Testbuilder panel are saved

before the RTL simulation is performed.

When selected, the options defined on the Testbuilder panel are saved

before the Gate level simulation is performed.

3.6 Running Simulation Using Modelsim PE or Modelsim AE

Overview

Modifying the file mtip_sim_pack.vhd located in the directory source/package/vhdl

creates a custom simulation scenario. The Core files and dependencies are available in the file

comp.do (In Directory simulation), the testbench file and simulation models files are listed

in the file sim.do. The files comp.do and sim.do should be modified and adapted with the

simulator command.

Once a scenario has been created, the following steps should be followed:

1. Change to the simulation directory.

2. Compile the Core database:

• do comp.do

3. Compile the Simulation database and run simulation:

• do sim.do

Simulation Options

The simulation is controlled and is configured with a set of parameters set in the file

mtip_sim_pack.vhd.

Table 6: Simulation Options

Option Unit Description Default

Sets the number of frames that are generated by

the Ethernet frame Generator connected to the

TB_RXFRAMES Frames

Receive PHY interface.

If set to 0, a Serdes loopback test is performed

with the Core pin loop_ena set to '1'.

5

13

Page 14

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Sets the number of frames that are generated by

TB_TXFRAMES Frames

TB_RXIPG Bytes

the frame Generator connected to the Core

transmit FIFO interface.

Sets the inter-packet gap (IGP) used by the

Ethernet Frame generator when generating

frames to the RX PHY interface.

User's Guide

Version 1.0 - October 2005

5

12

TB_LENSTART Bytes

TB_LENSTEP Bytes

TB_LENMAX Bytes

TB_ENA_PADDING Boolean

TB_ENA_VLAN Boolean

Defines the payload length of the first frame

generated by the Ethernet and FIFO models.

Frame payload length increment. During

simulation frames are generated starting from

"length of first frame" incrementing with each

frame generated.

Defines the payload maximum length used by the

Ethernet Generator models. This value specifies

the wrap around for the frame length of generated

frames. I.e. if the frame length increment would

exceed this value it wraps around to zero. Can be

used to test frame length error detection, when set

to any value larger than the MAC length

configuration.

If enabled, RX PHY Generator model generated

frames are padded to 64 octets in length (normal

mode). If disabled, no padding occurs and

erroneous frames will be sent to the MAC RX.

If enabled, all frames sent/received will be VLAN

type of frames

Inhibits the Testbench RX FIFO monitor reading

the RX FIFO, after this amount of frames has

been sent to the RX.

100

1

1500

True

False

TB_STOPREAD Frames

TB_HOLDREAD

TB_TX_FF_ERR Boolean

TB_PAUSECONTROL Boolean

RX FIFO

clocks

Can be used to test Flow-Control behaviour. If

more frames are received, the FIFO will get filled.

When the threshold level is reached, a PauseFrame will be generated by the MAC TX. If set to

0, the RX FIFO read is never paused.

Number of clock cycles, the RX FIFO should not

be read after it has been stopped. Only relevant if

the previous configuration (read stop) was set to a

non-null value.

After this number of RX FIFO clock cycles, the RX

FIFO will be emptied again.

Enable Transmit Error Generation the Core

Transmit Interface. When selected, the transmit

FIFO signal ff_tx_err is asserted with

ff_tx_eop to signal an Error. When disabled,

the FIFO error is signalled, ff_tx_err is never

set to '1'.

If enabled (true) the Testbench will stop the RX

(PHY) Frame generator, if the MAC sends a

0

10

False

True

14

Page 15

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Pause Frame. This simulates a usual flow-control

chain correctly.

If disabled (False) Pause Frames sent by the

MAC are ignored by the Testbench and the RX

(PHY) Frame generator will never pause. This can

be used to test the MACs FIFO overflow behavior.

This option has no effect, if loopback mode is

enabled (i.e. Frame generation in RX path is set

0).

XOFF Pause Frame Generation. Set the time for

TB_TRIGGERXOFF Integer

TB_TRIGGERXON Integer

to generate a XOFF Frame with the Core

command pin xoff_gen. When set to 0, XOFF

Frame generation is disabled.

XON Pause Frame Generation. Set the time for to

generate a XON Frame with the Core command

pin xon_gen. When set to 0, XON Frame

generation is disabled.

User's Guide

Version 1.0 - October 2005

0

0

Table 7: MAC Configuration Options

Option Unit Description Default

TX_FIFO_SE Integer

TX_FIFO_SF Integer

RX_FIFO_SE Integer

RX_FIFO_SF Integer

TB_ENA_AUTONEG Boolean

Set the Transmit FIFO Section empty threshold

to any value between 0 and 63 (Maximum

memory depth).

Set the Transmit FIFO Section full threshold to

any value between 0 and 63 (Maximum memory

depth).

Set the Receive FIFO Section empty threshold

to any value between 0 and 63 (Maximum

memory depth).

Set the Receive FIFO Section full threshold to

any value between 0 and 63 (Maximum memory

depth).

Enable Auto-Negotiation. When selected, the

Core performs auto-negotiation to check the link

with the Link Partner before simulation starts.

After simulation, the Auto-Negotiation is

restarted with the Core signal an_enable set to

'0'. When disabled, non Auto-Negotiation is

performed.

16

16

0

16

True

Ignore Pause Frames. When enabled, received

TB_IGNORE_PAUSE Boolean

TB_PAD_ENA Boolean

Pause Frames are ignored, when disable,

Pause Frames are decoded.

Enable Receive Padding Remove. When

enabled, Frames are provided on the Client

Interface without padding, when disabled,

Frames are provided on the Client Interface with

padding.

False

True

15

Page 16

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

Enable CRC Forwarding. When selected, CRC

TB_CRC_FWD Boolean

is passed transparently from the Transmit Client

Interface to line and, is preserved on the

Received Client Interface.

User's Guide

Version 1.0 - October 2005

False

TB_IPG_LEN Integer

Transmit Inter-Packet Gap. Defined, in Bytes,

the IPG between transmitted Frames.

3.7 Design Implementation with Quartus II

Two TCL script (quartus.tcl) is provided in the design kit directory quartus, which performs

the following actions:

1. Create project

2. Build database

3. Set timing constraints

4. Set I/O Fast Register constraint on fast I/O signals

5. Run Quartus fitter

6. Reports design timing and timing violations

7. Generates VHO VHDL gate level netlist and SDO timing file used during Gate level

simulation

The TCL script can run from the Quartus II graphical interface or in batch mode.

• Graphical Mode:

1. In Quartus II TCL console Change to Quartus working directory

cd <Design Kit Root>/quartus

12

2. Run the design TCL script

source quartus.tcl

3.8 VQM Netlist Generation

After you obtain a core license from Altera, a VQM netlist of the Core can be generated with the

Quartus II software. The VQM netlist can be used to integrate the Core in a customer design.

To create the VQM netlist:

1. Analyze and Synthesize the Core

2. Generate the VQM Netlist

16

Page 17

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

1

2

Figure 6: VQM Netlist Generation

The VQM Netlist (embedded_gige_mac_phy.vqm) is created in the directory quartus/

atom_netlists.

Note: Without the free license from Altera, the VQM netlist cannot be generated and an error

message will appear. You can disregard this message as it will not prevent you from running RTL

simulation.

3.9 Full Timing Gate Level Simulation

The gate level verification is performed using Quartus II VHDL output files (Structural VHDL and

SDF timing files) in the directory quartus/simulation.

To run the gate level simulation with Modelsim, use as described in chapters “

gate level simulation when the Testbuilder simulation option “Run Gate-Level” is used.

With a Modelsim PE or Modelsim AE, run the script gate.do:

• do gate.do

3.5” and following. A

17

Page 18

4 Contact

Altera

For the most up-to-date information about Altera products, go to the Altera world-wide

web site at www.altera.com. For technical support on this product, go to

www.altera.com/mysupport. For additional information about Altera products, consult

the sources shown below.

Information Type USA & Canada All Other Locations

Stratix II GX Embedded Gigabit Ethernet MAC / PHY

User's Guide

Version 1.0 - October 2005

www.altera.com/mysupport www.altera.com/mysupport Technical support

(800) 800-EPLD (3753)

(7:00 a.m. to 5:00 p.m. Pacific Time)

Product literature www.altera.com www.altera.com

Altera literature services literature@altera.com literature@altera.com

Non-technical customer

service

FTP site ftp.altera.com ftp.altera.com

(800) 767-3753 +1 408-544-7000

+1 408-544-8767

7:00 a.m. to 5:00 p.m. (GMT –8:00)

Pacific Time

7:00 a.m. to 5:00 p.m. (GMT –8:00)

Pacific Time

MorethanIP

E-Mail : info@morethanip.com

Internet : www.morethanip.com

Europe

Muenchner Strasse 199

D-85757 Karlsfeld

Germany

Tel : +49 (0) 8131 333939 0

FAX : +49 (0) 8131 333939 1

18

Loading...

Loading...