Page 1

ModelSim®

Xilinx Edition II

User’s Manual

Version 5.7c

Published: 11/Mar/03

The world’s most popular HDL simulator

Page 2

ii

ModelSim is produced by Model Technology™, a Mentor Graphics Corporation

company. Copying, duplication, or other reproduction is prohibited without the

written consent of Model Technology.

The information in this manual is subject to change without notice and does not

represent a commitment on the part of Model Technology. The program described

in this manual is furnished under a license agreement and may not be used or

copied except in accordance with the terms of the agreement. The online

documentation provided with this product may be printed by the end-user. The

number of copies that may be printed is limited to the number of licenses

purchased.

ModelSim is a registered trademark and Signal Spy, TraceX, ChaseX and Model

Technology are trademarks of Mentor Graphics Corporation. PostScript is a

registered trademark of Adobe Systems Incorporated. UNIX is a registered

trademark of AT&T in the USA and other countries. FLEXlm is a trademark of

Globetrotter Software, Inc. IBM, AT, and PC are registered trademarks, AIX and

RISC System/6000 are trademarks of International Business Machines

Corporation. Windows, Microsoft, and MS-DOS are registered trademarks of

Microsoft Corporation. OSF/Motif is a trademark of the Open Software Foundation,

Inc. in the USA and other countries. SPARC is a registered trademark and

SPARCstation is a trademark of SPARC International, Inc. Sun Microsystems is a

registered trademark, and Sun

, SunOS and OpenWindows are trademarks of Sun

Microsystems, Inc. All other trademarks and registered trademarks are the

properties of their respective holders.

Copyright

© 1990 -2003, Model Technology, a Mentor Graphics Corporation

company. All rights reserved. Confidential. Online documentation may be printed

by licensed customers of Model Technology and Mentor Graphics for internal

business purposes on ly.

ModelSim support

Support for ModelSim is available from your FPGA vendor. See the About

ModelSim dialog box (accessed via the Help menu) for contact information.

ModelSim User’s Manual

Page 3

Table of Contents

1 - Introduction (UM-13)

Standards supported . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-14

Assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-14

Sections in this document . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-14

What is an "HDL item" . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-16

Text conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-16

2 - Projects (UM-17)

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-18

How do proje cts differ from pre-5.5 version s? . . . . . . . . . . . . . . . . . . UM-19

Project conversion between versions . . . . . . . . . . . . . . . . . . . . . . UM-19

Getting started with projects . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-20

Step 1 — Creating a new project . . . . . . . . . . . . . . . . . . . . . . . UM-20

Step 2 — Adding items to the project . . . . . . . . . . . . . . . . . . . . . UM-21

Step 3 — Compiling the files . . . . . . . . . . . . . . . . . . . . . . . . . UM-24

Step 4 — Simula t ing a design . . . . . . . . . . . . . . . . . . . . . . . . UM-25

Other basic project operations . . . . . . . . . . . . . . . . . . . . . . . . UM-25

The Project tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-26

Project tab context menu . . . . . . . . . . . . . . . . . . . . . . . . . . UM-27

Changing compile order . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-28

Grouping files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-29

Creating a Simulation Configuration . . . . . . . . . . . . . . . . . . . . . . . . UM-30

Organizing projects with folders . . . . . . . . . . . . . . . . . . . . . . . . . UM-32

Setting compiler options . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-34

Accessing projects from the command line . . . . . . . . . . . . . . . . . . . . . UM-35

UM-3

3 - Design libraries (UM-37)

Design library contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-38

Design library types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-39

Working with design libraries . . . . . . . . . . . . . . . . . . . . . . . . . . UM-40

Managing library contents . . . . . . . . . . . . . . . . . . . . . . . . . . UM-41

Assigning a logical name to a design library . . . . . . . . . . . . . . . . . . . UM-43

Moving a library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-44

Specifying the resource libraries . . . . . . . . . . . . . . . . . . . . . . . . . UM-45

Predefined libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-46

Alternate IEEE libraries supplied . . . . . . . . . . . . . . . . . . . . . . . UM-46

Regenerating your design libraries . . . . . . . . . . . . . . . . . . . . . . . UM-47

Importing FPGA libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-48

ModelSim User’s Manual

Page 4

UM-4 Table of Contents

4 - VHDL simulation (UM-49)

Compiling VHDL designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-50

Invoking the VHDL compiler . . . . . . . . . . . . . . . . . . . . . . . . UM-50

Dependency checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-50

Range and index checking . . . . . . . . . . . . . . . . . . . . . . . . . . UM-50

Simulating VHDL designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-52

Simulator resolution limit . . . . . . . . . . . . . . . . . . . . . . . . . . UM-52

Delta delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-53

Using the TextIO package . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-55

Syntax for file declaration . . . . . . . . . . . . . . . . . . . . . . . . . . UM-55

Using STD_INPUT and STD_OUTPUT within ModelSim . . . . . . . . . . . . . UM-56

TextIO implementation issues . . . . . . . . . . . . . . . . . . . . . . . . . . UM-57

Reading and writing hexadecimal numbers . . . . . . . . . . . . . . . . . . . UM-58

Dangling pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-58

The ENDLINE function . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-58

The ENDFILE function . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-58

Using alternative input/output files . . . . . . . . . . . . . . . . . . . . . . UM-59

Providing st imulus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-59

VITAL specification and source code . . . . . . . . . . . . . . . . . . . . . . . UM-60

VITAL packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-60

ModelSim VITAL compliance . . . . . . . . . . . . . . . . . . . . . . . . . . UM-60

VITAL compliance checking . . . . . . . . . . . . . . . . . . . . . . . . . UM-60

Compiling and simulating with accelerated VITAL packages . . . . . . . . . . . . . . UM-61

Util package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-62

get_resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-62

init_signal_driver() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-63

init_signal_spy() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-63

signal_force() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-63

signal_release() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-63

to_real() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-64

to_time() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-65

5 - Verilog simulation (UM-67)

Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-69

Incremental compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-70

Library usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-72

Verilog-XL compatible compiler arguments . . . . . . . . . . . . . . . . . . . UM-73

Verilog-XL ‘uselib compiler directive . . . . . . . . . . . . . . . . . . . . . UM-74

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-76

Simulator resolution limit . . . . . . . . . . . . . . . . . . . . . . . . . . UM-77

Event ordering in Verilog designs . . . . . . . . . . . . . . . . . . . . . . . UM-79

Negative timing check limits . . . . . . . . . . . . . . . . . . . . . . . . . UM-83

Verilog-XL compatible simulator arguments . . . . . . . . . . . . . . . . . . . UM-86

Cell libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-87

Delay modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-87

ModelSim User’s Manual

Page 5

System tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-89

IEEE Std 1364 system tasks . . . . . . . . . . . . . . . . . . . . . . . . . UM-89

Verilog-XL compatible system tasks . . . . . . . . . . . . . . . . . . . . . . UM-92

ModelSim Verilog system tasks . . . . . . . . . . . . . . . . . . . . . . . . UM-94

Compiler directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-95

IEEE Std 1364 compiler directives . . . . . . . . . . . . . . . . . . . . . . UM-95

Verilog-XL compatible compiler directives . . . . . . . . . . . . . . . . . . . UM-96

Verilog PLI/VPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-97

Registering PLI applications . . . . . . . . . . . . . . . . . . . . . . . . . UM-97

Registering VPI applications . . . . . . . . . . . . . . . . . . . . . . . . . UM-99

Compiling and linking PLI/VPI C applications . . . . . . . . . . . . . . . . . UM-101

Compiling and linking PLI/VPI C++ applications . . . . . . . . . . . . . . . . UM-102

Specifying the PLI/VPI file to load . . . . . . . . . . . . . . . . . . . . . UM-103

PLI example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-104

VPI example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-105

The PLI callback reason argument . . . . . . . . . . . . . . . . . . . . . . UM-106

The sizetf callback function . . . . . . . . . . . . . . . . . . . . . . . . UM-107

PLI object handles . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-107

Third party PLI applications . . . . . . . . . . . . . . . . . . . . . . . . UM-108

Support for VHDL objects . . . . . . . . . . . . . . . . . . . . . . . . . UM-109

IEEE Std 1364 ACC routines . . . . . . . . . . . . . . . . . . . . . . . . UM-110

IEEE Std 1364 TF routines . . . . . . . . . . . . . . . . . . . . . . . . . UM-111

Verilog-XL compatible routines . . . . . . . . . . . . . . . . . . . . . . . UM-113

64-bit support in the PLI . . . . . . . . . . . . . . . . . . . . . . . . . . UM-113

PLI/VPI tracing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-113

Debugging PLI/VPI application code . . . . . . . . . . . . . . . . . . . . UM-115

UM-5

6 - WLF files (datasets) and virtuals (UM-117)

WLF files (datasets) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-118

Saving a simulation to a WLF file . . . . . . . . . . . . . . . . . . . . . . UM-119

Opening datasets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-119

Viewing dataset structure . . . . . . . . . . . . . . . . . . . . . . . . . UM-120

Managing multiple datasets . . . . . . . . . . . . . . . . . . . . . . . . UM-121

Saving at intervals with Dataset Snapshot . . . . . . . . . . . . . . . . . . . UM-123

Virtual Objects (User-defined buses, and more) . . . . . . . . . . . . . . . . . . UM-125

Virtual signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-125

Virtual functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-126

Virtual regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-127

Virtual types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-127

Dataset, WLF file, and virtual commands . . . . . . . . . . . . . . . . . . . . . UM-128

7 - Graphic interface (UM-129)

Window overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-130

Common window features . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-131

Quick access toolbars . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-132

Drag and Drop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-132

ModelSim User’s Manual

Page 6

UM-6 Table of Contents

Command his tory . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-132

Automatic window updating . . . . . . . . . . . . . . . . . . . . . . . . UM-133

Finding names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-133

Sorting HDL items . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-133

Saving window layout . . . . . . . . . . . . . . . . . . . . . . . . . . UM-134

Context menus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-134

Menu tear of f . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-134

Tree window hierarchical view . . . . . . . . . . . . . . . . . . . . . . . UM-135

Main window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-137

Workspace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-138

Transcript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-139

The Main window menu bar . . . . . . . . . . . . . . . . . . . . . . . . UM-140

The Main window toolbar . . . . . . . . . . . . . . . . . . . . . . . . . UM-145

The Main window status bar . . . . . . . . . . . . . . . . . . . . . . . . UM-147

Mouse and keyboard shortcuts . . . . . . . . . . . . . . . . . . . . . . . UM-147

Dataflow window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-149

Adding items to the window . . . . . . . . . . . . . . . . . . . . . . . . UM-149

Links to other windows . . . . . . . . . . . . . . . . . . . . . . . . . . UM-150

Dataflow window menu bar . . . . . . . . . . . . . . . . . . . . . . . . UM-150

The Dataflow window toolbar . . . . . . . . . . . . . . . . . . . . . . . UM-153

Exploring the connectivity of your design . . . . . . . . . . . . . . . . . . . UM-156

Zooming an d panning . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-158

Tracing events (causality) . . . . . . . . . . . . . . . . . . . . . . . . . UM-159

Tracing the source of an unknown (X) . . . . . . . . . . . . . . . . . . . . UM-160

Finding items by name in the Dataflow window . . . . . . . . . . . . . . . . UM-161

Saving the display . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-162

Configuring page setup . . . . . . . . . . . . . . . . . . . . . . . . . . UM-164

Symbol mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-165

Configuring window options . . . . . . . . . . . . . . . . . . . . . . . . UM-166

List window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-168

HDL items you can view . . . . . . . . . . . . . . . . . . . . . . . . . UM-168

Adding HDL items to the List window . . . . . . . . . . . . . . . . . . . . UM-169

The List window menu bar . . . . . . . . . . . . . . . . . . . . . . . . . UM-170

Editing and formatting HDL items in the List window . . . . . . . . . . . . . . UM-172

Combining items in the List window . . . . . . . . . . . . . . . . . . . . . UM-174

Setting List window display properties . . . . . . . . . . . . . . . . . . . . UM-175

Finding items by name in the List window . . . . . . . . . . . . . . . . . . UM-177

Setting time markers in the List window . . . . . . . . . . . . . . . . . . . UM-178

Saving List window data to a file . . . . . . . . . . . . . . . . . . . . . . UM-179

List window keyboard shortcuts . . . . . . . . . . . . . . . . . . . . . . . UM-180

Process window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-181

The Process window menu bar . . . . . . . . . . . . . . . . . . . . . . . UM-182

Signals window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-183

The Signals window menu bar . . . . . . . . . . . . . . . . . . . . . . . UM-184

Filtering the signal list . . . . . . . . . . . . . . . . . . . . . . . . . . UM-185

Forcing signal and net values . . . . . . . . . . . . . . . . . . . . . . . . UM-186

Adding HDL items to the Wave and List windows or a WLF file . . . . . . . . . . UM-187

Finding HDL items in the Signals window . . . . . . . . . . . . . . . . . . UM-188

Setting signal breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . UM-189

ModelSim User’s Manual

Page 7

Defining cl ock signals . . . . . . . . . . . . . . . . . . . . . . . . . . UM-189

Source window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-191

The Source window menu bar . . . . . . . . . . . . . . . . . . . . . . . UM-192

The Source window toolbar . . . . . . . . . . . . . . . . . . . . . . . . UM-194

Setting file-line breakpoints . . . . . . . . . . . . . . . . . . . . . . . . UM-197

Checking HDL item values and descriptions . . . . . . . . . . . . . . . . . . UM-197

Finding and replacing in the Source window . . . . . . . . . . . . . . . . . . UM-197

Setting tab stops in the Source window . . . . . . . . . . . . . . . . . . . . UM-198

Structure window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-199

Structure window menu bar . . . . . . . . . . . . . . . . . . . . . . . . UM-200

Structure window context menu . . . . . . . . . . . . . . . . . . . . . . . UM-201

Finding items in the Structure window . . . . . . . . . . . . . . . . . . . . UM-202

Variables window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-203

The Variables window menu bar . . . . . . . . . . . . . . . . . . . . . . UM-204

Finding HDL items in the Variables window . . . . . . . . . . . . . . . . . . UM-205

Wave window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-206

Pathname pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-206

Values pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-207

Waveform pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-207

Cursor panes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-207

HDL items you can view . . . . . . . . . . . . . . . . . . . . . . . . . UM-207

Adding HDL items in the Wave window . . . . . . . . . . . . . . . . . . . UM-208

The Wave window menu bar . . . . . . . . . . . . . . . . . . . . . . . . UM-209

The Wave window toolbar . . . . . . . . . . . . . . . . . . . . . . . . . UM-212

Using dividers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-215

Splitting Wave window panes . . . . . . . . . . . . . . . . . . . . . . . UM-216

Combining items in the Wave window . . . . . . . . . . . . . . . . . . . . UM-217

Displaying drivers of the selected waveform . . . . . . . . . . . . . . . . . . UM-218

Editing and formatting HDL items in the Wave window . . . . . . . . . . . . . UM-219

Setting Wave window display properties . . . . . . . . . . . . . . . . . . . UM-222

Setting signal breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . UM-224

Finding items by name or value in the Wave window . . . . . . . . . . . . . . UM-225

Using time cursors in the Wave window . . . . . . . . . . . . . . . . . . . UM-226

Examining waveform values . . . . . . . . . . . . . . . . . . . . . . . . UM-228

Zooming - changing the waveform display range . . . . . . . . . . . . . . . . UM-228

Saving zoom range and scroll position with bookmarks . . . . . . . . . . . . . UM-229

Wave window mouse and keyboard shortcuts . . . . . . . . . . . . . . . . . UM-231

Saving waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-233

Compiling with the graphic interface . . . . . . . . . . . . . . . . . . . . . . UM-238

Locating source errors during compilation . . . . . . . . . . . . . . . . . . . UM-239

Setting default compile options . . . . . . . . . . . . . . . . . . . . . . . UM-240

Simulating with the graphic interface . . . . . . . . . . . . . . . . . . . . . . UM-245

Design tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-245

VHDL tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-247

Verilog tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-249

Libraries tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-250

SDF tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-251

Options tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-253

Setting default simulation options . . . . . . . . . . . . . . . . . . . . . . UM-254

UM-7

ModelSim User’s Manual

Page 8

UM-8 Table of Contents

Creating and managing breakpoints . . . . . . . . . . . . . . . . . . . . . . . UM-258

Signal breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-258

File-line breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-258

Breakpoints dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-259

Miscellaneous tools and add-ons . . . . . . . . . . . . . . . . . . . . . . . . UM-262

The GUI Expression Builder . . . . . . . . . . . . . . . . . . . . . . . . UM-262

Language templates . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-264

Graphic interface commands . . . . . . . . . . . . . . . . . . . . . . . . . . UM-267

8 - Signal Spy (UM-269)

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-270

init_signal_driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-271

init_signal_spy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-274

signal_force . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-276

signal_release . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-278

$init_signal_driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-280

$init_signal_spy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-283

$signal_force . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-285

$signal_release . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-287

9 - Standard Delay Format (SDF) Timing Annotation (UM-289)

Specifying SDF files for simulation . . . . . . . . . . . . . . . . . . . . . . . UM-290

Instance specification . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-290

SDF specification with the GUI . . . . . . . . . . . . . . . . . . . . . . . UM-291

Errors and warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-291

VHDL VITAL SDF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-292

SDF to VHDL generic matching . . . . . . . . . . . . . . . . . . . . . . UM-292

Resolving errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-293

Verilog SDF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-294

The $sdf_annotate system task . . . . . . . . . . . . . . . . . . . . . . . UM-294

SDF to Verilog construct matching . . . . . . . . . . . . . . . . . . . . . UM-295

Optional edge specifications . . . . . . . . . . . . . . . . . . . . . . . . UM-298

Optional conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-299

Rounded timing values . . . . . . . . . . . . . . . . . . . . . . . . . . UM-299

SDF for Mixed VHDL and Verilog Designs . . . . . . . . . . . . . . . . . . . . UM-300

Interconnect delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-300

Disabling timing checks . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-300

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-301

Mistaking a component or module name for an instance label . . . . . . . . . . . UM-302

Forgetting to specify the instance . . . . . . . . . . . . . . . . . . . . . . UM-302

ModelSim User’s Manual

Page 9

10 - Value Change Dump (VCD) Files (UM-303)

ModelSim VCD commands and VCD tasks . . . . . . . . . . . . . . . . . . . . UM-304

Creating a VCD file . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-306

Flow for four-state VCD file . . . . . . . . . . . . . . . . . . . . . . . . UM-306

Flow for extended VCD file . . . . . . . . . . . . . . . . . . . . . . . . UM-306

Case sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-306

Resimulating a design from a VCD file . . . . . . . . . . . . . . . . . . . . . UM-307

A VCD file from source to output . . . . . . . . . . . . . . . . . . . . . . . . UM-309

VCD simulator commands . . . . . . . . . . . . . . . . . . . . . . . . . UM-309

VCD output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-310

Capturing port driver data . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-312

Supported TSSI states . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-312

Strength values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-313

Port identifier code . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-313

Example VCD output from vcd dumpports . . . . . . . . . . . . . . . . . . UM-314

11 - Tcl and macros (DO files) (UM-315)

UM-9

Tcl features within ModelSim . . . . . . . . . . . . . . . . . . . . . . . . . UM-316

Tcl References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-316

Tcl commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-317

Tcl command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-318

if command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-320

set command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-321

Command substitution . . . . . . . . . . . . . . . . . . . . . . . . . . UM-321

Command separator . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-322

Multiple-line commands . . . . . . . . . . . . . . . . . . . . . . . . . . UM-322

Evaluation order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-322

Tcl relational expression evaluation . . . . . . . . . . . . . . . . . . . . . UM-322

Variable substitution . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-323

System commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-323

List processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-324

ModelSim Tcl commands . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-324

ModelSim Tcl time commands . . . . . . . . . . . . . . . . . . . . . . . . . UM-325

Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-325

Relations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-325

Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-326

Tcl examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-327

Example 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-328

Macros (DO files) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-331

Using Parameters with DO files . . . . . . . . . . . . . . . . . . . . . . . UM-331

Making ma cro parameters optional . . . . . . . . . . . . . . . . . . . . . UM-332

Useful commands for handling breakpoints and errors . . . . . . . . . . . . . . UM-333

ModelSim User’s Manual

Page 10

UM-10 Table of Contents

A - ModelSim variables (UM-335)

Variable settings report . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-336

Personal preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-336

Returning to the original ModelSim defaults . . . . . . . . . . . . . . . . . . . UM-337

Environment variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-337

Creating environment variables in Windo ws . . . . . . . . . . . . . . . . . . UM-339

Referencing environment variables within ModelSim . . . . . . . . . . . . . . UM-340

Removing temp files (VSOUT) . . . . . . . . . . . . . . . . . . . . . . . UM-340

Preference variables located in INI files . . . . . . . . . . . . . . . . . . . . . UM-341

[Library] library path variables . . . . . . . . . . . . . . . . . . . . . . . UM-341

[vcom] VHDL compiler control variables . . . . . . . . . . . . . . . . . . . UM-342

[vlog] Verilog compiler control variabl es . . . . . . . . . . . . . . . . . . . UM-343

[vsim] simulator control variables . . . . . . . . . . . . . . . . . . . . . . UM-344

Commonly used INI variables . . . . . . . . . . . . . . . . . . . . . . . UM-349

Preference variables located in Tcl files . . . . . . . . . . . . . . . . . . . . . UM-352

User-defined variables . . . . . . . . . . . . . . . . . . . . . . . . . . UM-352

More preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-352

Variable precedence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-353

Simulator state variables . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-353

Referencing simulator state variables . . . . . . . . . . . . . . . . . . . . . UM-354

Special considerations for the now variable . . . . . . . . . . . . . . . . . . UM-354

B - ModelSim shortcuts (UM-355)

Wave window mouse and keyboard shortcuts . . . . . . . . . . . . . . . . . . . UM-356

List window keyboard shortcuts . . . . . . . . . . . . . . . . . . . . . . . . UM-357

Command shor t cuts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-358

Mouse and keyboard shortcuts in Main and Source windows . . . . . . . . . . . . . UM-359

Right mouse button . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-360

C - ModelSim messages (UM-361)

ModelSim message sy st e m . . . . . . . . . . . . . . . . . . . . . . . . . . UM-362

Message format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-362

Getting more information . . . . . . . . . . . . . . . . . . . . . . . . . UM-362

Suppressing warning messages . . . . . . . . . . . . . . . . . . . . . . . . . UM-363

Suppressing VCOM warning messages . . . . . . . . . . . . . . . . . . . . UM-363

Suppressing VLOG warning messages . . . . . . . . . . . . . . . . . . . . UM-363

Suppressing VSIM warning messages . . . . . . . . . . . . . . . . . . . . UM-363

Exit codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-364

Miscellaneous messages . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-366

Empty port name warning . . . . . . . . . . . . . . . . . . . . . . . . . UM-366

Lock message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-366

Metavalue detected warning . . . . . . . . . . . . . . . . . . . . . . . . UM-366

ModelSim User’s Manual

Page 11

Sensitivity list warning . . . . . . . . . . . . . . . . . . . . . . . . . . UM-367

Tcl Initialization error 2 . . . . . . . . . . . . . . . . . . . . . . . . . . UM-367

Too few port connections . . . . . . . . . . . . . . . . . . . . . . . . . UM-368

VSIM license lost . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-369

D - System initialization (UM-371)

Files accessed during startup . . . . . . . . . . . . . . . . . . . . . . . . . . UM-372

Environment variables accessed during startup . . . . . . . . . . . . . . . . . . . UM-373

Initialization sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-374

E - Tips and techniques (UM-377)

Running command-line and batch-mode simulations . . . . . . . . . . . . . . . . UM-378

Saving and viewing waveforms in batch mode . . . . . . . . . . . . . . . . . . . UM-379

Setting up libraries for group use . . . . . . . . . . . . . . . . . . . . . . . . UM-379

Using a DO file to test for assertions . . . . . . . . . . . . . . . . . . . . . . . UM-380

Locating assertion warnings . . . . . . . . . . . . . . . . . . . . . . . . . . UM-380

Sampling signals at a clock change . . . . . . . . . . . . . . . . . . . . . . . UM-381

Configuring a List trigger with Expression Builder . . . . . . . . . . . . . . . . . UM-382

Converting signal values to strings . . . . . . . . . . . . . . . . . . . . . . . UM-384

Converting an integer into a bit_vector . . . . . . . . . . . . . . . . . . . . . . UM-385

Detecting infinite zero-delay loops . . . . . . . . . . . . . . . . . . . . . . . UM-386

Referencing source files with location maps . . . . . . . . . . . . . . . . . . . . UM-387

Using location mapping . . . . . . . . . . . . . . . . . . . . . . . . . . UM-387

Pathname syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . UM-388

How location mapping works . . . . . . . . . . . . . . . . . . . . . . . . UM-388

Mapping with Tcl variables . . . . . . . . . . . . . . . . . . . . . . . . UM-388

Performance affected by scheduled events being cancelled . . . . . . . . . . . . . . UM-389

Modeling memory in VHDL . . . . . . . . . . . . . . . . . . . . . . . . . . UM-390

UM-11

Index (UM-401)

ModelSim User’s Manual

Page 12

UM-12

ModelSim User’s Manual

Page 13

1 - Introduction

Chapter contents

Standards supported . . . . . . . . . . . . . . UM-14

Assumptions . . . . . . . . . . . . . . . . UM-14

Sections in this document . . . . . . . . . . . . . UM-14

What is an "HDL item" . . . . . . . . . . . . . UM-16

Text conventions . . . . . . . . . . . . . . . UM-16

What is an "HDL item" . . . . . . . . . . . . . UM-16

This documentation was written for ModelSim version 5.7c for Microsoft Windows 98/

Me/NT/2000/XP. If the ModelSim software you are using is a later release, check the

README file that accompanied the software. Any supplemental information will be there.

UM-13

ModelSim User’s Manual

Page 14

UM-14 1 - Introduction

Standards supported

Assumptions

ModelSim VHDL supports both the IEEE 1076-1987 and 1076-1993 VHDL, the

1164-1993 Standard Multivalue Logic System for VHDL Interoperability, and the

1076.2-1996 Standard VHDL Mathematical Packages standards. A ny design developed

with ModelSim will be compatible with any other VHDL system that is compliant with

either IEEE Standard 1076-1987 or 1076-1993.

ModelSim Verilog is based on IEEE Std 1364-1995 and a partial implementation of

1364-2001 Standard Hardware Description Language Based on the Ve rilog Hardware

Description Language (see /<install_dir>/modeltech/docs/technotes/vlog_2001.note for

implementation details). The Open Verilog International Veri l og LRM version 2.0 is also

applicable to a large extent. Both PLI (Programming Language Interface) and VCD (V alue

Change Dump) are supported for ModelSim PE and SE users.

In addition, all products support SDF 1.0 through 3.0, VITAL 2.2b, VITAL’95 – IEEE

1076.4-1995, and VITAL 2000 – IEEE 1076.4-2000.

We assume that you are familiar with the use of your operating system. If you are not

familiar with Microsoft Windows, we recommend that you work through the tutorials

provided with MS Windows before using ModelSim.

We also assume that you have a working knowledge of VHDL and Verilog. Although

ModelSim is an excellent tool to use while learning HDL concepts and practices, this

document is not written to support that goal.

Finally, we make the assumption that you have worked the appropriate lesson s in the

ModelSim Tutorial and are therefore familiar with the basic functionality of ModelSim.

The ModelSim Tutorial is available from the ModelSim Help menu.

Sections in this document

In addition to this introduction, you will find the following major sections in this document:

2 - Projects (UM-17)

This chapter discusses ModelSim "projects", a container for design files and their

associated simulation properties.

3 - Design libraries

To simulate an HDL design using ModelSim, you need to know how to create,

compile, maintain, and delete design libraries as described in this chapter.

4 - VHDL simulation

This chapter is an overview of compilation and simulation for VHDL within the

Model

Sim environment.

(UM-37)

(UM-49)

ModelSim User’s Manual

5 - Verilog simulation

This chapter is an overview of compilation and simulation for Verilog within the

Model

Sim environment.

(UM-67)

Page 15

Sections in this document UM-15

6 - WLF files (datasets) and virtuals

(UM-117)

This chapter describes datas ets and virtuals - both methods for viewing and organizing

simulation data in Model

7 - Graphic interface

(UM-129)

Sim.

This chapter describes the graphic interface available while operating ModelSim.

Model

Sim’s graphic interface is designed to provide consistency throughout all

operating system environments.

8 - Signal Spy

(UM-269)

This chapter describes Signal Spy, a set of VHDL procedures and Verilog system tasks

that let you monitor, drive, force, or release an item from anywhere in the hierarchy of

a VHDL or mixed design.

9 - Standard Delay Format (SDF) Timing Annotation

(UM-289)

This chapter discusses ModelSim’s implementation of SDF (Standard Delay Format)

timing annotation. Included are sections on VITAL SDF and Verilog SDF, plus

troubleshooting.

10 - Value Change Dump (VCD) Files

(UM-303)

This chapter explains Model Technology’s Verilog VCD implementation for

Model

Sim. The VCD usage is extended to include VHDL designs.

11 - Tcl and macros (DO files)

(UM-315)

This chapter provides an overview of Tcl (tool command language) as used with

Model

Sim.

A - ModelSim variables

(UM-335)

This appendix describes environment, system, and preference variables used in

Model

Sim.

B - ModelSim shortcuts

(UM-355)

This appendix describes ModelSim keyboard and mouse shortcuts.

C - ModelSim messages

(UM-361)

This appendix describes ModelSim error and warning messages.

D - System initialization

(UM-371)

This appendix describes what happens during ModelSim startup.

E - Tips and techniques

(UM-377)

This appendix contains a collection of ModelSim usage examples taken from our

manuals and tech support solutions.

ModelSim User’s Manual

Page 16

UM-16 1 - Introduction

What is an "HDL item"

Text conventions

Because ModelSim works with both VHDL and Verilog, “HDL” refers to either VHDL or

Verilog when a specific language reference is not needed. Depending on the context, “HDL

item” can refer to any of the following:

VHDL block statement, component instantiation, constant, generate

statement, generic, package, signal, or variable

Verilog function, module instantiation, named fork, named begin, net,

task, or register variable

Text conventions used in this manual include:

italic text provides emphasis and sets off filenames, path names, and

design unit names

bold text indicates commands, command options, menu choices,

package and library logical names, as well as variables,

dialog box s elections, and language keywords

monospace type

The right angle (>) is used to connect menu choices when traversing menus as

UPPER CASE denotes file types used by ModelSim (e.g., DO, WLF, INI,

monospace type is used for program and command examples

in: File > Quit

MPF, PDF, etc.)

ModelSim User’s Manual

Page 17

2 - Projects

Chapter contents

Introduction . . . . . . . . . . . . . . . . UM-18

What are projects?. . . . . . . . . . . . . . UM-18

What are the benefits of projects?. . . . . . . . . . UM-18

How do projects differ from pre-5.5 versions? . . . . . . UM-19

Project conversion between versions . . . . . . . . . UM-19

Getting started with projects . . . . . . . . . . . . UM-20

Step 1 — Creating a new project . . . . . . . . . . UM-20

Step 2 — Adding items to the project. . . . . . . . . UM-21

Step 3 — Compiling the files . . . . . . . . . . . UM-21

Step 4 — Simula ting a design. . . . . . . . . . . UM-21

Other basic project operations. . . . . . . . . . . UM-25

The Project tab . . . . . . . . . . . . . . . . UM-26

Sorting the list. . . . . . . . . . . . . . . UM-26

Project tab context menu . . . . . . . . . . . . UM-27

UM-17

Changing compile order . . . . . . . . . . . . . UM-28

Auto-generating compile order . . . . . . . . . . UM-28

Grouping f iles . . . . . . . . . . . . . . . UM-29

Creating a Simulation Configuration . . . . . . . . . . UM-30

Organizing projects with folders . . . . . . . . . . . UM-32

Setting compiler options . . . . . . . . . . . . . UM-34

Accessing projects from the command line . . . . . . . . UM-35

This chapter discusses ModelSim projects. Projects simplify the process of compiling and

simulating a design and are a great tool for getting started with ModelSim.

ModelSim User’s Manual

Page 18

UM-18 2 - Projects

Introduction

What are projects?

Projects are collection entities for HDL designs under specification or test. At a minimum,

projects have a root directory, a work library, and " metadata" which are stored in a .mpf file

located in a project’s root directory. The metadata include compiler switch settings, compile

order, and file mappings. Projects may also include:

• HDL source files or references to source files

• other files such as READMEs or other project documentation

• local libraries

• references to global libraries

• Simulation Configurations (see "Creating a Simulation Config uration"

• Folders (see "Organizing projects with folders" (UM-32))

Important: Project metadata are updated and stored only for actions taken within the

project itself. For example, if you have a file in a project, and you compile that file from

the command line rather than using the project menu commands, the project will not

update to reflect any new compile settings.

What are the benefits of pr ojects?

Projects offer benefits to both new and advanced users. Projects

• simplify interaction with ModelSim; you don’t need to understand the intricacies of

compiler switches and library mappings

• eliminate the need to remember a conceptual model of the design; the compile order is

maintained for you in the project

• remove the necessity to r e-establish compiler switches and settings at each session; these

are stored in the project metadata as are mappings to HDL source files

• allow users to share libraries without copying files to a local directory; you can establish

references to source files that are stored remotely or locally

• allow you to change individual parameters across multiple files; in previous versions you

could only set parameters one file at a time

(UM-30)

ModelSim User’s Manual

• enable "what-if" analysis; you can copy a project, manipulate the settings, and rerun it to

observe the new results

• reload .ini variable settings every time the project is opened; in previous versions you had

to quit ModelSim and restart the program to read in a new .ini file

Page 19

How do projects differ from pre-5.5 versions?

Projects have improved a great deal from version s prior to 5.5. Some of the key diff erences

include:

• A new interface eliminates the need to write custom scripts.

• You don’t have to copy files into a specific directory; you can establish references to files

in any location.

• You don’t have to specify compiler switches; the automatic defaults will work for many

designs. However, if you do want to customi ze the settings, you do it through a dialog

box rather than by writing a script.

• All metadata (compiler settings, compile order, file mappings, etc.) are stored in the

project .mpf file.

Note: Due to the significant changes, pro jects created in versions prior to 5.5 cannot be

converted automatically. If you created a project in an earlier version, you will need to

recreate it in versions later than 5.5. With the new interface even the most complex

project should take less than 15 minutes to recreate. Follow the instructions in the

ensuing pages to recreate your project.

Introduction UM-19

Project conversion between versions

Projects are generally not backwards compatible for either number or letter releases. Wh en

you open a project created in an earlier version (e.g, yo u’re using 5.6 and you open a project

created in 5.5), you’ll see a message warning that the project will be converted to the newer

version. You have the option of continuing with the conversion or cancelling the operation.

As stated in the warning message, a backup of the original project is created before the

conversion occurs. The backup file is named <proj ect name>.mpf.bak an d is created in the

same directory in which the original project is located.

ModelSim User’s Manual

Page 20

UM-20 2 - Projects

Getting started with projects

This section describes the four basic steps to working with a project.

Step 1 — Creating a new project (UM-20)

This creates a .mpf file and a working library.

Step 2 — Adding items to the project (UM-21)

Projects can reference or include HDL source files, folders for organization, simulations,

and any other files you want to associate with the project. You can copy files into the

project directory or simply create mappings to files in other locations.

Step 3 — Compiling the files (UM-24)

This checks syntax and semantics and creates the pseudo machine code ModelSim us es

for simulation.

Step 4 — Simulating a design (UM-25)

This specifies the design unit you want to simulate and op ens a st ructure tab in the Main

window workspace.

Step 1 — Creating a new project

Select File > New > Project (Main window) to create a new project. This opens the Create

Project dialog.

The dialog includes these options:

• Project Name

The name of the new project.

• Project Location

The directory in which the .mpf file will be created.

• Default L ibrary Name

The name of the working library. See "Design library types"

work libraries. You can generally leave the Default Library Name set to "work." The

(UM-39) for more details on

ModelSim User’s Manual

Page 21

workspace

Getting started with projects UM-21

name you specify will be used to create a working library subdirectory within the Project

Location.

After selecting OK, you will see a blank Project tab in the workspace area of the Main

window and the Add Items to the Project dialog.

The name of the current project is shown at the bottom left corner of the Main window.

Step 2 — Adding items to the project

The Add Items to the Project dialog includes these options:

• Create New File

Create a new VHDL, Verilog, Tcl, or text file using the Source window. See below for

details.

• Add Existing File

Add an existing file. See below for details.

• Create Simulation

Create a Simulation Configuration that specifies source files and simulator options. See

"Creating a Simulation Configuration"

• Create New Folder

Create an organization folder. See "Organizing projects with folders"

(UM-30) for details.

(UM-32) for details.

ModelSim User’s Manual

Page 22

UM-22 2 - Projects

Create New File

The Create New File command lets you create a new VHDL, Verilog, Tcl, or text file using

the Source window. You can also access this command by s electing File > Add to Project

> New File (Main window) or right-clicking

The Create Project File dialog includes these options:

• File Nam e

The name of the new file.

• Add file as type

The type of the new file. Select VHDL, Verilog, TCL, or text.

• Folder

The organization folder in which you want the new file placed. You must first create

folders in order to access them here. See "Organizing projects with folders"

(UM-32) for

details.

When you select OK, the Source window opens with an empty file, and the file is listed in

the Project tab of the Main window workspace.

ModelSim User’s Manual

Page 23

Getting started with projects UM-23

Add Existing File

You can also access this command by selecting File > Add to Project > Existing File

(Main window) or by right-clicking

The Add file to Project dialog includes these options:

• File Nam e

The name of the file to add. You can add multiple files at one time.

• Add file as type

The type of the file. "Default" assigns type based on the file extension (e.g., .v is type

Verilog).

• Folder

The organization folder in which you want the file placed. You must first create folders

in order to access them here. See "Organizing projects with folders"

(UM-32) for details.

• Reference from current location/Copy to project directory

Choose whether to reference the file from its current location or to copy it into the project

directory.

When you select OK, the file(s) is listed in the Project tab of the Main window workspace.

ModelSim User’s Manual

Page 24

UM-24 2 - Projects

Step 3 — Compiling the files

The question marks next to the files in the Project tab denote either the files haven’t been

compiled into the project or the source has changed since the last compile. To compile the

files, select Compile > Compile All (Main window) or right click in the Project tab and

select Compile > Compile All.

Once compilation is finished, click the Library tab, expand library work by clicking the "+",

and you’ll see the two compiled design units.

ModelSim User’s Manual

Page 25

Step 4 — Simulating a design

To simulate one of the designs, either double-click the name or right-click the name and

select Simulate. A new tab appears showing the structure of the active simulation.

Getting started with projects UM-25

At this point you are ready to run the simulation and analyze your results. You often do this

by adding signals to the Wave window and running the simulation for a given period of

time. See the ModelSim Tutorial for examples.

Other basic project operations

Open an existing project

If you previously exited ModelSim with a project open, ModelSim automatically will open

that same project upon startup. You can open a different project by selecting File > Open

> Project (Main window).

Close a project

Select File > Close > Project (Main window). This closes the Project tab but leaves the

Library tab open in the workspace. Note that you cannot close a project while a simulation

is in progress.

Delete a project

Select File > Delete > Project (Main window). You cannot delete a project while it is open.

ModelSim User’s Manual

Page 26

UM-26 2 - Projects

The Project tab

The Project tab contains information about the items in your project. By default the tab is

divided into five columns.

Sorting the list

Name – The name of a file or object.

Status – Identifies whether a source file has been successfully compiled. Applies only to

VHDL or Verilog files. A question mark means the file hasn’t been compiled or the source

file has changed since the last successful com pile; an X means the compile failed; a check

mark means the compile succeeded.

Type – The file type as determined by registered file types on Windows or the type y ou

specify when you add the file to the project.

Order – The order in which the file will be compiled when you execute a Compile All

command.

Modified – The date and time of the last modification to the file.

You can hide or show columns by right-clicking on a column title and selecting or

deselecting entries.

You can sort the list by any of the five columns. Click on a column heading to sort by that

column; click the heading again to invert the sort order. An arrow in the column heading

indicates which field the list is sorted by and whether the sort order is descending (down

arrow) or ascending (up arrow).

ModelSim User’s Manual

Page 27

Project tab context menu

Like the other workspace tabs, the Project tab has a context menu that you access by

clicking your right mouse button anywhere in the tab.

The context menu has the following options:

• Edit

Open the selected file in the ModelSim editor.

• Compile > Compile Selected

Compile the selected file(s). Note that if you select a folder and select Compile Selected,

it will compile all files in the folder and any sub-folders.

• Compile > Compile All

Compile all source files included in the project.

• Compile > Compile Out-of-Date

Compile source files that have been modified since the last compile.

• Compile > Compile Order

Set compile order for all files in the project. See "Changing compile order"

more details.

• Compile > Compile Report

Show the compilation history of the selected file.

The Project tab UM-27

(UM-28) for

• Compile > Compile Summary

Show the compilation history of the entire project.

• Compile > Compile Properties

View/change project compiler settings for the selected source file(s).

• Simulate

Load the design unit(s) and associated simulation options from the selected Simulation

Configuration. See "Creating a Simulation Configuration"

(UM-30) for more details.

• Add to Project > New File

Add a new file to the project.

• Add to Project > Existing File

Add an extant file to the project.

• Add to Project > Simulation Configuration

Create a new Simulation Configuration. See "Creating a Simulation Configuration"

for more details.

30)

• Add to Project > Folder

Add an organization folder to the project. See "Organizing projects with folders"

(UM-32)

for more details.

• Remove from Project

Remove the selected item from the project.

• Close Project

Close the active project.

(UM-

• Properties

View/change project compiler settings for the selected source file(s).

ModelSim User’s Manual

Page 28

UM-28 2 - Projects

Changing compile order

When you compile all files in a project, ModelSim by default compiles the files in the order

in which they were added to the project. You have two alternatives for changing the default

compile order: 1) select and compile each file individually; 2) specify a custom compile

order.

To specify a custom compile order, follow these steps:

1 Select Compile > Compile Order (Main window) or select it from the context menu in

the Project tab.

2 Drag the files into the correct order or use the up and down ar row buttons. Note that yo u

can select multiple files and drag them simultaneously.

Auto-generating compile order

The Auto Generate button in the Compile Order dialog (see above) "determines" the

correct compile order by making multiple passes over the files. It starts compiling from the

top; if a file fails to compile due to dependencies, it moves that file to the bottom and then

recompiles it after compiling the rest of the files. It continues in this manner until all files

compile successfully or until a file(s) can’t be compiled for reasons other than depen dency.

ModelSim User’s Manual

Page 29

Grouping files

Changing compile order UM-29

You can group two or more files in the Compile Order dialog so they are sent to the

compiler at the same time. For example, you might have one file with a bunch of Verilog

define statements and a second file that is a Verilog module. You would want to compile

these two files together.

To group files, follow these steps:

1 Select the files you want to group.

2 Click the Group button.

To ungroup files, select the group and click the Ungroup button.

ModelSim User’s Manual

Page 30

UM-30 2 - Projects

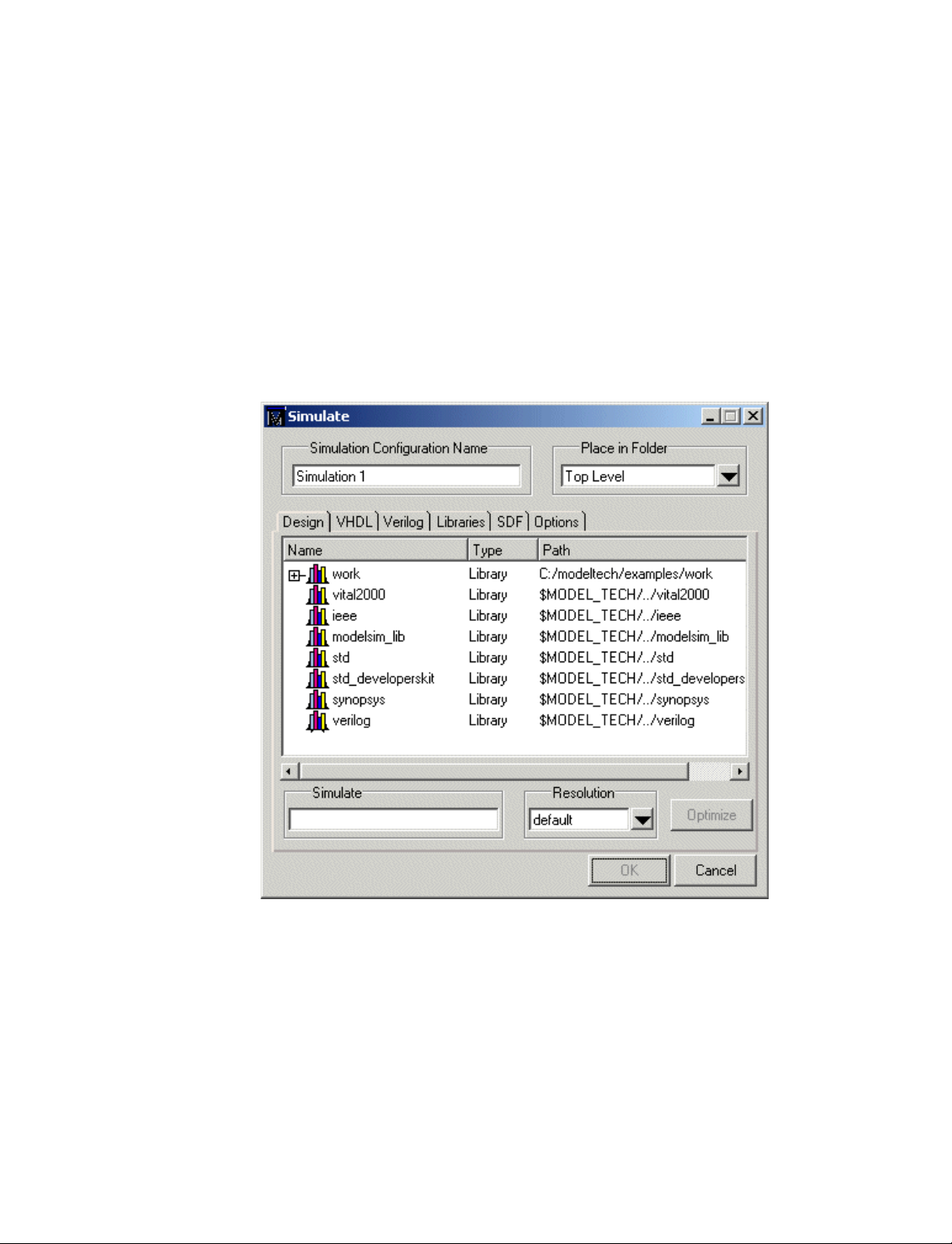

Creating a Simulation Configuration

A Simulation Configuration associates a design unit(s) and its simulation options. For

example, say you routinely load a particular design and you have to specify the simulator

resolution, generics, and SDF timing files. Or dinarily you wou l d have to specify t hose

options each time you load the design. With a Simulation Configuration, you would specify

the design and those options and then save the configuration with a name (e.g., top_config).

The name is then listed in the Project tab and you can double-click it to load the design

along with its options.

To create a Simulation Configuration, follow these steps:

1 Select File > Add to Project > Simulation Configuration ( Main window) o r select it

from the context menu in the Project tab.

ModelSim User’s Manual

2 Specify a name in the Simulation Configuration Name field.

3 Specify the folder in which you want to place the configuration (see Organi zing projects

with folders

4 Select one or more design unit(s) and click Add.

(UM-32)).

Page 31

Creating a Simulation Configu rat io n UM-31

Use the other tabs in the dialog to specify any required simulation options. All of the

5

options in t his dialog are described under "Simulating with the graphic interface"

.

245)

Click OK and the simulation configuration is added to the Project tab.

(UM-

Double-click the object to load it.

ModelSim User’s Manual

Page 32

UM-32 2 - Projects

Organizing projects with folders

Adding a folder

The more files you add to a project, the harder it can be to locate the item you need. You

can add "folders" to the project to organize your files. These folders are akin to directo ries

in that you can have multiple levels of folders and sub-folders. However, no actual

directories are created via the file system–the folders are present only within the project

file.

To add a folder to your project, select File > Add to Project > Folder.

Specify the Folder Name, the location for the folder, and click OK. The folder will be

displayed in the Project tab.

ModelSim User’s Manual

Page 33

Organizing projects with folders UM-33

You use the folders when you add new objects to the project. For example, when you add

a file, you can select which folder to place it in.

If you want to move a file into a folder later on, you can do so using the Properties dialog

for the file (right-click on the file and select Properties from the context menu).

ModelSim User’s Manual

Page 34

UM-34 2 - Projects

Setting compiler options

The VHDL and Verilog compilers (vcom and vlog, respectively) have numerous options

that affect how a design is compiled and subsequently simulated. You can customize the

settings on individual files or a group of files.

Important: Any changes you make to the compile properties outside of the project,

whether from the command line, the GUI, or the modelsim.ini file, will not affect the

properties of files already in the project.

To customize specific files, select the file(s) in the Project tab, right click on the file names,

and select Properties. The resulting dialog varies depending on the number and type of

files you have selected. If you select a single VHDL or Verilog file, you’ll see the General

tab and the VHDL or Verilog tab, respectively. On the General tab, you’ll see file properties

such as Type, Location, and Size. If you select multiple files, the file properties on the

General tab are not listed. Finally, if you select both a VHDL file and a Verilog file, you’ll

see all three tabs but no file information on the General tab.

ModelSim User’s Manual

The General tab includes these options:

• Do Not Compile

Determines whether the file is excluded from the compile.

• Compile to library

Specifies to which library you want to compile the file; defaults to the working library.

• Place in Folder

Specifies the folder in which to place the selected file(s). See "Organizing projects with

folders"

• File Properties

A variety of information about the selected file (e.g, type, size, path). Displays only if a

single file is selected in the Project tab.

The definitions of the options on the VHDL and Verilog tabs can be found in the section

"Setting default compile options"

(UM-32) for details on folders.

(UM-240).

Page 35

Accessing projects from the command line UM-35

When setting options on a group of files, keep in mind the following:

• If two or more files have different settings for the same option, the checkbox in the dialog

will be "grayed out." If you change the option, you cannot change it back to a "multi- state

setting" without cancelling out of the dialog. Once you click OK, ModelSim will set the

option the same for all selected files.

• If you select a combination of VHDL and Verilog files, the options you set on the VHDL

and Verilog tabs apply only to those file types.

Accessing projects from the command line

Generally, projects are used from within the ModelSim GUI. However, standalone tools

will use the project file if they are invoked in the project's root directory. If you want to

invoke outside the project directory, set the MODELSIM environment variable with the

path to the project file (<Project_Root_Dir>/<Project_Name>.mpf).

You can also use the project command

common operations on new projects. The command is to be used outside of a simulation

session.

(CR-104) from the command line to perform

ModelSim User’s Manual

Page 36

UM-36

ModelSim User’s Manual

Page 37

3 - Design libraries

Chapter contents

Design library contents. . . . . . . . . . . . . . UM-38

Design unit information . . . . . . . . . . . . UM-38

Archives . . . . . . . . . . . . . . . . UM-38

Design library types . . . . . . . . . . . . . . UM-39

Working with design libraries . . . . . . . . . . . . UM-40

Creating a library . . . . . . . . . . . . . . UM-40

Managing library contents . . . . . . . . . . . UM-41

Assigning a logical name to a design library . . . . . . . UM-43

Moving a library . . . . . . . . . . . . . . UM-44

Specifying the resource libraries . . . . . . . . . . . UM-45

VHDL resource libraries . . . . . . . . . . . . UM-45

Predefined libraries . . . . . . . . . . . . . UM-46

Alternate IEEE libraries supplied . . . . . . . . . . UM-46

Regenerating your design libraries . . . . . . . . . UM-47

UM-37

Importing FPGA libraries . . . . . . . . . . . . . UM-48

VHDL contains libraries, which are objects that contain compiled design units; libraries

are given names so they may be referenced. Verilog designs simulated with in ModelSim

are compiled into libraries as well.

ModelSim User’s Manual

Page 38

UM-38 3 - Design libraries

Design library contents

Design unit information

A design library is a directory or archive that serves as a repository for compiled design

units. The design units contained in a design library consist of VHDL entities, packages,

architectures, and configurations; and Verilog modules and UDPs (user-defined

primitives). The design units are classified as follows:

• Primary design units

Consist of entities, package declarations, configuration declarations, modules, and

UDPs. Primary design units within a given library must have unique names.

• Secondary design units

Consist of architecture bodies and package bodies. Secondary design units are associated

with a primary design unit. Architectures by the same name can exist if they are

associated with different entities.

The information stored for each design unit in a design library is:

• retargetable, executable code

Archives

• debugging information

• dependency information

By default design libraries are stored in a director y stru cture with a sub-dir ectory fo r each

design unit in the library. Alternatively, you can configure a design library to use archives.

In this case each design unit is stored in its own archive file. To create an archive, use the

-archive argument to the vlib command

Generally you would do this only in the rare case that you hit the reference count limit on

I-nodes due to the ".." entries in the lower-level directories. An example of an error message

that is produced when this limit is hit is:

mkdir: cannot create directory ‘65534’: Too many links

Archives may also have limited value to customers seeking disk space savings.

Note that GMAKE won’t work with these archives on the IBM platform.

(CR-180).

ModelSim User’s Manual

Page 39

Design library types

There are two kinds of design libraries: working libr aries and resource lib raries. A working

library is the library into which a design unit is placed after compilation. A resource library

contains design units that can be referenced within the design unit being compiled. Only

one library can be the working library; in contrast, any number of libraries (including the

working li brary itself) ca n be resource libraries during a compilation.

The library named work has special attributes within ModelSim; it is predefined in the

compiler and need not be declared explicitly (i.e. library work). It is also the library name

used by the compiler as the default destination of compiled design units. In other words the

work library is the working library. In all other aspects it is the same as any other library.

Design library types UM-39

ModelSim User’s Manual

Page 40

UM-40 3 - Design libraries

Working with design libraries

Creating a library

The implementation of a design library is not defined within standard VHDL or Verilog.

Within ModelSim design libraries are implemented as directories and can have any legal

name allowed by the operating system, with one exception; extended identifiers are not

supported for library names.

When you create a project (see "Getting started with projects" (UM-20)), ModelSim

automatically creates a working design library. If you don’t create a project, you need to

create a working design library bef ore yo u run the compiler. This can be done from either

the command line or from the ModelSim graphic interface.

From the ModelSim prompt or a DOS prompt, use this vlib command

vlib <directory_pathname>

To create a new library with the ModelSim graphic interface, select File > New > Library

(Main window).

The Create a New Library dialog box includes these options:

(CR-180):

ModelSim User’s Manual

• Create a new library and a logical mapping to it

Type the new library name into the Library Name field. This creates a library subdirectory in your current working directory, initially mapped to itself. Once created, the

mapped library is easily remapped to a different library.

• Create a map to an existing library

Type the new library name into the Library Name field, then type into the Library

Maps to field or Browse to select a library name for the mapping.

• Library Name

Type the logical name of the new library into this field.

Page 41

• Library Physical Name

Type the physical name of the new library into this field. ModelSim will create a

directory with this name.

• Library Maps to

Type or Browse for a mapping for the specified library. This field is visible and can be

changed only when the Create a map to an ex isting library opti on is selected.

When you cli ck OK, ModelSim creates the specified library directory and writes a

specially-formatted file named _info into that directory. The _info file must remain in the

directory to distinguish it as a ModelSim library.

The new map entry is written to the modelsim.ini file in the [Library] section. See

"[Library] library path variable s"

Note: Remember that a design library is a special kind of directory; the only way to

create a library is to use the ModelSim GUI or the vlib command

libraries using DOS or Windows commands.

Managing library contents

Working with design libraries UM-41

(UM-341) for more information.

(CR-180). Do not create

Library contents can be viewed, deleted, recompiled, edited and so on using either the

graphic interface or command line.

The Library tab in the Main window workspace provides access to design units

(configurations, modules, packages, entities, and architectures) in a library. The listing is

organized hierarchically, and the unit types are identified both by icon (entity (E), module

(M), and so forth) and the Type column.

ModelSim User’s Manual

Page 42

UM-42 3 - Design libraries

The Library tab has a context menu that you access by clicking your right mo use button in

the Library tab.

The context menu includes the following commands:

• Simulate

Loads the selected design unit and opens structure and Files tabs in the workspace.

Related command line command is vsim

(CR-189).

• Edit

Opens the selected design unit in the Source window, or if a library is selected, opens the

Edit Library Mapping dialog (see "Library mappings with the GUI"

(UM-43)).

• Refresh

Rebuilds the library image of the selected library without using source code. Related

command line command is vcom

(CR-145) or with the -refresh argument.

• Recompile

Recompiles the selected design unit. Related command line command is vcom

(CR-145)

or .

• Update

Updates the display of available libraries and design units.

• Delete

Deletes the selected design unit. Related command line command is vdel

(CR-151).

Deleting a package, configuration, or entity will remove the design unit from the library.

If you delete an entity that has one or more architectures, the entity and all its associated

architectures will be deleted.

You can also delete an architecture without deleting its associated entity. Expand the

entity, right-click the desired architecture name, and select Delete. You are prompted for

confirmation before any design unit is actually deleted.

• New

Create a new library.

ModelSim User’s Manual

• Properties

Displays various properties (e.g., Name, Type, Source, etc.) of the selected design unit

or library.

Page 43

Assigning a logical name to a design library

VHDL uses logical library names that can be mapped to ModelSim library directories. By

default, ModelSim can find libraries in your current directory (assuming they have the right

name), but for it to find libraries located elsewhere, you need to map a logical library name

to the pathname of the library.

You can use the GUI, a command, or a pro j ect to assign a log ical name to a d esign library.

Library mappings with the GUI

To associate a logical name with a library, select the library in the workspace, right-click

and select Edit from the context menu. This brings up a dialog box that allows you to edit

the mapping.

Working with design libraries UM-43

The dialog box includes these options:

• Library Mapping N ame

The logical name of the library.

• Library Pathname

The pathname to the library.

Library mapping from the command line

You can issue a command to set the mapping between a logical library name and a

directory; its form is:

vmap <logical_name> <directory_pathname>

You may invoke this command from either a DOS prompt or from the command line within

ModelSim.

When you use vmap

(CR-188) this way you are modifying the modelsim.ini file. You can

also modify modelsim.ini manually by adding a mapping li n e. To do this, use a text editor

and add a line under the [Library] section heading using the syntax:

<logical_name> = <directory_pathname>

ModelSim User’s Manual

Page 44

UM-44 3 - Design libraries

More than one logical name can b e mapped to a single directo ry. For examp le, suppose th e

modelsim.ini file in the current working directory contains following lines:

[Library]

work = /usr/rick/design

my_asic = /usr/rick/design

This would allow you to use either the logical name work or my_asic in a library or use

clause to refer to the same design library.

Moving a library

The vmap command

(CR-188) can also be used to display the mapping of a logical library

name to a directory. To do this, enter the shortened form of the command:

vmap <logical_name>

Library search rules

The system searches for the mapping of a logical name in the following order:

• First the system looks for a modelsim.ini file.

• If the system doesn’t find a modelsim.ini file, or if the specified logical name does not

exist in the modelsim.ini file, the system searches the current working directory for a

subdirectory that matches the logical name.

An error is generated by the compiler if you specify a logical name that does not resolve to

an existing directory.

Individual design units in a design library cannot be moved. An entire design library can

be moved, however, by using standard operating system commands for moving a directory

or an archive.

ModelSim User’s Manual

Page 45

Specifying the resource libraries

Verilog resource libraries

ModelSim supports and encourages separate compilation of distinct portions of a Verilog

design. The vlog

specified library. The library thus contains pre-comp iled modules and UDPs that are

referenced by the simulator as it loads the design. See "Library usage"

Important: Resource libraries are specified differently for Verilog and VHDL. For

Verilog you use either the -L or -Lf argument to vlog

VHDL resource libraries

Within a VHDL source file, you use the VHDL library clause to specify logical names of

one or more resource libraries to be r eferenc ed in the subsequent design unit. Th e scope of

a library clause includes the text region that starts immediately after the library clause an d

extends to the end of the declarative region of the a ssociated design unit. It does not extend

to the next design unit in the file.

(CR-181) compiler is used to compile one or more source files into a

Specifying the resource libraries UM-45

(UM-72).

(CR-181).

Note that the library clause is not used to specify the working library into which the design

unit is placed after compilation; the vcom command

to the current working library. By default, this is the library named work. To change the

current working library, you can use vcom -work and specify the name of the desired target

library.

Default binding rules

A common question related to resource libraries is how ModelSim handles default binding

for components. ModelSim addresses default binding at compile time. When look ing f or

an entity to bind with, ModelSim searches the currently visible libraries for an entity with

the same name as the component. ModelSim does this because IEEE 1076-1987 contained