Page 1

ModelSim

SE

User’s Manual

Version 5.5

Published: 22/Feb/01

The world’s most popular HDL simulator

Page 2

ModelSim /VHDL, ModelSim /VLOG, ModelSim /LNL, and ModelSim /PLUS are

produced by Model Technology Incorporated. Unauthorized copying, duplication,

or other reproduction is prohibited without the written consent of Model

Technology.

The information in this manual is subject to change without notice and does not

represent a commitment on the part of Model Technology. The program described

in this manual is furnished under a license agreement and may not be used or

copied except in accordance with the terms of the agreement. The online

documentation provided with this product may be printed by the end-user. The

number of copies that may be printed is limited to the number of licenses

purchased.

ModelSim is a registered trademark of Model Technology Incorporated. PostScript

is a registered trademark of Adobe Systems Incorporated. UNIX is a registered

trademark of AT&T in the USA and other countries. FLEXlm is a trademark of

Globetrotter Software, Inc. IBM, AT, and PC are registered trademarks, AIX and

RISC System/6000 are trademarks of International Business Machines

Corporation. Windows, Microsoft, and MS-DOS are registered trademarks of

Microsoft Corporation. OSF/Motif is a trademark of the Open Software Foundation,

Inc. in the USA and other countries. SPARC is a registered trademark and

SPARCstation is a trademark of SPARC International, Inc. Sun Microsystems is a

registered trademark, and Sun, SunOS and OpenWindows are trademarks of Sun

Microsystems, Inc. All other trademarks and registered trademarks are the

properties of their respective holders.

Copyright (c) 1990 -2001, Model Technology Incorporated.

All rights reserved. Confidential. Online documentation may be printed by licensed

customers of Model Technology Incorporated for internal business purposes only.

Model Technology Incorporated

10450 SW Nimbus Avenue / Bldg. R-B

Portland OR 97223-4347 USA

phone: 503-641-1340

fax: 503-526-5410

e-mail: support@model.com

home page: http://www.model.com

, sales@model.com

ii

Page 3

Table of Contents

1 - Introduction (1-15)

Performance tools included with ModelSim SE . . . . . . . . . . . . . . . . . . . . 1-16

ModelSim’s graphic interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Standards supported . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Sections in this document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

Command reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

Text conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

What is an "HDL item" . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

Where to find our documentation . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

Download a free PDF reader with Search . . . . . . . . . . . . . . . . . . . . . 1-21

Online References - www.model.com . . . . . . . . . . . . . . . . . . . . . . . . 1-22

Comments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

2 - Projects and system initialization (2-25)

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

How do proje cts differ in version 5.5? . . . . . . . . . . . . . . . . . . . . . . 2-27

Getting started with projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Step 1 — Create a new project . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

Step 2 — Add files to the project . . . . . . . . . . . . . . . . . . . . . . . . 2-31

Step 3 — Compile the files . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

Step 4 — Simulate a design . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Other project operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Customizing project settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Changing compile order . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Setting compiler options . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

Accessing projects from the command line . . . . . . . . . . . . . . . . . . . . . . 2-36

System initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

Files accessed during startup . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

Environment variables accessed during startup . . . . . . . . . . . . . . . . . . . 2-38

Initialization sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-39

3 - Design libraries (3-41)

Design library contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

Design library types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-42

Working with design libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-43

Managing library contents . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-44

Assigning a logical name to a design library . . . . . . . . . . . . . . . . . . . . 3-47

Moving a library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-49

Specifying the resource libraries . . . . . . . . . . . . . . . . . . . . . . . . . . 3-50

Predefined libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-50

ModelSim SE User’s Manual Table of Contents - 3

Page 4

Alternate IEEE libraries supplied . . . . . . . . . . . . . . . . . . . . . . . . 3-51

VITAL 2000 library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-51

Rebuilding supplied libraries . . . . . . . . . . . . . . . . . . . . . . . . . . 3-51

Regenerating your design libraries . . . . . . . . . . . . . . . . . . . . . . . . 3-51

Verilog resource libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-52

Maintaining 32-bit and 64-bit versions in the same library . . . . . . . . . . . . . . 3-52

Importing FPGA libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-53

4 - VHDL Simulation (4-55)

Compiling VHDL designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-57

Invoking the VHDL compiler . . . . . . . . . . . . . . . . . . . . . . . . . 4-57

Dependency checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-57

Simulating VHDL designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-58

Invoking the simulator from the Main window . . . . . . . . . . . . . . . . . . . 4-58

Invoking Code Coverage with vsim . . . . . . . . . . . . . . . . . . . . . . . 4-59

Using the TextIO package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-60

Syntax for file declaration . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-60

Using STD_INPUT and STD_OUTPUT within ModelSim . . . . . . . . . . . . . . 4-61

TextIO implementation issues . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-62

Reading and writing hexadecimal numbers . . . . . . . . . . . . . . . . . . . . 4-63

Dangling pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-63

The ENDLINE function . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-63

The ENDFILE function . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-63

Using alternative input/output files . . . . . . . . . . . . . . . . . . . . . . . 4-64

Providing st imulus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-64

Obtaining the VITAL specification and source code . . . . . . . . . . . . . . . . . . 4-65

VITAL packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-65

ModelSim VITAL compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-66

VITAL compliance checking . . . . . . . . . . . . . . . . . . . . . . . . . . 4-66

VITAL compliance warnings . . . . . . . . . . . . . . . . . . . . . . . . . . 4-66

Compiling and Simulating with accelerated VITAL packages . . . . . . . . . . . . . . . 4-67

Util package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-68

get_resolution() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-68

init_signal_spy() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-69

to_real() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-70

to_time() . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-71

5 - Verilog Simulation (5-73)

Compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-75

Incremental compilation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-76

Library usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-78

Verilog-XL compatible compiler options . . . . . . . . . . . . . . . . . . . . . 5-79

Verilog-XL ‘uselib compiler directive . . . . . . . . . . . . . . . . . . . . . . 5-81

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-84

4 - Table of Contents ModelSim SE User’s Manual

Page 5

Simulation resolution limit . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-84

Event order issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-85

Verilog-XL compatible simulator options . . . . . . . . . . . . . . . . . . . . . 5-86

Compiling for faster performance . . . . . . . . . . . . . . . . . . . . . . . . . . 5-90

Compiling with -fast . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-90

Compiling gate-level designs with -fast . . . . . . . . . . . . . . . . . . . . . . 5-91

Referencing the optimized design . . . . . . . . . . . . . . . . . . . . . . . . 5-92

Enabling design object visibility with the +acc option . . . . . . . . . . . . . . . . 5-94

Using pre-compiled libraries . . . . . . . . . . . . . . . . . . . . . . . . . . 5-96

Cell Libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-97

Delay modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-97

System Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-99

IEEE Std 1364 system tasks . . . . . . . . . . . . . . . . . . . . . . . . . . 5-99

Verilog-XL compatible system tasks . . . . . . . . . . . . . . . . . . . . . . 5-102

$init_signal_spy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-104

Compiler Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-106

IEEE Std 1364 compiler directives . . . . . . . . . . . . . . . . . . . . . . 5-106

Verilog-XL compatible compiler directives . . . . . . . . . . . . . . . . . . . 5-106

Using the Verilog PLI/VPI . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-108

Registering PLI applications . . . . . . . . . . . . . . . . . . . . . . . . . 5-108

Registering VPI applications . . . . . . . . . . . . . . . . . . . . . . . . . 5-110

Compiling and linking PLI/VPI applications . . . . . . . . . . . . . . . . . . . 5-111

The PLI callback reason argument . . . . . . . . . . . . . . . . . . . . . . . 5-117

The sizetf callback function . . . . . . . . . . . . . . . . . . . . . . . . . 5-119

PLI object handles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-119

Third party PLI applications . . . . . . . . . . . . . . . . . . . . . . . . . 5-120

Support for VHDL objects . . . . . . . . . . . . . . . . . . . . . . . . . . 5-121

IEEE Std 1364 ACC routines . . . . . . . . . . . . . . . . . . . . . . . . . 5-122

IEEE Std 1364 TF routines . . . . . . . . . . . . . . . . . . . . . . . . . . 5-123

Verilog-XL compatible routines . . . . . . . . . . . . . . . . . . . . . . . . 5-125

64-bit support in the PLI . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-125

PLI/VPI tracing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-125

6 - Mixed VHDL and Verilog Designs (6-127)

Separate compilers, common libraries . . . . . . . . . . . . . . . . . . . . . . . 6-128

Mapping data types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-128

VHDL generics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-128

Verilog parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-129

VHDL and Verilog ports . . . . . . . . . . . . . . . . . . . . . . . . . . 6-129

Verilog states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-130

VHDL instantiation of Verilog design units . . . . . . . . . . . . . . . . . . . . . 6-132

Component declaration . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-132

vgencomp component declaration . . . . . . . . . . . . . . . . . . . . . . . 6-134

VCD output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-135

Verilog instantiation of VHDL design units . . . . . . . . . . . . . . . . . . . . . 6-136

ModelSim SE User’s Manual Table of Contents - 5

Page 6

7 - Datasets (saved simulations) and virtuals (7-137)

Datasets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-138

Saving a simulation to a dataset . . . . . . . . . . . . . . . . . . . . . . . . 7-138

Opening datasets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-139

Viewing dataset structure . . . . . . . . . . . . . . . . . . . . . . . . . . 7-140

Managing datasets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-142

Using datasets with ModelSim commands . . . . . . . . . . . . . . . . . . . . 7-142

Restricting the dataset prefix display . . . . . . . . . . . . . . . . . . . . . . 7-143

Virtual Objects (User-defined buses, and more) . . . . . . . . . . . . . . . . . . . 7-144

Virtual signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-144

Virtual functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-145

Virtual regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-146

Virtual types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-146

Dataset, logfile, and virtual commands . . . . . . . . . . . . . . . . . . . . . . . 7-147

8 - ModelSim Graphic Interface (8-149)

Window overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-150

Common window features . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-151

Quick access toolbars . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

Drag and Drop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

Command his tory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-152

Automatic window updating . . . . . . . . . . . . . . . . . . . . . . . . . 8-153

Finding names, searching for values, and locating cursors . . . . . . . . . . . . . 8-153

Sorting HDL items . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

Multiple window copies . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

Context menus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

Menu tear of f . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-154

Customizing menus and buttons . . . . . . . . . . . . . . . . . . . . . . . . 8-154

Combining signals into a user-defined bus . . . . . . . . . . . . . . . . . . . 8-154

Tree window hierarchical view . . . . . . . . . . . . . . . . . . . . . . . . 8-155

Main window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-157

Workspace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-158

Transcript . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-159

The Main window menu bar . . . . . . . . . . . . . . . . . . . . . . . . . 8-160

The Main window toolbar . . . . . . . . . . . . . . . . . . . . . . . . . . 8-166

The Main window status bar . . . . . . . . . . . . . . . . . . . . . . . . . 8-168

Mouse and keyboard shortcuts in the Transcript and Source windows . . . . . . . . . 8-168

Dataflow window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-171

Link to active cursor in Wave window . . . . . . . . . . . . . . . . . . . . . 8-171

Dataflow window menu bar . . . . . . . . . . . . . . . . . . . . . . . . . 8-172

Tracing HDL items with the Dataflow window . . . . . . . . . . . . . . . . . . 8-173

Saving the Dataflow window as a Postscript file . . . . . . . . . . . . . . . . . 8-174

List window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

HDL items you can view . . . . . . . . . . . . . . . . . . . . . . . . . . 8-175

The List window menu bar . . . . . . . . . . . . . . . . . . . . . . . . . . 8-176

Setting List window display properties . . . . . . . . . . . . . . . . . . . . . 8-178

6 - Table of Contents ModelSim SE User’s Manual

Page 7

Adding HDL items to the List window . . . . . . . . . . . . . . . . . . . . . 8-180

Editing and formatting HDL items in the List window . . . . . . . . . . . . . . . 8-181

Examining simulation results with the List window . . . . . . . . . . . . . . . . 8-184

Finding items by name in the List window . . . . . . . . . . . . . . . . . . . 8-185

Searching for item values in the List window . . . . . . . . . . . . . . . . . . 8-185

Setting time markers in the List window . . . . . . . . . . . . . . . . . . . . 8-187

List window keyboard shortcuts . . . . . . . . . . . . . . . . . . . . . . . . 8-188

Saving List window data to a file . . . . . . . . . . . . . . . . . . . . . . . 8-189

Process window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-190

The Process window menu bar . . . . . . . . . . . . . . . . . . . . . . . . 8-191

Signals window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8- 193

The Signals window menu bar . . . . . . . . . . . . . . . . . . . . . . . . 8-194

Selecting HDL item types to view . . . . . . . . . . . . . . . . . . . . . . . 8-195

Forcing signal and net values . . . . . . . . . . . . . . . . . . . . . . . . . 8-196

Adding HDL items to the Wave and List windows or a logfile . . . . . . . . . . . . 8-197

Finding HDL items in the Signals window . . . . . . . . . . . . . . . . . . . 8-198

Setting signal breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . 8-198

Defining cl ock signals . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-200

Source window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-201

The Source window menu bar . . . . . . . . . . . . . . . . . . . . . . . . 8-202

The Source window toolbar . . . . . . . . . . . . . . . . . . . . . . . . . 8-204

Setting file-line breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . 8-205

Editing the source file in the Source window . . . . . . . . . . . . . . . . . . . 8-208

Checking HDL item values and descriptions . . . . . . . . . . . . . . . . . . . 8-208

Finding and replacing in the Source window . . . . . . . . . . . . . . . . . . . 8-208

Setting tab stops in the Source window . . . . . . . . . . . . . . . . . . . . . 8-209

Structure window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-210

The Structure window menu bar . . . . . . . . . . . . . . . . . . . . . . . 8-211

Finding items in the Structure window . . . . . . . . . . . . . . . . . . . . . 8-212

Variables window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-213

The Variables window menu bar . . . . . . . . . . . . . . . . . . . . . . . 8-214

Wave window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-216

Pathname pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-216

Values pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-217

Waveform pane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-217

Cursor panes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-218

HDL items you can view . . . . . . . . . . . . . . . . . . . . . . . . . . 8-218

Adding HDL items in the Wave window . . . . . . . . . . . . . . . . . . . . 8-219

The Wave window menu bar . . . . . . . . . . . . . . . . . . . . . . . . . 8-220

The Wave window toolbar . . . . . . . . . . . . . . . . . . . . . . . . . . 8-224

Using Dividers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-227

Splitting Wave window panes . . . . . . . . . . . . . . . . . . . . . . . . 8-228

Combining items in the Wave window . . . . . . . . . . . . . . . . . . . . . 8-229

Editing and formatting HDL items in the Wave window . . . . . . . . . . . . . . 8-230

Setting Wave window display properties . . . . . . . . . . . . . . . . . . . . 8-235

Setting signal breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . 8-236

Finding items by name or value in the Wave window . . . . . . . . . . . . . . . 8-237

Searching for item values in the Wave window . . . . . . . . . . . . . . . . . . 8-237

Using time cursors in the Wave window . . . . . . . . . . . . . . . . . . . . 8-239

ModelSim SE User’s Manual Table of Contents - 7

Page 8

Finding a cursor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-240

Making cursor measurements . . . . . . . . . . . . . . . . . . . . . . . . . 8-240

Zooming - changing the waveform display range . . . . . . . . . . . . . . . . . 8-240

Saving zoom range and scroll position with bookmarks . . . . . . . . . . . . . . 8-241

Wave window mouse and keyboard shortcuts . . . . . . . . . . . . . . . . . . 8-244

Printing and saving wavefo rms . . . . . . . . . . . . . . . . . . . . . . . . 8-245

Compiling with the graphic interface . . . . . . . . . . . . . . . . . . . . . . . 8-250

Locating source errors during compilation . . . . . . . . . . . . . . . . . . . . 8-251

Setting default compile options . . . . . . . . . . . . . . . . . . . . . . . . 8-252

Simulating with the graphic interface . . . . . . . . . . . . . . . . . . . . . . . 8-256

Design selection page . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-257

VHDL settings page . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-259

Verilog settings page . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-261

Libraries settings page . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-262

SDF settings page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-263

SDF options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-264

Setting default simulation options . . . . . . . . . . . . . . . . . . . . . . . 8-265

ModelSim tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-269

The Button Adder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-269

The Macro Helper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-270

The Tcl Debugger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-271

The GUI Expression Builder . . . . . . . . . . . . . . . . . . . . . . . . . 8-275

Graphic interface commands . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-277

Customizing the interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-279

9 - Performance Analyzer (9-281)

Introducing Performance Analysis . . . . . . . . . . . . . . . . . . . . . . . . 9-282

A Statistical Sampling Profiler . . . . . . . . . . . . . . . . . . . . . . . . 9-282

Getting Started . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-283

Interpreting the data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-283

Viewing Performance Analyzer Results . . . . . . . . . . . . . . . . . . . . 9-284

Interpreting the Name Field . . . . . . . . . . . . . . . . . . . . . . . . . 9-286

Interpreting the Under(%) and In(%) Fields . . . . . . . . . . . . . . . . . . . 9-286

Differences in the Ranked and Hierarchical Views . . . . . . . . . . . . . . . . 9-287

Ranked/Hierarchical Profile Window Features . . . . . . . . . . . . . . . . . . . . 9-288

The report option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-289

Setting preferences with Tcl variables . . . . . . . . . . . . . . . . . . . . . . . 9-290

Performance Analyzer commands . . . . . . . . . . . . . . . . . . . . . . . . . 9-290

10 - Code Coverage (10-291)

Enabling Code Coverage . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-292

The coverage_summary window . . . . . . . . . . . . . . . . . . . . . . . . . 10-292

Summary information . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-293

Misses tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-293

8 - Table of Contents ModelSim SE User’s Manual

Page 9

Exclusions tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-293

The coverage_summary window menu bar . . . . . . . . . . . . . . . . . . . 10-294

The coverage_source window . . . . . . . . . . . . . . . . . . . . . . . . . . 10-296

Excluding lines and files . . . . . . . . . . . . . . . . . . . . . . . . . . 10-296

Merging coverage report files . . . . . . . . . . . . . . . . . . . . . . . . . . 10-298

Exclusion filter files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-299

Code Coverage preference variables . . . . . . . . . . . . . . . . . . . . . . . . 10-300

Code Coverage commands . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-300

11 - Waveform Comparison (11-301)

Introducing Waveform Comparison . . . . . . . . . . . . . . . . . . . . . . . . 11-302

Two Modes of Comparison . . . . . . . . . . . . . . . . . . . . . . . . . 11-303

Comparing Hierarchical and Flattened Designs . . . . . . . . . . . . . . . . . . 11-304

Graphical Interface to Waveform Comparison . . . . . . . . . . . . . . . . . . . . 11-305

Opening Dataset Comparison . . . . . . . . . . . . . . . . . . . . . . . . . 11-305

Adding Signals, Regions and/o r Clo cks . . . . . . . . . . . . . . . . . . . . . 11-307

Setting Compare Options . . . . . . . . . . . . . . . . . . . . . . . . . . 11-314

Wave window display . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-316

Printing compare differences . . . . . . . . . . . . . . . . . . . . . . . . . 11-321

List window display . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-322

Command-line interface to Waveform Comparison . . . . . . . . . . . . . . . . . . 11-323

12 - Standard Delay Format (SDF) Timing Annotation (12-325)

Specifying SDF files for simulation . . . . . . . . . . . . . . . . . . . . . . . . 12-326

Instance specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-326

SDF specification with the GUI . . . . . . . . . . . . . . . . . . . . . . . . 12-327

Errors and warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-327

VHDL VITAL SDF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-328

SDF to VHDL generic matching . . . . . . . . . . . . . . . . . . . . . . . 12-328

Resolving errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-329

Verilog SDF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-330

The $sdf_annotate system task . . . . . . . . . . . . . . . . . . . . . . . . 12-330

SDF to Verilog construct matching . . . . . . . . . . . . . . . . . . . . . . 12-331

Optional edge specifications . . . . . . . . . . . . . . . . . . . . . . . . . 12-333

Optional conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-334

Rounded timing values . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-335

SDF for Mixed VHDL and Verilog Designs . . . . . . . . . . . . . . . . . . . . . 12-336

Interconnect delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-336

Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-337

Mistaking a component or module name for an instance label . . . . . . . . . . . . 12-338

Forgetting to specify the instance . . . . . . . . . . . . . . . . . . . . . . . 12-338

Obtaining the SDF specification . . . . . . . . . . . . . . . . . . . . . . . . . 12-339

ModelSim SE User’s Manual Table of Contents - 9

Page 10

13 - Value Change Dump (VCD) Files (13-341)

ModelSim VCD commands and VCD tasks . . . . . . . . . . . . . . . . . . . . . 13-342

Resimulating a VHDL design from a VCD file . . . . . . . . . . . . . . . . . . . 13-344

Specifying a filename and state mappings . . . . . . . . . . . . . . . . . . . . 13-344

Creating the VCD file . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-344

A VCD file from source to output . . . . . . . . . . . . . . . . . . . . . . . . . 13-346

VCD simulator commands . . . . . . . . . . . . . . . . . . . . . . . . . . 13-346

VCD output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-347

Capturing port driver data . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-349

Supported TSSI states . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-349

Strength values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-350

Port identifier code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-350

Example VCD output from vcd dumpports . . . . . . . . . . . . . . . . . . . 13-351

14 - Logic Modeling SmartModels (14-353)

VHDL SmartModel interface . . . . . . . . . . . . . . . . . . . . . . . . . . 14-354

Creating foreign architectures with sm_entity . . . . . . . . . . . . . . . . . . 14-355

Vector ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-357

Command channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-358

SmartModel Windows . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-359

Memory arrays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-360

Verilog SmartModel interface . . . . . . . . . . . . . . . . . . . . . . . . . . 14-361

LMTV usage documentation . . . . . . . . . . . . . . . . . . . . . . . . . 14-361

Linking the LMTV interface to the simulator . . . . . . . . . . . . . . . . . . 14-361

Compiling Verilog shells . . . . . . . . . . . . . . . . . . . . . . . . . . 14-361

15 - Logic Modeling Hardware Models (15-363)

VHDL Hardware Model interface . . . . . . . . . . . . . . . . . . . . . . . . . 15-364

Creating foreign architectures with hm_entity . . . . . . . . . . . . . . . . . . 15-365

Vector ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-367

Hardware model commands . . . . . . . . . . . . . . . . . . . . . . . . . 15-368

16 - Tcl and ModelSim (16-369)

Tcl features within ModelSim . . . . . . . . . . . . . . . . . . . . . . . . . . 16-370

Tcl References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-370

Tcl commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-371

Tcl command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-372

if command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-374

set command syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-375

Command substitution . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-375

Command separator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-376

Multiple-line commands . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-376

Evaluation order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-376

10 - Table of Contents ModelSim SE User’s Manual

Page 11

Tcl relational expression evaluation . . . . . . . . . . . . . . . . . . . . . . 16-376

Variable substitution . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-377

System commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-377

List processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-378

ModelSim Tcl commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-378

ModelSim Tcl time commands . . . . . . . . . . . . . . . . . . . . . . . . . . 16-379

Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-379

Relations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-379

Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-380

Tcl examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-381

Example 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-382

A - Technical Support, Updates, and Licensing (A-385)

Technical support - electronic . . . . . . . . . . . . . . . . . . . . . . . . . . A-386

Mentor Graphics customers . . . . . . . . . . . . . . . . . . . . . . . . . A-386

Technical support - telephone . . . . . . . . . . . . . . . . . . . . . . . . . . A-387

Mentor Graphics customers in North America . . . . . . . . . . . . . . . . . . A-387

Mentor Graphics customers outside North America . . . . . . . . . . . . . . . . A-387

Technical support - other channels . . . . . . . . . . . . . . . . . . . . . . . . A-387

Updates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-388

Online References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-388

FLEXlm Licenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-389

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-390

B - ModelSim Variables (B-391)

Variable settings report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-392

Personal preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-392

Returning to the original ModelSim defaults . . . . . . . . . . . . . . . . . . . . B-392

Environment variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-393

Setting environment variables in Windows . . . . . . . . . . . . . . . . . . . B-394

Referencing environment variables within ModelSim . . . . . . . . . . . . . . . B-395

Removing temp files (VSOUT) . . . . . . . . . . . . . . . . . . . . . . . . B-395

Preference variables located in INI files . . . . . . . . . . . . . . . . . . . . . . B-396

[Library] library path variables . . . . . . . . . . . . . . . . . . . . . . . . B-396

[vcom] VHDL compiler control variables . . . . . . . . . . . . . . . . . . . . B-396

[vlog] Verilog compiler control variabl es . . . . . . . . . . . . . . . . . . . . B-398

[vsim] simulator control variables . . . . . . . . . . . . . . . . . . . . . . . B-398

[lmc] Logic Modeling variables . . . . . . . . . . . . . . . . . . . . . . . . B-402

Setting variables in INI files . . . . . . . . . . . . . . . . . . . . . . . . . B-402

Reading variable values from the INI file . . . . . . . . . . . . . . . . . . . . B-402

Variable functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-403

Preference variables located in TCL files . . . . . . . . . . . . . . . . . . . . . . B-406

User-defined variables . . . . . . . . . . . . . . . . . . . . . . . . . . . B-406

ModelSim SE User’s Manual Table of Contents - 11

Page 12

More preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-406

Preference variable loading order . . . . . . . . . . . . . . . . . . . . . . . . . B-407

Simulator state variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-408

Referencing simulator state variables . . . . . . . . . . . . . . . . . . . . . . B-408

C - ModelSim Shortcuts (C-409)

Wave window mouse and keyboard shortcuts . . . . . . . . . . . . . . . . . . C-410

List window keyboard shortcuts . . . . . . . . . . . . . . . . . . . . . . . . C-411

Command shor tcuts . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-412

Command history shortcuts . . . . . . . . . . . . . . . . . . . . . . . . . C-412

Mouse and keyboard shortcuts in the Transcript and Source windows . . . . . . . . . C-413

Right mouse button . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-415

D - Using the FLEXlm License Manager (D-417)

Starting the license server daemon . . . . . . . . . . . . . . . . . . . . . . . . D-418

Controlling the license file search . . . . . . . . . . . . . . . . . . . . . . . D-418

Manual start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-418

Automatic start at boot time . . . . . . . . . . . . . . . . . . . . . . . . . D-419

What to do if another application uses FLEXlm . . . . . . . . . . . . . . . . . D-419

Format of the license file . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-420

Format of the daemon options file . . . . . . . . . . . . . . . . . . . . . . . . . D-420

License administration tools . . . . . . . . . . . . . . . . . . . . . . . . . . . D-422

lmdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-422

lmremove . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-423

lmreread . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-423

Administr ation tools for Windows . . . . . . . . . . . . . . . . . . . . . . . D-423

E - Tips and Techniques (E-425)

How to use checkpoint/restore . . . . . . . . . . . . . . . . . . . . . . . . . . E-426

The difference between checkpoint/restore and restarting . . . . . . . . . . . . . . E-427

Using macros with restart and checkpoint/restore . . . . . . . . . . . . . . . . . E-427

Running command-line and batch-mode simulations . . . . . . . . . . . . . . . . . E-428

Command-line mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-428

Batch mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-429

Using macros (DO files) . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-430

Using Parameters with DO files . . . . . . . . . . . . . . . . . . . . . . . . E-430

Source code security and -nodebug . . . . . . . . . . . . . . . . . . . . . . . . E-433

Saving and viewing waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . E-434

Setting up libraries for group use . . . . . . . . . . . . . . . . . . . . . . . . . E-434

Maintaining 32-bit and 64-bit modules in the same library . . . . . . . . . . . . . . . E-434

Bus contention checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-435

Bus float checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-435

12 - Table of Contents ModelSim SE User’s Manual

Page 13

Design stability checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-436

Toggle checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-436

Detecting infinite zero-delay loops . . . . . . . . . . . . . . . . . . . . . . . . E-436

Referencing source files with location maps . . . . . . . . . . . . . . . . . . . . . E-437

Using location mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . E-437

Pathname syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-438

How location mapping works . . . . . . . . . . . . . . . . . . . . . . . . . E-438

Mapping with Tcl variables . . . . . . . . . . . . . . . . . . . . . . . . . E-438

Accelerate simulation by locking memory under HP-UX 10.2 . . . . . . . . . . . . . . E-439

Modeling memory in VHDL . . . . . . . . . . . . . . . . . . . . . . . . . . . E-440

Setting up a List trigger with Expression Builder . . . . . . . . . . . . . . . . . . . E-444

F - What’s new in ModelSim (F-447)

New features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . F-447

Command and variable changes . . . . . . . . . . . . . . . . . . . . . . . . F-448

Documentation changes . . . . . . . . . . . . . . . . . . . . . . . . . . . F-449

GUI changes in version 5.5 . . . . . . . . . . . . . . . . . . . . . . . . . . . F-450

Main window changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . F-451

Signals window changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . F-457

Source window changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . F-458

Wave window changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . F-459

Coverage_summary window changes . . . . . . . . . . . . . . . . . . . . . . . F-461

License Agreement (463)

Index (469)

ModelSim SE User’s Manual Table of Contents - 13

Page 14

14 - Table of Contents ModelSim SE User’s Manual

Page 15

1 - Introduction

Chapter contents

Performance tools included with ModelSim SE . . . . . . . 1-16

ModelSim’s graphic interface . . . . . . . . . . . . 1-16

Standards supported . . . . . . . . . . . . . . 1-17

Assumptions . . . . . . . . . . . . . . . . 1-17

Sections in this document . . . . . . . . . . . . . 1-18

Command reference . . . . . . . . . . . . . . 1-19

Text conventions . . . . . . . . . . . . . . . 1-20

What is an "HDL item" . . . . . . . . . . . . . 1-20

Where to find our documentation . . . . . . . . . . . 1-21

Online References - www.model.com . . . . . . . . . . 1-22

Comments . . . . . . . . . . . . . . . . . 1-23

This documentation was written for ModelSim SE version 5.5 for UNIX and Microsoft

Windows 95/98/ME/NT/2000 (see note below for exception). If the ModelSim software

you are using is a later release, check the README file that accompanied the software.

Any supplemental information will be there.

Although this document covers both VHDL and Verilog simulation, you will find it a

useful reference for single HDL design work.

ModelSim SE User’s Manual Introduction 1-15

Page 16

Performance tools included with ModelSim SE

Performance tools included with ModelSim SE

All ModelSim SE versions include the followin g performance tools:

• Performance Analyzer

Identifies areas in your simulation where performance can be improved.

Note: Performance Analyzer will not operate on Windows 95.

• Code Coverage

Gives you graphical and report file feedback on how the source code is being executed.

(9-281)

(10-291)

ModelSim’s graphic interface

While your operating system interface provides the window-management frame,

ModelSim controls all internal-window features including menus, buttons, and scroll bars.

The resulting simulator interface remains consistent within these operating systems:

• SPARCstation with OpenWindows, OSF/Motif, or CDE

• IBM RISC System/6000 with OSF/Motif

• Hewlett-Packard HP 9000 Series 700 with HP VUE, OSF/Motif, or CDE

• Linux (Red Hat v. 6.0 or later) with KDE or GNOME

• Microsoft Windows 95/98/ME/NT/2000

Because ModelSim’s graphic interface is based on Tcl/TK, you also have the tools to build

your own simulation environment. Preference variables and configuration commands,

"Preference variables located in INI files"

give you control over the use and placement of windows, menus, menu options and

277)

buttons. See "Tcl and ModelSim"

For an in-depth look at ModelSim’s graphic interface see, Chapter 8 - ModelSim Graphic

Interface.

(B-396), and "Graphic interface commands" (8-

(16-369) for more information on Tcl.

1-16 Intr oduction ModelSim SE User’s Manual

Page 17

Standards supported

ModelSim VHDL supports both the IEEE 1076-1987 and 1076-1993 VHDL, the

1164-1993 Standard Multivalue Logic System for VHDL Interoperability, and the

1076.2-1996 Standard VHDL Mathematical Packages standards . A ny design devel oped

with ModelSim will be compatible with any other VHDL system that is compliant with

either IEEE Standard 1076-1987 or 1076-1993.

ModelSim Verilog is base d on the IEEE Std 1 364 Standard Hard ware Description

Language Based on the Verilog Hardware Description Language. The Open Verilog

International Verilog LRM version 2.0 is also applicable to a large extent. Both PLI

(Programming Language Interface) and VCD (Value Change Dump) are supported for

ModelSim PE and SE users.

In addition, all products support SDF 1.0 through 3.0, VITAL 2.2b, VITAL’95 - IEEE

1076.4-19 95, and VITAL 2000.

Assumptions

We assume that you are familiar with the use of your operating system. You should also be

familiar with the window management functions of your graphic interface: either

OpenWindows, OSF/Motif, CDE, HP VUE, KDE, GNOME, or

Microsoft Windows 95/98/ME/NT/2000.

Standards supported

We also assume that you have a working knowledge of VHDL and Verilog. Although

ModelSim is an excellent tool to use while learning HDL concepts and practices, this

document is not written to support that goal. If you need more information about HDLs,

check out our Online References - www.model.com

Finally, we make the assumption that you have worked the appropriate lesson s in the

ModelSim Tutorial or the Quick Start and are therefore familiar with the basic functionality

of ModelSim. The M od e lSim Tutorial and Quick Start are both available from the

ModelSim Help menu. The ModelSim Tutorial is also available from the Support page of

our web site : www.model.com

For installation instructions please refer to the Start Here for Mod elSim guide that was

shipped with the ModelSim CD. Start Here may also be downloaded from our

website: www.model.com

.

.

(1-22).

ModelSim SE User’s Manual Introduction 1-17

Page 18

Sections in this document

Sections in this document

In addition to this introduction, you will find the following major sections in this document:

2 - Projects and system initialization (2-25)

This chapter provides a definition of a ModelSim "project" and discusses the use of a

new file extension for project files.

3 - Design libraries

(3-41)

To simulate an HDL design using ModelSim, you need to know how to create,

compile, maintain, and delete design libraries as described in this chapter.

4 - VHDL Simulation

(4-55)

This chapter is an overview of compilation and simulation for VHDL within the

ModelSim environment.

5 - Verilog Simulation

(5-73)

This chapter is an overview of compilation and simulation for Verilog within the

ModelSim environment.

6 - Mixed VHDL and Verilog Designs

(6-127)

ModelSim/Plus single-kernel simulation (SKS) allows you to simulate designs that are

written in VHDL and/or Verilog. This chapter outlines data mapping and the criteria

established to instantiate design units between HDLs.

7 - Datasets (saved simulations) and virtuals

(7-137)

This chapter describes datas ets and virtuals - both methods for viewing and organizing

simulation data in ModelSim.

8 - ModelSim Graphic Interface

(8-149)

This chapter describes the graphic interface available while operating ModelSim.

ModelSim’s graphic interface is designed to provide consistency throughout all

operating system environments.

9 - Performance Analyzer

(9-281)

This chapter describes how the ModelSim Performance Analyzer is used to easily

identify areas in your simulation where performance can be improved.

10 - Code Coverage (10-291)

This chapter describes the Code C overage feature. Code Cover age gives you graphical

and report file feedback on how the source code is being executed.

11 - Waveform Comparison

(11-301)

This chapter describes Waveform Comparison, a feature that lets you compare

simulations.

12 - Standard Delay Format (SDF) Timing Annotation

(12-325)

This chapter discusses ModelSim’s implementation of SDF (Standard Delay Format)

timing annotation. Included are sections on VITAL SDF and Verilog SDF, plus

troubleshooting.

1-18 Intr oduction ModelSim SE User’s Manual

Page 19

Command reference

13 - Value Change Dump (VCD) Files

(13-341)

This chapter explains Model Technology’s Verilog VCD implementation for

ModelSim. The VCD usage is extended to include VHDL designs.

14 - Logic Modeling SmartModels

(14-353)

This chapter describes the use of th e Sm artM odel Li br ary an d S martModel Windows

with ModelSim.

15 - Logic Modeling Hardware Models

(15-363)

This chapter describes the use the Logic Modeling Hardware Modeler w ith ModelSim.

16 - Tcl and ModelSim

(16-369)

This chapter provides an overview of Tcl (tool command language) as used with

ModelSim. Additional Tcl and Tk (Tcl’s toolkit) informatio n can be found thr ough

several Tcl online references

A - Technical Support, Updates, and Licensing

(16-370).

(A-385)

This appendix describes how and where to get technical support and updates and

licensing for ModelSim. It also contains links to the Model Technology web site and

references to books, organizations, and companies involved in EDA and simulation.

B - ModelSim Variables

(B-391)

This appendix describes environment, system and preference variables used in

ModelSim.

C - ModelSim Shortcuts

This appendix describes ModelSim keyboard and mouse shortcuts.

D - Using the FLEXlm License Manager

This appendix covers Model Technology’s application of FLEXlm for ModelSim

licensing.

E - Tips and Techniques

This appendix contains an extended collection of ModelSim usage examples taken

from our manuals, and tech support solutions.

F - What’s new in ModelSim

This appendix lists new features and changes in the various versions of ModelSim.

Command reference

The complete command reference for all ModelSim c ommands is located in the ModelSim

Command Reference. Command Reference cross reference page numbers are prefixed with

"CR" (e.g.,"ModelSim Commands"

(C-409)

(D-417)

(E-425)

(F-447)

(CR-9)).

ModelSim SE User’s Manual Introduction 1-19

Page 20

Text conventions

Text conventions

Text conventions used in this manual include:

italic text provides emphasis and sets off filenames, path names, and

bold text indicates commands, command options, menu choices,

design unit names

package and library logical names, as well as variables and

dialog box s election

monospace type

The right angle (>) is used to connect menu choices when traversing menus as

path separa t ors examples wil l show either UNIX or Windows path

UPPER CASE denotes file types used by ModelSim (e.g., DO, WLF, INI,

What is an "HDL item"

Because ModelSim works with both VHDL and Verilog, “HDL” refers to either VHDL or

Verilog when a specific language reference is not needed. Depending on the context, “HDL

item” can refer to any of the following:

VHDL block statement, component instantiation, constant, generate

Verilog function, module instantiation, named fork, named begin, net,

monospace type is used for program and command examples

in: File > Save

separators - use separators appropriate for your operating

system when trying the examples

MPF, PDF, etc.)

statement, generic, package, signal, or variable

task, or register variable

1-20 Intr oduction ModelSim SE User’s Manual

Page 21

Where to find our documentation

ModelSim documentation is available from our website at

model.com/support/documentation.asp

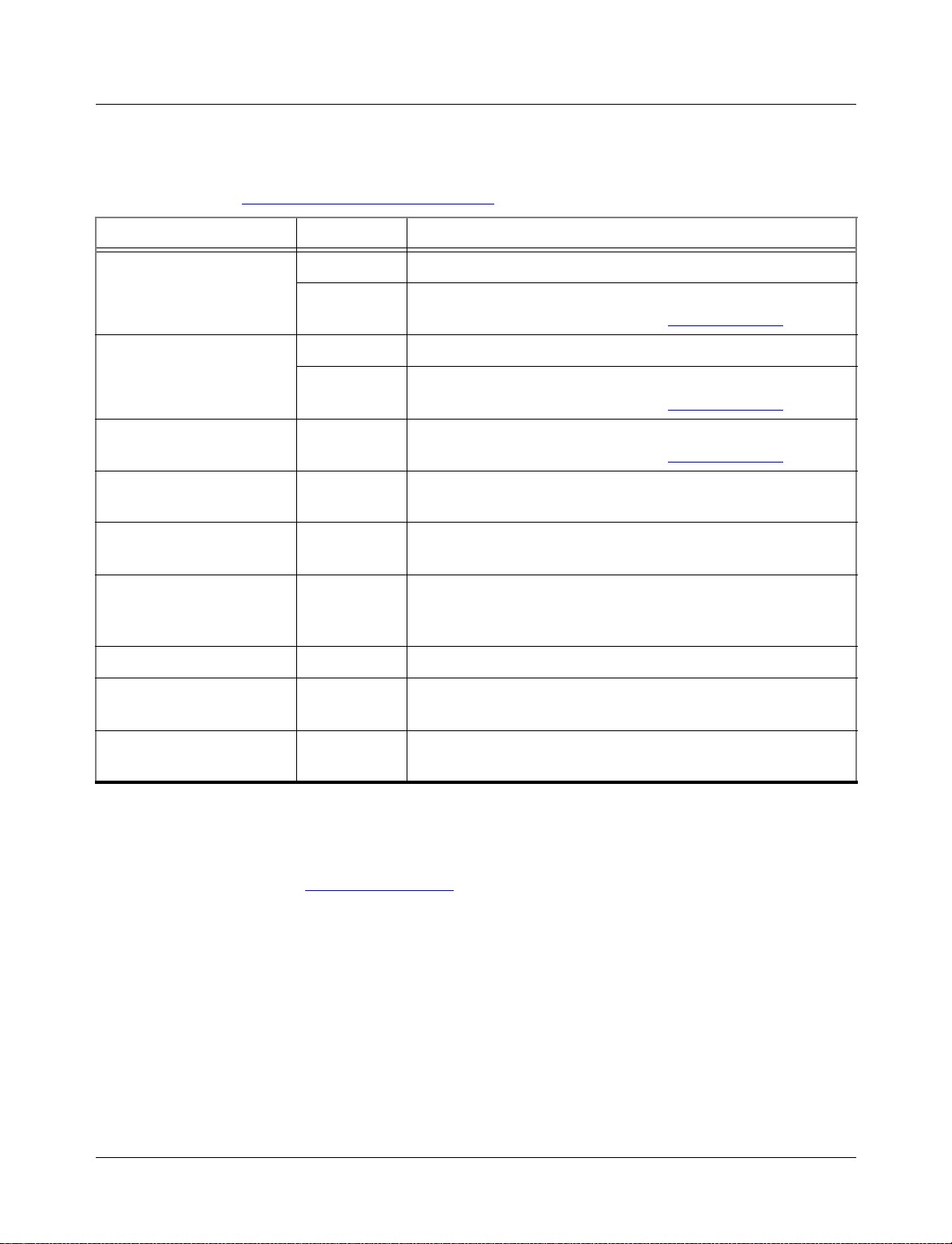

Document Format How to get it

Where to find our documentation

or in the following formats and locations:

Start Here for ModelSim SE

(installation & support

reference)

ModelSim SE Quick Guide

(command and feature

quick-reference)

ModelSim SE Tutorial PDF, HTML select Main window > Help > SE Documentation; also available

ModelSim SE User’s

Manual

ModelSim SE Command

Reference

ModelSim Foreign

Language Int erface

Reference

ModelSim Command Help ASCII type

Tcl Man Pages (Tcl

manual)

paper shipped with ModelSim

PDF select Main window > Help > SE Documentation; also available

from the Support page of our web site: www.model.com

paper shipped with ModelSim

PDF select Main window > Help > SE Documentation, also available

from the Support page of our web site: www.model.com

from the Support page of our web site: www.model.com

PDF, HTML select Main win dow > Help > SE Documentation

PDF, HTML select Main win dow > Help > SE Documentation

PDF, HTML select Main win dow > Help > SE Documentation

help [command name] at the prompt in the Main window

HTML select Main window > Help > Tcl Man Pages, or find

contents.htm in \modeltech\tcl_help_html

technotes ASCII select Main window > He lp > Technotes, or located in the

\modeltech\docs\technotes directory

Download a free PDF reader with Search

Model Technology’s PDF documentation requires an Adobe Acrobat Reader fo r viewing .

The Reader may be installed from the ModelSim CD. It is also available withou t cost from

Adobe at http:

take advantage of the index file supplied with our documentation; the index makes

searching for key words much faster.

ModelSim SE User’s Manual Introduction 1-21

//www.adobe.com. Be sure to download the Acrobat Reader with Search to

Page 22

Online References - www.model.com

Online References - www.model.com

The Model Technology w eb site includes li nks to support, softwar e d ownl oad s, an d many

EDA information sources. Check the links below for the most current information.

Latest version email

Place your name on our list for email notification of new releases and updates.

model.com/support/register_news_list.asp

News

Current news of Model Technology within the EDA industry.

model.com/news_events/default.asp

Partners

Model Technology’s value added partners, OEM partners, FPGA partners, ASIC

partners, and training partners.

model.com/partners/default.asp

Products

A complete collection of Model Technology product information.

model.com/products/default.asp

Technical Documents

Technical notes, application notes, FAQs.

model.com/resources/techdocs.asp

Sales

Locate ModelSim sales contacts anywhere in the world.

model.com/contact_us.asp

Support

Model Technology email support and software downloads.

model.com/support/default.asp

1-22 Intr oduction ModelSim SE User’s Manual

Page 23

Comments

Comments

Comments and questions about this manual and ModelSim software are welcome. Call,

write, fax or email:

Model Technology Incorporated

10450 SW Nimbus Avenue, Bldg. R-B

Portland, OR 97223-4347 USA

phone: 503-641-1340

fax: 503-526-5410

email: manuals@model.com

home page: http://www.model.com

ModelSim SE User’s Manual Introduction 1-23

Page 24

1-24 I ntroduction M odelSim SE User’s Manual

Page 25

2 - Projects and system initialization

Chapter contents

Introduction . . . . . . . . . . . . . . . . 2-26

What are projects?. . . . . . . . . . . . . . 2-26

What are the benefits of projects?. . . . . . . . . . 2-26

How do proje cts differ in version 5.5? . . . . . . . . 2-27

Getting started with projects . . . . . . . . . . . . 2-28

Step 1 — Create a new project . . . . . . . . . . 2-29

Step 2 — Add files to the project . . . . . . . . . . 2-31

Step 3 — Compile the files . . . . . . . . . . . 2-31

Step 4 — Simulate a design . . . . . . . . . . . 2-31

Other project operations . . . . . . . . . . . . 2-33

Customizing project settings . . . . . . . . . . . . 2-34

Changing compile order . . . . . . . . . . . . 2-34

Setting compiler options . . . . . . . . . . . . 2-35

Accessing projects from the command line . . . . . . . . 2-36

System initialization . . . . . . . . . . . . . . 2-37

Files accessed during startup . . . . . . . . . . . 2-37

Environment variables accessed during startup . . . . . . 2-38

Initialization sequence. . . . . . . . . . . . . 2-39

This chapter discusses ModelSim projects. Projects greatly simplify the process of

compiling and simulating a design and are a great tool for getting started with ModelSim.

This chapter also includes a section on ModelSim initialization.

ModelSim SE User’s Manual Projects and system initialization 2-25

Page 26

Introduction

Introduction

What are projects?

Projects are collection entities for HDL designs under specification or test. At a minimum

projects have a root directory, a work libr ary, and "metadata" which are stored in a .mpf file

located in a project’s root directory. The metadata include compiler switch settings, compile

order, and fil e mappings. Projects may also consist of:

• HDL source files or references to source files

• other files such as READMEs or other project documentation

• local libraries

• references to global libraries

What are the benefits of pr ojects?

Projects offer benefits to both new and advanced users. Projects

• simplify interaction with ModelSim; you don’t need to understand the intricacies of

compiler switches and library mappings

• eliminate the need to remember a conceptual model of the design; the compile order is

maintained for you in the project

• remove the necessity to re-establish compiler switches and settings at each session; these

are stored in the project metadata as are mappings to HDL source files

• allow users to share libraries without copying f iles to a local directory; you can establish

references to source files that are stored remotely or locally

• allow you to change individual parameters across multiple files; in previous versions you

could only set parameters one file at a time

• enable "what-if" analysis; you can copy a project, manipulate the settings, and rerun it to

observe the new results

• reload .ini variable settings every time the project is opened; in previous versions you h ad

to quit ModelSim and restart the program to read in a new .ini file

2-26 Pr ojects and system initialization ModelSim SE User’s Manual

Page 27

How do projects differ in version 5.5?

Projects have improved a great deal from earlier versions. Some of the key differences

include:

• A new interface eliminates the need to write custom scripts.

• You don’t have to copy files into a specific directory; you can establish references to files

in any location.

• You don’t have to specify compiler switches; the automatic defaults will work for many

designs. However, if you do want to customi ze the settings, you do it through a dialog

box rather than by writing a script.

• All metadata (compiler settings, compile order, file mappings) are stored in the project

.mpf file.

Important: Due to the significant changes, projects created in versions prior to 5.5 cannot

be converted automatically. If you created a project in an earlier version, you will need to

recreate it in version 5.5. With the new interface even the most complex p roject should take

less than 15 minutes to recreate. Follow the instructions in the ensuing pages to recreate

your project.

Introduction

ModelSim SE User’s Manual Projects and system initialization 2-27

Page 28

Getting started with projects

Getting started with projects

This section describes the four basic steps to working with a project. For a discussion of

more advanced project features, see

"Customizing project settings" (2-34).

Step 1 — Create a new project

This creates a .mpf file and a working library.

Step 2 — Add files to the project (2-31)

Projects can reference or include HDL source files and any other files you want to

associate with the project. You can copy files into the project directory or simply create

mappings to files in other locations.

Step 3 — Compile the files (2-32)

This checks syntax and semantics and creates the pseudo machine code ModelSim uses

for simulation.

Step 4 — Simulate a design (2-33)

This specifies the design unit you want to simulate and opens a structure page in the

workspace.

(2-29)

2-28 Pr ojects and system initialization ModelSim SE User’s Manual

Page 29

Step 1 — Create a new project

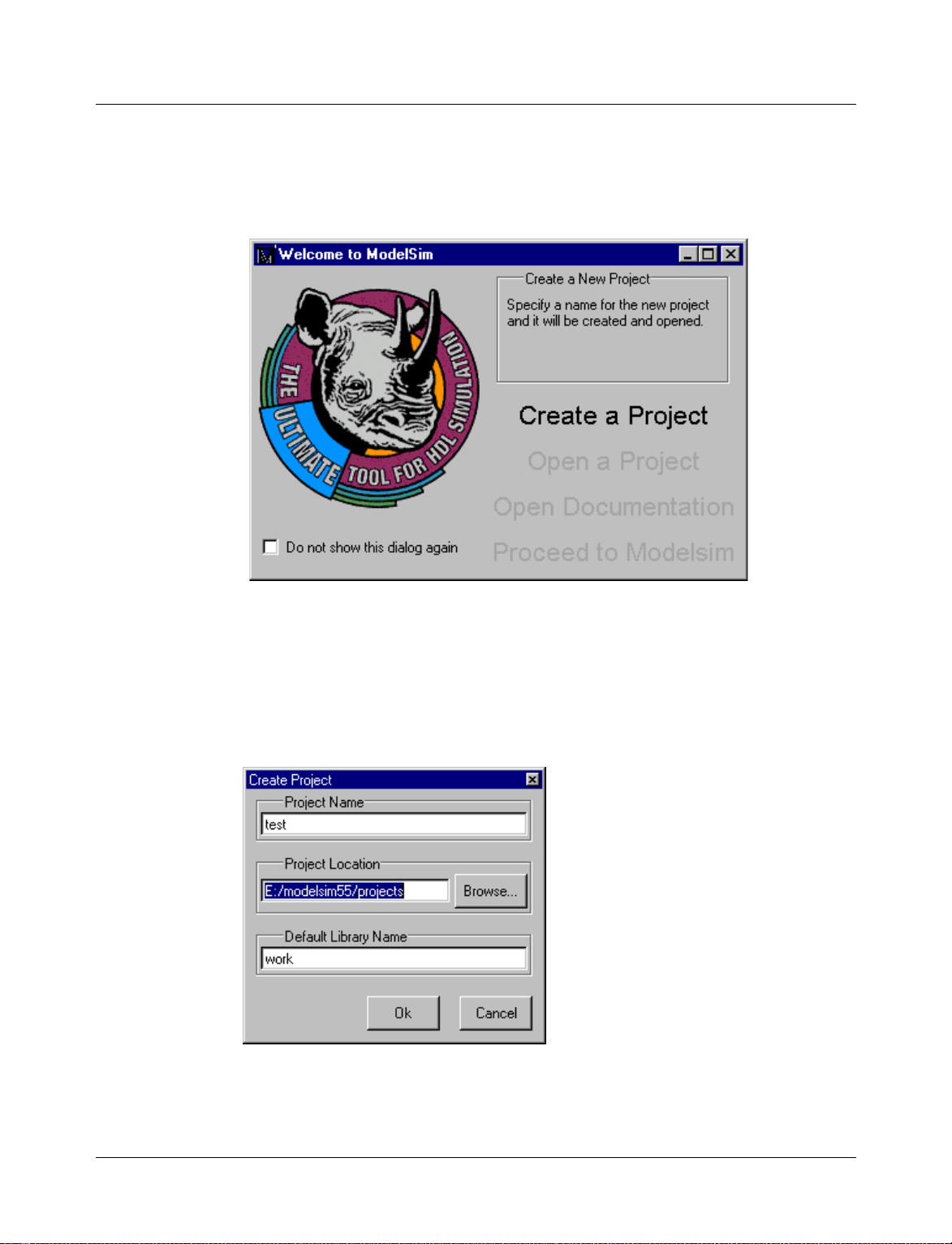

1 Select Create a Project from the Welcome to ModelSim screen that opens the first time

you start ModelSim. If this screen is not available, you can enable it by selecting Help >

Enable Welcome (Main window).

Getting started with projects

You can also use the File > New > Project (Main window) command to create a new

project.

2

Clicking the Create a Project button opens the Create Project dialog box.

ModelSim SE User’s Manual Projects and system initialization 2-29

Page 30

Getting started with projects

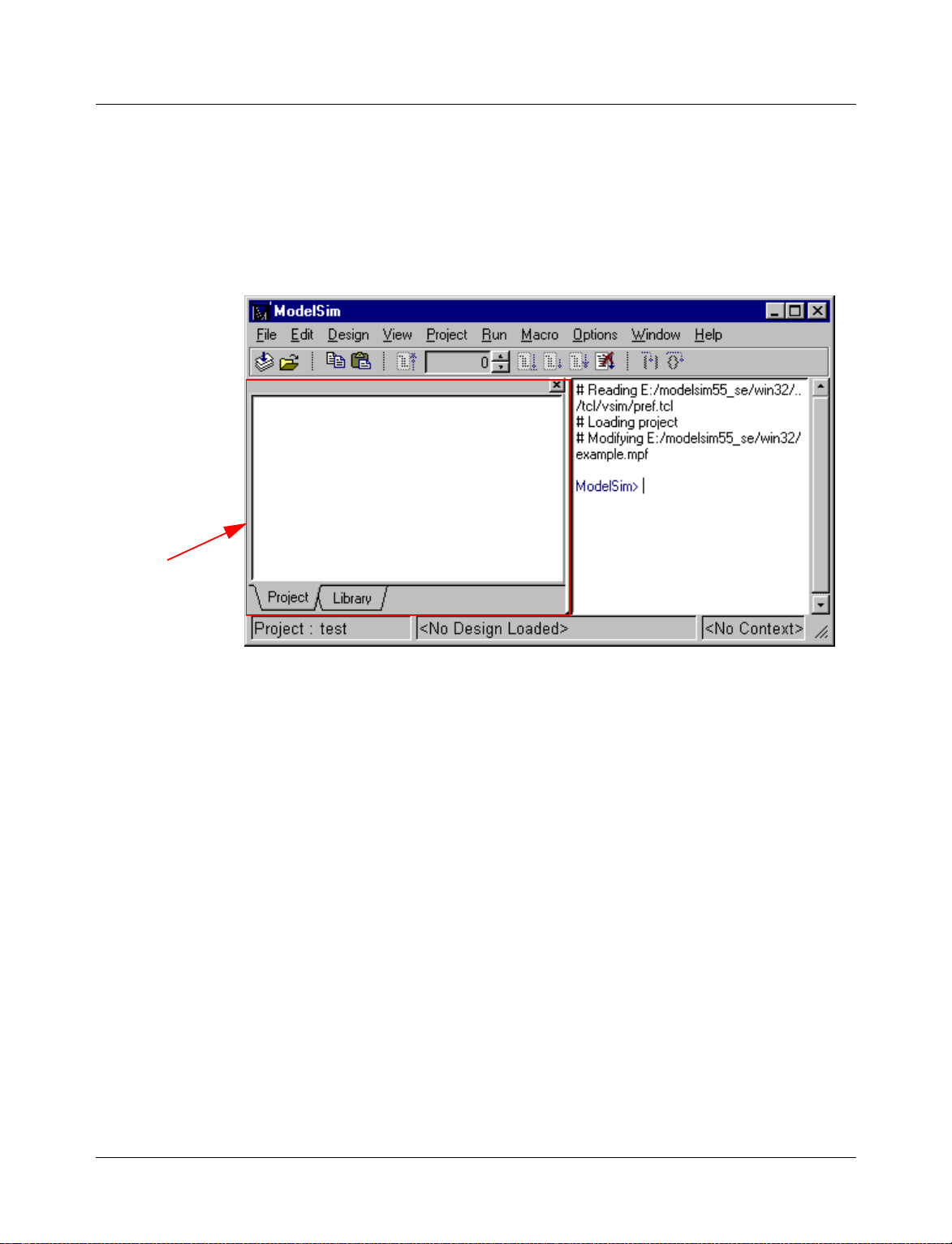

3 Specify a Project Name and Project Location. The location is where the pro ject .mpf file

and any copied source files will be stored. You can leave the Default Library Name set to

"work," or specify a different name if desired. The name that is specified will be used to

create a working library subdirectory within the Project Location.

After selecting OK, you will see a blank Project page in the workspace area of the Main

window. You can hide or show the workspace at any time using the View > Hide/Show

Workspace command.

workspace

The name of the current project is shown at the bottom left corner of the Main window.

2-30 Pr ojects and system initialization ModelSim SE User’s Manual

Page 31

Step 2 — Add files to the project

Your right mouse button (2nd button in Windows ; 3rd button in UNIX) gives qu ick access

to project commands. When you right-click in the wor kspace, a context menu appear s. The

menu that appears depends on where you click in the workspace.

Getting started with projects

1 Right click in a blank area on the Project page and select Add file to Project. This opens

the Add file to Project dialog. You can also select Project > Add file to Project from the

menu bar.

2 Specify one or more files you want to add to the project. (The files used in this example are

available in the examples directory that is installed along with ModelSim.)

3 For the files you’re adding, choose whether to reference them from their current location

or copy them into the project directory.

ModelSim SE User’s Manual Projects and system initialization 2-31

Page 32

Getting started with projects

Step 3 — Compile the files

1 To compile the files, right click in the Project page and select Compile All. You can also

select Project > Compile All from the menu bar.

2 Once compilation is finished, click the Library tab and you’ll see the two compiled designs.

2-32 Pr ojects and system initialization ModelSim SE User’s Manual

Page 33

Step 4 — Simulate a design

1 To simulate one of the designs, either double-click the name or right click the name and

select Load. A new page appears showing the structure of the current active simulation.

Getting started with projects

At this point you are ready to run the simulation and analyze your results. You often do this

by adding signals to the Wave window and running the simulation for a given period of

time. See the ModelSim Tutorial for examples.

Other project operations

In addition to the four actions just discussed, the following are common project operations .

Open an existing project

When you leave a ModelSim session, ModelSim will remember the last opened project.

You can reopen it for your next session by cl icking Open Project in the Welcome to

ModelSim dialog. You can also open an existing project by selecting File > Open > Project

(Main window).

Close a project

Select File > Close > Project (Main window). This closes the Project page but leaves the

Library and Structure (labeled "Sim" in the graphic above) pages open in the workspace.

Delete a project

Select File > Delete > Project (Main window).

ModelSim SE User’s Manual Projects and system initialization 2-33

Page 34

Customizing project settings

Customizing project settings

Though the default project settings will work for many designs, it is easy to customize the

settings if needed. You can change the compile order and set compiler options.

Changing compile order

When you compile all files in a project, ModelSim by default compiles the files in the order

in which they were added to the project. You have two alternatives for changing the default

compile order: 1) select and compile each file individually; 2) specify a custom compile

order using the Compile Order dialog.

Note: Files can be displayed in the Project tab in alph abetical or compile order (using the

Sort by Alphabetical Order or Sort by Compile Order commands on the context menu).

Keep in mind that the order you see in th e Project tab is no t neces sarily th e or der in which

the files will be compiled.

To open the Compile Order dialog, right click in an empty area of th e Project tab and select

Compile Order. The dialog shown below opens.

move up in order

move down in order

group Verilog files

ungroup Verilog files

The group and ungroup buttons are used on Verilog files only. They allow you to group two

or more Verilog files so they are sent to the compiler at the same time. One case where you

might use this is when you have one file with a bunch of define statements and a second

file that is a Verilog module. You would want to compile these two files at the same time.

2-34 Pr ojects and system initialization ModelSim SE User’s Manual

Page 35

Setting compiler options

The VHDL and Verilog compilers (vcom and vlog, respectively) have numerous options

that affect how a design is compiled and subsequently simu lated. Outs ide of a p roject yo u

can set the defaults for all future simulations using the Options > Compile (Main window)

command. Inside of a project you can set these options on individual files or a group of

files.

To set the compiler options in a project, select the file(s) in the Project page, right click on

the file names, and select Compile Properties. The pages that appear in the resulting dialog

depend on the type of files you have selected. If you select a VHDL file, you’ll see only the

General and VHDL pages. If you select a Verilog file, you’ll see only the General and

Verilog pages. If you select both a VHDL file and a Verilog file, you’ll see all three pages

(as shown in the dialog below).

When setting options on a group of files, keep in mind the following:

• If two or more files have different settings for the same option, the checkbox in the dialog

will be "grayed out" like this:

If you change the option, you cannot change it back to a "multi- state setting" without

cancelling out of the dialog. Once you click OK, ModelSim will set the option the same

for all selected files.

• If you select a combination of VHDL and Verilog files, the options you set on the VHDL

and Verilog tabs apply only to those file types.

Customizing project settings

• Exclude File from Build

Determines whether the file is excluded from the compile.

• Compile to library

Specifies to which library you want to compile the file; defaults to the working library.

The definitions of the options on the VHDL and Verilog pages can be found in the section

"Setting default compile options"

ModelSim SE User’s Manual Projects and system initialization 2-35

(8-252).

Page 36

Accessing projects from the command line

Accessing projects from the command line

Generally, projects are used only within the ModelSim graphical user interface. However,

standalone tools will use the project file if they are invoked in the project’s root directory.

If invoked outside the project directory, th e MODELSIM environment variable can be set

with the path to the project file (<Project_Root_Dir>/<Project_Name>.mpf).

You can also use the project command

common operations on new projects. The command is to be used outside of a simulation

session.

(CR-159) from the command line to perform

2-36 Pr ojects and system initialization ModelSim SE User’s Manual

Page 37

System initialization

ModelSim goes through numerous steps as it initializes the system during startup. It

accesses various files and environment variables to determine library mappings, configure

the GUI, check licensing, and so forth.

Files accessed during startup

The table below describes the files that are read during startup. T hey are listed in the order

in which they are accessed.

File Purpose

modelsim.ini contains initial tool settings; see "Preference variables located in

location map file used by ModelSim tools to find source files based on easily

pref.tcl contains defaults for fonts, colors, prompts, window positions,

System initialization

INI files"

(B-396) for specific details on the modelsim.ini file

reallocated "soft" paths; default file name is mgc_location_map;

see "How location mapping works"

(E-438) for more details

and other simulator window characteristics; see "Preference

variables located in TCL files"

(B-406) for specific details on the

pref.tcl file

modelsim.tcl contains user-customized settings for fonts, colors, prompts,

window positions, and other simulator window characteristics;

see "Preference variables located in TCL files"

(B-406) for

specific details on the modelsim.tcl file

ModelSim SE User’s Manual Projects and system initialization 2-37

Page 38

System initialization

Environment variables accessed during startup

The table below describes the environment variables that are read during star tup. They are

listed in the order in which they are accessed. For more information on environment

variables, see "Environment variables"

Environment variable Purpose

MODEL_TECH set by ModelSim to the directory in which the binary executables reside

(e.g., ../modeltech/<platform>/)

MODEL_TECH_OVERRIDE provides an alternative directory for the binary executables;

MODEL_TECH is set to this path

MODELSIM identifies path to the modelsim.ini file

MGC_WD identifies the Mentor Graphics working directory (set by Mentor Graphics

tools)

MGC_LOCATION_MAP identifies the path to the location map file; set by ModelSim if not defined

MODEL_TECH_TCL identifies the path to all Tcl libraries installed with ModelSim

(B-393).

HOME identifies your login directory (UNIX only)

MGC_HOME identifies the path to the MGC tool suite

TCL_LIBRARY identifies the path to the Tcl library; set by ModelSim to the same path as

MODEL_TECH_TCL; must point to libraries supplied by Model

Technology

TK_LIBRARY identifies the path to the Tk library; set by ModelSim to the same path as

MODEL_TECH_TCL; must point to libraries supplied by Model

Technology

TIX_LIBRARY identifies the path to the Tix library; set by ModelSim to the same path as

MODEL_TECH_TCL; must point to libraries supplied by Model

Technology

ITCL_LIBRARY identifies the path to the [incr]Tcl library; set by ModelSim to the same

path as MODEL_TECH_TCL; must point to libraries supplied by Model

Technology

ITK_LIBRARY identifies the path to the [incr]Tk library; set by ModelSim to the same

path as MODEL_TECH_TCL; must point to libraries supplied by Model

Technology

VSIM_LIBRARY identifies the path to the Tcl files that are used by ModelSim; set by

ModelSim to the same path as MODEL_TECH_TCL; must point to

libraries supplied by Model Technology

MTI_LIB_DIR identifies the path to all Tcl libraries installed with ModelSim

2-38 Pr ojects and system initialization ModelSim SE User’s Manual

Page 39

System initialization

Environment variable Purpose

MODELSIM_TCL identifies the path to the modelsim.tcl file; this environment variable can

be a list of file pathnames, separated by semicolons (Windows) or colons

(UNIX)

Initialization sequence

The following list describes in detail ModelSim’s initialization sequence. The sequence

includes a number of conditional structures, the results of which are determined by the

existence of certain files and the current settings of environment variables.

In the steps below, names in uppercase denote environment variables (except

MTI_LIB_DIR which is a Tcl variable). Instances of $(NAME) denote paths that are

determined by an environment variable (except $(MTI_LIB_DIR) which is determined by

a Tcl variable).

1 Determines the path to the executable directory (../modeltech/<platform>/). Sets

MODEL_TECH to this path, unless MODEL_TECH_OVERRIDE exists, in which case

MODEL_TECH is set to the same value as MODEL_TECH_OVERRIDE.

2 Finds the modelsim.ini file by evaluating the following conditions:

• use MODELSIM if it exists; else

• use $(MGC_WD)/modelsim.ini; else

• use ./modelsim.ini; else

• use $(MODEL_TECH)/modelsim.ini; else

• use $(MODEL_TECH)/../modelsim.ini; else

• use $(MGC_HOME)/lib/modelsim.ini; else

• set path to ./modelsim.ini even though the file doesn’t exist

3 Finds the location map file by evaluating the following conditions:

• use MGC_LOCATION_MAP if it exists (if this variable is set to "no_map", ModelSim

skips initialization of the location map); else

• use mgc_location_map if it exists; else

• use $(HOME)/mgc/mgc_location_map; else

• use $(HOME)/mgc_location_map; else

• use $(MGC_HOME)/etc/mgc_location_map; else

• use $(MGC_HOME)/shared/etc/mgc_location_map; else

• use $(MODEL_TECH)/mgc_location_map; else

• use $(MODEL_TECH)/../mgc_location_map; else

• use no map

4 Reads various variables from the [vsim] section of the modelsim.ini file. See "[vsim]

simulator control variables"

ModelSim SE User’s Manual Projects and system initialization 2-39

(B-398) for more details.

Page 40

System initialization

5 Parses any command line arguments that were included when you started ModelSim and

6 Defines the following environment variables:

7 Initializes the simulator’s Tcl interpreter.

8 Checks for a valid license (a license is not checked out unless specified by a modelsim.ini

reports any problems.

• use MODEL_TECH_TCL if it exists; else

• set MODEL_TECH_TCL=$(MODEL_TECH)/../tcl

• set TCL_LIBRARY=$(MODEL_TECH_TCL)/tcl8.0

• set TK_LIBRARY =$(MODEL_TECH_TCL)/tk8.0

• set TIX_LIBRARY=$(MODEL_TECH_TCL)/tix4.1

• set ITCL_LIBRARY=$(MODEL_TECH_TCL)/itcl3.0

• set ITK_LIBRARY=$(MODEL_TECH_TCL)/itk3.0

• set VSIM_LIBRARY=$(MODEL_TECH_TCL)/vsim

setting or command line option).

The next four steps relate to initializing the graphical user interface.

9

Sets Tcl variable "MTI_LIB_DIR"=MODEL_TECH_TCL

10 Loads $(MTI_LIB_DIR)/pref.tcl.

11 Loads last w orking directory, project init, project history, and printer defaults from the

registry (Windows) or $(HOME)/.modelsim (UNIX).

12 Finds the modelsim.tcl file by evaluating the following conditions:

• use MODELSIM_TCL if it exists (if MODELSIM_TCL is a list of files, each file is

loaded in the order that it appears in the list); else

• use ./modelsim.tcl; else

• use $(HOME)/modelsim.tcl if it exists

That completes the initialization sequence. Also note the following about the modelsim.ini

file:

• When you change the working directory within ModelSim, the tool reads the [library],

[vcom], and [vlog] sections of the local modelsim.ini file. When you make changes in the

compiler options dialog or use the vmap command, the tool updates the appropriate

sections of the file.

• The pref.tcl file references the default .ini file via the [GetPrivateProfileString] Tcl