MITSUBISHI <DIGITAL ASSP>

M66850J/FP, M66851J/FP

M66852J/FP, M66853J/FP

SRAM TYPE FIFO MEMORY

DESCRIPTION

M66850/851/852/853 are very high-speed and clock synchronous

FIFO(First-In,First-Out) memories fabricated by high-speed CMOS

technology.

These FIFOs are applicable for a data buffer as networks and

communications.

The write operation is controlled by a write clock pin(WCLK) and

two write enable pins(WEN1,WEN2).

Data present at the data input pins(D0-D8) is written into the

Synchronous FIFO on every rising write clock edge when the

device is enabled for writing.

The read operation is controlled by a read clock pin(RCLK) and

two read enable pins(REN1,REN2).

Data is read from the Synchronous FIFO on every rising read clock

edge when the device is enabled for reading. An output enable

pin(OE) controls the states of the data output pins(Q0-Q8).

MITSUBISHI FIFOs have four flags (EF,FF,PAE,PAF). The empty

flag EF and the full flag FF are fixed flags. The almost empty flag

PAE and the almost full flag PAF are programmable flags. The

programmable flag offset is initiated by the load pin(LD).

FEATURES

• Memory configuration 64words x 9bits (M66850J/FP)

256words x 9bits (M66851J/FP)

512words x 9bits (M66852J/FP)

1024words x 9bits (M66853J/FP)

• Write and Read Clocks can be independent

• Advanced CMOS technology

• Programmable Almost-Empty and Almost-Full flags

• High-speed : 25ns cycle time

• Package Available :

32-pin Pastic Leaded Chip Carrier(PLCC)

32-pin Low profile Quad Flat Package(LQFP)

APPLICATION

• Data Buffer for networks communications.

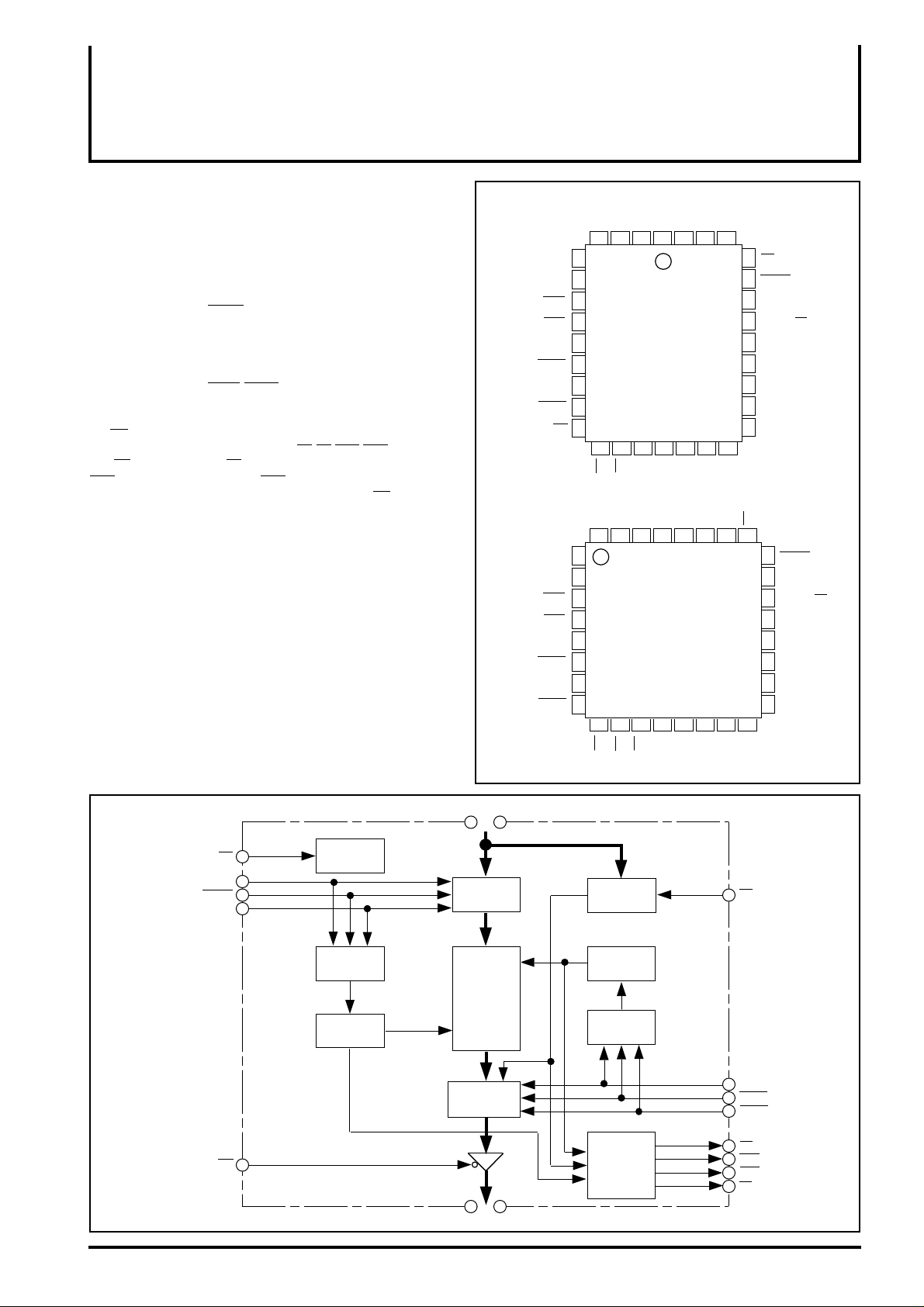

PIN CONFIGURATION (TOP VIEW)

D4D5D6D7D8

D2

D3

4

5

D1

6

D0

7

PAF

8

PAE

9

GND

10

REN1

11

RCLK

12

REN2

13

OE

14

EF

Outline 32P0(M66850 – 853J)

D2

32

1

D1

2

D0

3

PAF

4

PAE

5

GND

6

REN1

7

RCLK

REN2

8

9

OE

Outline 32P6B(M66850 – 853FP)

1

3

2

32

15

16

17

18

FF

Q0Q1Q2

D4D5D6D7D8

D3

31

30

29

28

11

10

12

13

FF

Q0Q1Q2

EF

31

19

Q3

27

14

30

20

Q4

26

15

Q3

29

RS

28

WEN1

27

WCLK

26

WEN2/LD

25

V

24

Q8

23

Q7

22

Q6

21

Q5

RS

25

16

Q4

CC

24

WEN1

23

WCLK

22

WEN2/LD

21

V

20

Q8

19

Q7

18

Q6

17

Q5

CC

BLOCK DIAGRAM

WCLK

WEN1

WEN2

RS

OE

RESET

LOGIC

WRITE

CONTROL

WRITE

POINTER

D0-D8

–

INPUT

REGISTER

MEMORY

ARRAY

OUTPUT

REGISTER

–

Q0-Q8

OFFSET

REGISTER

READ

POINTER

READ

CONTROL

FLAG

LOGIC

LD

RCLK

REN1

REN2

EF

PAE

PAF

FF

1

MITSUBISHI <DIGITAL ASSP>

M66850J/FP, M66851J/F P

M66852J/FP, M66853J/F P

SRAM TYPE FIFO MEMORY

PIN and SIGNAL DESCRIPTIONS

•VCC

One+5 volt power supply pin.

• GND

One 0 volt ground pin.

• RS : Reset(INPUT)

When RS is set LOW, internal read and write pointers are set to

the first physical location,the output register is initialized to LOW,

FF and PAF are set HIGH, EF and PAE are set LOW.

A reset is required after power-up before a write operation.

• WCLK : Write Clock(INPUT)

Data present on D0-D8 is written into the FIFO on the rising edge

of WCLK when the FIFO is enabled for writing.

• RCLK : Read Clock(INPUT)

Data is read from the FIFO on the rising edge of RCLK when the

FIFO is enabled for reading.

• WEN1 : Write Enable1(INPUT)

If the FIFO is configured to allow loading of the offset registers,

WEN1 is the only the write enable. When WEN1 is LOW, data on

D0-D8 is written to the FIFO on the rising edge of WCLK.

If the FIFO is configured to have two writeenables, data on D0D8 is written to the FIFO on the rising edge of WCLK when

WEN1 is LOW and WEN2 is High. But if the FF is LOW, data on

D0-D8 will not be written to the FIFO.

• EF : Empty Flag(OUTPUT)

The Empty flag goes LOW when the read pointer is equal to the

write pointer.

When EF is LOW, the FIFO is empty and further data reads from

the data output are inhibited.

EF is synchronized to the rising edge of RCLK.

• PAE : Programmable Almost-Empty Flag(OUTPUT)

When PAE is LOW, the FIFO is almost empty based on the

offset. The default offset is Empty+7. PAE is synchronized to the

rising edge of RCLK.

• FF : Full Flag(OUTPUT)

When FF is LOW, the FIFO is full and further data writes into the

data input are inhibited.

The Full Flag goes LOW when the FIFO is full of data.

FF is synchronized to the rising edge of WCLK.

• PAF : Programmable Almost-Full Flag(OUTPUT)

When PAF is LOW, the FIFO is almost full based on the offset.

The default offset is Full-7. PAF is synchronized to the rising

edge of WCLK.

• WEN2/LD : Write Enable2/Load(INPUT)

The function of this signal is defined at reset.

If WEN2/LD is HIGH at reset, this signal functions as a second

write enable(WEN2). If WEN2/LD is LOW at reset, this signal

functions as a control to load and read the offset register.

If the FIFO is configured to have two write enables, data on D0D8 is written to the FIFO on the rising edge of WCLK when

WEN1 is LOW and WEN2 is High. But if the FF is LOW, data on

D0-D8 will not be written to the FIFO.

If the FIFO is configured to have programmable flags, it is

possible to write and read from the offset registers. There are

four 9-bit offset registers. Two are used to control the

programmable Almost-Empty Flag

programmable Almost-Full Flag.

Data on D0-D8 is written to an offset register on the rising edge

of WCLK when WEN1 is LOW and LD is LOW. Data on D0 – D8

is written to the offset registers in the following order :

PAE LSB, PAE MSB, PAF LSB, PAF MSB.

• REN1, REN2 : Read Enable(INPUT)

Data is read from the FIFO and presented Q0-8 on the rising

edge of RCLK, when REN1 and REN2 are LOW and output port

is enabled.

If either Read Enable is HIGH,the output register holds the

previous data.

When the FIFO is empty, the Read Enable signals are ignored.

• OE : Output Enable(INPUT)

When OE is LOW, the output port Q0-8 is enabled for output.

When OE is HIGH, the output port Q0-8 is placed in a high

impedance state.

and

two are used to control the

• D0-8 : Data Input(INPUT)

D0-8 is the 9-bit data input port.

• Q0-8 : Data Output(OUTPUT)

Q0-8 is the 9-bit data Output port.

2

OFFSET FLAG

MITSUBISHI <DIGITAL ASSP>

M66850J/FP, M66851J/F P

M66852J/FP, M66853J/F P

SRAM TYPE FIFO MEMORY

LD WEN1 WCLK SELECTION

0 0 Empty Offset (LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

0 1 No Operation

1 0 Write into FIFO

1 1 No Operation

Figure 1. Write Offset Register

M66850J(64X9-bit) OFFSET REGISTERS

876543210

PAE LSB

PAE MSB

PAF LSB

PAF MSB

M66851J(256X9-bit) OFFSET REGISTERS

PAE LSB

PAE MSB

PAF LSB

PAF MSB

E0/F0 are the least significant bits.

X=Don't Care.

X X X E5E4E3E2E1E0

Default Value 007H

XXXXXXXXX

X X X F5F4F3F2F1F0

Default Value 007H

XXXXXXXXX

876543210

XE7E6E5E4E3E2E1E0

Default Value 007H

XXXXXXXXX

XF7F6F5F4F3F2F1F0

Default Value 007H

XXXXXXXXX

LD REN1 REN2 RCLK SELECTION

0 0 0 Empty Offset (LSB)

Empty Offset (MSB)

Full Offset (LSB)

Full Offset (MSB)

0 0 1

1 0 No Operation

1 1

1 1 0 Read from FIFO

1 0 1

1 0 No Operation

1 1

Figure 2. Read Offset Register

M66852J(512X9-bit) OFFSET REGISTERS

876543210

PAE LSB

PAE MSB

PAF LSB

PAF MSB

M66853J(1024X9-bit) OFFSET REGISTERS

PAE LSB

PAE MSB

PAF LSB

PAF MSB

XE7E6E5E4E3E2E1E0

Default Value 007H

XXXXXXXXE8

Default Value 0

XF7F6F5F4F3F2F1F0

Default Value 007H

XXXXXXXXF8

Default Value 0

876543210

XE7E6E5E4E3E2E1E0

Default Value 007H

XXXXXXXE9E8

Default Value 0 0

XF7F6F5F4F3F2F1F0

Default Value 007H

XXXXXXXF9F8

Default Value 0 0

Figure 3. Offset Regigter Location

3

ABSOLUTE MAXIMUM RATINGS

MITSUBISHI <DIGITAL ASSP>

M66850J/FP, M66851J/F P

M66852J/FP, M66853J/F P

SRAM TYPE FIFO MEMORY

Symbol

Vcc

VI

VO

Pd

Tstg

Note : 450mW(32P6B), 550mW(32P0)

Supply voltage

Input voltage

Output voltage

Maximum power dissipation

Storage temperature

Parameter Conditions

A value based on GND pin

Ta=70˚C

-0.5 – +7.0

-0.3 – V

-0.3 – V

RECOMMENDED OPERATING CONDITIONS

Symbol

Vcc Supply voltage 4.5

GND

Topr

Supply voltage

Operating ambient temperature

Min.

0

Limits

Typ.

5

0

Max.

5.5

70

UnitParameter

V

V

˚C

DC ELECTRICAL CHARACTERISTICS (Ta=0 – 70˚C, Vcc=5V±10%, GND=0V)

Symbol Test conditions UnitParameter

IH

V

V

IL

VOH

VOL

IIH

IIL

I

OZH

IOZL

I

CC1

ICC2

CI

CO Off state output capacitance

"H"input voltage

"L"input voltage

"H"output voltage

"L"output voltage

"H"input current

"L"input current

Off state "H"output current

Off state "L"output current

Operating power supply current

Power supply current (Static)

Input capacitance

I

OH =-1mA

I

OL =8mA

V

I =VCC, Any input

V

I = GND, Any input

VO =VCC

VO =GND

V

I =VCC or GND, f = 40MHz, Outputs are open

V

I =VCC or GND, Outputs are open

f = 1MHz

f = 1MHz

Ratings

CC+0.5

CC+0.5

Note

-65 – 150

Min. Typ. Max.

2.0

2.4

Unit

mW

Limits

V

V

V

˚C

0.8

0.4

1.0

-1.0

5.0

-5.0

70

500

10 pF

15

V

V

V

V

µ

µ

µ

µ

mA

µ

pF

A

A

A

A

A

4

M66850J/FP, M66851J/F P

M66852J/FP, M66853J/F P

SWITCHING CHARACTERISTICS (Ta=0 – 70˚C, Vcc=5V±10%, GND=0V)

Symbol UnitParameter

AC

t

tWFF

REF

t

tPAF

tPAE

tOE

tOLZ

tOHZ

tRSF

TIMING CONDITIONS (Ta=0 – 70˚C, Vcc=5V±10%, GND=0V)

Symbol UnitParameter

tCLK

tCLKH

tCLKL

tDS

tDH

tENS

tENH

tRS

tRSS

tRSR

tSKEW1

tSKEW2

Data Access Time

Write Clock to Full Flag

Read Clock to Empty Flag

Write Clock to Almost-Full Flag

Read Clock to Almost-Empty Flag

Output Enable to Output Valid

Output Enable to Output in Low-Z

Output Enable to Output in High-Z

Reset to Flag and Output Valid time

Clock Cycle Time

Clock Pulse Width HIGH

Clock Pulse Width LOW

Data Setup Time

Data Hold Time

Enable Setup Time

Enable Hold Time

Reset Pulse Width

Reset Setup Time

Reset Recovery Time

Skew time between Read Clock and Write Clock for Empty Flag and Full Flag

Skew time between Read Clock and Write Clock for Almost-Empty Flag and Almost-Full

Flag

MITSUBISHI <DIGITAL ASSP>

SRAM TYPE FIFO MEMORY

Limits

Min. Typ. Max.

3

3

0

3

Limits

Min. Typ. Max.

25

10

10

6

1

6

1

25

25

25

10

40

15

15

15

15

15

13

13

25

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

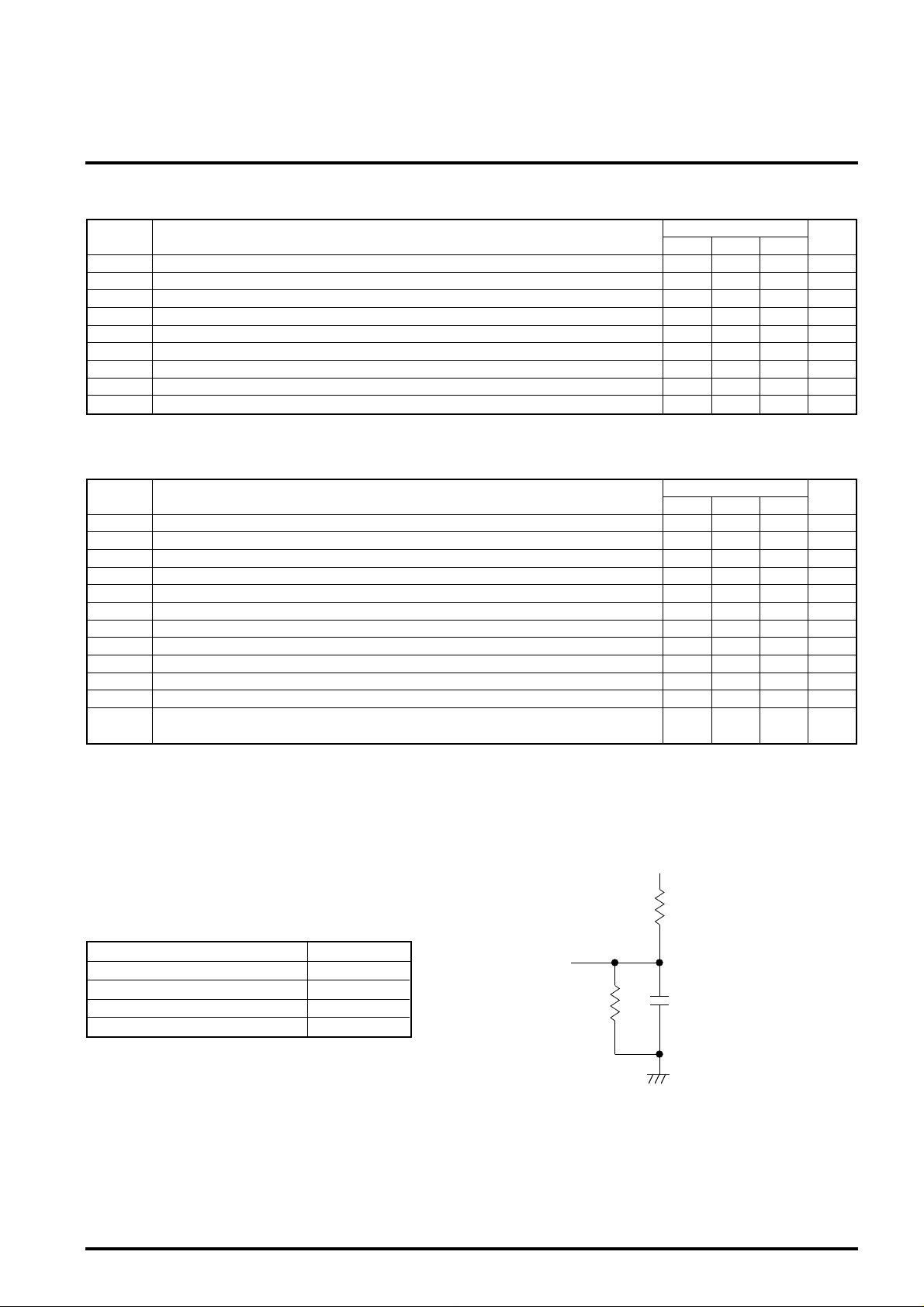

AC TEST CONDITIONS

In Pulse Levels GND – 3.0V

Input Rise/Fall Times 3ns

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

Output Load See Figure 4

5.0V

1.1kΩ

D.U.T.

680Ω

Figure 4. Output Load

Including Test board and scope capacitances.

30pF

5

Loading...

Loading...