Mitsubishi M66305AP, M66305AFP Datasheet

MITSUBISHI 〈DIGITAL ASSP〉

MITSUBISHI 〈DIGITAL ASSP〉

DESCRIPTION

M66305A Toggle Line Buffer has two 5,120-bit line buffer

memories. It takes in serial data that arrives synchronously

with clock pulses and outputs it in serial at a rate of up to 10

Mbits per second synchronously with external clock pulses.

This buffer employs the double buffer system: While data is

being output, data on the next line can be written on the other

line buffer memory.

FEATURES

• 5,120 × 1bit serial input-serial output line buffer memories

• Data transmission at 10 megabits/second maximum

• Two line buffer memories can be alternated by external

toggle signal.

• Memory capacity can be doubled by cascade connection.

• Because of cascade input pin (CAS1), output potential after

completion of output can be set to either H or L.

• Low noise and high fan-out output (I

O = ±24mA guaranteed)

• Every input pin has built-in Schmidt trigger circuit.

• Read counter and write counter can be reset independently.

• RESET, T, CNTRST1 and CNTRST2 are equipped with

negative noise reduction circuit.

APPLICATION

Data buffer between industrial or home-use image data processing system and peripheral equipment

M66305AP/AFP

M66305AP/AFP

TOGGLE LINE BUFFER

TOGGLE LINE BUFFER

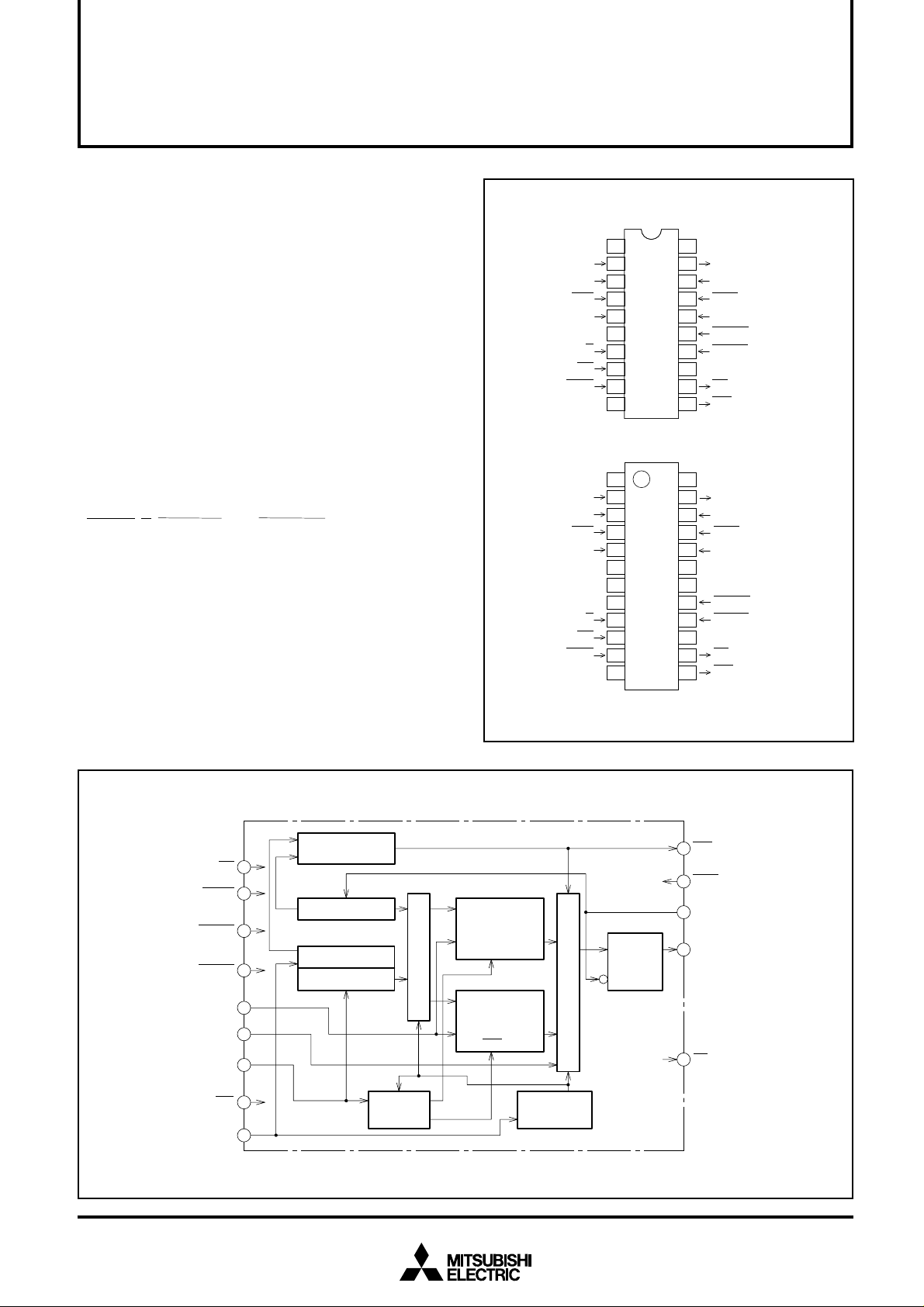

PIN CONFIGURATION (TOP VIEW)

GND

INPUT CLOCK

INPUT DATA

INPUT CLOCK ENABLE

CASCADE INPUT 1

TOGGLE SIGNAL INPUT

CHIP SELECT INPUT

RESET INPUT

SICLK

SIDATA

ICE

CAS1

GND

CS

RESET

GND

1

1

2

2

3

3

4

4

5

5

6

6

7

7

T

8

8

9

9

10

10

20

19

18

17

16

15

14

13

12

11

Outline 20P4

GND

INPUT CLOCK

INPUT DATA

INPUT CLOCK ENABLE

CASCADE INPUT 1

TOGGLE SIGNAL INPUT

CHIP SELECT INPUT

RESET INPUT

SICLK

SIDATA

ICE

CAS1

NC

NC

GND

CS

RESET

GND

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

T

10

10

11

11

12

12

24

24

23

23

22

22

21

21

M66305AFPM66305AP

20

20

19

19

18

18

17

17

16

16

15

15

14

14

13

13

V

CC

OUTPUT DATA

SODATA

SOCLK

OUTPUT CLOCK

OCE

OUTPUT CLOCK ENABLE

CAS2

CASCADE INPUT 2

CNTRST2

READ COUNTER RESET INPUT

CNTRST1

WRITE COUNTER RESET INPUT

V

CC

(5V)

BF

BUFFER FULL OUTPUT

INT

WRITE REQUEST OUTPUT

CC

V

OUTPUT DATA

SODATA

SOCLK

OUTPUT CLOCK

OCE

OUTPUT CLOCK ENABLE

CAS2

CASCADE INPUT 2

NC

NC

CNTRST2

READ COUNTER RESET INPUT

CNTRST1

WRITE COUNTER RESET INPUT

V

CC

(5V)

BF

BUFFER FULL OUTPUT

INT

WRITE REQUEST OUTPUT

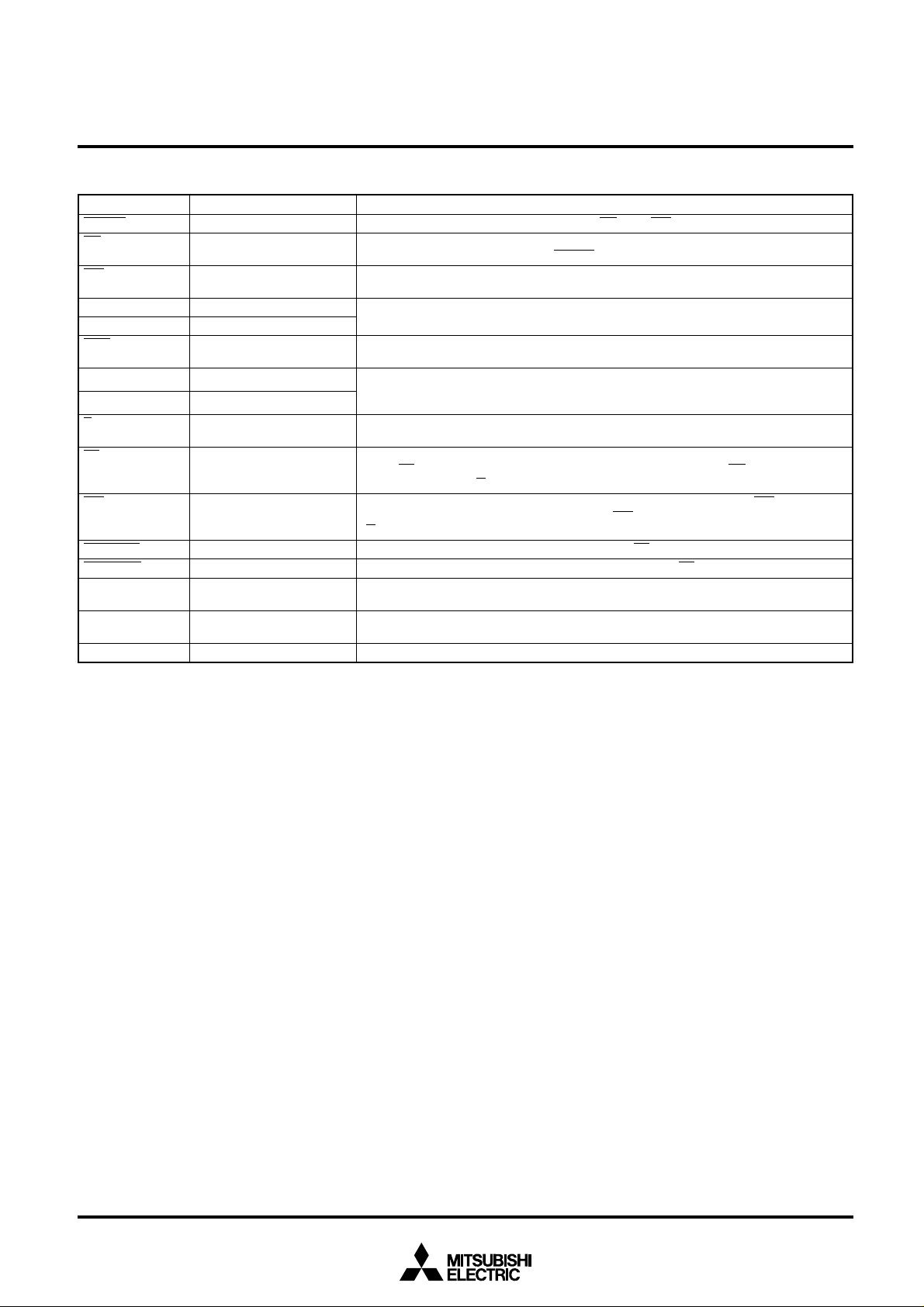

BLOCK DIAGRAM

CHIP SELECT

INPUT

RESET INPUT

WRITE COUNTER

RESET INPUT

READ COUNTER

RESET INPUT

INPUT DATA

CASCADE INPUT 1

INPUT CLOCK

INPUT CLOCK

ENABLE

TOGGLE SIGNAL

INPUT

CS

RESET

CNTRST1

CNTRST2

SIDATA

CAS1

SICLK

ICE

T

Matching

detection circuit

Read counter

Write register

Write counter

and P.G.

Switch

AD

S-RAM

5120 bits

DI D0

WR

Address selector

A

D

S-RAM

5120 bits

DI D0

WR

Data selector

Toggle F/F

Outline 24P2W-A

INT

OCE

SOCLK

Data

buffer

SODATA

BF

NC: No Connection

WRITE REQUEST

OUTPUT

OUTPUT CLOCK

ENABLE

OUTPUT CLOCK

OUTPUT DATA

BUFFER FULL

OUTPUT

1

MITSUBISHI 〈DIGITAL ASSP〉

M66305AP/AFP

TOGGLE LINE BUFFER

FUNCTION

When the status of input clock enable (ICE) is “L”, input data

(SIDATA) is taken in (written) synchronously with input clock

(SICLK) rise edge. When output clock enable (OCE) is “L”,

output data (SODATA) is output (read) synchronously with

output clock (SOCLK) fall edge. The double buffer system

makes independent read and write operation possible.

When one-line write and one-line read are completed, toggle

eration is switched to read mode, and the line buffer which

has completed output is switched to write mode, enabling

next write and read operations.

To rewrite data during write operation, use write counter reset input (CNTRST1). To repeat output during output operation, use read counter reset (CNTRST2).

These operations are possible only when the status of chip

select (CS) is “L”.

signal (T) is required to be changed to “L”, With input of toggle

signal, the line buffer memory which has completed write op-

FUNCTION T ABLE

OutputInput

RES

L

H

H

H

H

H

H

H

H

H

H

H

Q0: No change

x : “H” or “L”

*1 : BF changes from “H” to “L” with rise of SICLK for write of 5120th bit.

*2 : With fall of SOCLK, data written before toggle signal input is output in order.

*3 : INT changes from “H” to “L” when the status of SOCLK rises after output of final bit of written before toggle signal inputs.

*4 : Outputs the first bit of written data (D

*5 : Output operation can be performed irrespective of CNTRST1.

*6 : SODATA changes to the first bit of written data (D0). Write operation can be performed irrespective of CNTRST2.

CS

X

H

L

L

L

L

L

L

L

L

L

L

ICE

X

X

H

L

H

L

L

H

L

H

X

X

SIC

X

X

X

X

L

X

L

X

X

X

OCE

X

X

H

H

L

L

X

X

X

X

L

H

SOC

X

X

X

X

L

L

X

X

L

X

0).

T

CR1

CR2

SOD

INT

BF

X

X

X

L

H

H

0

X

X

X

Q

H

H

H

Q

H

H

H

Q

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

0

Q

0

0

Q

0

0

Q

*2

*3

*2

*3

*4

H

*5

*5

*6

H

Initialization

0

Q

No internal change, no output change

0

Q

No internal change, no output change

*1

With rise of SICLK, data is written on line buffer memory.

0

Q

With fall of SOCLK, data is output.

*1

Write and read

With rise of T:

1)Line buffer memory in read mode is switched to write

H

mode and the other in write mode is switched to read

mode.

2)BF and INT are canceled.

With CNTRST1 input, internal write counter is reset,

H

enabling rewriting.

With CNTRST2 input, internal read counter is reset,

*6

enabling retrial of output.

Remarks

2

PIN DESCRIPTION

Pin

RESET

CS

ICE

SICLK

SIDATA

OCE

SOCLK

SODATA

T

BF

INT

CNTRST1

CNTRST2

CAS1

CAS2

NC

Name

Reset input

Chip select input

Input clock enable

Input clock

Input data

Output clock enable

Output clock

Output data

Toggle signal input

Buffer full output

Write request output

Write counter reset input

Read counter reset input

Cascade input 1

Cascade input 2

No Connection

MITSUBISHI 〈DIGITAL ASSP〉

M66305AP/AFP

TOGGLE LINE BUFFER

Functions

Initializes integrated circuit. (SODATA =“L”, BF =“H”, INT = “H”)

“L”: Chip select

“H”: Non-select (Inputs other than RESET have no effects on circuit inside.)

“L”: Input clock (SICLK) enable

“H”: Input clock (SICLK) disable

With rise of SICLK, SIDATA is written on line buffer memory.

“L”: Output clock (SOCLK) enable

“H”: Output clock (SOCLK) disable

With fall of SOCLK, SODATA is output. Because buffer is provided between memory and

output, each piece of data is propagated at a constant rate, irrespective of internal

memory read access time.

The line buffer memory in write mode is switched to read mode, and the other in read

mode is switched to write mode.

Output when SICLK rises for input of 5,120th bit, indicating no more writing is possible.

When BF is “L”, circuit inside is automatically set to “input disable”. BF is canceled with

rise of toggle signal (T) status.

Output when SOCLK rises after output of final bit of written data. When INT is “L”, circuit

inside is automatically set to “output disable”. INT is canceled with rise of toggle signal

(T) status.

Used to rewrite data during write operation when CS is “L”.

Used to undo data output halfway or to retry output when CS is “L”.

Output when SOCLK falls after output of final bit of written data. When cascade

connection is not used, be sure to connect this pin to VCC or GND.

Up to 2 cascade connections are possible. Connect the CA2 pin of master IC to VCC,

and the CA2 pin of slave IC to GND. Refer to APPLICATION EXAMPLE for details.

Non-connected pin provided only for M66305AFP. This pin can be used for wiring.

3

Loading...

Loading...