USB DEVICE CONTROLLER

D12

D13

INTRDWR

RST

CS

TEST2

Ver.1.0 Oct. 27, 2000

ADDRESS BUS

DATA BUS

READ STROBE

CHIP SELECT

RESET

DATA BUS

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

DESCRIPTION

The M66290A is a general purpose USB (Universal Serial

Bus) device controller compatible with the USB

specification version 1.1 and corresponds to full speed

transfer. Built-in transceiver circuits meet all transfer type

which is defined in USB.

M66290A has FIFO of 3k Bytes for data transfer and can

set 6 endpoints (maximum).

Each endpoint can be set programmable of its transfer

condition, so can correspond to each device class transfer

system of USB.

FEATURES

· USB specification 1.1 compliant

· Built-in USB transceiver circuit

· Supports Full Speed (12 Mbps) transmission

· Supports all four USB transfer type :

· Control transfer

· Bulk transfer

· Isochronous transfer

· Interrupt transfer

· Built-in FIFO (3 KBytes) for Endpoint

· Up to 6 endpoint (EP0 to EP5) selectable

· Data transfer condition selectable for each

Endpoints (EP1 to EP5)

· Data transfer type

(Bulk, Isochronous and Interrupt)

· Transfer direction (IN/OUT)

· Buffer size of FIFO (maximum 1024 Bytes)

· Double (Toggle) buffer configuration

· Continuous transfer mode

(Buffering up to 1 KByteX2)

· Max packet size

· Supports 4 input clock frequencies

· Input clock : 6/12/24/48 MHz

· Built-in PLL which has an oscillation buffer

and outputs at 48 MHz

· Supports both 8-bit and 16-bit DMA transfers

· 16-bit CPU bus interface

· 3.3V single power source

· Built-in JTAG

APPLICATION

· Printer , Scanner , DSC , DVC

· PC camera , Multimedia speaker , Terminal adapter etc.

· Support all PC peripheral using Full Speed USB

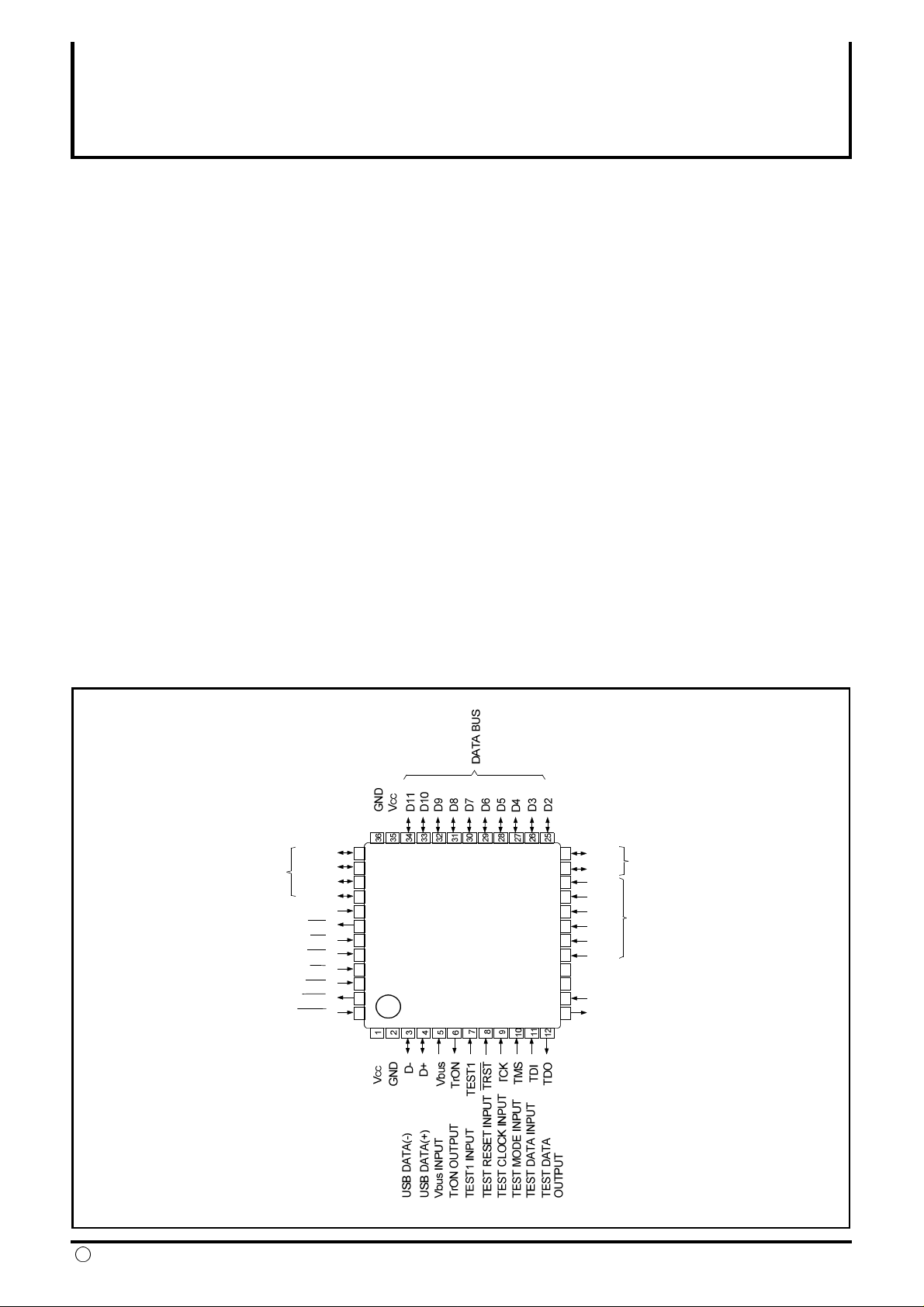

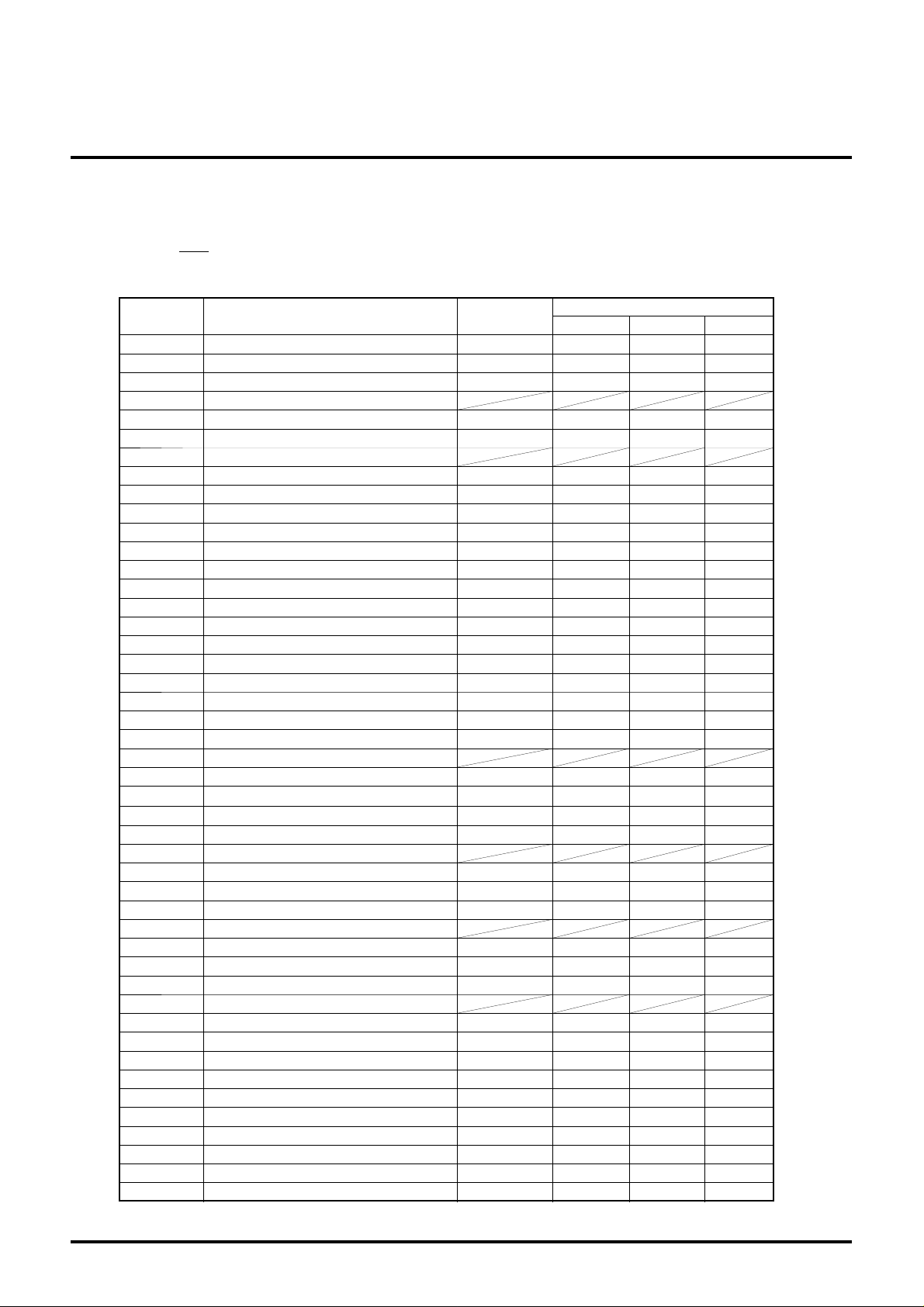

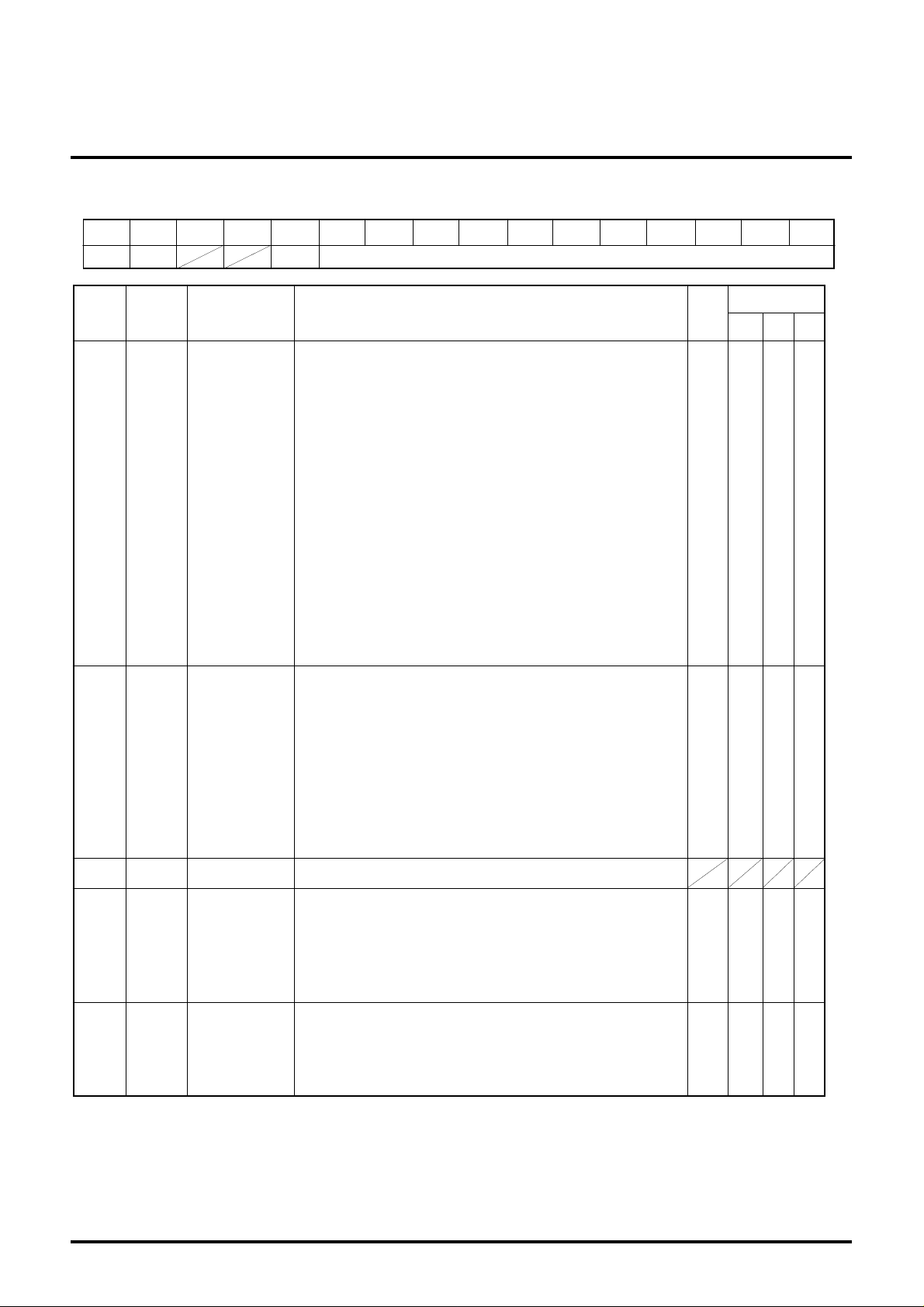

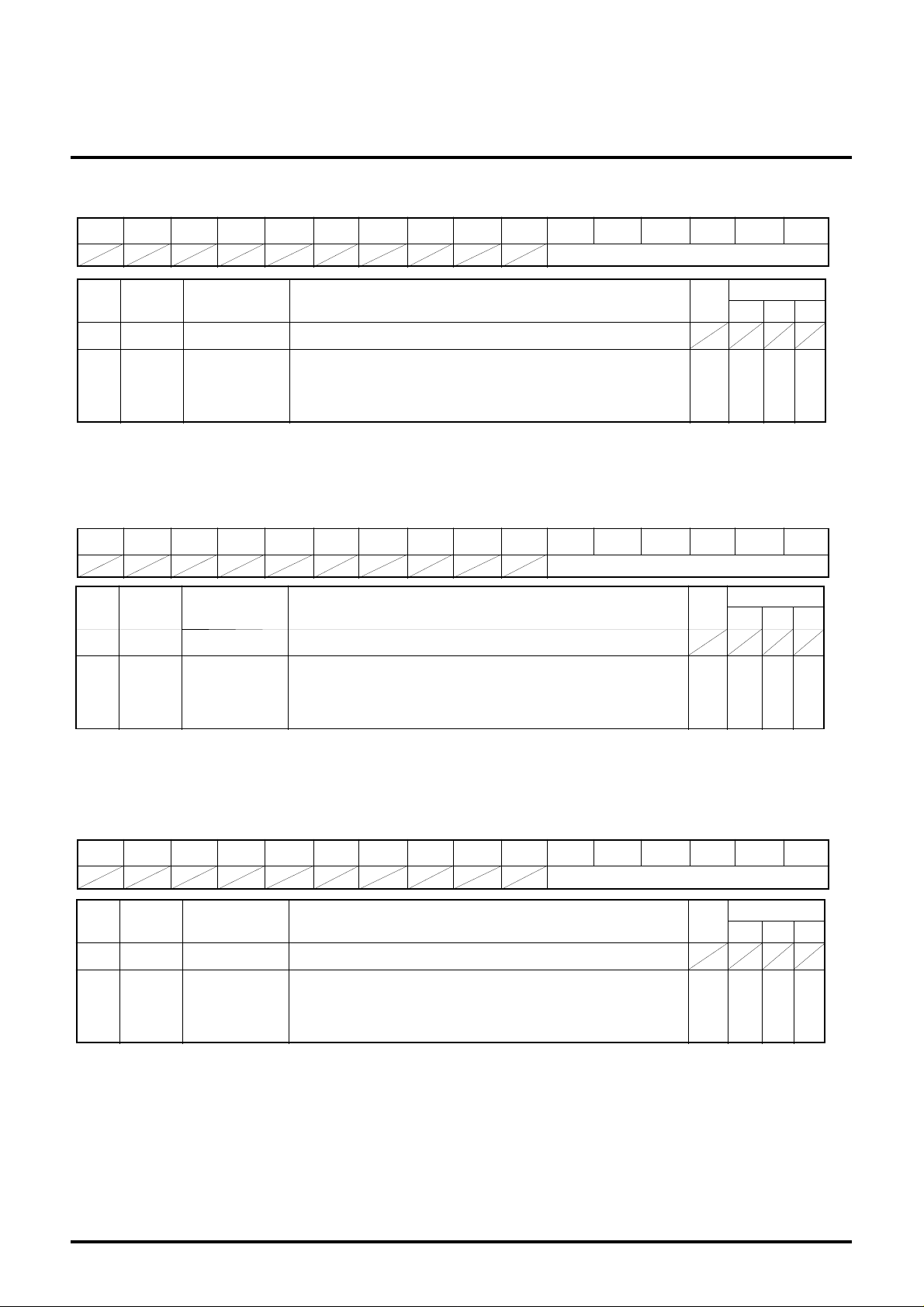

PIN CONFIGURATION

(TOP VIEW)

TEST2 INPUT

INTERRUPT

WRITE STROBE

DMA REQUEST

DMA ACKNOWLEDGE

Outline

M66290AGP:48P6Q-A(LQFP)

M66290AFP:48P6X-A(TQFP)

D14

D15

Dreq

Dack

24

37

38

39

40

41

42

43

44

45

46

47

48

M66290AGP

OR

M66290AFP

D1

23

D0

22

A6

21

A5

20

A4

19

A3

18

A2

17

A1

16

VCC

15

GND

14

13

OSCILLATOR INPUT

Xin

Xout

OSCILLATOR OUTPUT

c MITSUBISHI ELECTRIC CORPORATION

1

USB DEVICE CONTROLLER

XinCSRDWRINT

Dreq

GND

21536

Clock

Unit

A6 to 1

Register

(3KByte FIFO)

Dack

11635

4

3

Vbus

13

14

6

TrON

5

Xout

45

44434217222340

D15 to 0

47

48

41

7

RST

TEST2

TEST1

89101112

TRST

TCK

TMS

TDI

TDO

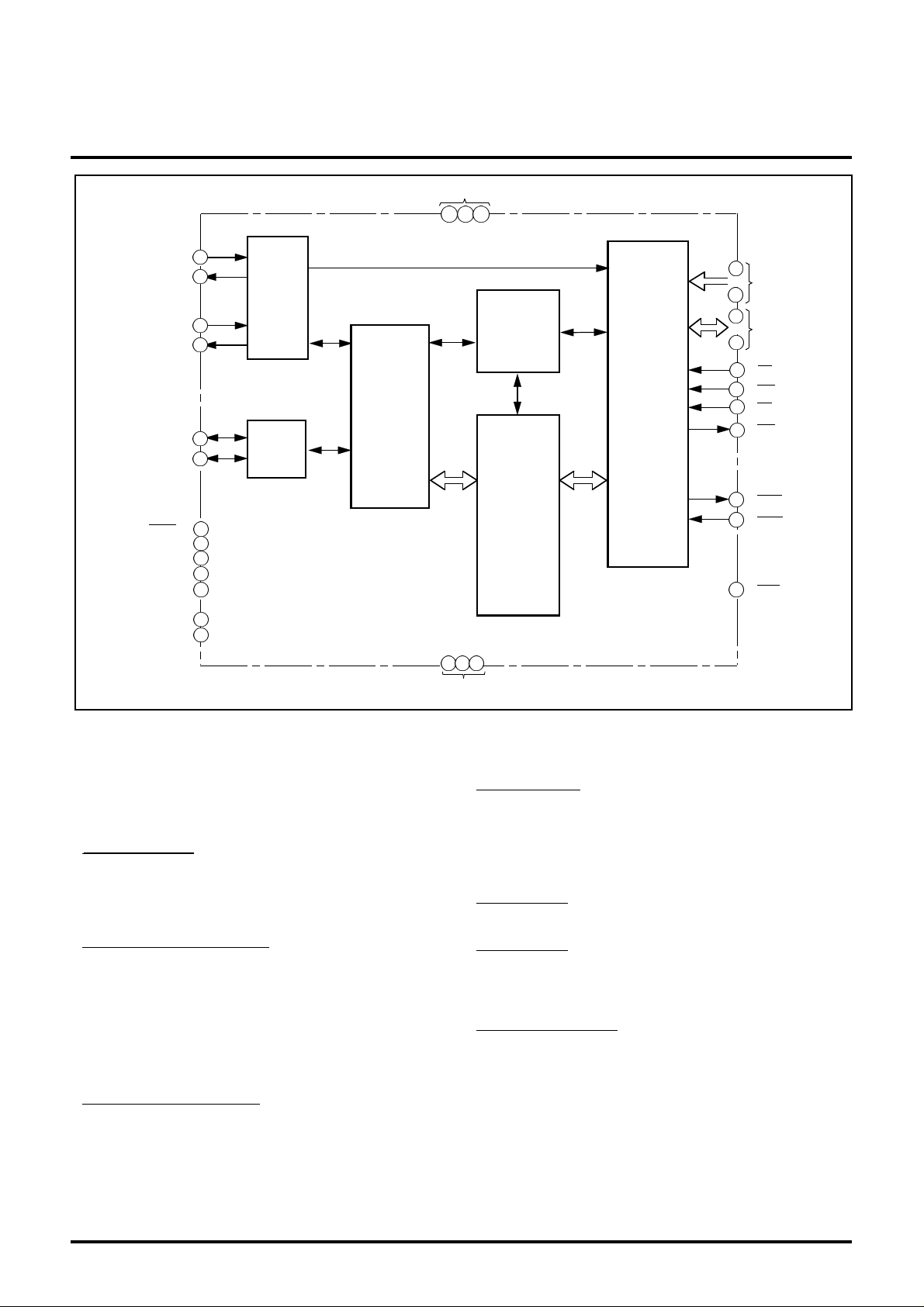

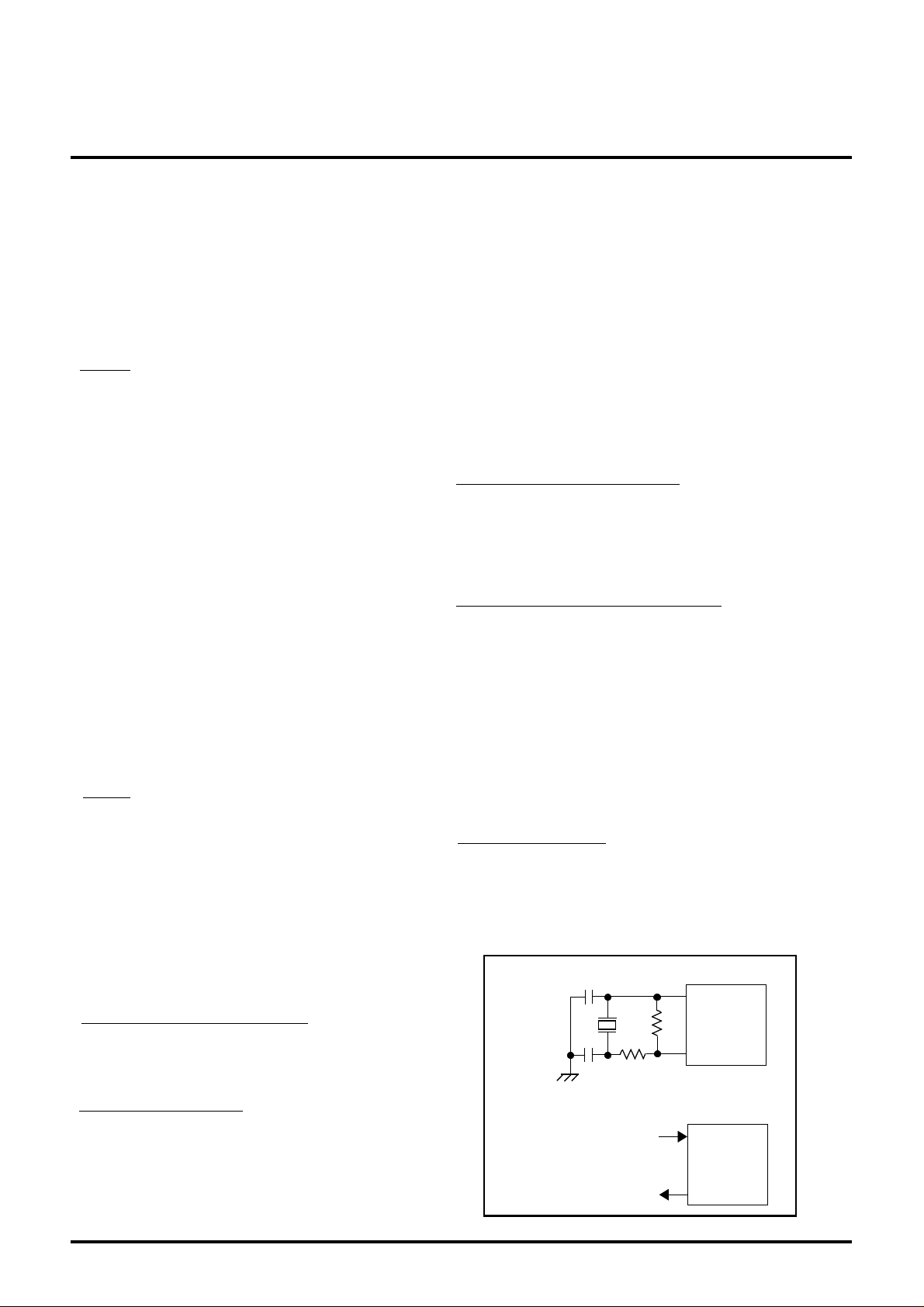

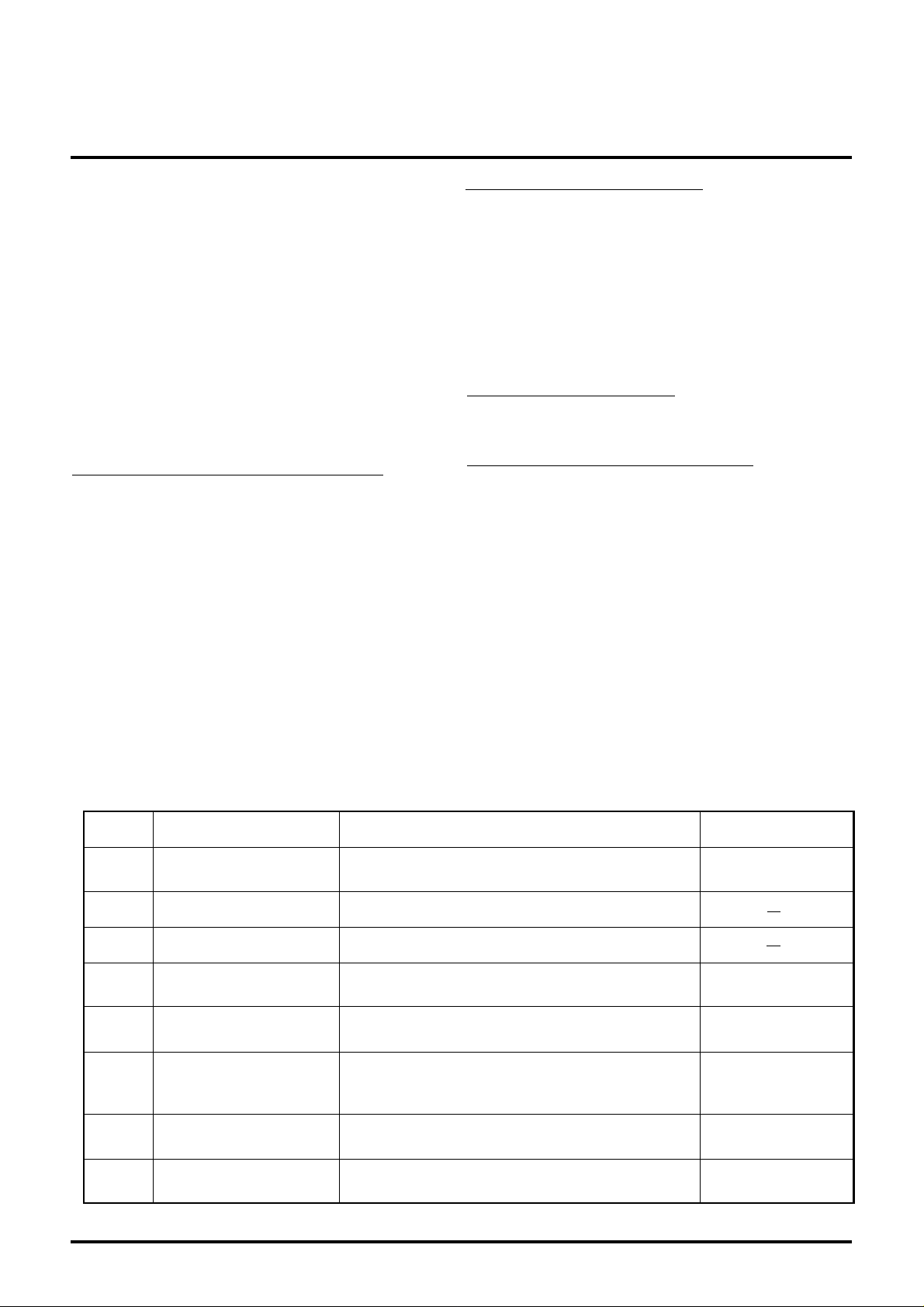

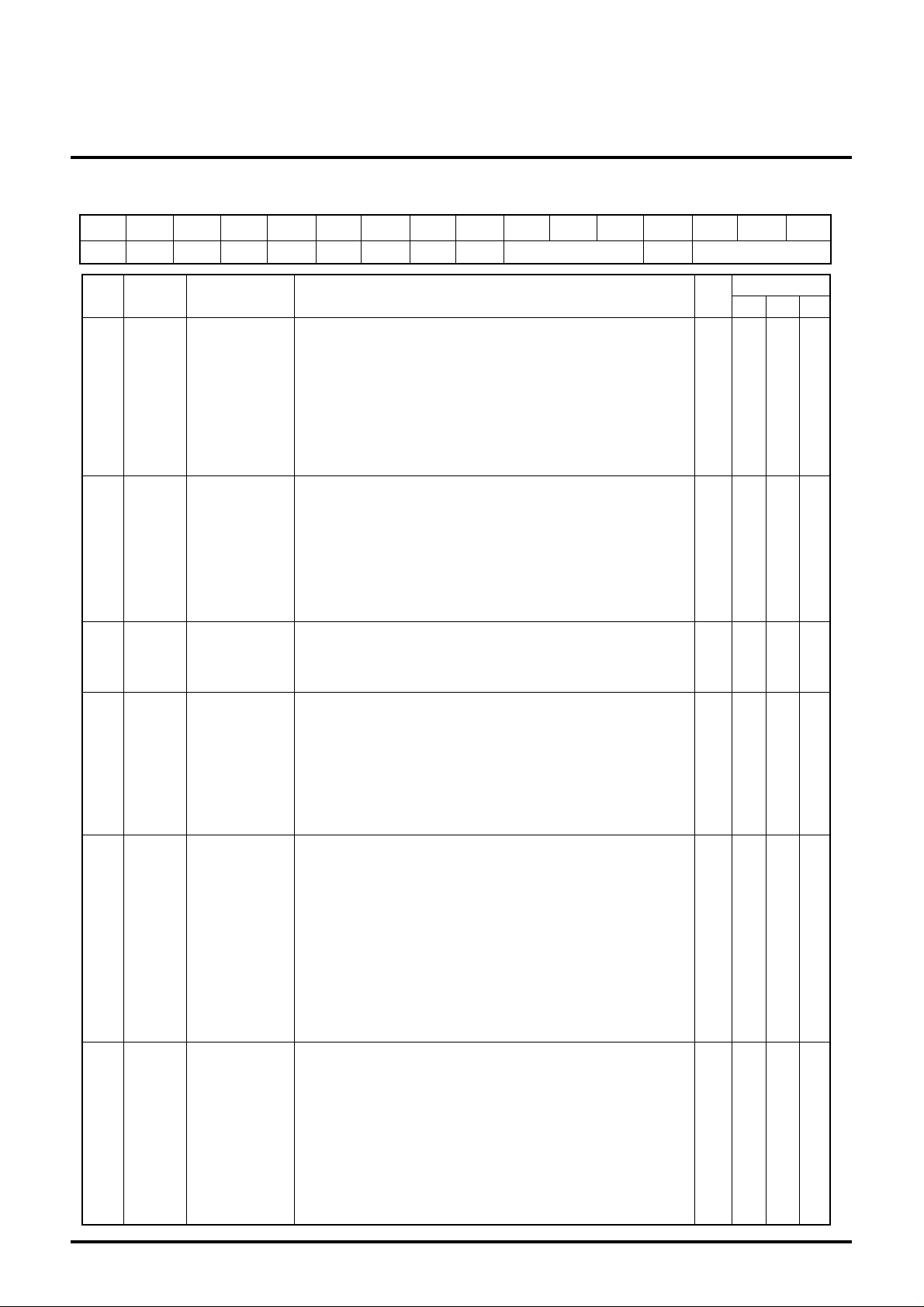

BLOCK DESCRIPTIONS

BLOCK DIAGRAM

Transceiver

Control

(Oscillator/

PLL)

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

VCC

to

D+

USB

Peripheral

Circuit

Serial

Interface

Engine

USB

D-

Device

Control

Endpoint

Buffer

to

CPU

68

68

46

The M66290A contains USB transceiver, oscillation

circuit, PLL, serial interface engine, endpoint buffer,

device control unit, and CPU register.

USB Transceiver

USB Transceiver is consisted of differential driver

and differential receiver.

And is compatible with USB specification version 1.1

and corresponds to Full Speed Transfer mode.

Serial Interface Engine (SIE)

SIE handles protocol layer as follows.

Extract a USB 12MHz clock

Serial-Parallel data conversion

SYNC detection

NRZI encode and decode

Bit stuffing and destuffing

CRC generator and checker

Device Control Unit (DCU)

DCU controls the device state sequence, control

transfer sequence, and so on.

Endpoint Buffer

This is a FIFO buffer for transmit and receive

between endpoints.

Except for EP0 for control transfer, five endpoints

(EP1 to EP5) can be set.

CPU Register

This is an interface block with CPU.

Oscillator/PLL

This block oscillates the internal operation clock

source of 48MHz.

External clock of 6/12/24/48MHz can be input.

USB peripheral circuit

Detect the connection and the shutdown of USB

by the Vbus input.

Connect the Vbus of USB bus to or the 5V power

supply to Vbus input.

Connect the TrON output to D+ pull-up resistor of

1.5kohm. ON/OFF of the pull-up resistor is controlled

by the register.

2

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

OSCILLATO

OSCILLATO

-

ON/OFF control of the pull-up resistor is available.

Input/

PIN DESCRIPTIONS

M66290AGP/FP

Item Pin name

D15 to D0

CPU

interface

interface

interface

WR Input

INT Output

Dreq Output

DMA

D+

D-

USB

Vbus

TrON

DATA BUS

Input/

Data bus to access the register from the system

Output

ADDRESS BUS

Input A6 to A1

Address bus to access the register from the system

CHIP SELECT

Input CS

"L" level enables to communicate with M66290A

WRITE STROBE

Input data is written into the register by the positive edge

READ STROBE

Input RD

Register data can be read when "L" level

INTERRUPT

"L" level requests interrupt to system

DMA REQUEST

DMA transfer request to endpoint FIFO

DMA ACKNOWLEDGE

Input Dack

FIFO access by DMA transfer is available in "L" level

Input/

USB DATA(+)

Output

D+ of USB. Connect the external resistor serially.

USB DATA(-)

Input/

D- of USB. Connect the external resistor serially.

Output

Vbus INPUT (Built-in pull down resistor)

Input

Connect to the Vbus of USB bus or to the 5V power supply.

Connection or shutdown of the Vbus can be detected.

TrON OUTPUT

Output

Connect to the D+ pull-up resistor of 1.5kohm.

Function

Number of

16

6

1

1

1

1

1

1

1

1

1

1

JTAG

interface

Others

Input TRST

TMS Input

TCK

TDI

TDO

Input

Input

Output

Input RST

Input Xin

Output Xout

Input TEST1

Input TEST2

-

GND

TEST RESET INPUT (Built-in pull up resistor)

Reset input of JTAG. Even if the JTAG is not used, JTAG circuit must be

initialized. Input "L" level to initialize like the RST input.

TEST MODE INPUT (Built-in pull up resistor)

Mode set input to JTAG. If JTAG is not used, keep "H" level or open.

TEST CLOCK INPUT (Built-in pull down resistor)

Clock input to JTAG. If JTAG is not used, keep "L" level or open.

TEST DATA INPUT (Built-in pull up resistor)

Data input to JTAG. If JTAG is not used, keep "H" level or open.

TEST DATA OUTPUT

Data output from JTAG. If the JTAG is not used, keep open.

RESET

"L" level initializes the register or the counter of M66290A.

Generate an internal clock.

R INPUT

R OUTPUT

TEST1 INPUT (Built-in pull down resistor)

Input for the test. Keep "L" level or open.

TEST2 INPUT (Built-in pull down resistor)

Input for the test. Keep "L" level or open.

Power supply pin VCC

Ground

Input or output of internal clock oscillator. When use as a crystal oscillator, connect a

crystal between Xin and Xout.

If an external clock is used, input it to Xin, and Xout must be opened.

1

1

1

1

1

1

1

1

1

1

3

3

3

USB DEVICE CONTROLLER

USB DATA TRANSFER DESCRIPTIONS

Data receive

When M66290A received IN token packet again from host,

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

M66290A is a USB device controller correspond to all

the four types of transfer (control, bulk, isochronous,

and interrupt transfer), which is compatible to USB

specification 1.1.

M66290A acts USB functions as below automatically.

(1) Bit stuffing/destuffing

(2) CRC generate/check

(3) NRZI encode/decode

(4) Packet handling

(5) USB address check

(6) Bus error handling

Therefore, when CPU transact the operations as

follows, USB transfer is realized.

(1) Response to the control transfer request

(2) Permission of store and transmission of the

transmit data into the endpoint buffer.

(Or read of the received data from the endpoint

buffer)

(3) Stall handling

(4) Suspend/resume handling

Below are the descriptions about the data transfer.

Data transmit

When the data of endpoint FIFO, which corresponds to

transmit request by IN token packet, is ready, M66290A

transmit the corresponded data packet to USB bus.

If the ACK packet come from the host for the transmitted

data packet, a transaction completed and the endpoint

FIFO becomes empty and urge CPU to write the next

transmit data by buffer ready interrupt.

If the transmit data, which correspond to transmit request

by IN token packet, is not exist in the endpoint FIFO,

M66290A transmit NAK packet to host when received

IN token packet from host and occurs interrupt and

request CPU to write transmit data.

M66290A transmits the data which is written.

If error is not occurred in that transfer, host transmit ACK

packet and if M66290A received it normally, a transaction

completed.

If USB protocol error is occurred in the data which is

transmitted via USB bus, host does not transmit ACK

packet, so M66290A watch and wait until receive IN token

packet, with keeping the data to be transmitted.

In data receive, there are differences of its function

between setup transaction and out transaction.

In setup transaction, when received device request

from host, 8Byte request is always stored into four

resistors.

When request data is received correctly,sends back

ACK packet to host and at the same time, occurs

interrupt to CPU and urge CPU to read request.

In out transaction, after M66290A received OUT

token packet, host transmits data packet.

If packet of maximum packet size or short packet

is stored into the endpoint FIFO of M66290A, and

moreover, error is not occurred in that transfer,

M66290A transmits ACK packet to host and informs

CPU that the data was received by occurring buffer

ready interrupt.

If USB protocol error is occurred in the host data

which received via USB bus, or if the endpoint FIFO

is full, M66290A does not transmit ACK packet to

host. Host knows that the error occurred because the

ACK packet does not come, and take a step such as

data resend.

4

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

-

0000h

0000h

R/W-0000h

0000h

R/W--------------

0000h

0000h

R/W

Interrupt Status Register2

1Ch-0000h

0000h

R/W

Interrupt Enable Register2

14h-0000h

0000h

-

0000h

0000h

-

0000h

0000h

Note 2

0000h

0000h

-

0000h

0000h

--0000h

--0000h

--0000h

--0000h

-

0000h

-

0008h

-

0000h

-

0000h

-

xxxx-0000h

-

0000h

-

0800h

-

xxxx-0000h

-

0800h

-

xxxx--

0000h

--0040h

--0000h

--0040h

--0000h

--0040h

--0000h

--0040h

--0000h

0000h

0000h

-

-

-

USB

0000h

0000h

0000h

-

S/W

0000h

0000h

0000h

H/W

R/W

R/W

R/W

R/W

R/W

R/WRRRRRR/W (note 2)

R/W

R/W

R/W (note 2)

R

R/W

R/W

R/W

R/W

R/W (note 2)

R/W

R/W

R/W (note 2)

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

EP5 Configuration Register0

EP4 Configuration Register1

EP4 Configuration Register0

EP3 Configuration Register1

EP3 Configuration Register0

EP2 Configuration Register1

EP2 Configuration Register0

EP1 Configuration Register1

EP1 Configuration Register0

Reserved

DMA_FIFO Data Register

DMA_FIFO Control Register

DMA_FIFO Selection Register

Reserved

CPU_FIFO Data Register

CPU_FIFO Control Register

CPU_FIFO Selection Register

Reserved

EP0 Continuous transmit Data Length

EP0_FIFO Data Register

EP0_FIFO Selection Register

Reserved

Auto-response Control Register

EP0 Packet Size Register

Control Transfer Control Register

Length Register

Index Register

Value Register

Request Register

Interrupt Status Register3

Interrupt Status Register1

Interrupt Status Register0

Interrupt Enable Register3

Interrupt Enable Register1

Interrupt Enable Register0

Reserved

IsochronousStatus Register

USB_Address Register

Reserved

Sequence Bit Clear Register

Remote Wake-up Register

USB Operation Enable Register

4Eh to 5Eh

70h

6Eh

6Ch

6Ah

68h

66h

64h

62h

60h

4Ch

4Ah

48h

46h

44h

42h

40h

38h to 3Eh

36h

34h

30h

2Eh

2Ch

2Ah

28h

26h

24h

22h

20h

1Eh

1Ah

18h

16h

12h

10h

0Ch to 0Eh

0Ah

08h

06h

04h

02h

00h

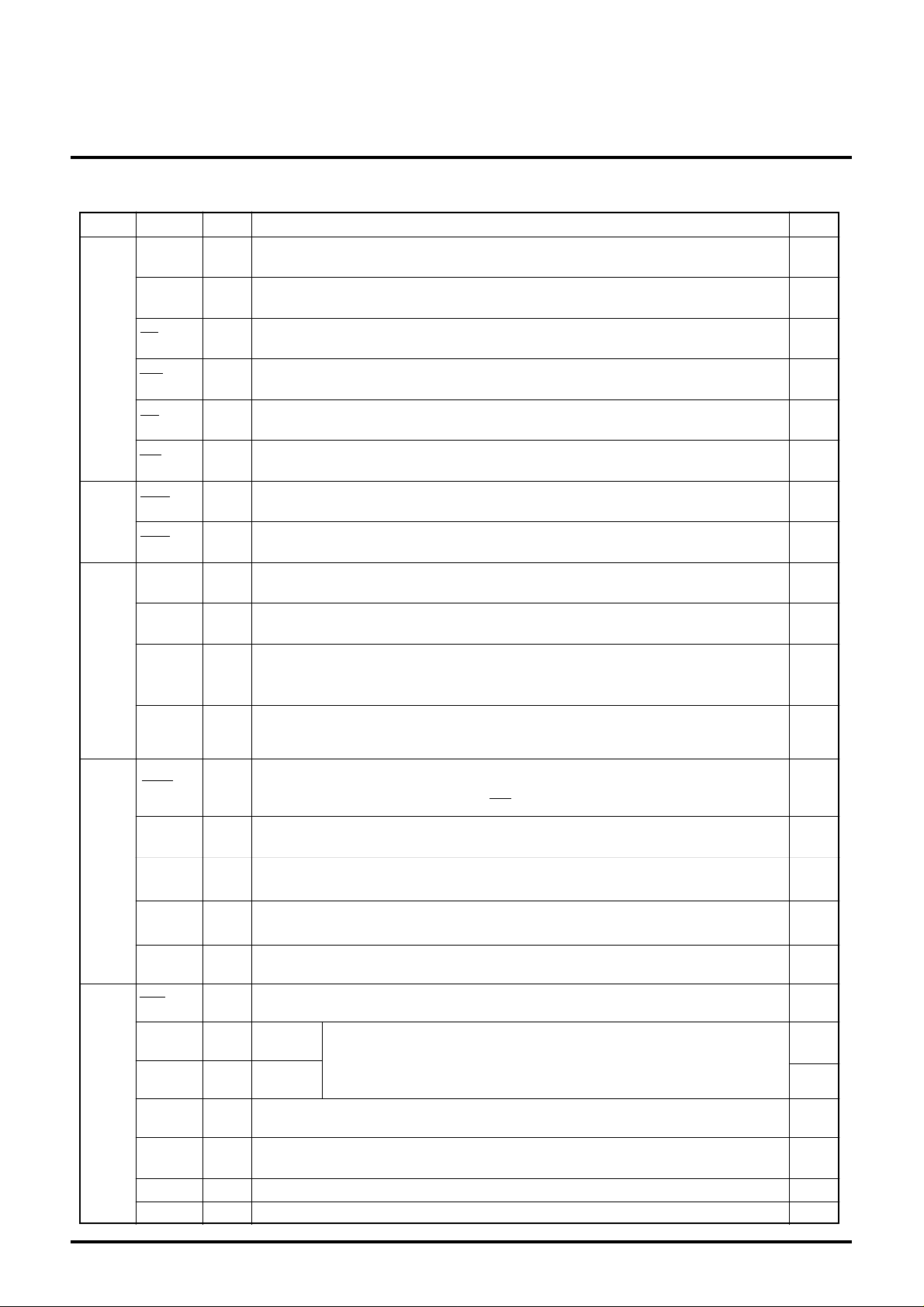

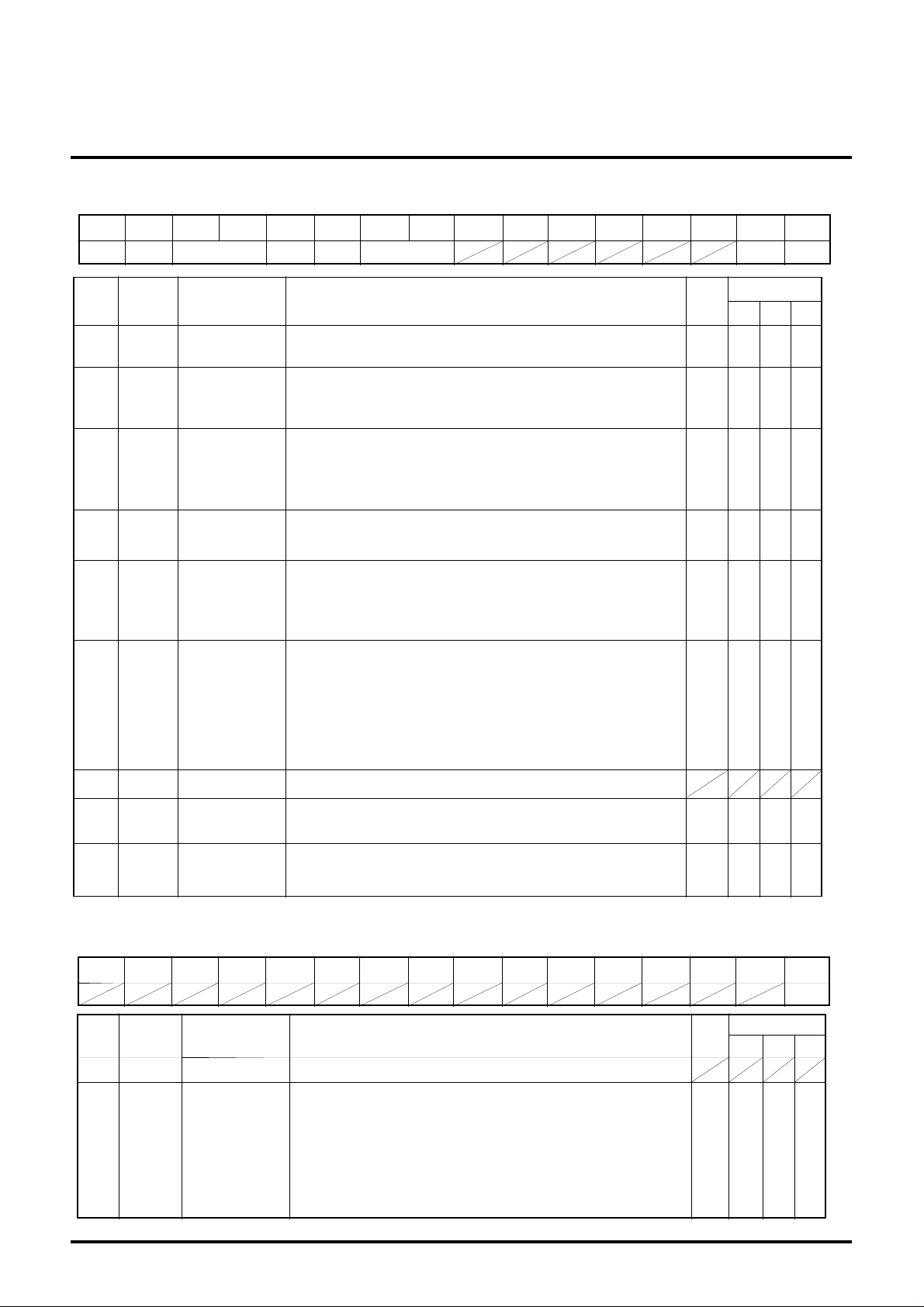

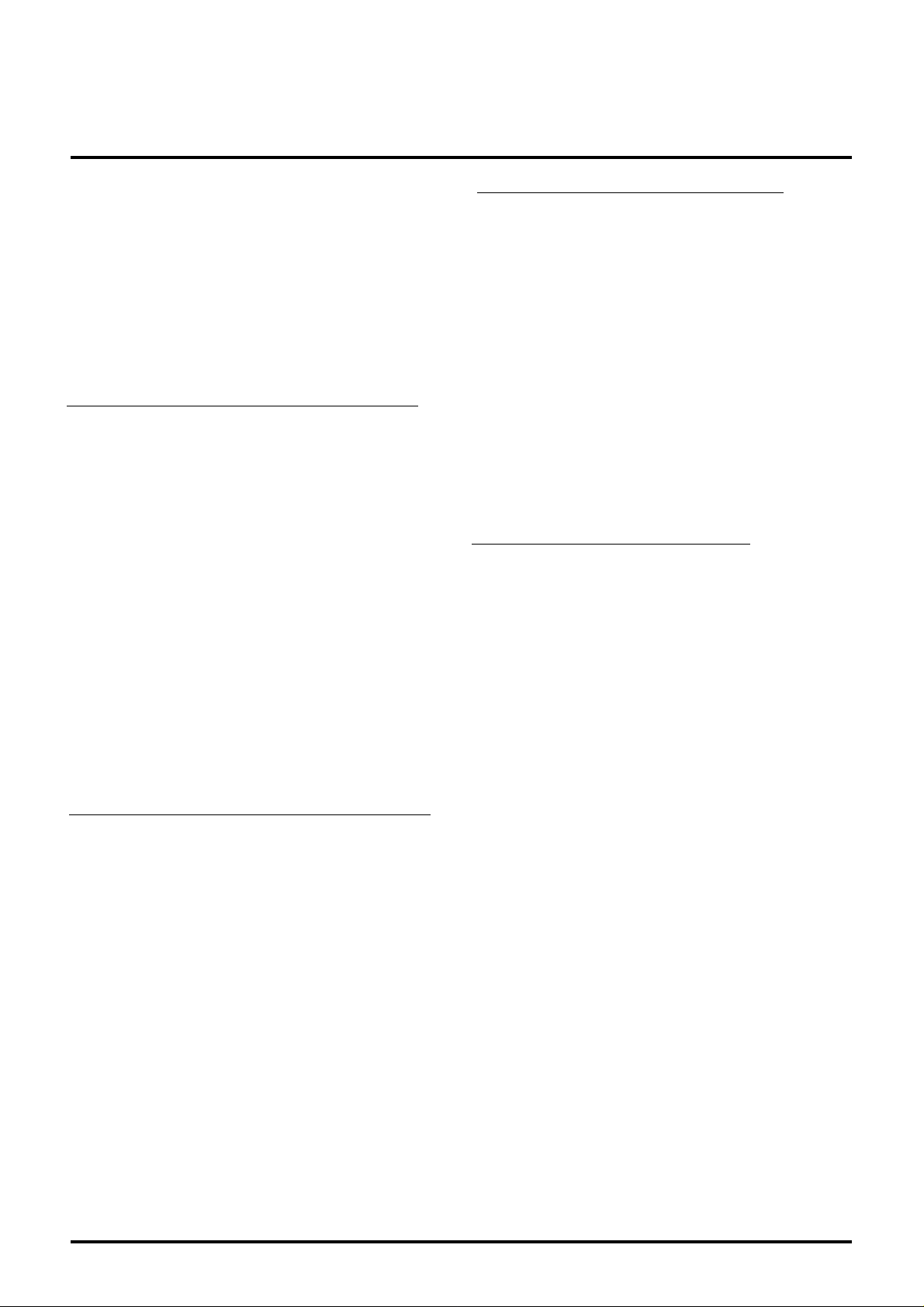

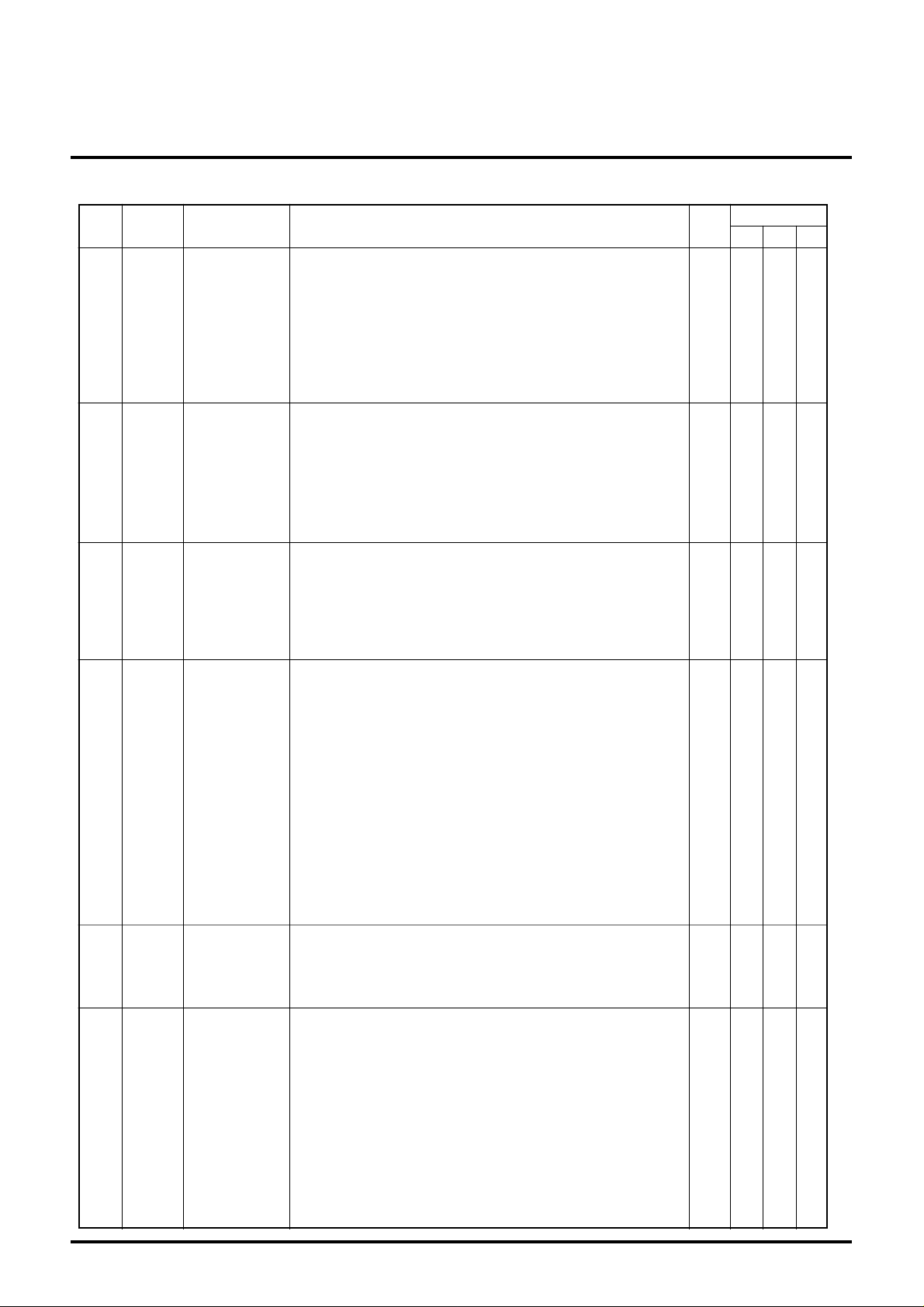

CONTROL REGISTER TABLE

M66290AGP/FP

Below is the table of registers of M66290A.

Bit width of all register is 16bits.

In reset item, "H/W" shows the reset status

by external RST input, "S/W" shows reset

status by USBE register, and "USB"

Address Name R/W

shows the reset status by receiving USB reset.

" - " shows that the previous status is kept.

Write into reserved address is inhibited.

32h

note 1 : Detail description is mentioned later.

note 2 : Some are read only.

EP0_FIFO Control Register

R/W (note 2)

5

-0800h

USB DEVICE CONTROLLER

Functional and register descriptions

We explain about Function and register constitution of

M66290A dividing into four items as follows.

by self oscillation.

n USB reset (when more than 2.5us of SE0 state

firmware to manage incorrect transfer in case of transfer

from CPU as follows, USB_Address register (USB_Addr),

process, that is, enables clock input by XCKE, wait

until oscillation stabilized (less than 1ms), and start

wakeup signal and can cancel suspended state to receive

(1) System control

(2) Interrupts

(3) Control transfer/enumeration

(4) Endpoints and FIFO control

(1) System control

CLOCK

Clock of 48MHz is needed for internal operations

of M66290A.

Built in PLL enables to input external clock of 6/12/

24/48MHz. Selection of it is realized by the XTAL

of "USB Operation Enable Register".

When use external clock of 48MHz, PLL is not

needed, so set to PLL operation disable.

Built in oscillation circuit enables to supply clock

To set the "USB Operation Enable Register", it can

be set the device to standby state. Oscillation is

halted (clock input halted) by XCKE, PLL operation

is halted by PLLC, and clock supply to USB block

is halted by SCKE.

To prevent unstable behavior by unstable clock,

clock supply to USB block must be obeyed the

until oscillation stabilized, start PLL by PLLC, wait

clock supply to USB block by SCKE.

RESET

S/W reset by the register set (USBE), different from

the hardware reset, keeps the value of register of

USB operation enable register, FIFO relational

register, control transfer relational register,endpoint

setting register, and so on.

And i

is continued on D+, D- terminal), the value of register

is kept except for "Interrupt Status Register 0" and

"USB_Address Register"

As to details of reset state, see each item of register.

D+ pull-up resistor control function

To set the register, external TrON output is controlled

and can control the ON/OFF of pull-up resistor

(1.5kohm) on USB D+ line.

Remote wakeup function

When device is in suspended state, outputs remote

resume from USB.

Remote wakeup function is only effective in Suspended

state in which device state shifts from Configured state,

so don't use to other device state.

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

And when use this function, device state shifts to Address

state after outputs remote wakeup signal, so it is needed

to set up again the device state to Configured state.

Change of set up of device state can be done in S/W

control mode.

Remote wakeup signal is a signal to set USB bus to idle

state after output K-state of 10ms length.

If this remote wakeup function is set up immediately after

detected suspend, USB bus idle state is kept for 2ms and

then shifts to K state output. (Because USB bus idle state

must be kept for 5ms minimum until transmit of remote

wakeup signal, on the other hand after detect suspend,

USB idle state is continued for 3ms)

Sequence toggle bit clear function

In each endpoint of EP0 to EP5, data PID can be reset

independently and also can appoint PID of DATA0.

By this function, management of sequence toggle bit

in transfer after reset PID, is done by H/W automatically.

Error information in isochronous transfer

In isochronous transfer there is not retry function of

transmit/receive, because the handshake from receiver

to transmitter is not returned not to disturb the time

equivalent data transfer.

M66290A has enough information function which enables

error occurred in isochronous transfer.

Information which M66290A can inform is, over run

error, under run error, received data error (CRC error,

bit stuffing error), and frame number.

Software control mode

In software control mode, it is available to set up (write)

device state register (DVSQ), control transfer stage

register (CTSQ).

Normally, use this mode with OFF.

(1) In case of crystal oscillation

Place the parts as near the terminal as possible

(2) In case of external clock input

Figure 1. Xin and Xout connections

C1

XTAL

Rd

C2

clock input

open

Rf

Xin

M66290A

Xout

Xin

M66290A

Xout

6

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

USBPC

(1-2) Remote Wake-up Register

(Address : 02h)

(1-1) USB Operation Enable Register (Address : 00h)

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

SCKEPLLCXCKE USBE

Tr_on[1:0]XTAL[1:0]

SCTR

Bit

14

13, 12

11

10

9, 8

Bit

Name

XCKE15 Oscillator enable

SCKE

USBPC

Tr_on

[1:0]

Name Function W/R

PLL controlPLLC

Crystal selectXTAL[1:0]

Internal clock

enable

USB transceiver

power control

Tr_on output

control

0 : Oscillator disable (clock input disable)

1 : Oscillator enable (clock input enable)

0 : PLL disable

1 : PLL enable

When use external clock of 48MHz, set to PLL disable.

00 : 1/1 division (external 48MHz input)

10 : 1/2 division (external 24MHz input)

01 : 1/4 division (external 12MHz input)

11 : 1/8 division (external 6MHz input)

0 : Internal clock (sck) disable

1 : Internal clock (sck) enable

0 : USB transceiver disable

1 : USB transceiver enable

In suspend state, resume signal can be received even if USB

transceiver disabled.

X0 : TrON port ="Hi-Z"

01 : TrON port ="L"

11 : TrON port ="H"

This fields selects TrON output state, and it is effective when

external Vbus input is "H" level (5V). If external Vbus input is "L",

these bits can be set but TrON output does not operate.

Reset

USBS/WH/W

--0W/R

--0W/R

--00W/R

--0W/R

--0W/R

--00W/R

Reserved

7 to 2

0

Bit

Reserved

15 to 1

0 Remote wake-upWKUP

SCTR1

USBE

Bit

Name

Software control

mode

USB module

enable

Name

Write/Read "0"

0 : Normal Operation

1 : Software Control Mode Operation

0 : USB module disable (S/W Reset)

1 : USB module enable

Function W/R

Write/Read "0"

When CPU write "1" to WKUP for remote wake-up, M66290A outputs

K-State for 10ms, and return to Bus Idle-State.

(Remote wake-up signal)

This bit returns to "0" automatically after suspend is canceled.

If "1" is written into this bit after detected suspend, bus idle state is kept

for 2ms and after then shifts to K state output.

--0W/R

--0W/R

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

WKUP

Reset

USBS/WH/W

-00W/R

7

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

Sequence toggle bit

(1-3) Sequence Bit Clear Register (Address : 04h)

(1-4)USB Address Register (Address

:

08h)

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

SQCLR[5:0]

Bit Name Function W/R

15 to 6

5 to 0

Bit

15 to 7

Bit

Name

Reserved

SQCLR

[5:0]

Bit

Name

Reserved

Write/Read "0"

When write "1" into the bit which is correspond to the number

of endpoint, sequence toggle bit of that endpoint is cleared

and appoint the DATA0 by the data PID of next transmission.

Write "1" into the bit after set the response PID of the endpoint, which

clears sequence toggle bit, to NAK("00") .

clear

Name Function W/R

Transfers After the transfer appointed, sequence toggle bit is controlled

by H/W.

In USB reset, Sequence toggle bit of each endpoint is not cleared.

If "0" is written into this bit, flag is not changed.

Read data of this bit is always "0".

USB_Addr[6:0]

Write/Read "0"

Reset

USBS/WH/W

-00h00hW/R

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

Reset

USBS/WH/W

6 to 0 USB_Address

USB_

Addr

[6:0]

register

USB address which is assigned by host is stored.

After stored the address, transaction is done only to the token packet

which is transmitted to this address.

(If S/W control mode is set, write operation is available)

8

00h00h00hR

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

(1-5) Isochronous Status Register

(

Address

:

0Ah

)

FMODCRCEOVRN FRNM[10:0]

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

Bit

Name

OVRN15 Over run error

14

FunctionNameBit

In isochronous transfers (OUT/IN), when over-run or under-run is

occurred to the endpoint buffer, this flag is set at the timing of the

receive end of the OUT/IN token packet.

Over run is occurred when delayed to read the received data from

the endpoint buffer, and means that could not received. Over run is

occurred when the direction of transmission is OUT.

Also the received data has CRC or bit stuffing error, this flag is set.

Under run is occurred when delayed to write the transmit data into the

endpoint buffer, and means that could not transmitted. Under-run is

occurred when the direction of transmission is IN.

When a state above is occurred, endpoint buffer notready interrupt is

occurred.

When "0" is written, status flag is cleared.

When "1" is written, flag is not changed.

In isochronous transfers(OUT), if the received data has CRC or

bit stuffing error, this flag is set at the timing of the end of transaction.

When a state above is occurred, endpoint buffer notready interrupt is

Receive data errorCRCE

occurred.

W/R

Reset

USBS/WH/W

-00W/R

-00W/R

13 to 12

Reserved

FMOD11

FRNM

[10:0]

Frame number

mode

Frame number10 to 0

When "0" is written, status flag is cleared.

When "1" is written, flag is not changed.

Write/Read "0"

Select the renewal timing of the flame number to be stored

to FRNM[10:0].

0 : Renew the flame number when SOF is received .

1 : In isochronous transfer, renew the flame number at the

timing of the end of transaction.

Stores the flame number.

The timing to renew the stored flame number is selectable by set

FMOD.

-00W/R

-000h000hR

9

USB DEVICE CONTROLLER

(2) Interrupts

There are eight factors of interrupt to CPU.

If disable is set, interrupt is not occurred but interrupt

When buffer of each endpoint became ready

If the internal clock(sck) is halted, status flag can not

Summary of interrupts

When interrupt occurred, the factor can be known to

refer to "Interrupt Status Register 0" and "Interrupt

Status Register 1".

These interrupts can be set of its enable/disable

independently to set "Interrupt Enable Register 0"

and "Interrupt Enable Register 1".

status flag is set.

Each factor of interrupt is shown in the table below,

and also describes below the interrupt conditions and

how to deal with the interrupt.

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

Resume detect interrupt (RESM)

If device state is in suspended state and resume interrupt

enable flag is set, interrupt occurs when USB bus state

is changed ("J" to "K" or "SE0").

This interrupt can be occurred even if the internal

clock(sck) is halted. To clear the status flag, set the

internal clock(sck) in operation and then write "0". If the

internal clock(sck) is halted, status flag can not be

cleared.

SOF detect interrupt (SOFR)

Interrupt occurs when detect SOF.

Vbus (connect/shut down) interrupt (VBUS)

Interrupt occurs when Vbus input state is changed

(both "L" to "H" and "H" to "L").

To know Vbus input state, confirm the Vbus bit of

interrupt status register 0. Confirmation of Vbus bit

must be done after enabled internal clock operation.

This interrupt can be occurred even if the internal

clock(sck) is halted. To clear the status flag, enables

the internal clock(sck) in operation and then write "0".

be cleared.

This interrupt is useful to detect connect/shut-down of

USB for prepareration/close of USB transfers.

Status bit Name

VBUS

RESM Resume detect interrupt

Vbus interrupt

(connec/shut-down detect)

Change of the Vbus input

(both "L" to "H" and "H" to "L")

Resume signal received in suspended

Device state transition interrupt (DVST)

M66290A manages the device state by H/W.

It manages Powered, Default, Address, Configured, and

Suspended state. Device state can be known to refer to

"Interrupt Status Register 0".

As to device state shift, see the item of "Device state

shift" in "(3) Control transfer/emulation" in the latter part.

Device state transition interrupt occurs when device state

shifted. The number of factors is four, that is, USB bus

reset detect, suspend detect, execution of "Set Address",

and execution of "Set Configuration".

USB reset is detected when SE0 state over 2.5us is

continued on D+, D- terminal.

Suspend is detected when idle state over 3ms is

continued on D+, D- terminal.

Abstract of interrupt factor

Relational status bit

Vbus

SOFR SOF detect interrupt Received SOF

DVST

CTRT

BEMP

INTN

INTR

device state transition

interrupt

Control transfer

stage transition interrupt

Endpoint buffer

empty/size-over interrupt

Endpoint buffer not ready

interrupt

Endpoint buffer ready

interrupt

In each endpoint, when data transmit of all buffer

is ended and buffer is empty, or in OUT transfer,

received packet which exceeds max packet size.

When buffer is in not ready state (SIE cannot read

and write) to IN/OUT token of each endpoint.

(read enable/write enable)

Shift of device state DVSQ[2:0]

Stage shift of control transfer

10

CTSQ[2:0]

EPB_EMP_OVR[5:0]

EPB_NRDY[5:0]

EPB_RDY[5:0]

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

For example by using this interrupt, when USB bus reset

Control transfer stage transition interrupt (CTRT)

If the transfer direction is set to OUT, interrupt occurs

M66290AGP/FP

Each of "Set Address" and "Set Configuration" execution

detects the device state shift by analyzing the device

request in control transfer.

Each of these four factors can be set of its interrupt to

enable or disable by setting the corresponded bit of

interrupt enable register 0.

is detected, a step to USB bus is available and when

suspend is detected, a step to shift device to low power

consumption.

M66290A manages the sequence of control transfer

by H/W.

Each stage of control transfer, such as setup stage,

data stage, and status stage can be known to refer to

the "Interrupt Status Register 0".

Control transfer stage transition interrupt is occurred

when the control transfer stage is shifted.

There are five factors, that is, setup stage end,

control write transfer stage shift, control read transfer

stage shift, control transfer end, and control transfer

sequence error.

Except for setup stage, Each of these four factors can

be set of its interrupt to enable or disable by setting the

corresponded bit of interrupt enable register 0.

As to control transfer sequence error which can be

recognized by H/W, refer to "Control transfer stage

shift" in the item of "(3) Control transfer/enumeration"

in the latter part.

Endpoint buffer empty/size-over interrupt (BEMP)

Interrupt factor is different by transfer direction of

endpoint.

1. In case of transfer direction is IN

In each endpoint, interrupt occurs when transmission

ended of all data which is stored in the buffer.

By this interrupt, when endpoint is set to double buffer,

end of data transmission of all data of the buffer can

be known.

And also can know the end of data transmission of

control read transfer in endpoint 0 (EP0).

Endpoint buffer not ready interrupt (INTN)

When the buffer is in not ready state to IN/OUT token

of each endpoint, interrupt occurs at the timing of token

packet receive end.

By refer to EPB_NRDY[5:0] of interrupt status register 1,

it can be known which endpoint occurred the interrupt.

If endpoint is set to isochronous transfer, when over-run/

under-run error is occurred, interrupt occurs at the timing

of token packet receive end.

And if it is set to isochronous (OUT), if received data

has

error such as CRC error, interrupt occurs at the timing of

transaction end.

The variety of error in isochronous transfer is known to

refer "Isochronous Status Register".

Endpoint buffer ready interrupt (INTR)

Interrupt occurs when the buffer of each endpoint

became ready (read/write is available).

It can be known which endpoint occurred the interrupt

to refer EPB_RDY[5:0] of interrupt status register 1.

According to the endpoint and its access mode, the

factor of interrupt is different as follows.

1. In case of EP0

Interrupt occurs when receive (OUT) buffer of endpoint

0 became ready.

If it is set to control write continuous receive mode,

when continuous receive of 255 bytes ended or when

received short packet, interrupt occurs.

Interrupt is not occurred even if the transmit buffer

became ready.

2. In case of EP1 to EP5, when CPU access

Interrupt occurs when the buffer of each endpoint

became ready.

3. In case of EP1 to EP5, when DMA access

when received short data packet and then ended DMA

transfer.

Interrupt is not occurred if the transfer direction is set

to IN.

2. In case of transfer direction is OUT

In each endpoint, interrupt occurs in data packet

receive when received packet which exceeds the

maximum packet size.

By refer to EPB_EMP_OVR[5:0] of interrupt status

register, it can be known which endpoint occurred the

interrupt.

11

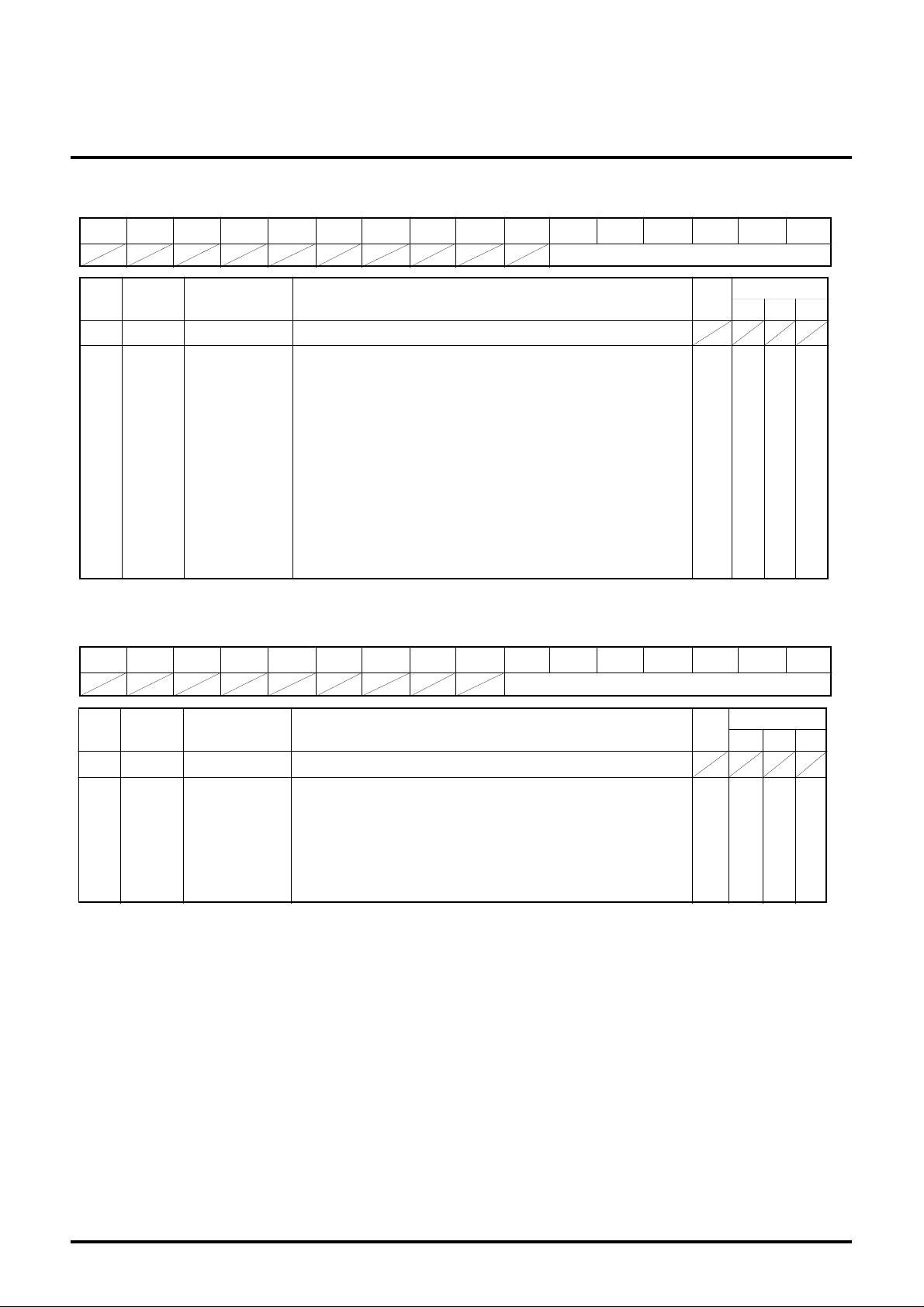

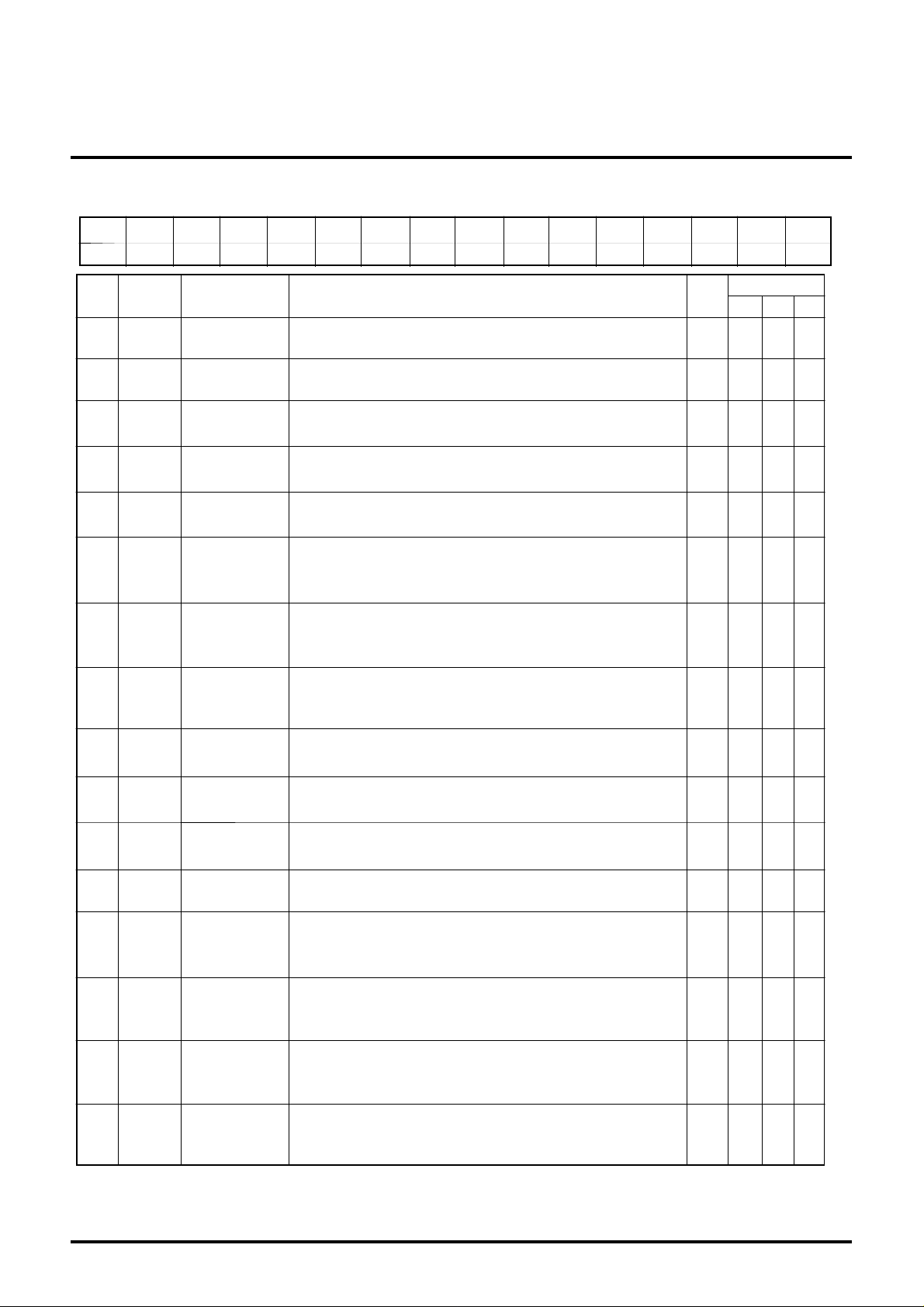

USB DEVICE CONTROLLER

Figure 2. shows the examples of interrupt output timing

(1) Endpoint buffer ready interrupt (ex.OUT transaction)

OUT token packet Data packet Hand shake packet (ACK)

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

USB

SYNC

PID

Addr

Endp CRC

EOP

SYNC

INT output

(2) Endpoint buffer not ready interrupt (ex.OUT transaction)

OUT token packet Data packet Hand shake packet (NAK)

USB

SYNC

PID

Addr

Endp CRC

EOP

SYNC

INT output

(3) Endpoint buffer not ready interrupt (ex.IN transaction)

IN token packet Hand shake packet (NAK)

USB

SYNC

PID

Addr

Endp CRC

EOP

SYNC

PID

DATA

CRC

EOP

SYNC

Buffer becomes ready (read enable)

and interrupt occurs

PID

DATA

CRC

EOP

SYNC

Buffer is in not ready (receive disable)

and interrupt occurs

PID EOP

PID EOP

PID EOP

INT output

Figure 2. Examples of interrupt output timing

Buffer is in not ready (transmit disable)

and interrupt occurs

12

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

BEMPE

(2-1) Interrupt Enable Register 0 (Address

:

10h)USB DEVICE CONTROLLER

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

WDST

RDSTINTNECTRE SERRCMPLSUSPSCFGSADRURSTINTREDVSESOFERSMEVBSE

Bit

14

13

12

11

10

Bit

Name

VBSE15

RSME

SOFE

DVSE

CTRE

BEMPE

INTNE

9

8

INTRE

Name

Vbus interrupt

enable

Resume interrupt

enable

SOF interrupt

enable

Device state

interrupt enable

Control transfer

interrupt enable

Endpoint5-0 buffer

empty/size error

interrupt enable

Endpoint5-0 buffer

not ready

interrupt enable

Endpoint5-0 buffer

ready

interrupt enable

Function W/R

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

0 : Disable

1 : Enable

Reset

USBS/WH/W

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

7

URST

6

SADR

5

SCFG

4

SUSP

WDST

3

2

RDST

1

CMPL

0

SERR

Set Address

execute

Set Configration

execute

Suspend

detect

Control write

transfer status

stage

Control read

transfer status

stage

Control transfer

complete

Control transfer

sequence error

If this bit is "1", then the DVST flag is set when detected USB reset.USB reset detect

If this bit is "1", then the DVST flag is set after executed SetAddress.

If this bit is "1", then the DVST flag is set after executed SetConfigration.

If this bit is "1", then the DVST flag is set when detected suspend.

If this bit is "1", then the CTRT flag is set when shifted to status stage

in control write transfer.

If this bit is "1", then the CTRT flag is set when shifted to status stage

in control read transfer.

If this bit is "1", then the CTRT flag is set when control transfer

completed (when the status stage completed normally).

If this bit is "1" then the CTRT flag is set when error

occurred in the sequence of control transfer.

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

-00W/R

13

MITSUBISHI <DIGITAL ASSP>

(2-2) Interrupt Enable Register

1(

Address

:

12h

)

(2-4) Interrupt Enable Register 3

(

Address

:

16h

)

(2-3) Interrupt Enable Register

2 (

Address

:

14h

)

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

EPB_RE[5:0]

Bit

5 to 0

Bit

5 to 0

Bit

Name

Reserved15 to 6

EPB_RE

[5:0]

Bit

Name

Reserved15 to 6

EPB_NRE

[5:0]

Name Function W/R

Write/Read "0"

Endpoint5-0 buffer

ready

interrupt enable

Name Function W/R

Endpoint5-0 buffer

not ready

interrupt enable

0 : Disable

1 : Enable

The number of endpoint is correspond to each bit one by one.

Write/Read "0"

0 : Disable

1 : Enable

The number of endpoint is correspond to each bit one by one.

Reset

USBS/WH/W

-00h00hW/R

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

EPB_NRE[5:0]

Reset

USBS/WH/W

-00h00hW/R

Name

Reserved15 to 6

EPB_

EMPE

Bit

[5:0]

Endpoint5-0 buffer

empty/size error

interrupt enable

Bit

5 to 0

EPB_EMPE[5:0]

Name Function W/R

Write/Read "0"

0 : Disable

1 : Enable

The number of endpoint is correspond to each bit one by one.

14

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

Reset

USBS/WH/W

-00h00hW/R

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

(2-5) Interrupt Status Register 0

(

Address

: 18h)

M66290AGP/FP

D0D1D2D3D4D5D6D7D8D9D10D11D12D15 D13D14

BEMP INTN VALIDDVSQ[2:0] CTSQ[2:0]CTRT VbusINTRDVSTSOFRRESMVBUS

Bit

Name

This bit changes to "1" when Vbus input changed both "0" to "1" and

"1" to "0".

As to the Vbus input state, confirm to see the bit of Vbus input port.

Vbus interrupt

14

RESM

SOFR

13

12

DVST

Resume detect

interrupt

SOF detect

interrupt

Device state

transition interrupt

This bit is set even if the internal clock (sck) is in halt state.

If "0" is written after enabled internal clock as operation, status flag is

cleared. But if internal clock is in halt state, flag is not cleared.

If "1" is written, flag is not changed.

This bit changes to "1" when USB bus state changed("J" to "K" or "SE0")

under the condition that resume interrupt enable flag is set.

This bit is set even if the internal clock (sck) is in halt state.

If "0" is written after enabled internal clock as operation, status flag is

cleared. But if internal clock is in halt state, flag is not cleared.

If "1" is written, flag is not changed.

This bit changes to "1" when detected SOF.

If "0" is written, status flag is cleared.

If "1" is written, flag is not changed.

This bit changes to "1" when device state shifted.

There are four factors, that is, USB reset detect, suspend detect,

"Set Address" execution, and "Set Configuration" execution.

These four factors can be masked by the corresponded bit of

"Interrupt Enable Register0" .

If "0" is written, status flag is cleared.

If "1" is written, flag is not changed.

FunctionNameBit

W/R

Reset

USBS/WH/W

-00W/RVBUS15

-00W/R

-00W/R

100W/R

Control transfer

11

CTRT

BEMP10

stage transition

Endpoint5-0 buffer

empty/size error

interrupt

interrupt

This bit changes to "1" when the stage of control transfer is shifted.

There are five factors, that is, setup stage end, control write transfer

status stage shift, control read transfer status stage shift, control transfer

end, and control transfer sequence error.

Four factors, except for setup stage end, can be masked by the

corresponded bit of the "Interrupt Enable Register0".

If "0" is written, status flag is cleared.

If "1" is written, flag is not changed.

The factor is different by the direction of the transfer of each endpoint.

In each endpoint, this bit changes to "1" when the transmission of all

stored data is completed (direction:IN) and when received the packet

which is exceeded to maximum packet size (direction:OUT).

The endpoint which occurs the interrupt can be checked to see the

EPB_EMP_OVR[5:0].

This flag is cleared to clear the status flag of EPB_EMP_OVR[5:0].

15

-00W/R

-00R

USB DEVICE CONTROLLER

MITSUBISHI <DIGITAL ASSP>

M66290AGP/FP

Bit

Bit

Name

INTN9

INTR8

7

Vbus

Name Function

This bit changes to "1" at the timing of token packet receive end when

buffer respond NAK, of its not ready state, to IN/OUT token of each

Endpoint5-0 buffer

not ready

interrupt enable

Endpoint5-0 buffer

ready

interrupt enable

Vbus input port

endpoint.

The endpoint which occurred the interrupt is checked to see

EPB_NRDY[5:0].

This flag is cleared to clear the status flag of EPB_NRDY[5:0].

This bit changes to "1" when the buffer of each endpoint

became ready (read/write enable).

The endpoint which occurred the interrupt is checked to see

EPB_RDY[5:0].

This flag is cleared to clear the status flag of

EPB_RDY[5:0].

Input data from external Vbus is stored.

0: Vbus input port is "L"

1: Vbus input port is "H"

External Vbus input data is latched by the positive edge of internal clock.

Refer to this bit after enabled internal clock operation.

W/R

Reset

USBS/WH/W

-00R

-00R

Ext.Ext.Ext.R

6-4

3

2-0

DVSQ

[2:0]

VALID

CTSQ

[2:0]

Device state

Setup packet

detect

Control transfer

Stage

000: Powered State

001: Default State

010: Address State

011: Configured State

1xx: Suspended State

Device state can be known.

As to the device state shift, refer to Fig.5 in the later part.

When detect USB reset, this becomes 001: Default state automatically.

When detect suspend, this becomes 1xx: Suspended state automatically.

Whatever the automatic response mode is, this becomes 010: Address

state after executed Set_Address request, and becomes 011: Configured

state after executed Set_Configuration request.

(Write operation is available when S/W control mode is set)

This bit changes to "1" when received setup packet.

This flag does not the factor of interrupt.

When "0" is written, status flag is cleared .

When "1" is written, flag is not changed .

000 : Idle or Setup stage

001 : Control read transfer data stage

010 : Control read transfer status stage

011 : Control write transfer data stage

100 : Control write transfer status stage

101 : Control write no data transfer status stage

110 : Control transfer sequence error

111 : Not assigned

Can be seen the stage of control transfer.

As to the stage shift of control transfer, refer to Fig.5 in the later part.

(Write operation is available when S/W control mode is set)

R

W/R

R

001000000

-00

-000000

16

Loading...

Loading...