MITSUBISHI 〈DIGITAL ASSP〉

MITSUBISHI 〈DIGITAL ASSP〉

STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER

STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER

DESCRIPTION

The M66238 is a LSI that incorporates a PLL synthesizer and

a sync clock generator in it. The PLL synthesizer covers the

range of 25MHz to 50MHz at the minimum steps of 3kHz.

The sync circuit outputs a clock and a one-shot pulse which

are synchronized with an external trigger signal. Setting a

dividing ratio allows acquisition of sync clock outputs within

the range of 0.78MHz to 25MHz.

FEATURES

• Sync clock output frequency range:1/1, 1/2, 1/4, 1/8, 1/16,

1/32 of 25 to 50MHz

• Sync accuracy (jitter): ±3ns

• Trigger input: Polarity selectable

• One-shot pulse output: Polarity and width selectable

• 5V power supply

APPLICATION

Pixel clock generator

M66238FP

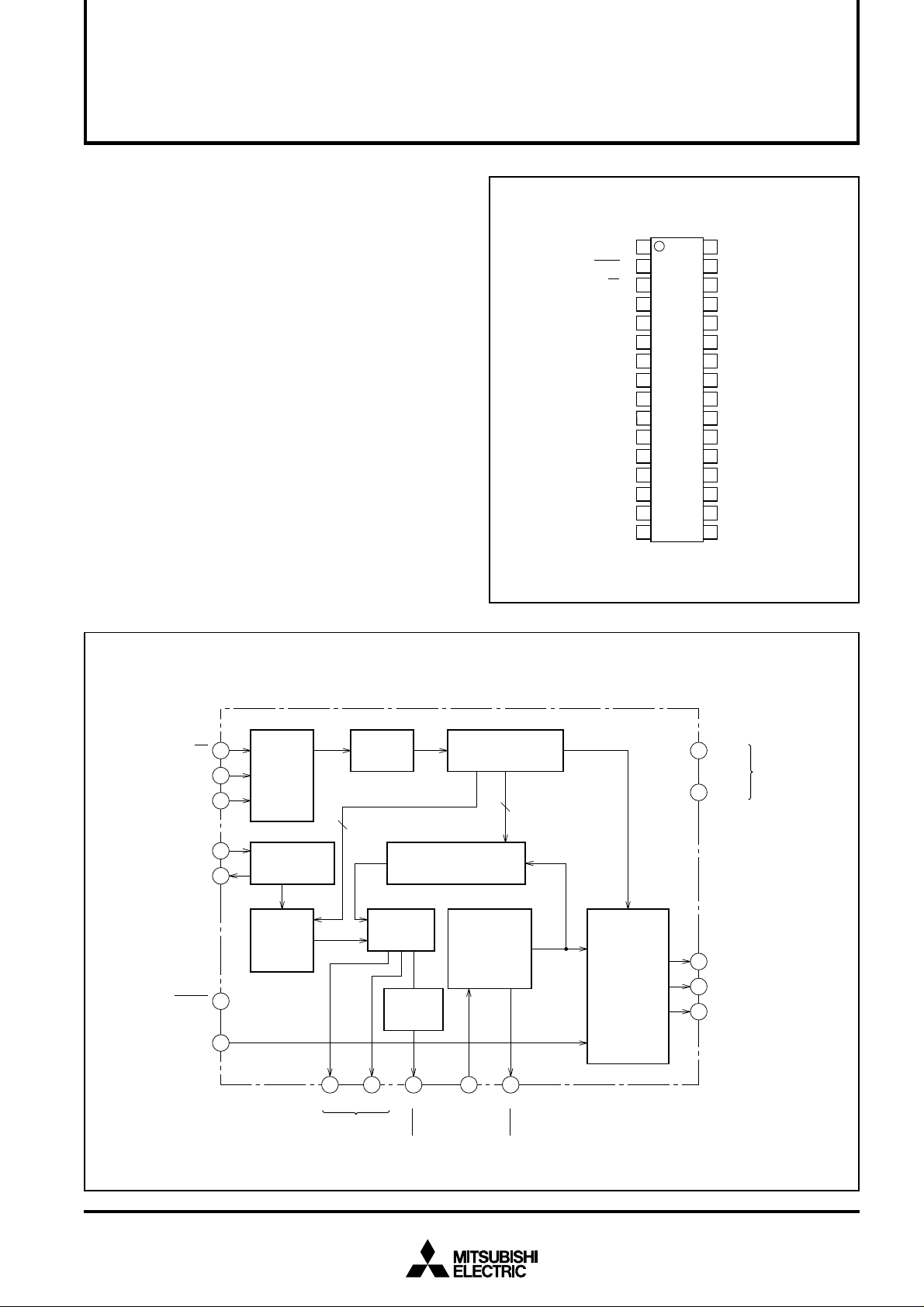

PIN CONFIGURATION (TOP VIEW)

DIGITAL GND PIN

RESET INPUT

CHIP SELECT INPU

SERIAL DATA INPUT

SERIAL CLOCK INPUT

CLOCK OUTPUT

CLOCK INPUT

DIGITAL GND PIN

DIGITAL POWER

SUPPLY PIN

TEST PIN

PLL OUTPUT

CLOCK OUTPUT

ONE-SHOT PULSE OUTPUT

SYNC OUTPUT POWER

SUPPLY PIN

SYNC OUTPUT GND PIN

DGND

1

→

RESET

→

T

CS

→

SIN

→

SCLK

←

XOUT

→

XIN

DGND

DVCC

→

TCKI

←

TCKO

←

CKO/PLLO

←

CKOB

←

PULSE

VCCO

GNDO

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

M66238FP

26

25

24

23

22

21

20

19

18

17

M66238FP

ANALOG GND PIN

AGND

ANALOG POWER

AVCC

SUPPLY PIN

ANALOG GND PIN

AGND

VCO LOAD OUTPUT

→ RV

ANALOG POWER

AVCC

SUPPLY PIN

ANALOG GND PIN

AGND

←

FILTER CONNECT PIN

CPIN

ANALOG GND PIN

AGND

→

CPOUT

FILTER CONNECT PIN

DGND

DIGITAL GND PIN

DIGITAL POWER

DVCC

SUPPLY PIN

→ UP

→ DOWN

←

TEST PIN

DIGITAL POWER

DVCC

SUPPLY PIN

DGND

DIGITAL GND PIN

TRIGGER INPUT

TR

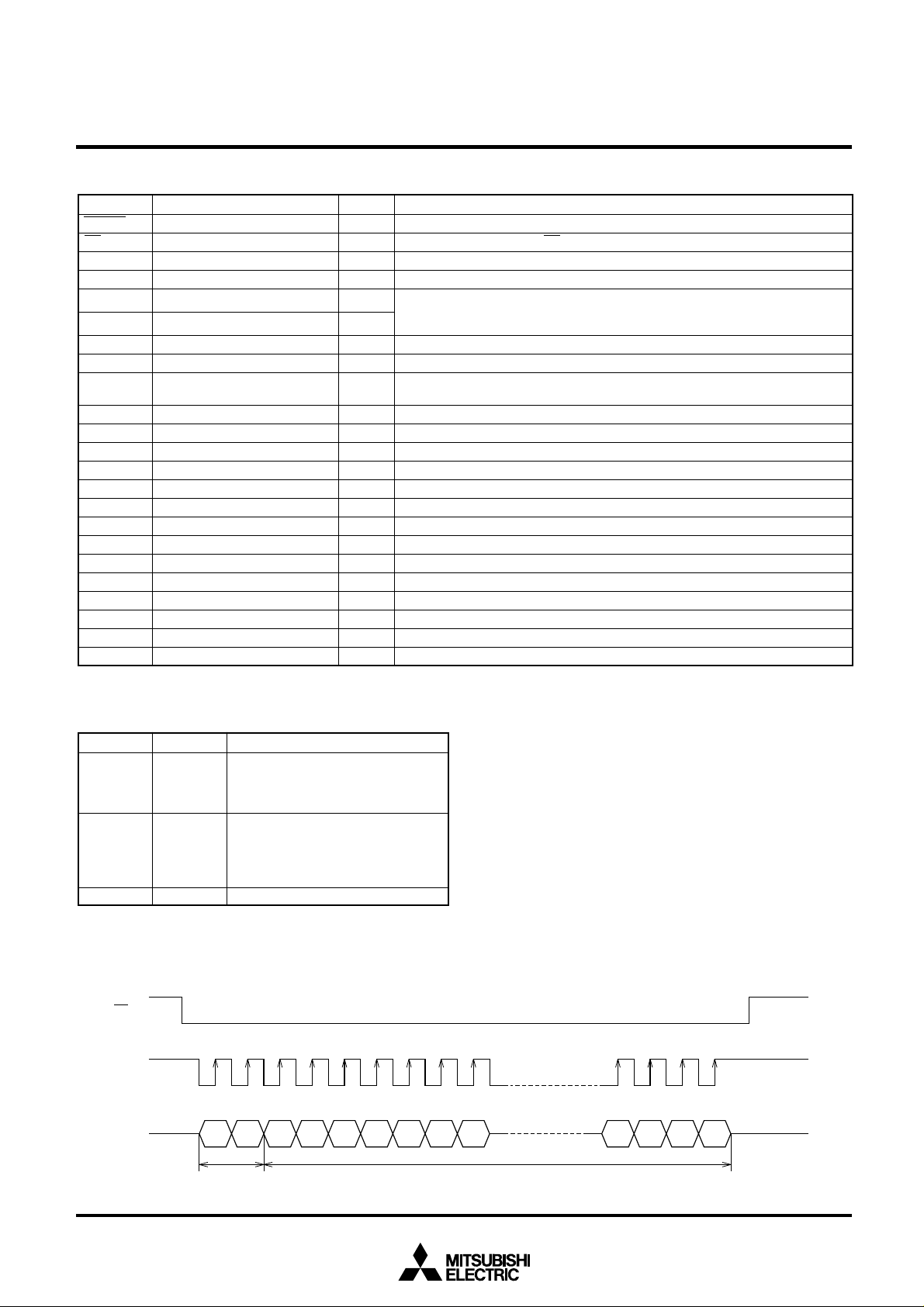

BLOCK DIAGRAM

CHIP SELECT INPUT

SERIAL DATA INPUT

SERIAL CLOCK INPUT

CLOCK INPUT

CLOCK OUTPUT

RESET INPUT

CS

SIN

SCLK

XIN

XOUT

RESET

3

4

5

7

6

2

SERIAL

WRITE

CONTROL

CIRCUIT

CRYSTAL

OSCILLATOR

CIRCUIT

fin

12-BIT

DIVIDER

COMMAND

REGISTER

12

PHASE

COMPARATOR

15-BIT COUNTER

CHARGE

PUMP

COMMAND CONTROL

CIRCUIT

15

VCO

25MHz ~ 50MHz

fvco

Outline 32P2W-A

SYNC/DIVIDER

CIRCUIT

SYNC CLOCK

(

GENERATOR

)

10

TCKI

11

TCKO

12

CKO/PLLO

13

CKOB

14

PULSE

TEST PIN

PLL OUTPUT

CLOCK OUTPUT

ONE-SHOT PULSE OUTPUT

TRIGGER INPUT

TR

17

21 20 24 26

UP DOWN CPOUT CPIN RV

TEST PIN

FILTER CONNECT PIN

FILTER CONNECT PIN

29

VCO LOAD OUTPUT

1

PIN DESCRIPTIONS

Pin name

RESET

CS

SIN

SCLK

XIN

XOUT

TR

CKOB

CKO/PLLO

PULSE

CPOUT

CPIN

RV

TCKI

TCKO

UP

DOWN

DVCC

DGND

VCCO

GNDO

AVCC

AGND

Reset input

Chip select input

Serial data input

Serial clock input

Clock input

Clock output

Trigger input

Clock output

PLL output

One-shot pulse output

Filter connect pin

Filter connect pin

VCO load output

Test pin

Test pin

Test pin

Test pin

Digital power supply pin

Digital GND pin

Sync output power supply pin

Sync output GND pin

Analog power supply pin

Analog GND pin

Name

MITSUBISHI 〈DIGITAL ASSP〉

M66238FP

STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER

I/O

Input

Input

Input

Input

Input

Output

Input

Output

Output

Output

Output

Input

Output

Input

Output

Output

Output

—

—

—

—

—

—

Initialize M66238 internal status.

Transfer serial data when CS=“L”.

Synchronize 32-bit serial data from MCU with SCK, and enter.

Enter a sync clock for writing 32-bit serial data.

Used by connecting crystal oscillator between XIN and XOUT. When using an

external clock signal, connect the clock oscillator to XIN pin and open XOUT pin.

Trigger input for clock sync.

Output an inverted CKO signal.

CKO outputs a clock synchronized with a trigger signal and PLLO outputs a PLL

oscillator clock as it is.

Output a one-shot pulse synchronized with a CKO signal.

Connect a low pass filter to charge pump output.

Low pass filter input pin.

Connect a load resistor for VCO circuit operation between RV and GND.

Shipping test pin. Connect to GND when use.

Shipping test pin. Keep open when use.

Shipping test pin. Keep open when use.

Shipping test pin. Keep open when use.

Digital power supply pin.

Digital GND pin.

Power supply pin for sync output.

GND pin for sync output.

Analog power supply pin.

Analog GND pin.

Function

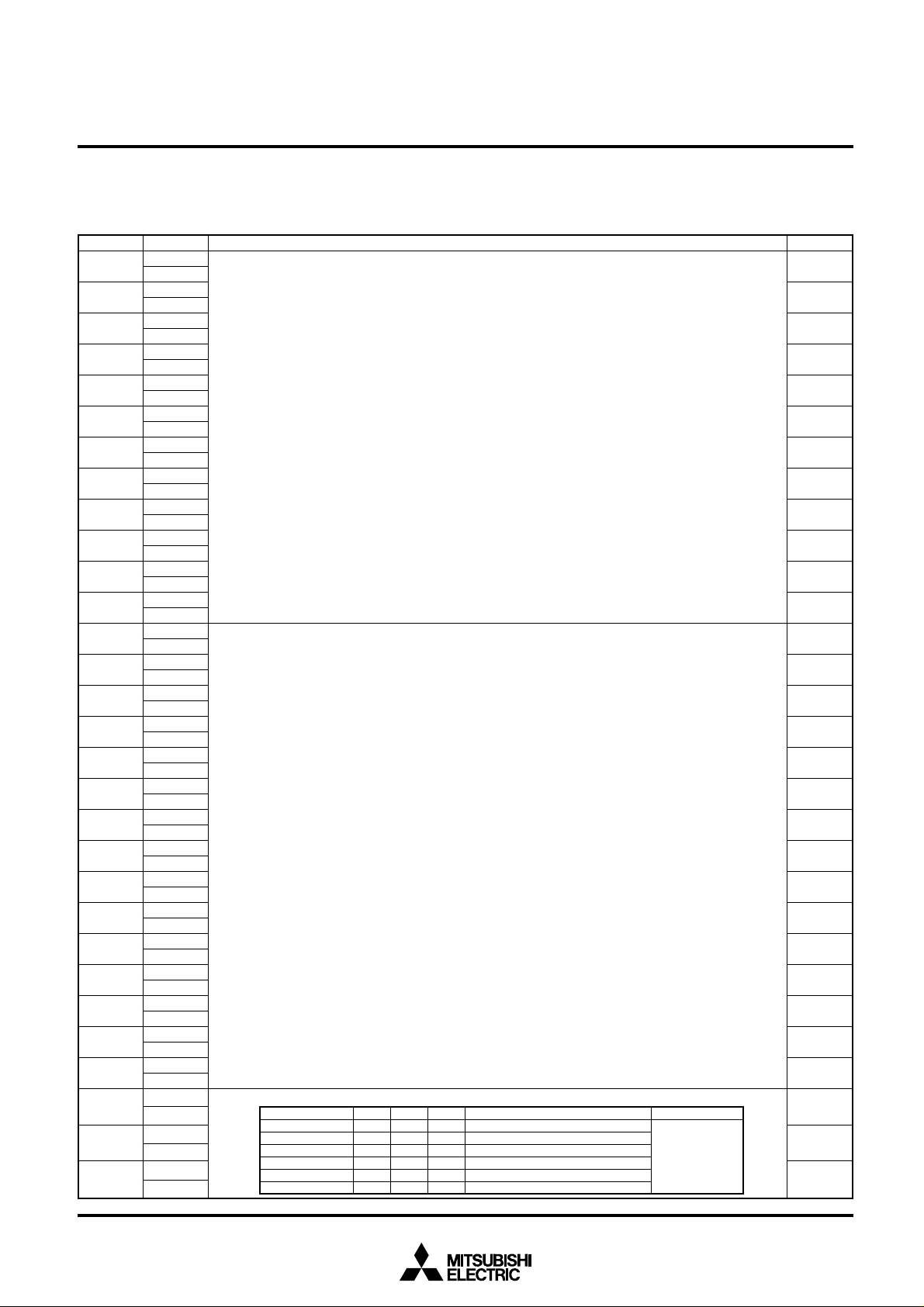

LIST OF REGISTER SETTING COMMANDS

A1

0

1

1

A0

Setting

Setting of CKO/PLLO dividing ratio,

0

0

1

PLL synthesizer 15-bit generation

dividing ratio and reference clock

generation 12-bit dividing ratio.

Setting of one-shot pulse polarity and

width, setting of trigger edge, HALT of

entire M66238, HALT of charge pump

and VCO, phase comparator output

UP/DOWN, CKO/PLLO switching.

Dummy trigger generation command

SERIAL DATA WRITE TIMING

CS

SCLK

SIN

A0 A1 D0 D1 D2 D3 D4 D5 D6 D26 D27 D28 D29

Address bit Data bit

2

MITSUBISHI 〈DIGITAL ASSP〉

M66238FP

STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER

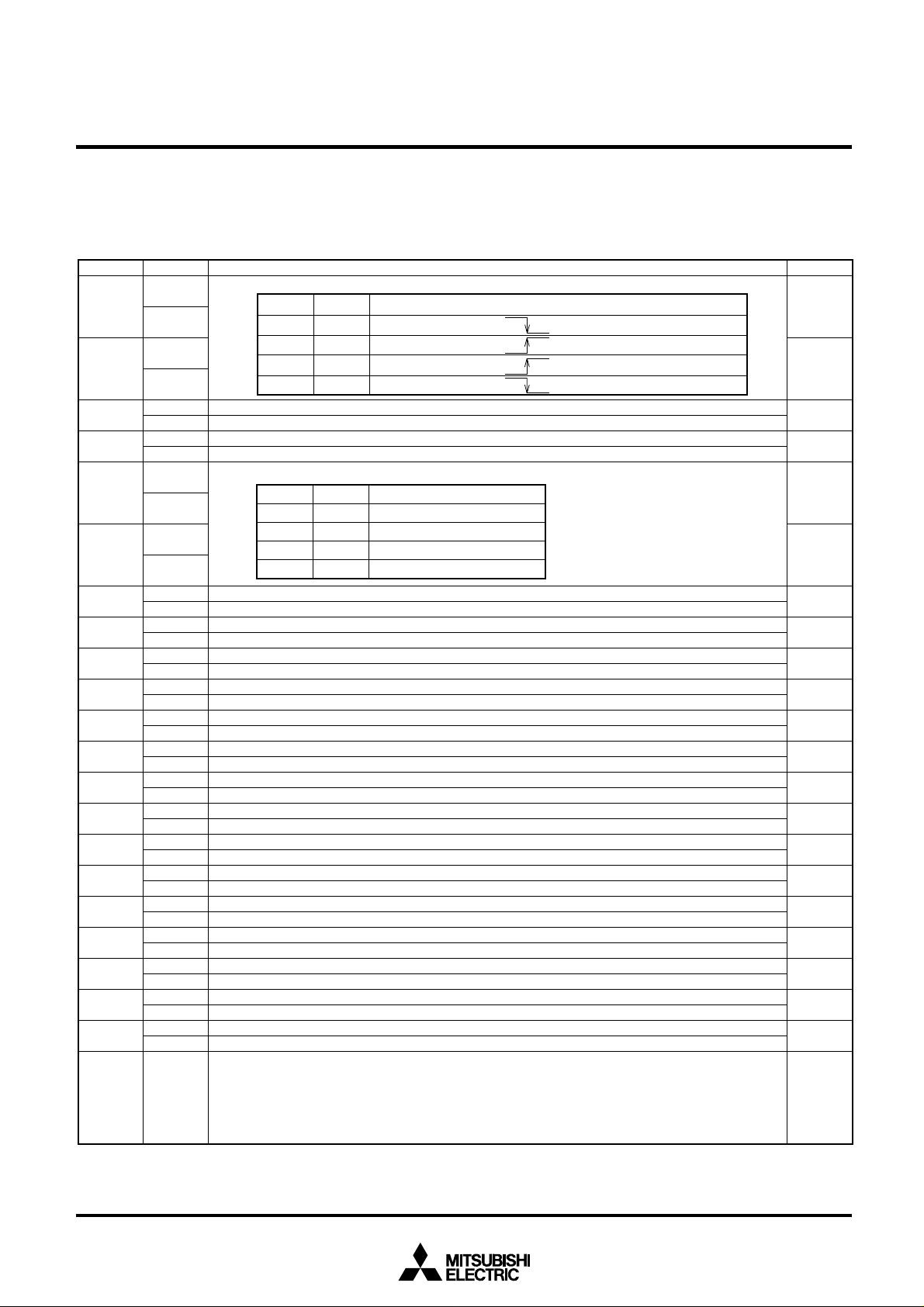

REGISTER CONFIGURATION

1. Clock frequency setting command

Reference clock generation 12-bit division ratio, PLL synthe-

Data bit

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

0

1

0

1

0

1

0

1

12-bit reference clock dividing ratio is set.

D11 and D0 correspond to MSB and LSB, respectively.

0

1

0

1

0

1

0

1

0

1

K: Reference clock dividing ratio

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

15-bit PLL synthesizer dividing ratio is set.

D26 and D12 correspond to MSB and LSB, respectively.

0

1

0

1

0

1

0

1

0

1

N: PLL synthesizer dividing ratio

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Setting of CKO/PLLO dividing ratios

Dividing ratio

1/1

1/2

1/4

1/8

1/16

1/32

D29

0

0

0

0

1

1

D28

0

0

1

1

0

0

sizer 15-bit division ratio and CKO/PLLO division ratio are set

at address (A1, A0) = (0, 0).

Description

11

K = ∑ (Dk × 2k)

k = 0

26

N = ∑ (Dn × 2

n = 12

D27

PLLO/CKO oscillator frequency

0

1

0

1

0

1

n–12

)

25MHz ~ 50MHz

12.5MHz ~ 25MHz

6.25MHz ~ 12.5MHz

3.125MHz ~ 6.25MHz

1.563MHz ~ 3.125MHz

0.781MHz ~ 1.563MHz

Remarks

Default

0

1

0

1

0

0

0

0

1

0

0

0

0

0

0

1

0

1

1

1

1

1

0

0

0

0

0

0

1

0

3

MITSUBISHI 〈DIGITAL ASSP〉

M66238FP

STANDARD CLOCK GENERATOR WITH PLL FREQUENCY SYNTHESIZER

2. Operating mode setting commands

Address (A1, A0) = (1, 0) allows setting of one-shot pulse

polarity and width, trigger edge, M66238 entire halt, charge

Data bit

Setting of trigger edge

D1

0

0

1

1

When trigger occurs: spike of sync clock is not eliminated.

When trigger occurs: spike of sync clock is eliminated (disabled when D1=1).

Polarity of one-shot pulse: Negative pulse

Polarity of one-shot pulse: Positive pulse

Setting of one-shot pulse width

D5

0

0

1

1

CKO/PLLO pin: CKO output

CKO/PLLO pin: PLLO output

Entire M66238: Operating state

Entire M66238: Halt state

VCO: Operating state

VCO: Halt state

Charge pump: ON

Charge pump: OFF

Low pass filter: Operating state

Low pass filter: Separated

Normal use: Not output to outside

Phase comparator UP/DOWN output enable

Normal use

VCO test circuit set

Normal use

Charge pump test circuit set

Normal use

15-bit counter test clock enable

Normal use

Sync clock generator test clock enable

Normal use

Sync clock generator test input enable

Normal use

12-bit counter test output enable

Normal use

15-bit counter test output enable

Normal use

Sync clock generator trigger test output enable

Normal use

Sync clock generator test output enable

D0

0

Synchronizes with TR CKO is stopped when TR=“H”.

1

Synchronizes with TR CKO is stopped when TR=“L”.

0

Synchronizes with TR CKO is output when TR=“H”.

1

Synchronizes with TR CKO is output when TR=“L”.

D4

0

CKO 2-cycle width

1

CKO 4-cycle width

0

CKO 8-cycle width

1

CKO 16-cycle width

Description

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

pump and VCO halt, phase comparator UP/DOWN output,

LPF cutoff, CKO/PLLO switching, VCO switching and charge

pump switching.

Description

Description

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

In normal use: “0” set

·············

D29

4

·············

0

Loading...

Loading...