MITSUBISHI 〈DIGITAL ASSP〉

MITSUBISHI 〈DIGITAL ASSP〉

DESCRIPTION

The M66220 is a mail box that incorporates a complete CMOS shared

memory cell of 256 × 8-bit configuration using high-performance silicon

gate CMOS process technology, and is equipped with two access

ports of A and B.

Access ports A and B are equipped with independent addresses CS,

WE and OE control pins and I/O pins to allow independent and

asynchronous read/write operations from/to shared memory

individually. This product also incorporates a port adjustment

arbitration function in address contention from both ports.

FEATURES

• Memory configuration of 256 × 8 bits

• High-speed access, address access time 40ns (typ.)

• Complete asynchronous accessibility from ports A and B

• Completely static operation

• Built-in port arbitration function

• Low power dissipation CMOS design

• 5V single power supply

• Not Ready output pin is provided (open drain output)

• TTL direct-coupled I/O

• 3-state output for I/O pins

APPLICATION

Inter-MPU data transfer memory, buffer memory for image processing

system.

M66220SP/FP

M66220SP/FP

256 × 8-BIT MAIL-BOX

256 × 8-BIT MAIL-BOX

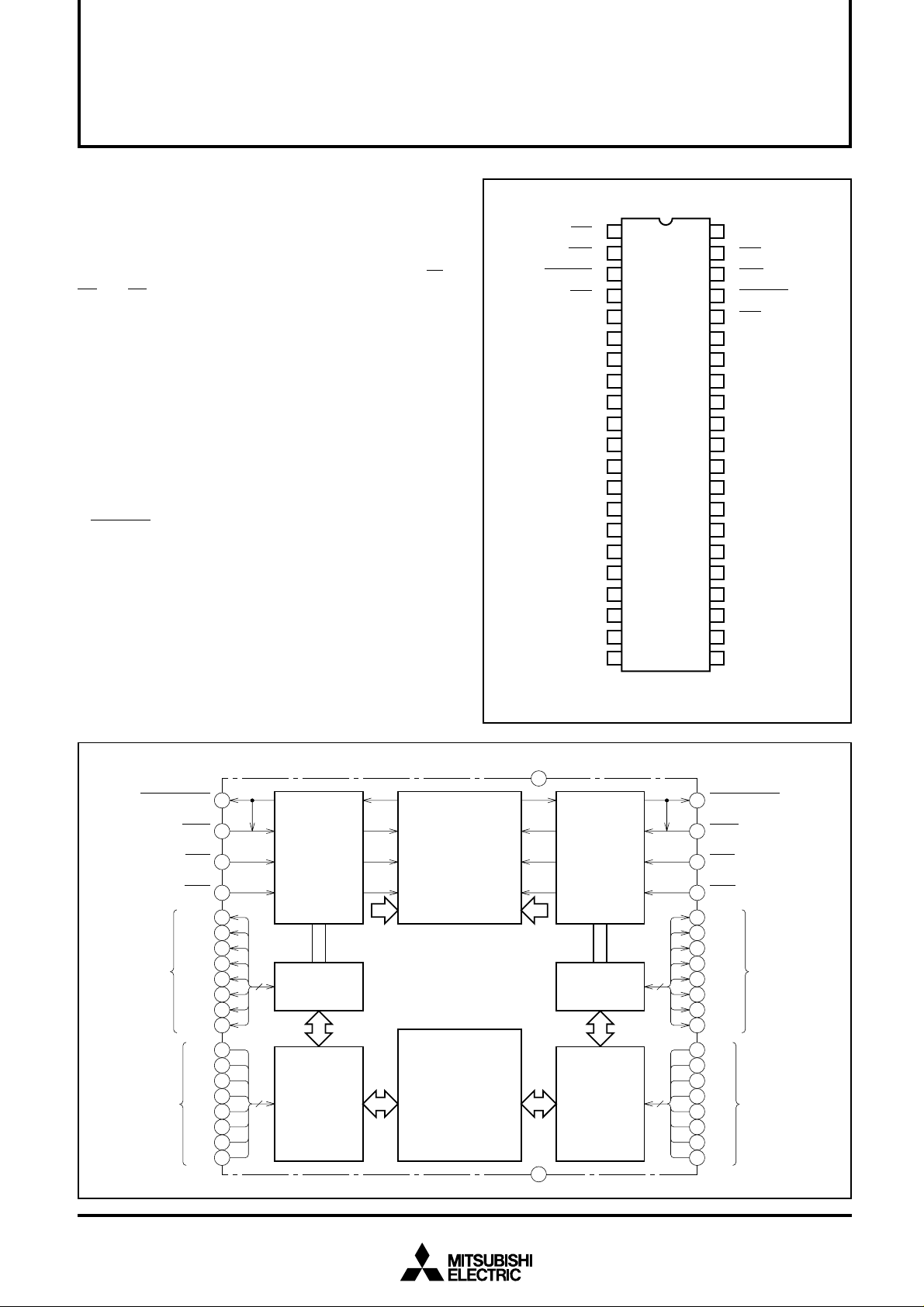

PIN CONFIGURATION (Top view)

CHIP SELECT

INPUT

WRITE ENABLE

INPUT

NOT READY

OUTPUT

OUTPUT ENABLE

INPUT

A PORT

ADDRESS

INPUT

A PORT

DATA I/O

Not Ready A

CSA

WEA

OEA

A

A

A

A

A

A

A

A

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

→

1

→

2

←

3

→

4

→

5

0

A

→

6

1

A

→

7

2

A

→

8

3

A

→

9

4

A

→

10

5

A

→

11

6

A

→

12

7

A

↔

0

A

13

↔

14

1

A

↔

15

2

A

↔

16

3

A

↔

17

4

A

↔

18

5

A

↔

19

6

A

↔

20

7

A

21

M66220SP/FP

42

←

41

←

40

→

39

←

38

←

37

←

36

←

35

←

34

←

33

←

32

←

31

←

30

↔

29

↔

28

↔

27

↔

26

↔

25

↔

24

↔

23

↔

22

V

CSB

WEB

Not Ready B

OEB

A

A

A

A

A

A

A

A

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

CC

CHIP SELECT

INPUT

WRITE ENABLE

INPUT

NOT READY

OUTPUT

OUTPUT ENABLE

INPUT

0

B

1

B

2

B

B PORT

3

B

ADDRESS

INPUT

4

B

5

B

6

B

7

B

7

B

6

B

5

B

4

B

B PORT

DATA I/O

3

B

2

B

1

B

0

B

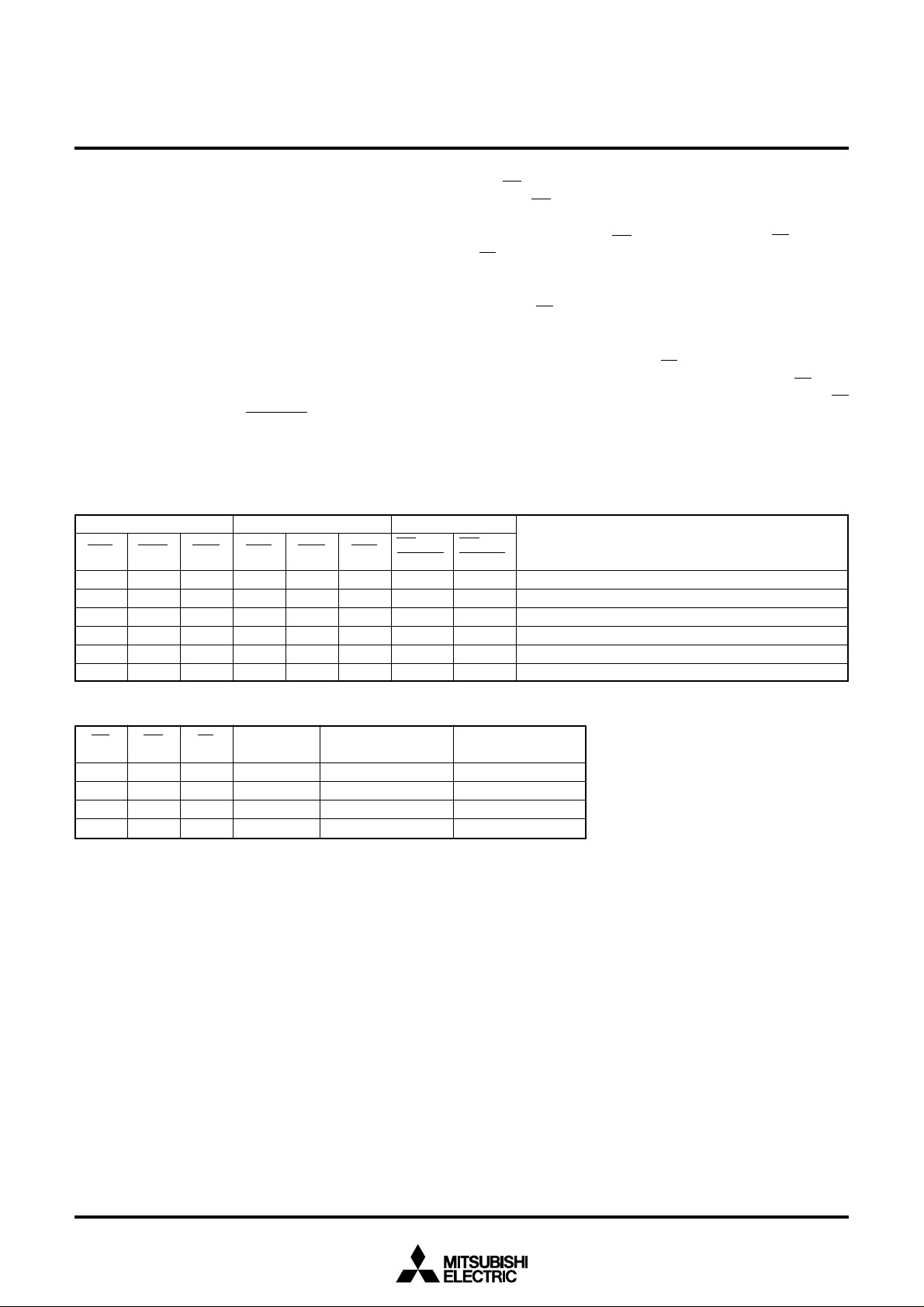

BLOCK DIAGRAM

NOT READY

OUTPUT

Not Ready A

WRITE

ENABLE INPUT

CHIP

SELECT INPUT

OUTPUT

ENABLE INPUT

A PORT DATA I/O

A PORT

ADDRESS INPUT

WEA

CSA

OEA

I/O0A

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

6

I/O

7

A0A

1

A

2

A

3

A

A

4

5

A

6

A

7

3

2

1

4

13

14

A

15

A

16

A

17

A

18

A

19I/O

A

20

A

5

6

A

7

A

8

A

9

A

10

A

11

A

12A

A

CONTROL

CIRCUIT

OEA

8

I/O BUFFER

8

ROW/COLUMN

DECODER

WEA

ARBITRATION

CIRCUIT

A

0

A

~

A

7

A

MEMORY ARRAY OF

256-WORD × 8-BIT

CONFIGURATION

CC

V

42

A

0

B

WEB

~

A

7

B

I/O BUFFER

ROW/COLUMN

21

GND

Outline

CONTROL

CIRCUIT

OEB

DECODER

42P4B

42P2R-A

39

40

41

38

22

23

24

25

8

26

27

28

29

37

36

35

8

34

33

32

31

30

Not Ready B

WRITE

WEB

ENABLE INPUT

CHIP

CSB

SELECT INPUT

OUTPUT

OEB

ENABLE INPUT

I/O0B

I/O

1

B

I/O

2

B

I/O

3

B

B PORT DATA I/O

I/O

4

B

I/O

5

B

I/O

6

B

I/O

7

B

A0B

1

B

A

2

B

A

B PORT

3

B

A

ADDRESS INPUT

A

4

B

5

B

A

6

B

A

7

B

A

NOT READY

OUTPUT

1

MITSUBISHI 〈DIGITAL ASSP〉

M66220SP/FP

256 × 8-BIT MAIL-BOX

FUNCTION

The M66220 is a mail box most suitable for inter-MPU data transfer

which is used in a multiport mode. Provision of two pairs of addresses

and data buses in its shared memory cell of 256 × 8 bit configuration

allows independent and asynchronous read/write operations from/to

two access ports of A and B individually.

This allows access to shared memory as simple RAM when viewing

from one MPU. The concurrent accessibility to shared memory from

two MPUs provides remarkable improvement of a multiport mode

processor system in throughput.

The arbitration function incorporated in the chip decides the first-in

port to assign a higher priority to the access from one MPU, even if

two MPUs contend for selection of the same address in shared

memory from ports A and B. A Not Ready signal “L” is output to the

last-in port and invalidates any access from the other MPU.

As a write operation to memory, one of addresses A0 to A7 is specified.

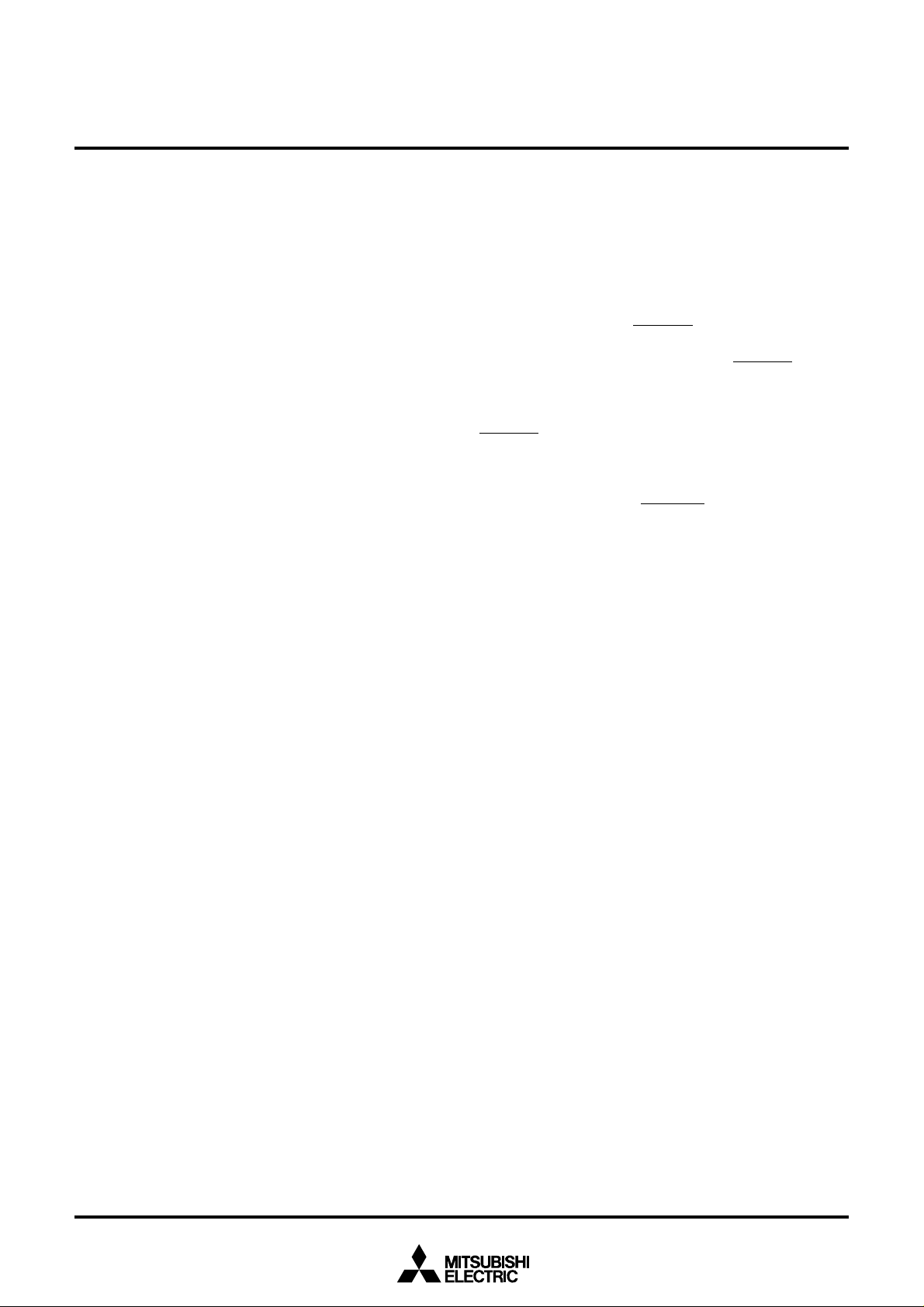

Table 1 Mode Settings of Ports (A0A ~ A7A ≠ A0B ~ A7B)

A port input B port input Flag

CSA

H

×

L

L

×

×

WEA

×

×

L

H

×

×

OEA

×

×

×

L

×

×

CSB

×

H

×

×

L

L

WEB

×

×

×

×

L

H

OEB

×

×

×

×

×

L

Not

Ready A

H

H

H

H

H

H

The CS signal is set to “L” to place one of I/O pins in the input mode.

Also, the WE signal is set to “L”. Data at the I/O pin is thus written

into memory.

As a read operation, the WE signal is set to “H”. Both CS signal and

OE signal are set to “L” to place one of I/O pins in the output mode.

One of addresses A0 to A7 is specified. Data at the specified address

is output to the I/O pin.

When the CS signal is set to “H”, the chip enters a non-select state

which inhibits a read and write operation. At this time, the output is

placed in the floating state (high impedance state), thus allowing OR

tie with another chip. When the OE signal is set to “H”, the output

enters the floating state. In the I/O bus mode, setting the OE signal

to “H” at a write time avoids contention of I/O bus data. When the CS

signal is set to Vcc, the output enters the full stand-by state to minimize

supply current (See Tables 1 and 2).

Not

Ready B

H

H

H

H

H

H

A port is set to the non-select mode.

B port is set to the non-select mode.

A port is set to the write mode for memory.

A port is set to the read mode for memory.

B port is set to the write mode for memory.

B port is set to the read mode for memory.

Operation

Table 2 Basic Functions of Ports

CS

H

Note 1: × indicates “L” or “H”. (Irrelevant)

WE

×

L

L

L

L

H

H

“H” = High level, “L” = Low level

OE

×

×

L

H

Mode

Non-select

Write

Read

I/O pin

High impedance

DIN

DOUT

High impedance

ICC

Stand-by

Operation

Operation

Operation

2

MITSUBISHI 〈DIGITAL ASSP〉

M66220SP/FP

256 × 8-BIT MAIL-BOX

FUNCTIONAL DESCRIPTION

Arbitration Function

The M66220 has asynchronous accessibility from two independent

ports to shared memory, thus remarkably improving the throughput

of the entire processor system used in the multiport mode. On the

other hand, this accessibility causes a problem of contending for

selecting the same address in shared memory during the addressing

from both ports.

If the same address is contentionally selected, the following four basic

operations are possible depending on an access mode set from both

ports:

(1) A port .......... Read B port .......... Read

(2) A port .......... Read B port .......... Write

(3) A port .......... Write B port .......... Read

(4) A port .......... Write B port .......... Write

In this case, when both ports are operating in the read mode as given

in (1), correct data is read to both ports and the contents of memory

are not destroyed. There is no special problem. If the other port is in

the read mode while one port is operating in the write mode as given

in (2) or (3), however, data is written correctly but the data read from

the other port in the read mode may change during the same cycle.

This comes into question. When both ports are operating in the write

mode as given in(4), reverse data is written into each port and the

contents of memory may become uncertain. Consequently, no result

will be guaranteed.

The M66220 incorporated an arbitration function circuit to solve such

problems when contentionally selecting an address from both ports.

The arbitration function decides which of A and B ports determines

an address first, and unconditionally assigns access priority to the

first-in port (At this time, the Not Ready signal holds “H”). As for the

last-in port operation, the function inhibits any write to that port from

MPU at the same time when “L” is output to the Not Ready output pin

at the port regardless of a read or write operation during the period of

address matching of both ports. If the address of the first-in port

changes after that and both ports do not have the same address, the

Not Ready output is reset to “H” and the access in the stopped state

is accepted from the last-in port. If the same address is selected by

an address input from both ports simultaneously, a decision by the

arbitration function on the chip also affords access only from one

port, and outputs “L” to the Not Ready output for the other port

invalidate any access from MPU. Tables 3 and 4 give the relationship

between the port arbitration function and port access.

3

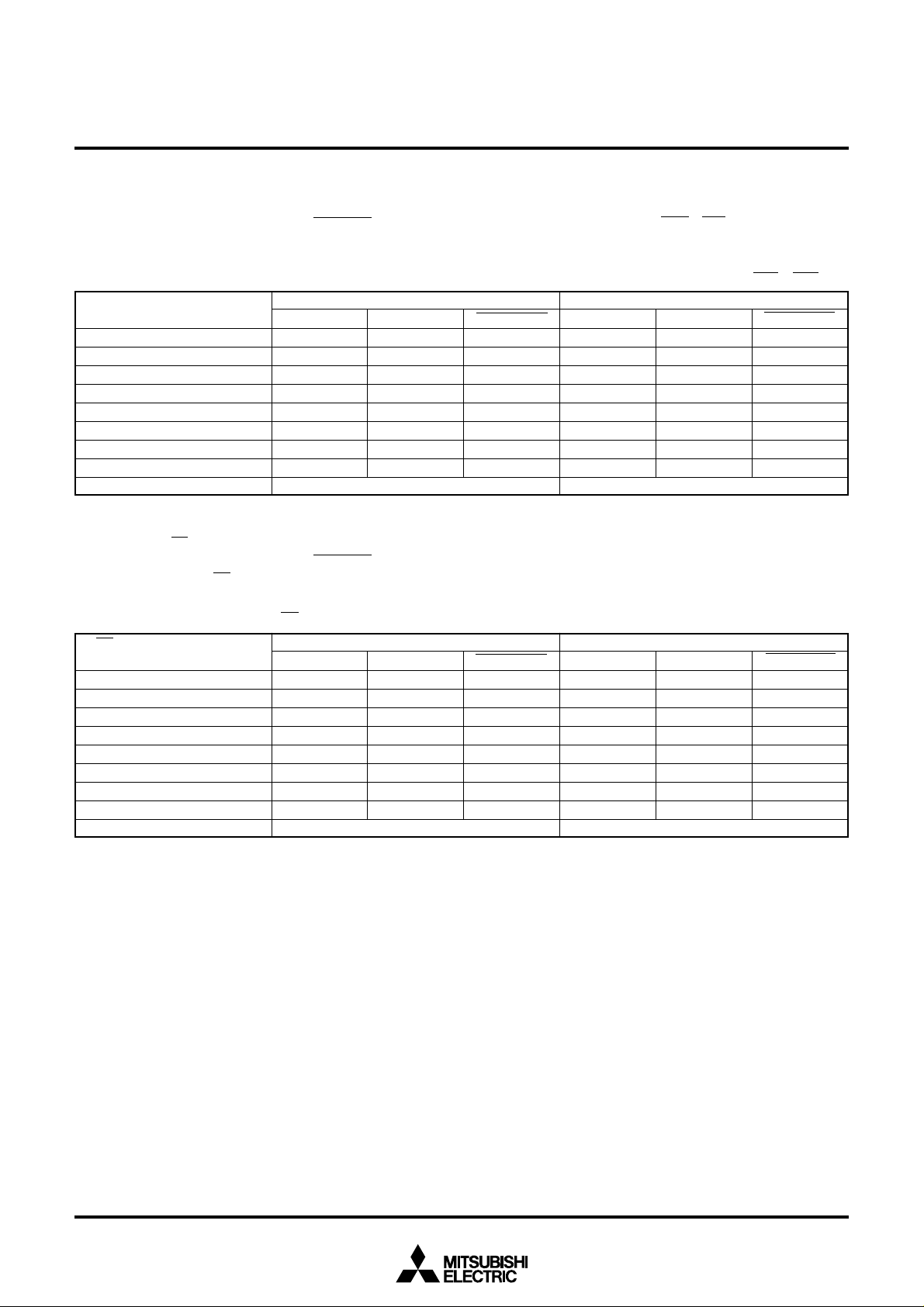

Arbitration Function and Port Access

Contention No.1 (Address control)

Table 3 gives the port access states and the Not Ready signal output

states if the same address is selected in shared memory by an address

MITSUBISHI 〈DIGITAL ASSP〉

M66220SP/FP

256 × 8-BIT MAIL-BOX

input set from A and B ports with CSA = CSB = “L”.

Table 3 Contention Processing by Address Input

Address setting when selecting

same address

First-in A port

First-in B port

First-in A port

First-in B port

First-in A port

First-in B port

First-in A port

First-in B port

Simultaneous A and B ports

Contention No.2 (CS control)

Table 4 gives the port access states and the Not Ready signal output

states when setting the CS inputs from A and B ports valid, and

Table 4 Contention Processing by CS Input

CS input set when selecting

same address

First-in A port

First-in B port

First-in A port

First-in B port

First-in A port

First-in B port

First-in A port

First-in B port

Simultaneous A and B ports

Note 2: “H” = High level, “L” = Low level

Mode setting

Read

Read

Read

Read

Write

Write

Write

Write

Mode setting

Read

Read

Read

Read

Write

Write

Write

Write

A port

Access

,

,

,

,

,

×

,

×

Arbitration Resolved

A port

Access

,

,

,

,

,

×

,

×

Arbitration Resolved

CSA = CSB = “L”

B port

Not Ready A

H

L

H

L

H

L

H

L

selecting the same address in shared memory with A0A to A7A=A0B

to A7B.

Not Ready A

H

L

H

L

H

L

H

L

Mode setting

Read

Read

Write

Write

Read

Read

Write

Write

Mode setting

Read

Read

Write

Write

Read

Read

Write

Write

Access

,

,

×

,

,

,

×

,

Arbitration Resolved

A0A ~ A7A = A0B ~ A7B

B port

Access

,

,

×

,

,

,

×

,

Arbitration Resolved

Not Ready B

L

H

L

H

L

H

L

H

Not Ready B

L

H

L

H

L

H

L

H

4

Loading...

Loading...