Mitsubishi M66014FP Datasheet

MITSUBISHI 〈DIGITAL ASSP〉

MITSUBISHI 〈DIGITAL ASSP〉

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

DESCRIPTION

M66014 Semiconductor Integrated Circuit is a serial bus controller. It converts 2-byte parallel data that arrives from microcomputer into serial and outputs it to serial bus. It also

converts serial data input from serial bus into parallel and outputs it to microcomputer.

The M66014 is used for the extension of microcomputer I/O

ports and two-way communication with peripheral equipment

connected with serial buses.

FEATURES

• Compatible with general-purpose 8-bit microprocessor busses

• TTL level input (one microcomputer side)

• Interrupt output

• Schmitt input (RESET, CS, SIN)

• Pin arrangement is fully compatible with M66011FP

• Low power dissipation

• Wide operating temperature range (Ta = –20 to 75˚C)

M66014FP

16-BIT SERIAL BUS CONTROLLER

16-BIT SERIAL BUS CONTROLLER

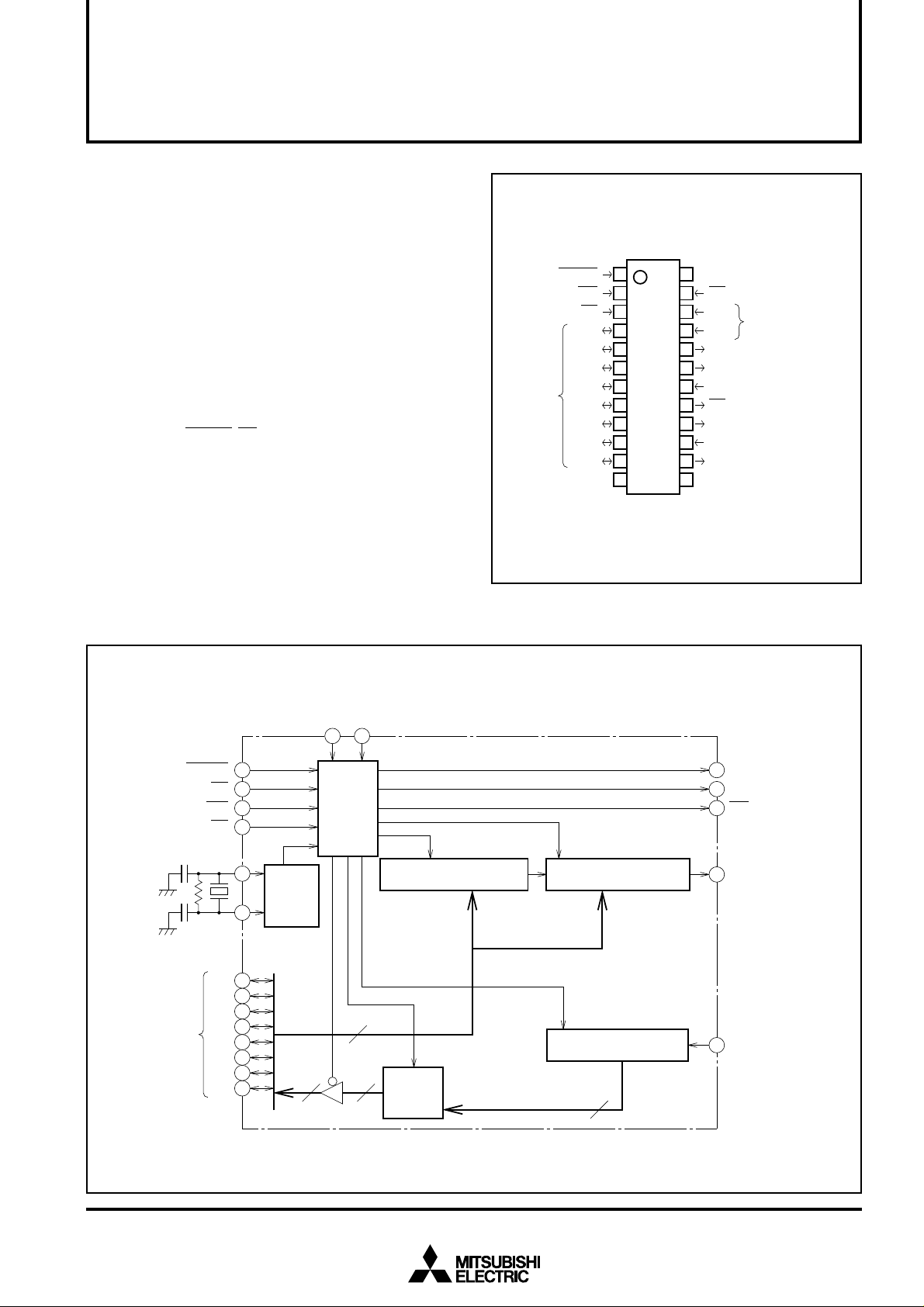

PIN CONFIGURATION (TOP VIEW)

RESET INPUT

WRITE INPUT

CHIP SELECT

DATA BUS

RESET

INPUT

WR

CS

D0

D1

D2

D3

D4

D5

D6

D7

GND

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

M66014FP

20

19

18

17

16

15

14

13

M66014FP

VCC

RD

READ INPUT

A0

ADDRESS INPUT

A1

SCLK

SHIFT CLOCK OUTPUT

SOUT

SERIAL DATA OUTPUT

SIN

SERIAL DATA INPUT

OE

OUTPUT ENABLE OUTPUT

INT

INTERRUPT OUTPUT

Xin

CLOCK INPUT

Xout

CLOCK OUTPUT

CC

V

APPLICATION

Microcomputer I/O port extension, etc.

BLOCK DIAGRAM

CS

WR

RD

Xout

Xin

1

3

2

23

15

14

Oscillation

circuit

RESET INPUT

CHIP SELECT INPUT

CLOCK INPUT

CLOCK OUTPUT

RESET

WRITE INPUT

READ INPUT

A0

21A122

Timing

control

circuit

Shift register for lower

byte serial output (8 bits)

SR

Outline 24P2N-B

CLK, LOADCLK, LOAD

Shift register for upper

byte serial output (8 bits)

L

SR

SHIFT CLOCK OUTPUT

20

SCLK

INTERRUPT OUTPUT

16

INT

17

OE

OUTPUT ENABLE OUTPUT

19

SOUT

SERIAL DATA OUTPUT

U

DATA BUS

D0

D1

D2

D3

D4

D5

D6

D7

10

11

4

5

6

7

8

9

X8

8

88

Read

register

CLK

Shift register for serial

input (16 bit)

8

18

SIN

SERIAL DATA INPUT

1

MITSUBISHI 〈DIGITAL ASSP〉

M66014FP

16-BIT SERIAL BUS CONTROLLER

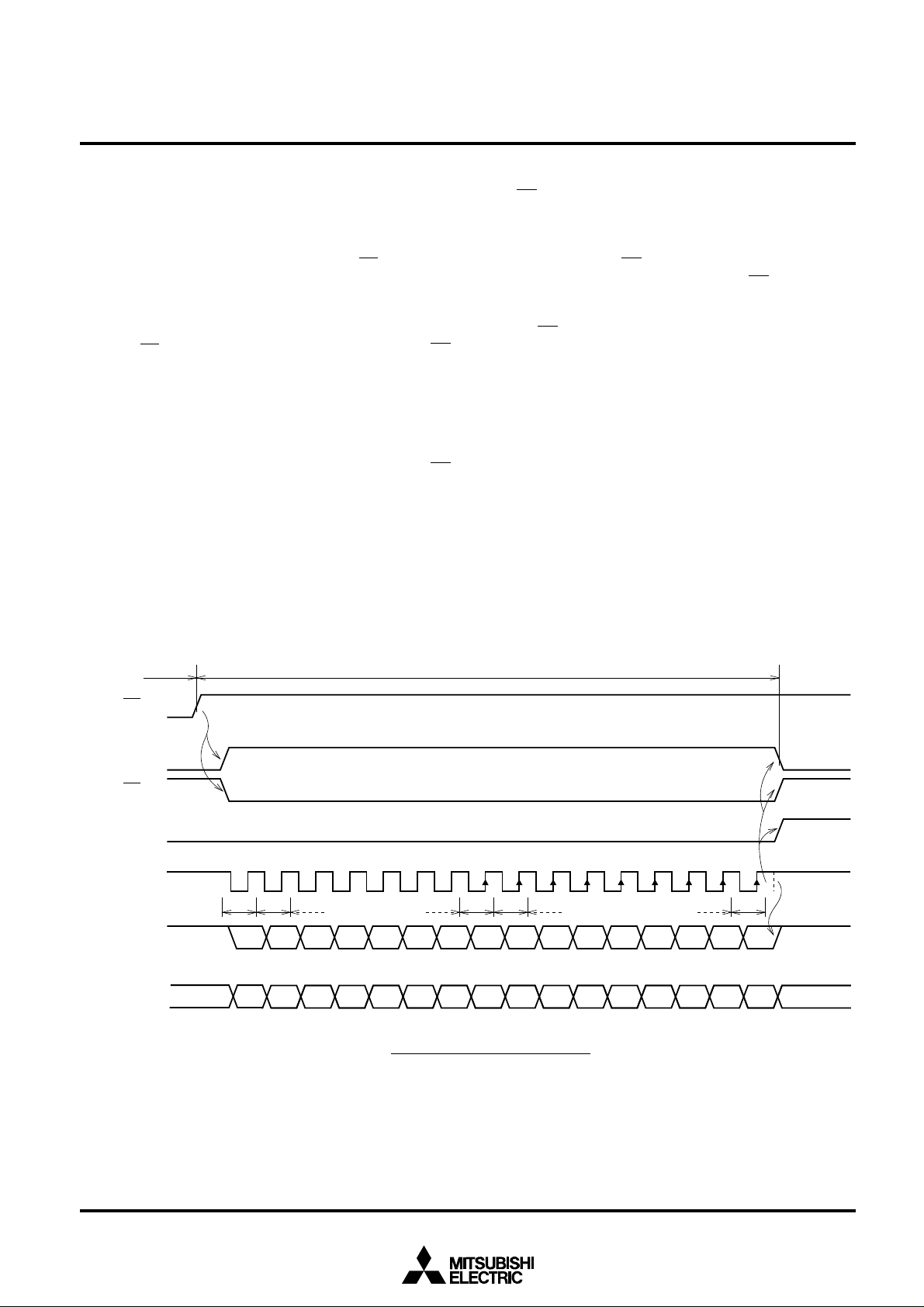

3. Serial data input/output operation

A cycle of 16-bit serial output data setting and serial data

communication starts with a write access given by microcomputer to transmission shift registers in M66014.

M66014 has two 8-bit shift registers, on for upper byte

(SR

U), the other for lower byte (SRL). If the CS status rises

from “L” to “H” after a write access is given to SR

data communication is started. SR

U 8-bit data and SRL 8-

bit data are output in series in this order. Output of each

data starts from its most significant bit.

At the CS rise edge, busy flag in M66014 is set, and OE

output shifts from “H” to “L”. Shift clock SCLK and serial

data SOUT are then output.

At SCLK fall edges, serial output shift register executes

shifting operation, and data on shift register is output in series from pin SOUT. Serial input data from pin SIN is taken

into input shift register at SCLK rise edges.

After the SCLK 16T rise edge, the status of SOUT and OE

shifts to “H” after one bit’s delay of SCLK, and busy flag is

reset. When interrupt output is being set to enable, INT

output is set.

L, serial

(Remarks)

(1) If CS rises after write operation is executed on SR

and not on SR

(2)When write operations executed on SR

U, SRU data is unstable.

L, M66014 be-

comes ready for start of serial communication and stands

by for detection of CS rise. However, if a read access is

given after data is written on SR

L while CS is maintained

on “L” level, this standby status is canceled. To resume serial communication in this case, rewrite data on SRL and

raise CS.

L only

SRL

write operation

CS

Busy flag

(in M66014)

OE

INT

SCLK

SOUT

SIN

Serial communication period

1T 2T 8T 9T 16T

D015D014D013D012D011D010D09D08D07D06D05D04D03D02D01D0

(D7U) (D0U) (D7L) (D0L)

DI

DI15DI14DI13DI12DI11DI10DI

Serial Communication Timing Chart

8DI7DI6DI5DI4DI3DI2DI1DI0

9

0

2

Loading...

Loading...