Mitsubishi M65827FP Datasheet

MITSUBISHI SOUND PROCESSORS

PRELIMINARY

Notice ; This is not a final specification.

some parametric limits are subject to change.

FEATURES

•Normal speed to 8 times speed playback

•Multi speed selector

•Clock doubler

•Error correction(C1:2 error correction,C2:4 error correction)

•Channel control circuit ( Bilingual / swap / (L+R)/2)

•Wide-band adjustment-free EFM-PLL

•CLV gain control

•Low power consumption and low radiation by 3.3V function of

internal circuit

APPLICATION

CD-ROM, CD-I, VIDEO-CD, etc.

10-TIMES SPEED CD-DSP

M65827FP

PACKAGE

Outline 42P2R

0.8mm Pitch 450mil SSOP

(8.4mm X 17.5mm X 2.0mm)

RECOMMENDED OPERATING CONDITIONS

Supply voltage range 3.3V±10% (internal logic,analog circuits,oscillation circuit)

5.0V±10% (I/O buffer)

Rated voltage range

3.3V (internal logic,analog circuit)

5.0V (I/O buffer )

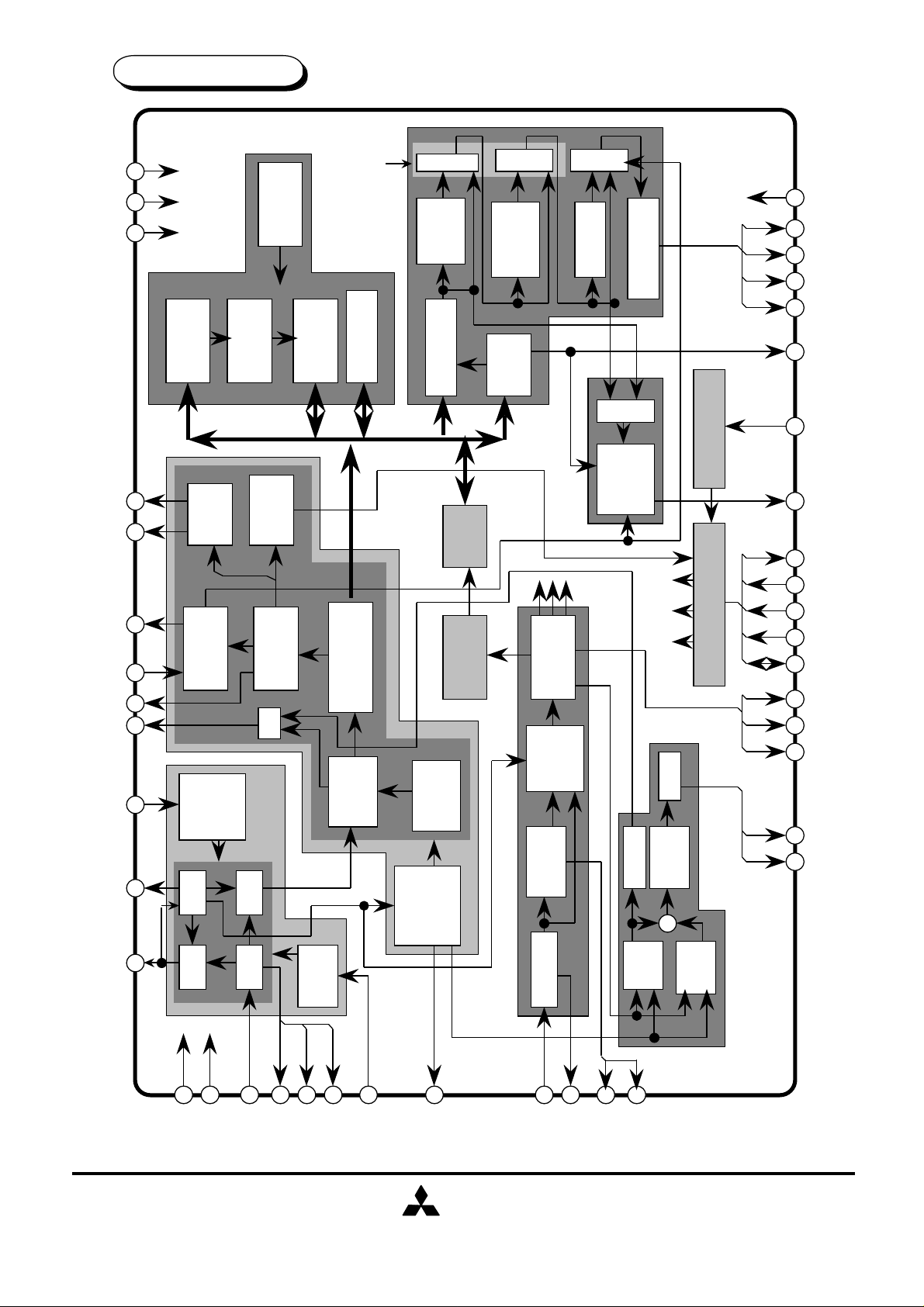

SYSTEM BLOCK DIAGRAM

M

Motor

Driver

Optical

Pick-up

RF-AMP

Pick-up

Servo

Auto

Adjustment

Subcode

Control

PLL

Slicer

PLL CLK OSC CLK

CLV

Digital Servo

MCU I/F

EFM

De-MOD

PLL CLK

Interpolation

18kSRAM

ECC

C1:2errors

C2:4errors

OSC CLK

SEL

Digital

Out

Channel

control

Timing Generator

(Speed Control)

DeEMP

M65827FP

S

E

L

Subcode

Digital Out

DATAOUT

System Control Microprocessor

MITSUBISHI

( / 52 )

1

ELECTRIC

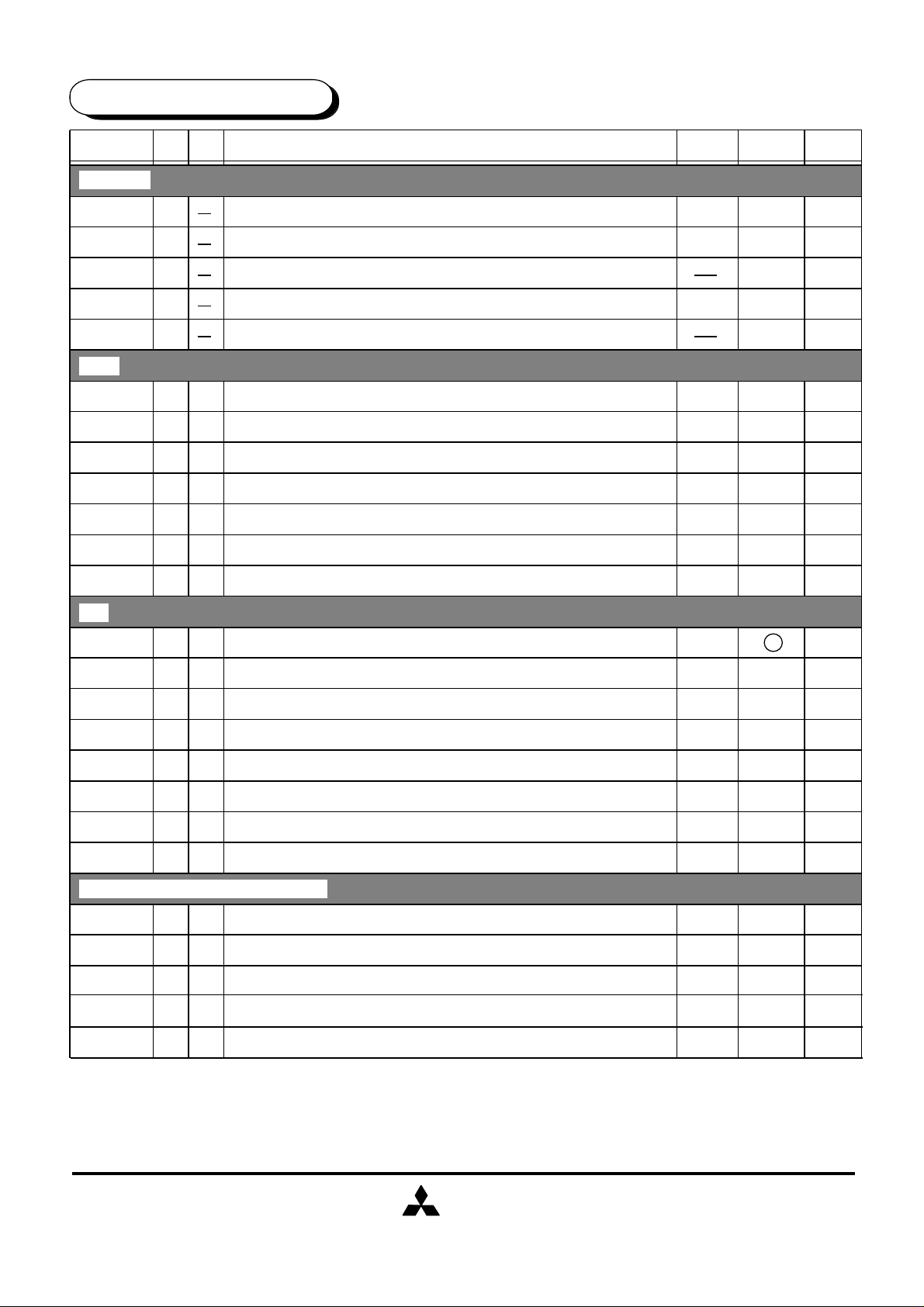

BUILT IN FUNCTIONS

DescriptionBlock name

Memory

PLL

EFM demodulation

Subcode control

Error correction

Interpolation

DAC interface

•18 Kbit SRAM

•±8 frames jitter margin

•Adjustment-free EFM-PLL

•Wide-band lock range(1•8 times)

•HF data slicer

•EFM demodulator

•Frame synchronization detection / protection / interpolation

•Frame synchronization monitor

•Subcode Q register

•CRC checker

•Subcode synchronous pattern detector (S0 and S1)

•Emphasis flag detector and digital de-emphasis filter

•Serial interface of subcode P~W (EIAJ CP-2401)

•C1: 2 error correction, C2: 4 error correction

(C1: 2 error correction, C2: 2 error correction selectable)

•Unscramble / De-interleave

•Error monitor

•Average and pre-hold interpolation (for CD-DA mode )

•Interpolate prohibition (for CD-ROM mode )

•Mute control

•Bilingual / swap / (L+R)/2 output

•Lch / Rch independent attenuation control (256 steps)

•Separate data output for CD-DA (DADT) and CD-ROM(ROMDT)

Digital output

Digital CLV servo

Oscillation circuit

MCU interface

•Based on EIAJ-1201

•C bit oscillation accuracy control

•C bit source number control

•PWM output

•Low disc rotation detector

•kick pulse control (256 steps)

•Automatic brake control

•CLV gain control

•Master clock selector (Playback speed control)

•Clock doubler

•VCO clock selector

•CLV servo control / mute control / attenuating level control

•Configuration control

•Attenuator control

•Channel control

•Play back speed control

•Analog switch control

•Error monitor control

•Track counter control

•Interrupt mask

•Kick timer control

•Digital audio interface C bit control

•Reset / sleep / clock disable control

•Subcode Q interface

MITSUBISHI

ELECTRIC

( / 52 )

2

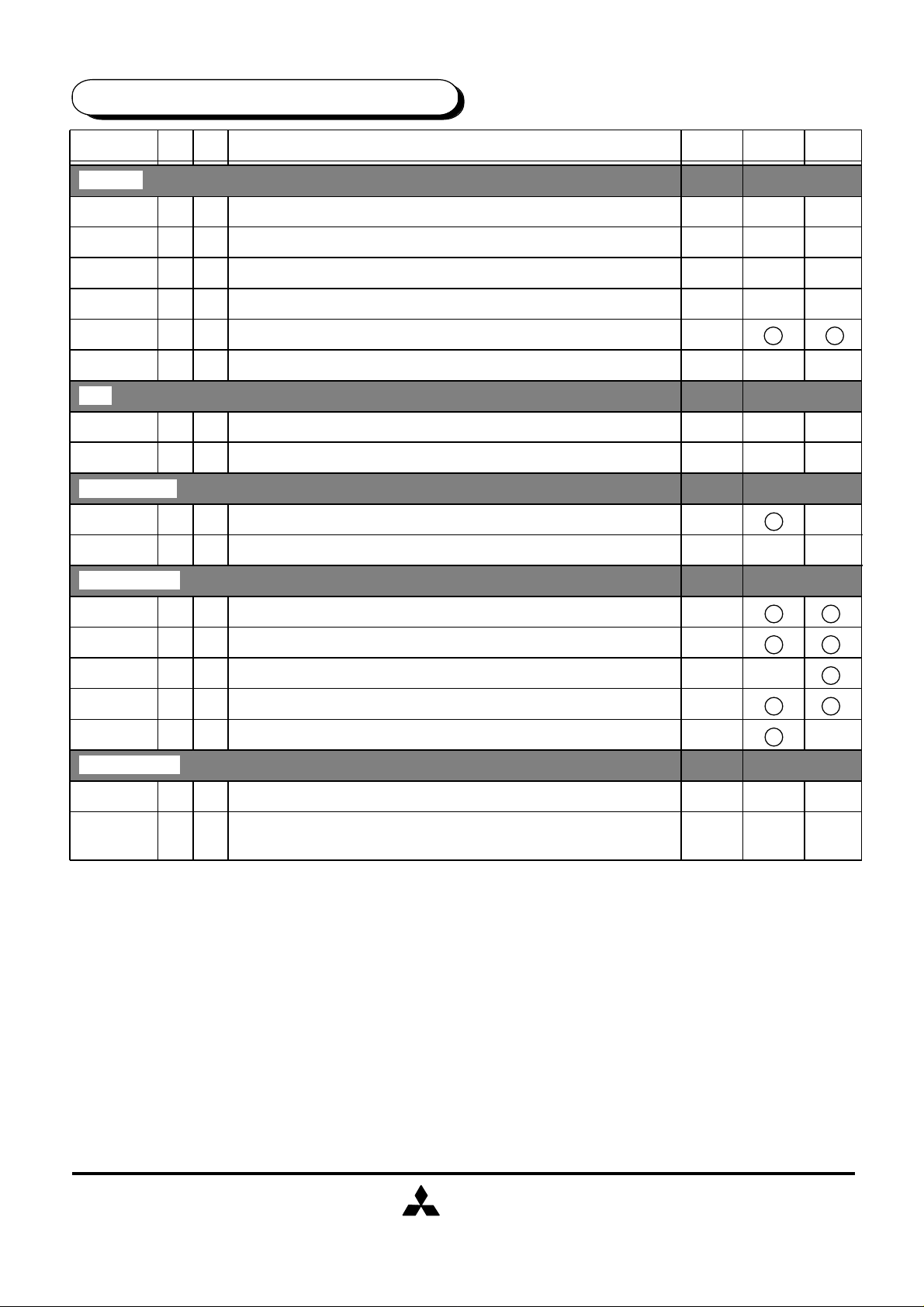

PIN DESCRIPTION TABLE

Name I/O Description Schmitt Pull-Up

VDD•VSS

DVDD5 Digital power supply (5V power supply for I/O buffer)

DVDD3 Digital power supply (3.3V power supply for internal circuit)

DVSS Digital ground

AVDD Analog power supply (3.3V power supply for analog circuit)

AVSS Analog ground

Clock

XI I Oscillator input

XO O Oscillator output

C423 O

S846 Crystal / PLL system clock

S423 O

DXLPF

DXRC

No.

1

2

42

14

21

41

40

38

34

35

3

12

O

I/O

O

Crystal half clock

Crystal / PLL half clock

Clock doubler loop filter connect pin

Clock doubler frequency gain control pin

Supply

DVDD5

DVDD3

AVDD

DVDD3

DVDD3

DVDD5

DVDD5

DVDD5

DVDD3

DVDD3

PLL

11

13

15

16

17

18

19

20

28

29

30

I

HF defect signal input

I

Current reference

O

EFM-PLL frequency gain control pin

O

O

O26

DVDD5

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

DVDD5

DVDD5

DVDD5

DVDD5

HFD

IREF

LPF I/O EFM-PLL loop filter connect pin

RC

HF I HF input

HPF1 OHPF1 O High Pass Filter 1

HPF2 O High Pass Filter 2

TLC O Data slicer charge pump output

Data output • Digital Audio Interface

DADT O Audio data output

ROMDT O CD-ROM data output31 DVDD5

LRCK LR clock

DSCK Data shift clock

DOTX Digital audio interface output

MITSUBISHI

ELECTRIC

( / 52 )

3

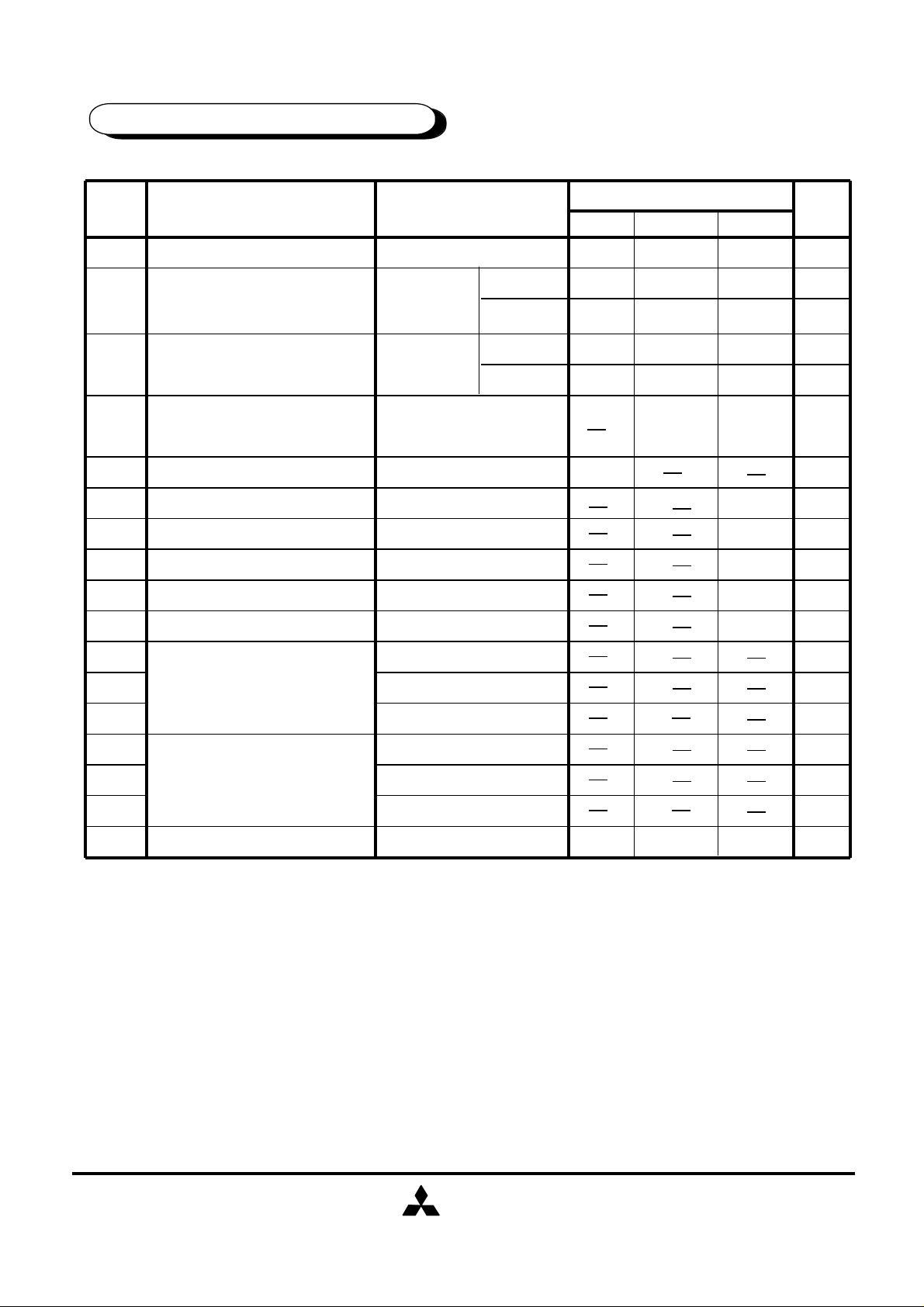

PIN DESCRIPTION TABLE (CONTINUED)

Name I/O

Subcode

SBQS O Subcode Q interrupt signal

SCAND Subcode sync. signal output (S0 and S1)O

SBCO Subcode data serial outputO

EFFK PLL frame clock outputO

SCCK Subcode data shift clock

CRCF CRC flag outputO

CLV

PWM1 Spindle motor PWM output (-)

PWM2 Spindle motor PWM output (+)

Track counter

TRIN Track cross signal input

INT O Interrupting signal output

MCU interface

No.

22

23

24

25

27

33

32

36

37

5

I

O

O

I

Description

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

SchmittSupply

Pull-Up

MCK MCU shift clock input

R/W MCU data read / write control

MSD I/O MCU data input / ouput

MLA I

ALCR Reset input

Monitor output

EST

LOCK/DRD

10

39

I

6

7

I

8

9

4

MCU latch clock input

I

O

C1/C2 error flag output

O

Lock monitor output / Low disc rotation detect signal output /

Frame synchronization status (SYCLK)

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

MITSUBISHI

ELECTRIC

( / 52 )

4

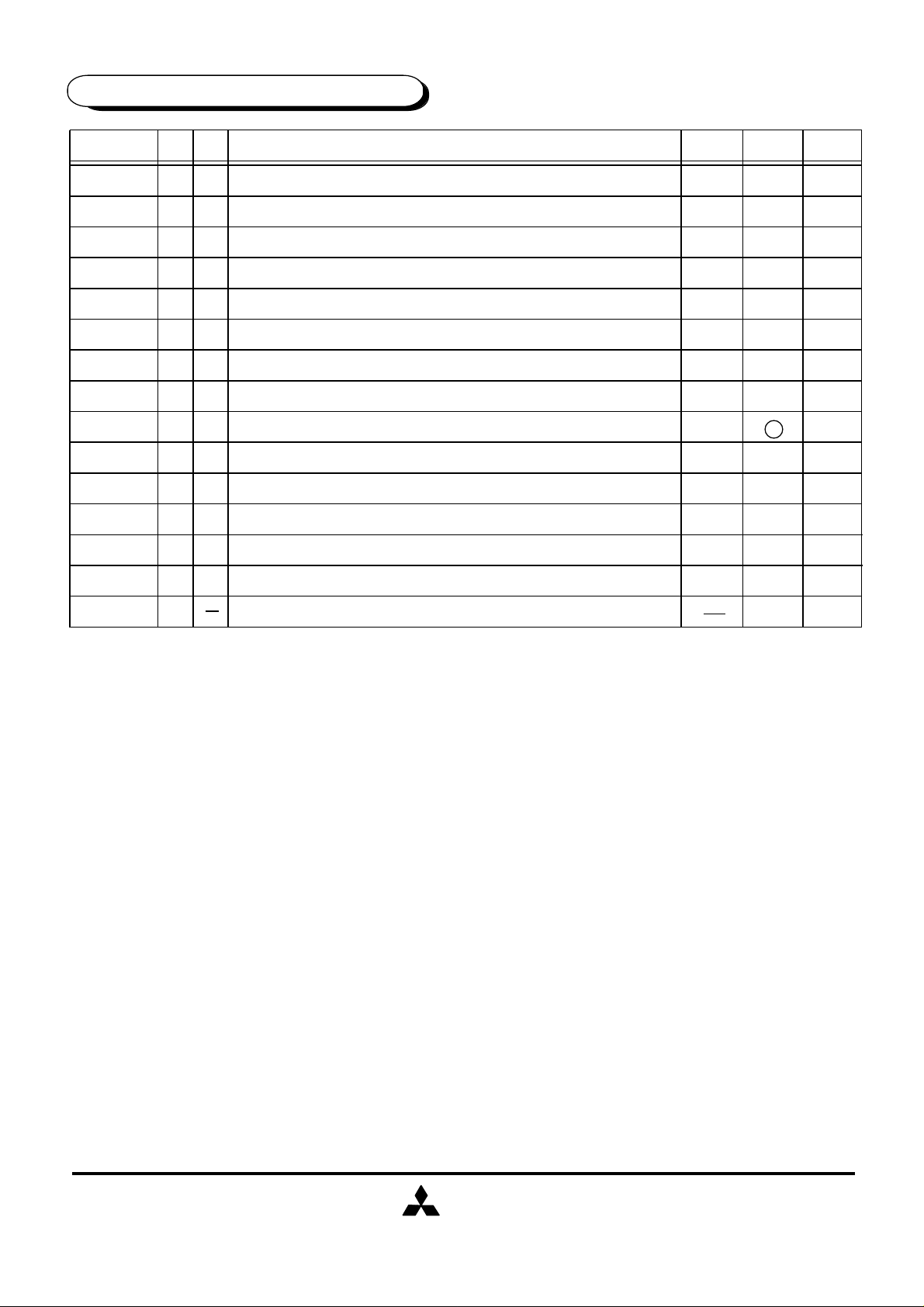

NUMERICAL PIN LIST

Name I/O Description Schmitt Pull-Up

DVDD5 Digital power supply (5V power supply for I/O buffer)

DVDD3 Digital power supply (3.3V power supply for internal circuits)

DXLPF

LOCK/DRD

SBQS O Subcode interrupt signal output

MCK MCU shift clock input

R/W MCU data read / write control

MSD I/O MCU data input / output

MLA I

ALCR Reset input

HFD

DXRC

IREF

AVDD Analog power supply (3.3V power supply for analog circuits)

No.

1

2

3

5

6

7

8

9

10

11

12

13

14

I/O

Clock doubler loop filter connect pin

O4

Lock monitor output / Low disc rotation detect signal output /

Frame synchronization status(SYCLK)

I

I

MCU latch clock input

I

I

HF defect signal input

Clock doubler frequency gain control pin

O

I

Current reference

Supply

DVDD5

DVDD3

DVDD3

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD3

AVDD

AVDD

LPF I/O

RC

HF I HF input

HPF1 OHPF1 O High Pass Filter 1

HPF2 O High Pass Filter 2

TLC O Data slice charge pump output

AVSS Analog ground

SCAND Subcode syncronization status (S0 and S1)O

SBCO Subcode data serial outputO

EFFK PLL frame clock outputO

SCCK Subcode readout clock

DOTX Digital output

CRCF CRC flag outputO

15

16

17

18

19

20

21

22

23

24

25

27

EFM-PLL loop filter connect pin

EFM-PLL frequency gain control pin

O

I

O26

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

MITSUBISHI

ELECTRIC

( / 52 )

5

NUMERICAL PIN LIST (CONTINUED)

Name I/O Description Schmitt Pull-Up

DADT O Audio data output

LRCK LR clock

DSCK Data shift clock

ROMDT

PWM2 Spindle motor PWM output (+signal)

PWM1 Spindle motor PWM output (-signal)

S846 Crystal / PLL system clock

S423 OOCrystal / PLL half clock

TRIN Track cross signal input

INT O Interrupt signal output

C423

EST

XO O Oscillator output

XI I Oscillator input

No.

28

29

30

31

33

34

35

37

38

40

41

O

O

CD-ROM data output

O

O32

O

I36

O

Crystal half clock

O

C2/C1 error output39

Supply

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD5

DVDD3

DVDD3

DVSS Digital ground

42

MITSUBISHI

ELECTRIC

( / 52 )

6

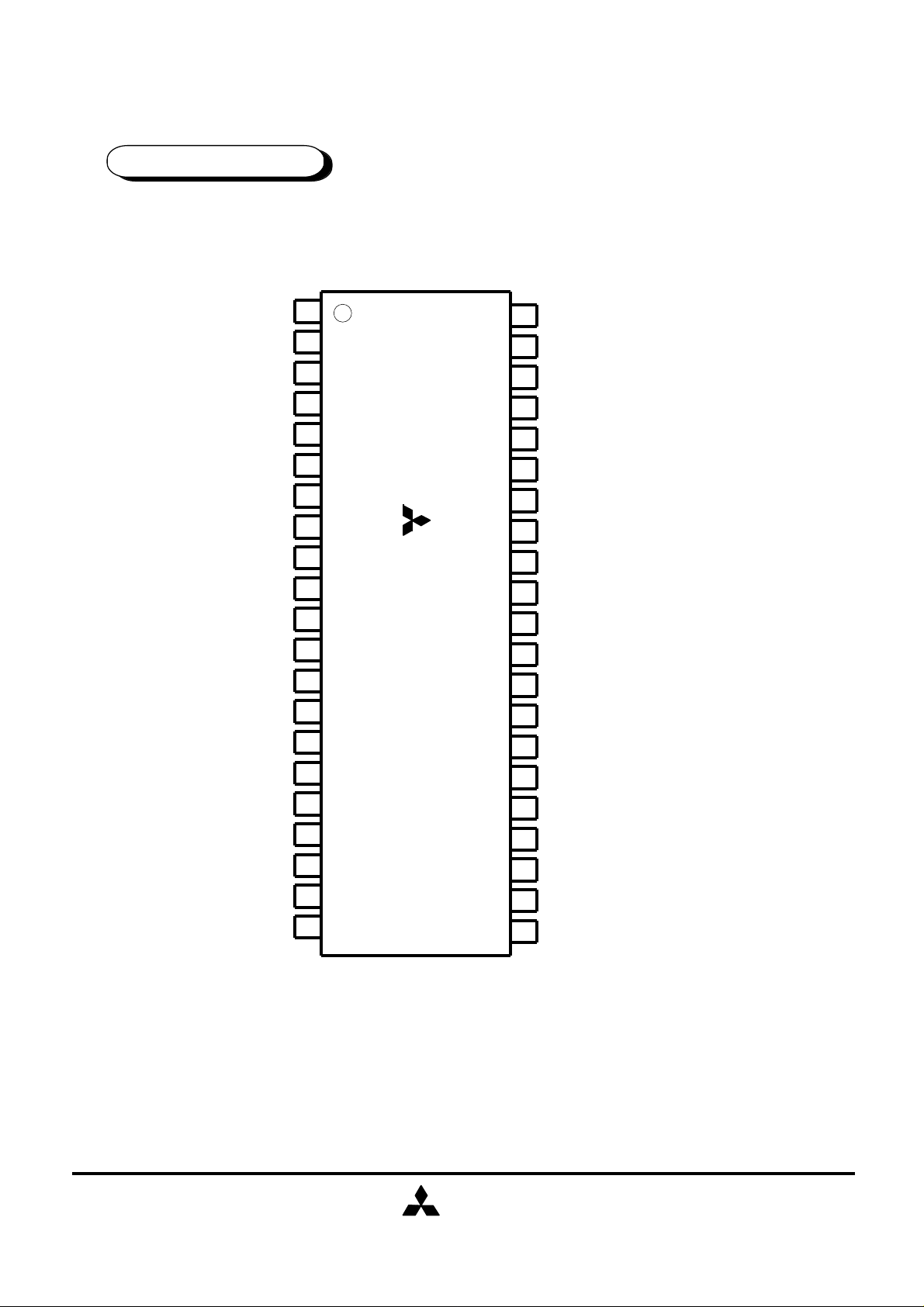

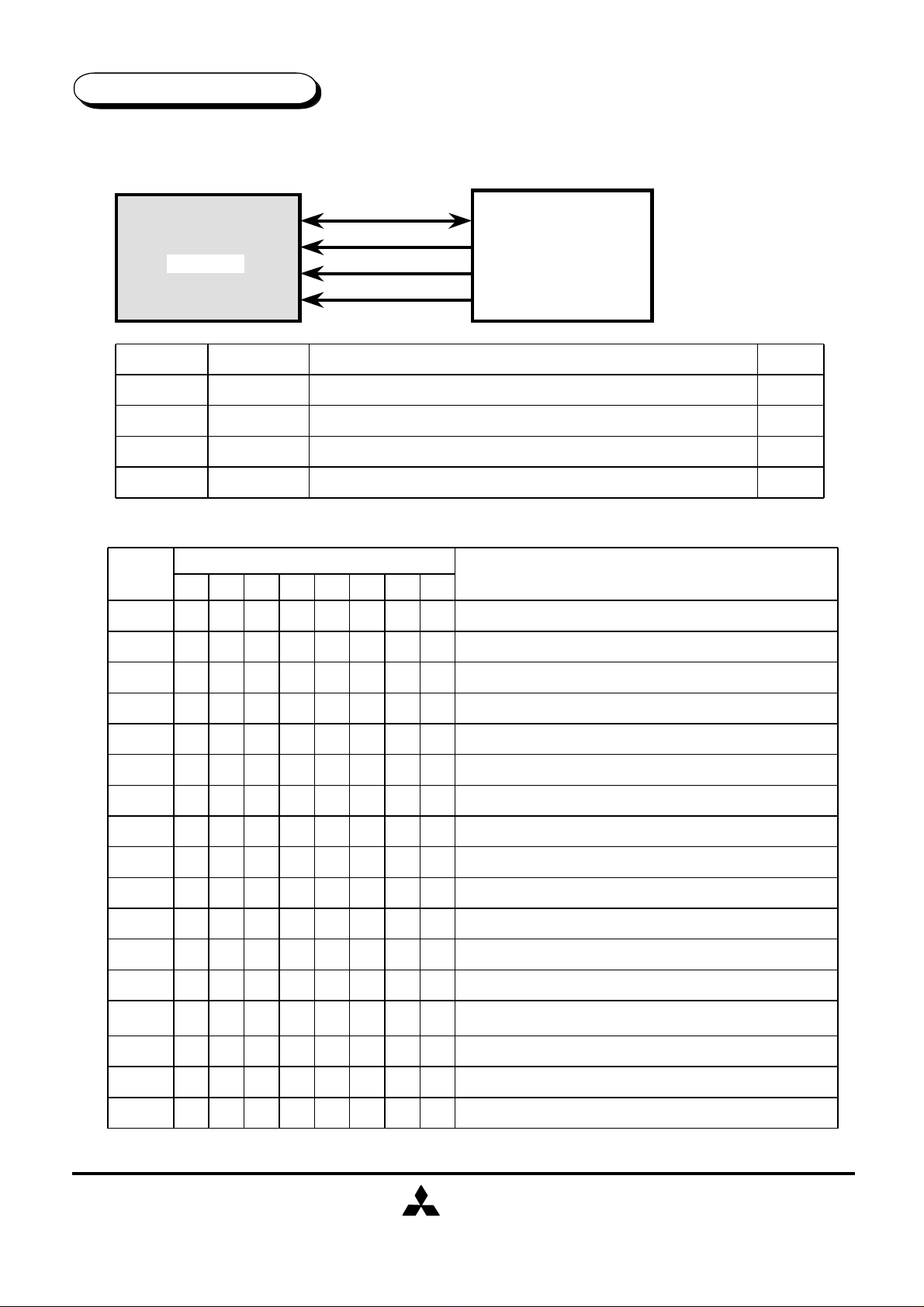

PIN CONFIGURATION

DVDD5

DVDD3

DXLPF

LOCK/DRD

SBQS

MCK

R/W

MSD

MLA

ALCR

HFD

DXRC

IREF

AVDD

LPF

RC

HF

HPF1

HPF2

TLC

AVSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

M65827FP

35

34

33

32

31

30

29

28

27

26

25

24

23

22

DVSS

XI

XO

EST

C423

INT

TRIN

S423

S846

PWM1

PWM2

ROMDT

DSCK

LRCK

DADT

CRCF

DOTX

SCCK

EFFK

SBCO

SCAND

MITSUBISHI

ELECTRIC

( / 52 )

7

OUTLINE : 42P2R (Top view)

BLOCK DIAGRAM

DVSS

DVDD3

DVDD5

SBQS

CRCF

SBCO

SCCK

SCAND

LOCK/DRD

Syndrome

Register

CRC

Checker

Sub Code

Serial I/F

CIRC

Decoder

SUBQ

Sub Code

SEL

CIRC

Sequencer

Correction

Register

Sync Det.

ECC

Control

Flag Control

EFM

De-Modulator

MCU I/F

DAC I/F

EFM

SEL

Channel

Control

Interpolation

18Kbit

SRAM

Address

Generator

SEL

Attenuate

Control

Flag

Control

Timing

SEL

De-EMP

SEL

Digital

Generator

DAC I/F

Audio

Interface

ALCR

ROMDT

DADT

DSCK

LRCK

EST

TRIN

Track Counter

DOTX

INT

R/W

MLA

MCK

Micro Computer I/F

MSD

S423

S846

C423

HFD

RC

LPF

HF

Defect

PLL VCO

AVSS

AVDD

Control

Slicer NRZ

HF

PLL

HPF1

SYNC

Current

Control

TLC

HPF2

Detector

IREF

SYNC

Protector

EFM

Timing

Generator

EFFK

MITSUBISHI

ELECTRIC

System

Clock

Selector

Clock

Doubler

Timing Generator

Oscillator

XI

XO

DXLPF

PWM

2/3 Det.

CLV

Freq.

Det.

DXRC

CLV

Control

+

Phase

Det.

Fig 1 : Block diagram

PWM2

PWM1

( / 52 )

8

ABSOLUTE MAXIMUM RATING

(Ta=25°C unless otherwise noted)

Symbol Parameter Condition Limit Unit

DVDD5-DVSS

DVDD3-DVSS

AVDD-AVSS Power supply voltage

Vi

Vo Output voltage

Pd Power consumption

Topr

Tstg

Power supply voltage

Power supply voltage -0.3 ~+4.5

Input voltage

Ambient temperature

Storage temperature

-0.3 ~+7

-0.3 ~+4.5

VSS-0.3≤Vi≤VDD+0.3

VSS≤Vo≤VDD

600

-10 ~+70

-40 ~+125

V

V

V

V

V

mW

°C

°C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Unit

DVDD5

DVDD3

AVDD

VIH

5V digital power supply voltage

3.3V digital power supply voltage

Analog supply voltage

"H" output voltage

Condition

MIN TYP MAX

0.7DVDD DVDD5

Limit

5.0 5.53.0

3.3 3.63.0

3.3 3.63.0

V

V

V

V

VIL

fOSC

fVCO

"L" input voltage

Oscillation frequency

(X'tal)

Oscillation frequency

(VCO)

DVSS

Single speed

Double speed MHz

Single speed

Double speed

Quad speed

6 times speed

8 times speed

8.4672 MHz

16.9344

33.8688Quad speed MHz

50.80326 times speed MHz

67.73768 times speed MHz

8.6436 MHz

17.2872 MHz

34.5744

51.8616 MHz

69.1488 MHz

0.3DVDD

V

MHz

MITSUBISHI

ELECTRIC

( / 52 )

9

ELECTRICAL CHARACTERISTICS

(Ta=25°C,DVDD5=5V, DVDD3=3.3V, AVDD=3.3V unless otherwise noted)

Symbol Parameter Unit

DVDD5

DVDD3 Operating voltage (3.3V, digital)

AVDD

| DD

| OH

| OL

| IH

| IL

| OZH

| OZL

f PLL1

f PLL2

f PLL3

Operating voltage (5V, digital)

Operating voltage (3.3V, analog)

Operating current

"H" output voltage

"L" output voltage

"H" input current

"L" input current

Off condition "H" output current

Off condition "L" output current

VCO (EFFK) free run

frequency

(RIREF=110kΩ,RRC=91kΩ)

Ta=-10~+70°C

Ta=-10~+70°C ≤8X

Ta=-10~+70°C

f osc=8.4672MHz

f vco=8.6436MHz

VDD=4.5V,| OH=-0.8mA

VDD=4.5V,| OL=0.8mA

VIH=4.5V

VIL=0.5V

VOH=4.5V

VOL=0.5V

VLPF=1.0V

VLPF=1.5V

VLPF=3.0V

Condition

8X~10X

≤8X

8X~10X

MIN TYP MAX

3.0

3.0

3.2

3.0

3.2

3.5

Limit

5.0 5.5

3.3 3.6 V

3.3

3.3

3.3

20

3.6 V

3.6 V

3.6

50

0.4

2

-2

2

-2

V

V

mA

V

V

µA

µA

µA

µA

kHz

kHz

kHz

f DX1

f DX2

f DX3

Rpu

Clock Doubler (S423) free run

frequency

(RIREF=110kΩ,RRC=91kΩ)

Pull up resistance

VLPF=1.0V

VLPF=1.5V

VLPF=3.0V

MITSUBISHI

ELECTRIC

5025 100

kHz

kHz

kHz

kΩ

( / 52 )

10

DETAILED DESCRIPTION

1. MCU interface

(1)Connection

M65827FP

MSD

MCK

MLA

B/W

MCU

Pin No.

8

6

9

7

(2)Mode description

Address

No.

0

1

2

3

4

5

6

Signal name Contents I/O

A7

L

L

L

L

L

L

L

MSD

MCK

MLA

R/W Data read write control pin (H : Read, L : Write) I

Address

A6

A5

L

L

L

L

L

L

L

L

L

L

L

L

L

L

MCU serial data input output pin

MCU shift clock input pin

MCU data latch clock input pin

A4

A3

A2

A1

A0

L

L

L

L

L

L

L

L

L

H

L

L

L

H

L

L

L

L

H

H

L

L

H

L

L

L

L

H

L

H

L

L

H

H

L

Data control

CLV servo, ATT, mute control

Configuration

Attenuation (Lch) control

Attenuation (Rch) control

Channel control

Playback speed control

Analog switch control

I/O

I

I

L

L

L

L

L

H

H

8

L7L L L H L L L

L L L L H L L H

L L L L H L H L9Track counter interrupt value (LSB)

B

L L L L H L H HATrack counter interrupt value (MSB)

C

L L L L H H L L

L L L L H H H LE

H H H HL L L LF

H X80≥

X X X X X X

Monitor output select

H

Track counter (LSB)

Track counter (MSB)

Interrupt mask

Kick timerL L L L H H L HD

Digital audio interface C bit control

Reset / Sleep / Clock disable control

Test Mode (For shipping test mode)

MITSUBISHI

ELECTRIC

( / 52 )

11

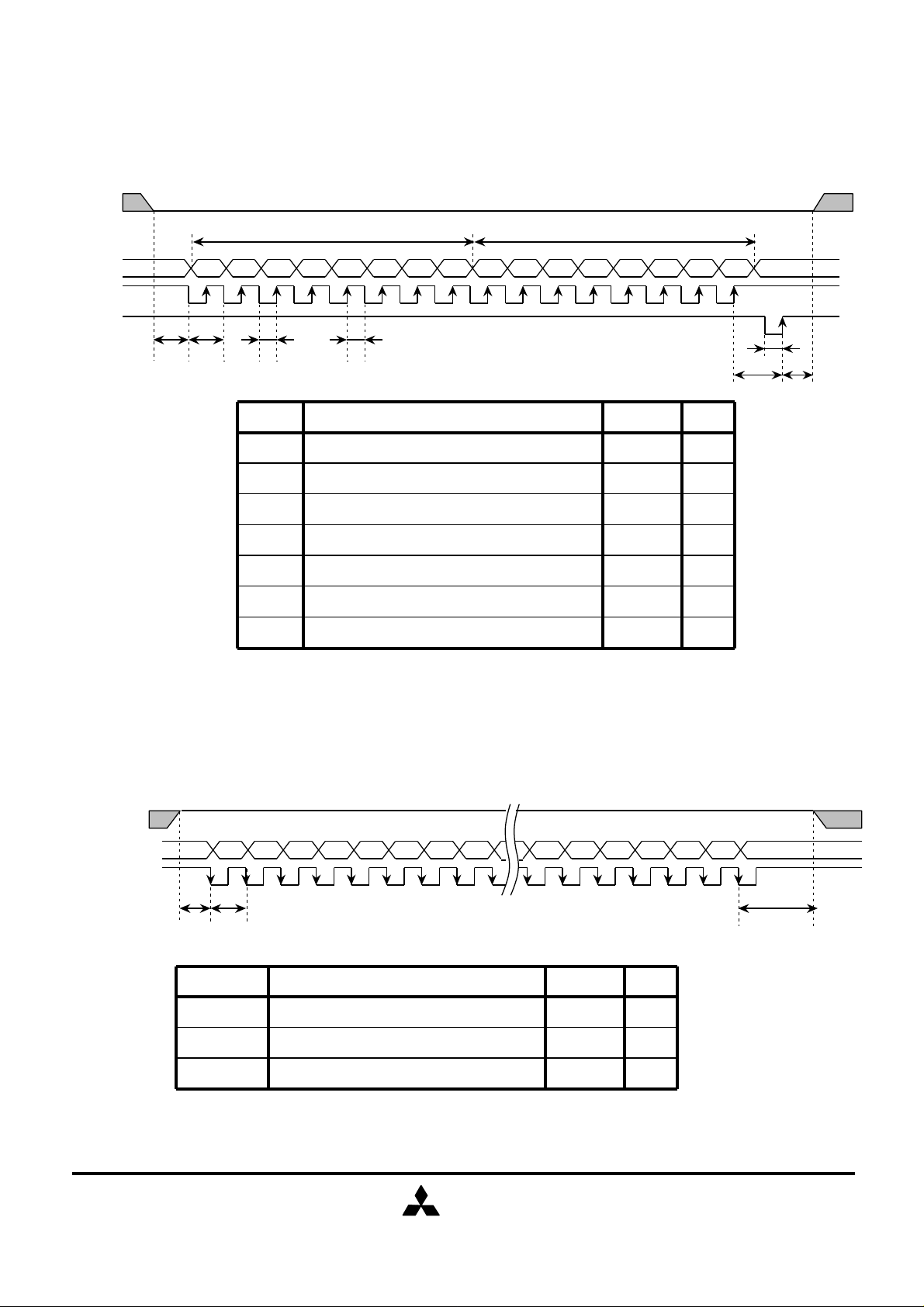

(3)Write timing

When R/W pin is L, MCU I/F is set in write mode. Address(1st byte) and data(2nd byte) are input with LSB

first. Address and data are captured at the rising edge of MCK and are latched in internal register at the

rising edge of MLA.

R/W

MSD

MCK

MLA

L

LSB MSB Data(2nd byte)LSB MSB

A0 A1 A2 A3 A4 A5 A6 A7

t1 t2

t6

Address(1st byte)

D0 D1 D2 D3 D4 D5 D6 D7

t3

Symbol Term Min

t1 Shift clock pulse width

t2

t3

t4

t5

t6

Shift clock set up time

Shift clock hold time

Latch clock set up time

Latch clock pulse width

Write set up time

Write hold timet7

200

100

100

200

200

250

200

Unit

nsec

nsec

nsec

nsec

nsec

nsec

nsec

t4

t5

t7

(4)Read timing (Subcode Q register interface)

When R/W pin is H, MCU I/F is set in subcode Q register read mode. Subcode Q data output from MSD pin

at the falling edge of MCK. Refer to (6) subcode Q I/F .

H

R/W

MSD

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

Q78 Q77 Q76 Q75 Q74 Q73 Q72

MCK

t8t9

t10

Symbol Term Min Unit

t8 Shift clock pulse width

t9

t10 nsecRead hold time

200

250

400

nsec

nsecRead set up time

MITSUBISHI

ELECTRIC

( / 52 )

12

(5) Write mode

Address 00h

Register name 0 1

Reserved

D0

S/S

D1

BCON

D2

BRAK

D3

ATT

D4

MUTE

D5

TRST

D6

Reserved

D7

D0: Reserved

Don't care.

D1: S / S (Start / Stop)

D2: BCON (Automatic brake control)

D3: BRAK (Brake)

CLV servo, Mute / ATT control

CLV OFF (STOP) CLV ON (START)

Automatic brake mode Manual brake mode

Manual brake OFF

ATT OFF ATT ON

MUTE ON MUTE OFF

Kick timer on Kick timer off

Manual brake ON

Default

0

0

1

0

0

1

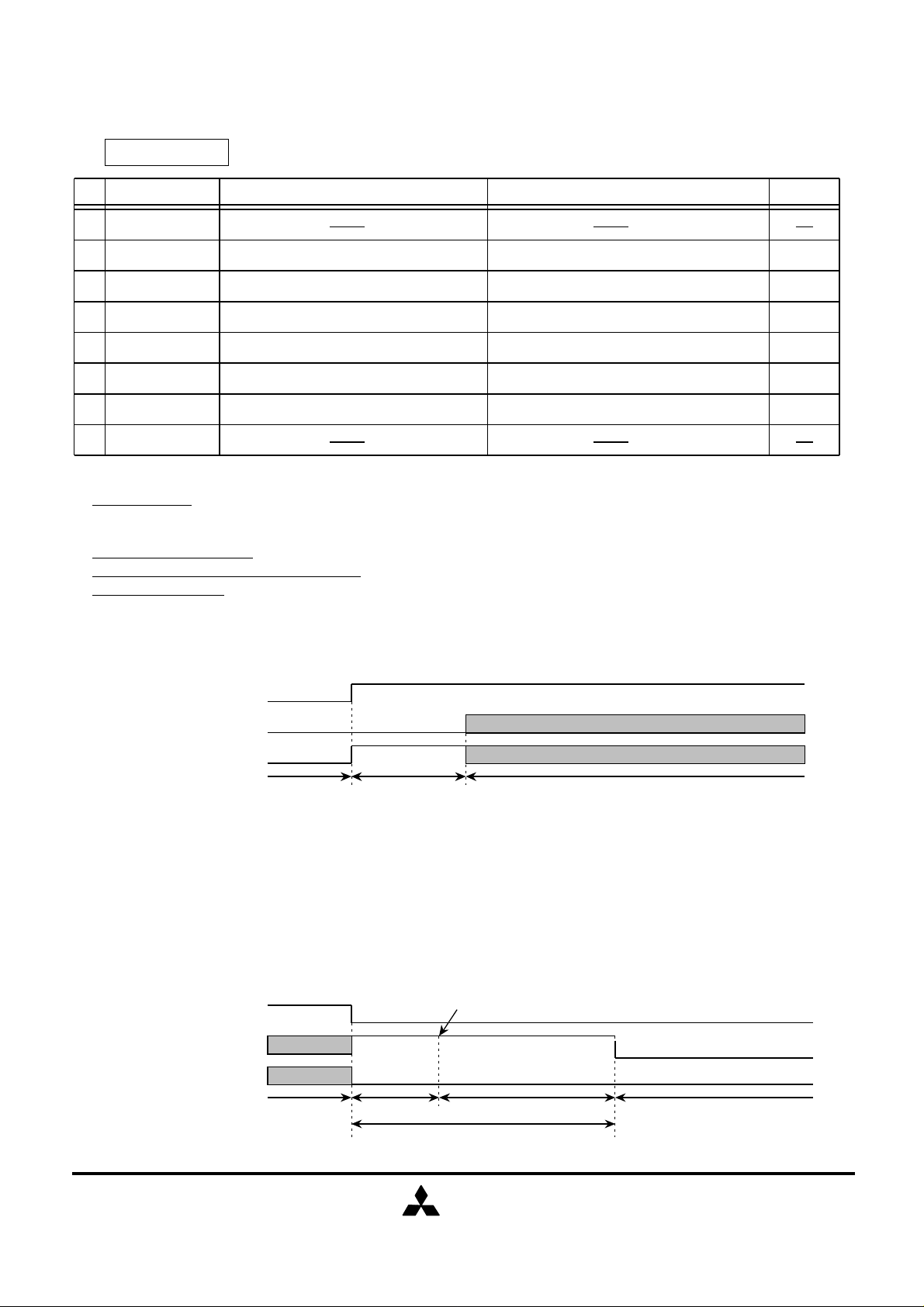

(1) Disc start

When S/S register changes from "0" to "1" , the kick pulse that is set by the kick control register at

address 0Bh is output. After kick mode, disc rotation switched to CLV mode automatically.

S/S

PWM1 (-Signal)

PWM2 (+Signal)

Kick time*

*Kick timer can be controlled by kick control register.

(2) Disc stop

(2-1) BCON=0 (Automatic brake mode)

When S/S register changes from "1" to "0", the brake pulse that is calculated by the internal circuit

output for the time 3t automatically. After brake mode, PWM switches to CLV off mode.

The time t is defined as the time that internal circuit detect the 2/3 rotation after S/S register

changes 0. The time of detecting the 2/3 rotation can be monitored by DRD signal in LOCK/DRD

pin.

Detect 2/3 rotation

S/S

PWM1 (-Signal)

CLV ONCLV OFF

PWM2 (+Signal)

CLV ON

t 2t

BRAKE (26.4sec max.)

MITSUBISHI

ELECTRIC

( / 52 )

13

CLV OFF

tmax = 8.8 sec

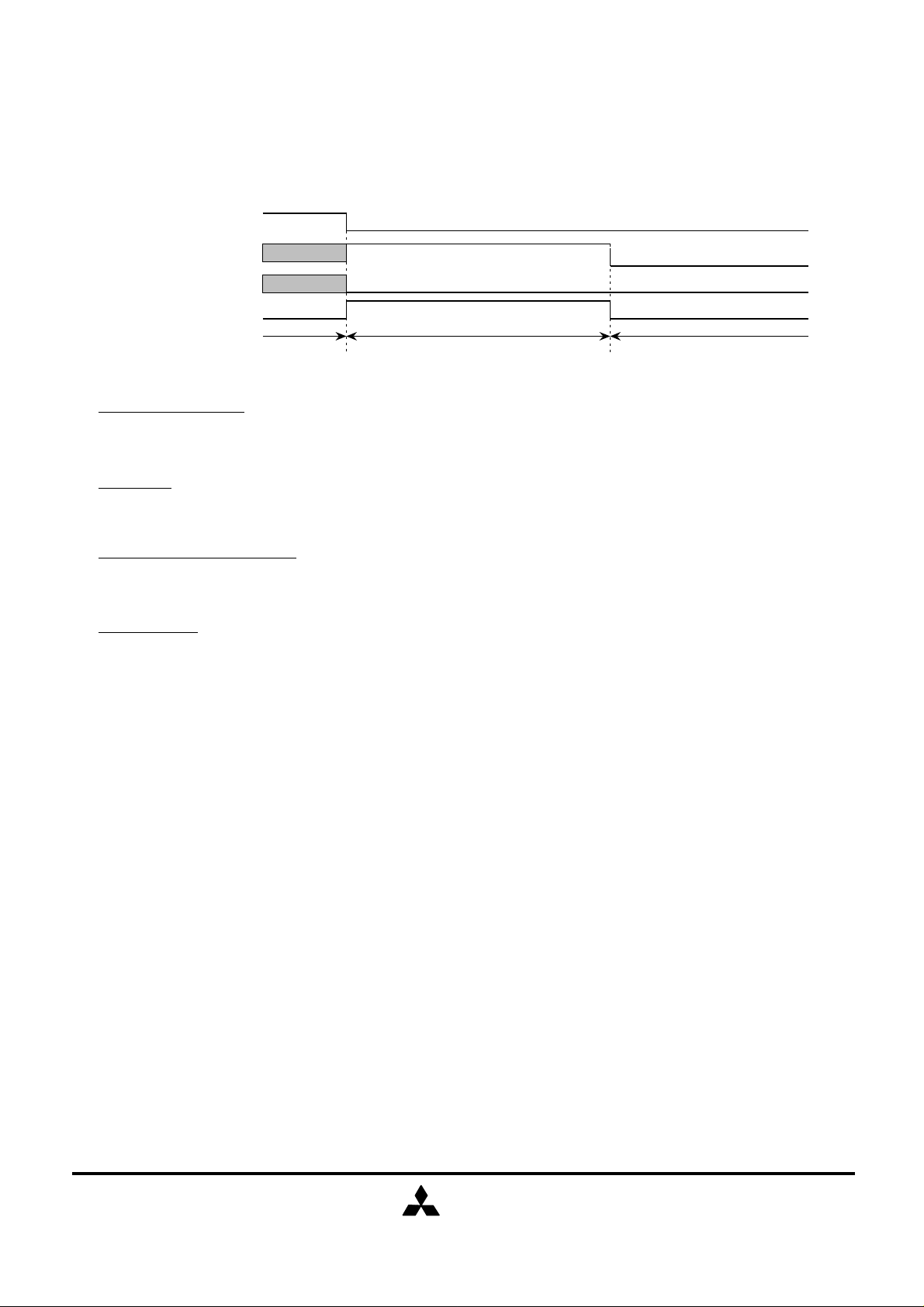

(2-2) BCON=1 (Manual brake mode)

When S/S register change from "1" to "0", PWM output brake pulse while BRAK register is "1".

This mode is used to stop the disc rotation by manual operation.

S/S

PWM1 (-Signal)

PWM2 (+Signal)

BRAK

BRAKECLV ON

D4: ATT (Attenuate)

ATT=0: Attenuation OFF

ATT=1: The output data of DADT and ROMDT are attenuated by address 02h and 03h.

D5: MUTE

MUTE=0: Mute on for DADT and ROMDT.

MUTE=1: Mute off for DADT and ROMDT.

D6: TRST (kick timer reset)

TRST=0: Kick timer active

TRST=1: Kick timer stopped

D7: Reserved

Don't care

CLV OFF

MITSUBISHI

ELECTRIC

( / 52 )

14

Address 01h

Configuration

Register name

NONAUDIO

D0

D1

ECCMOD

FLPDIS

D2

PFHEN VCO upper limiter OFF VCO upper limiter ON

D3

D4

HFDDIS

D5

GAINCNT

D6

GAINSEL

D7

Reserved

D0: NONAUDIO

NONAUDIO=0: Interpolation is enabled

C2 flag from EST pin output at 16 bit audioword unit.

NONAUDIO=1: Interpolation is disabled, prohibit interpolation.

C2 flag from EST pin output at 8 bit data byte unit.

D1: ECCMOD (Error correction mode)

ECCMOD=0: C1:2 error correction,C2:4 errors correction

ECCMOD=1: C1:2 error correction,C2:2 errors correction

Interpolation enable (Audio mode) Interpolation disable (CD-ROM mode)

C1:2 errors correction

C2:4 errors correction

False-lock protection circuit On Quasi-lock protection circuit Off

HFD enable HFD disable

Normal CLV gain mode CLV gain select mode

1/2 CLV gain mode 1/4 CLV gain mode

0 1

C1:2 errors correction

C2:2 errors correction

Inhibit

Default

0

0

0

0

0

0

0

0

D2: FLPDIS (False lock protection circuit disable)

FLPDIS=0: False lock protection circuit on

FLPDIS=1: False lock protection circuit off

(Refer to address 07h)

D3: PFHEN (VCO oscillation frequency upper limiter enable)

PFHEN=0: VCO oscillation frequency limiter is stopped

PFHEN=1: VCO oscillation frequency limiter is active

Limiter value = 8.6436MHz X 1.3 X S (S:Playback speed)

D4: HFDDIS (HFD disable)

HFDDIS=0: HFD input enable

HFDDIS=1: HFD input disable

D5:GAINCNT(CLV gain control)

D6:GAINSEL(CLV gain select)

GAINCNT=0: Normal gain mode.

GAINCNT=1: CLV gain control mode.

CLV gain can be selected 1/2 and 1/4 of normal gain by GAINSEL register.

MITSUBISHI

ELECTRIC

( / 52 )

15

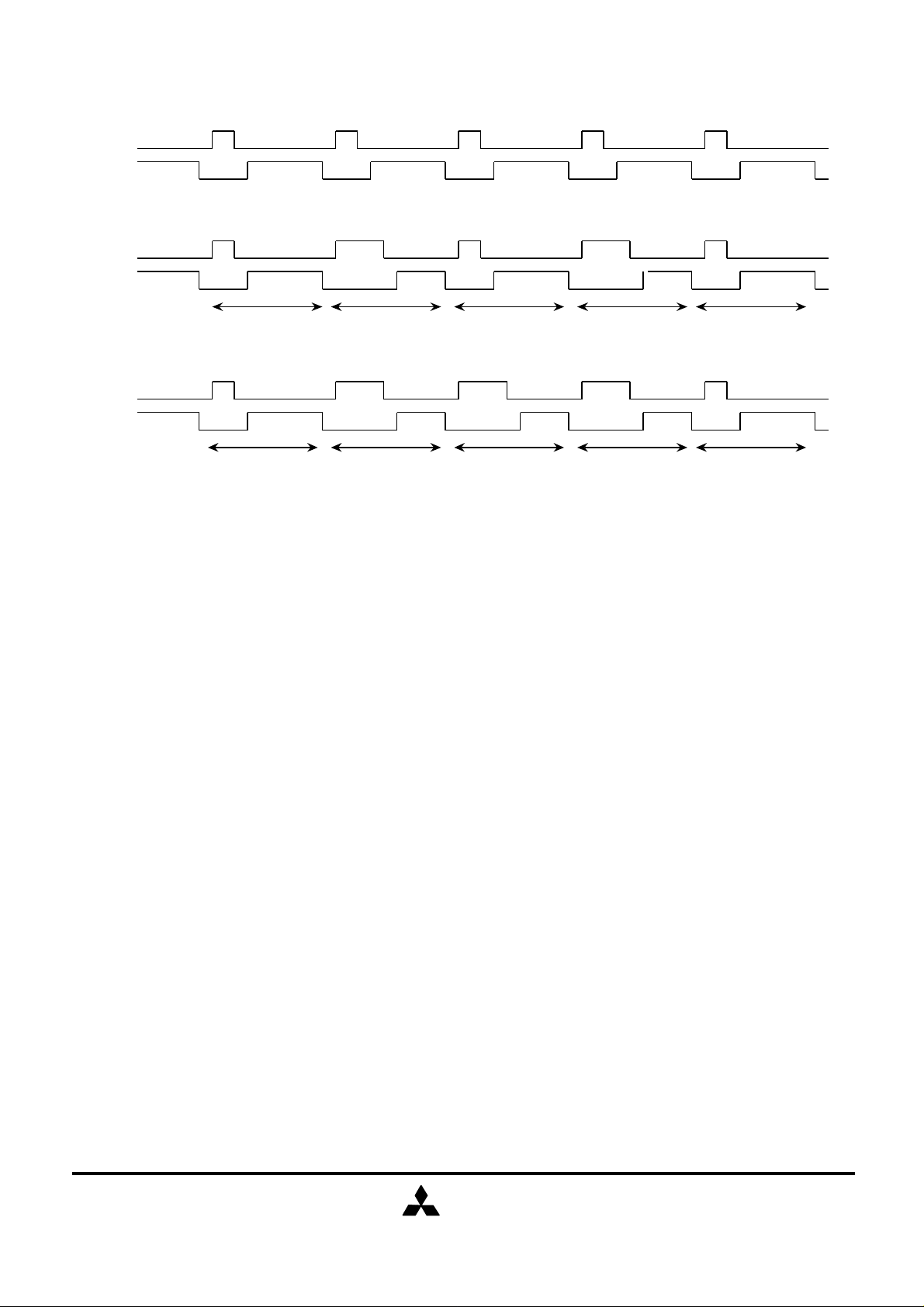

PWM2

PWM1

PWM2

PWM1

(a) Normal CLV gain mode (GAINCNT=0)

(b) 1/2 CLV gain mode (GAINCNT=1,GAINSEL=0)

PWM2

PWM1

CLV Mode CLV Mode

(c) 1/4 CLV gain mode (GAINCNT=1,GAINSEL=1)

PWM1=PWM2 PWM1=PWM2

PWM1=PWM2 PWM1=PWM2

PWM1=PWM2CLV Mode CLV Mode

CLV Mode

MITSUBISHI

ELECTRIC

( / 52 )

16

Loading...

Loading...