M65824AFP

/23

Specifications

1

MITSUBISHI SOUND PROCESSOR ICs

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

DESCRIPTION

The M65824AFP is a CMOS IC developed for compact disc players.

(suitable for CD-DA:Compact Disc-Digital Audio)

It has built-in memory,adjustment-free PLL and D/A converter with DSP function.

FEATURES

♦Adjustment free EFM-PLL circuit(Includes VCO)

♦±8 frames jitter margin

♦Digital CLV servo control

♦Attenuation(-12dB)

♦4 times over sampling IIR type digital filter

♦Digital de-emphasis function

♦D/A converter

♦A smaller package

♦Analog LPF

♦Digital audio interface

♦External D/A mode

RECOMMENDED OPERATING CONDITIONS

Supply voltage range(interface)·············································································DVDD=2.7 to 5.5V

Supply voltage range(internal logic system and analog)······················DSPS,AVDD=2.7 to 3.3V

Rated supply voltage(interface)························································································DVDD=5.0V

Rated supply voltage(internal logic system and analog)·································DSPS,AVDD=3.0V

Rated power dissipation···········································································································100mW

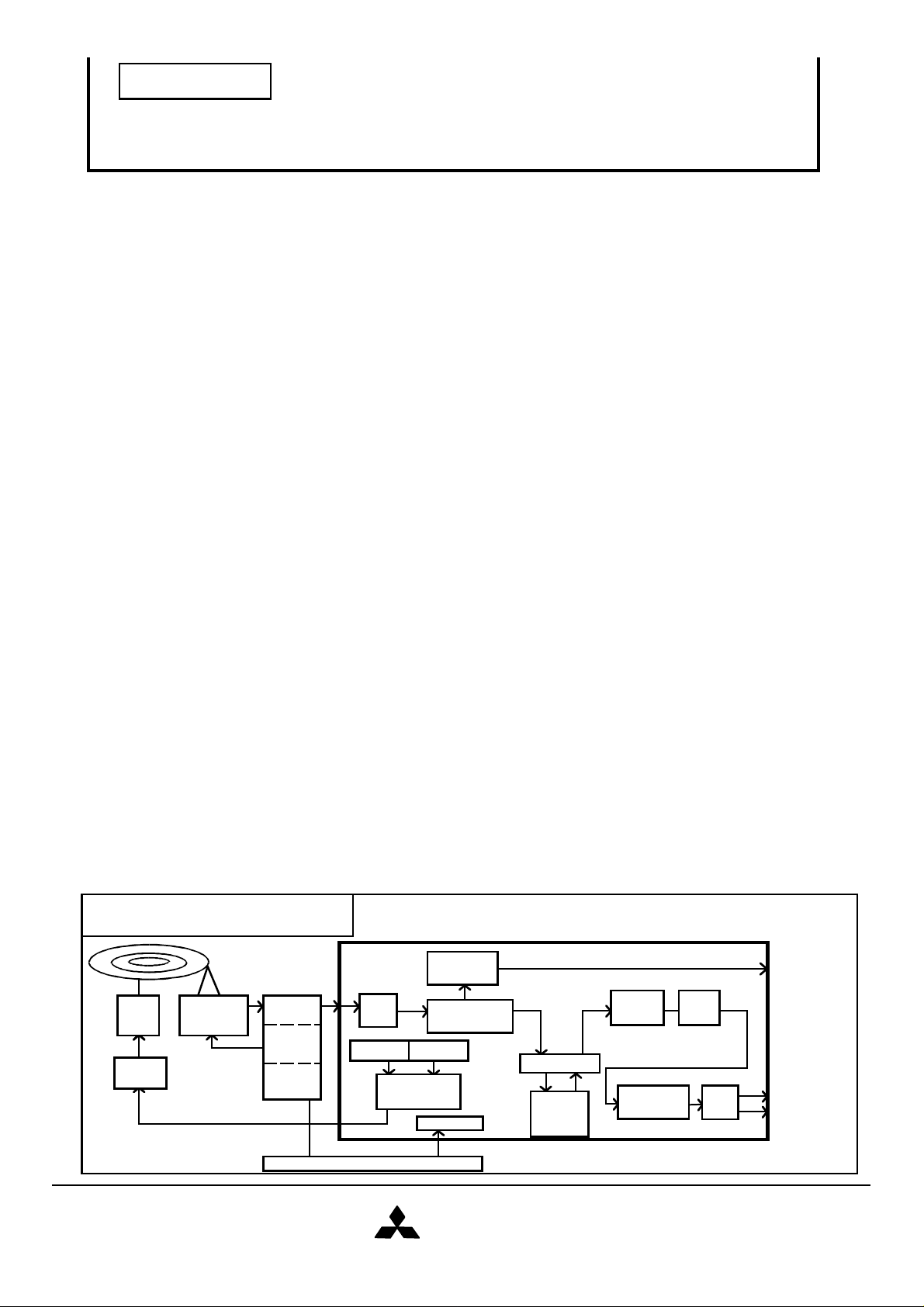

SYSTEM BLOCK DIAGRAM

M65824AFP

M

Motor

Driver

Optical

Pick-up

RF-Amp

Pick-up

Servo

Auto

Adjustment

PLL

Slicer

PLL CLK

CLV

Digital Servo

Subcode

Interface

EFM

De-modulator

OSC CLK

MCU I/F

18kSRAM

ECC

C1:2error

C2:2error

Inter

polation

4fs Digital

Filter

DeEMP

D/A

Display

L

R

System Control Microprocessor

MITSUBISHI

ELECTRIC

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

Microcomputer

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

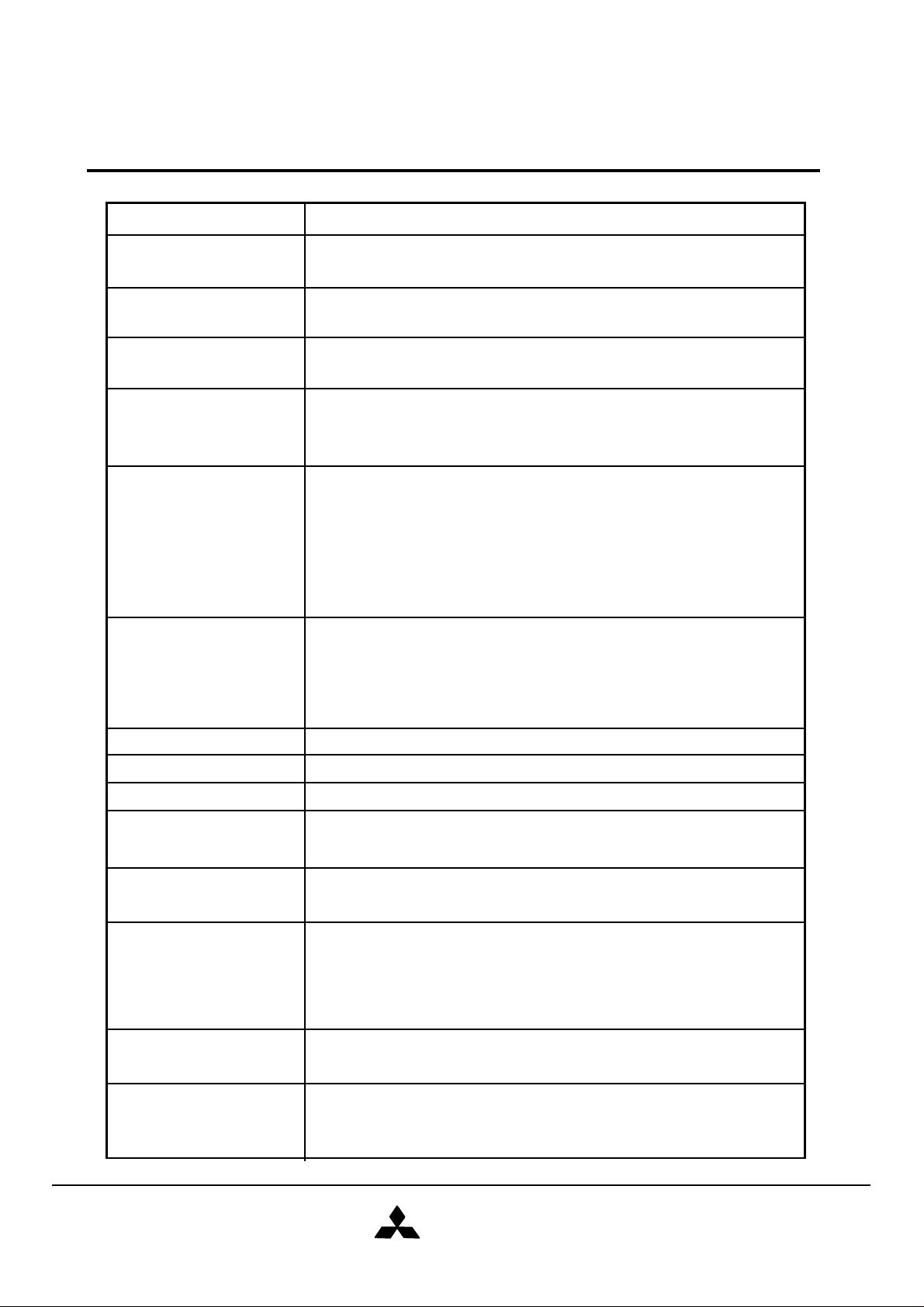

1.BUILT-IN FUNCTIONS

Functional block

D/A converter

Memory

PLL

EFM demodulator

Subcode decoding

CRC decoding

Description:

• 64fs 1bit Σ∆ D/A converter

• S/N:74dB(theoretically)

• 18kSRAM(built-in)

• ±8 fames jitter margin

• Adjustment free VCO

• Slice level control

• EFM demodulation

• Frame sync.detection,protection&interpolation

• Frame sync.signal output

• Subcode P to W decoding,serial output

• Subcode Q register

• Subcode Q-CRC Check

• Subcode sync.signal output(S0/S1)

• Emphasis detection,built-in de-emphasis

circuit control

• C1:Duplex,C2:Duplex

• De-scramble

• De-interleave

• Error monitor output

Data interpolator • Averaging/Holding

D/A interface

Digital filter • 4 times over sampling digital filter

De-emphasis

CLV digital servo

interface

Digital audio

interface

HFD

• Muting control

• Digital de-emphasis (IIR type digital filter)

• Automatic emphasis flag detection

• PWM output

• Low disc rotation detection

• CLV digital servo control

• Muting control

• Attenuation(-12dB)

• Subcode Q register interface

• Digital audio interface output ON/OFF

• Clock accuracy input

• TLC voltage "hold"

• LPF output "open"

• PWM output "regular acceleration"

MITSUBISHI

ELECTRIC

2

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

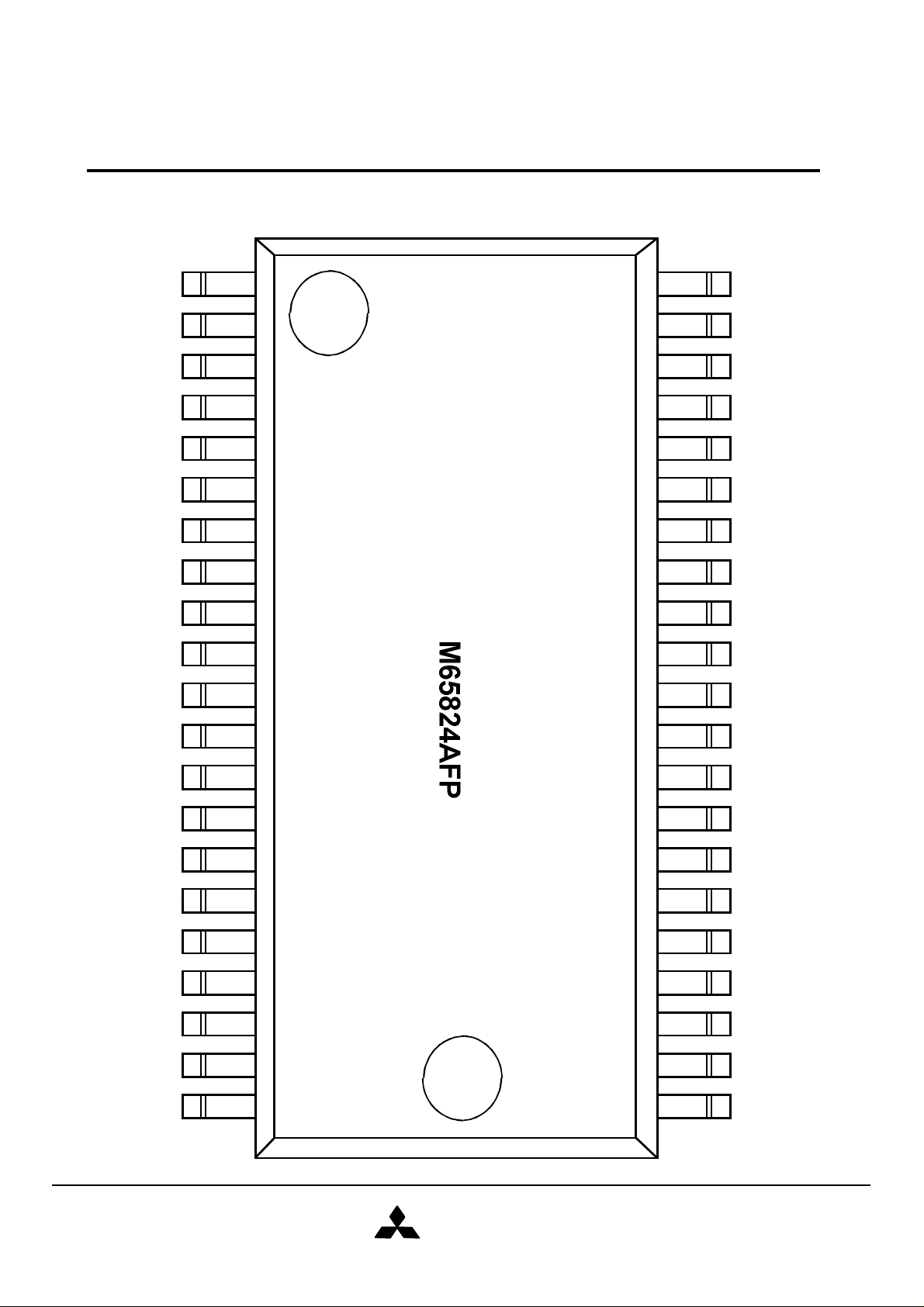

2. PIN CONFIGURATION

AVSS

LOCK/DRD

TEST I/O

DOTX

XI

DVSS

TEST

SBCO

SYCLK

KILLB

HF

AVDD

IREF

EXP2

MSD

MCK

DVSS2

PWM

SCAND

CRCF

DVDD

3

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

ADJCLK

ACLRB

C423/DSCK

XO

1

2

3

4

5

6

7

8

9

10

11

42

41

40

39

38

37

36

35

34

33

32

RAGND

ROUT/LRCK

RAVDD

LAVDD

LOUT/DO

LAGND

EXP1

MLAB

SCCK

EFFK

EST1

EST2

TLC

LPF

12

13

14

15

16

17

18

19

20

21 22

31

30

29

28

27

26

25

24

23

DVDD2

SBQS

DSPS

MITSUBISHI

ELECTRIC

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

4

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

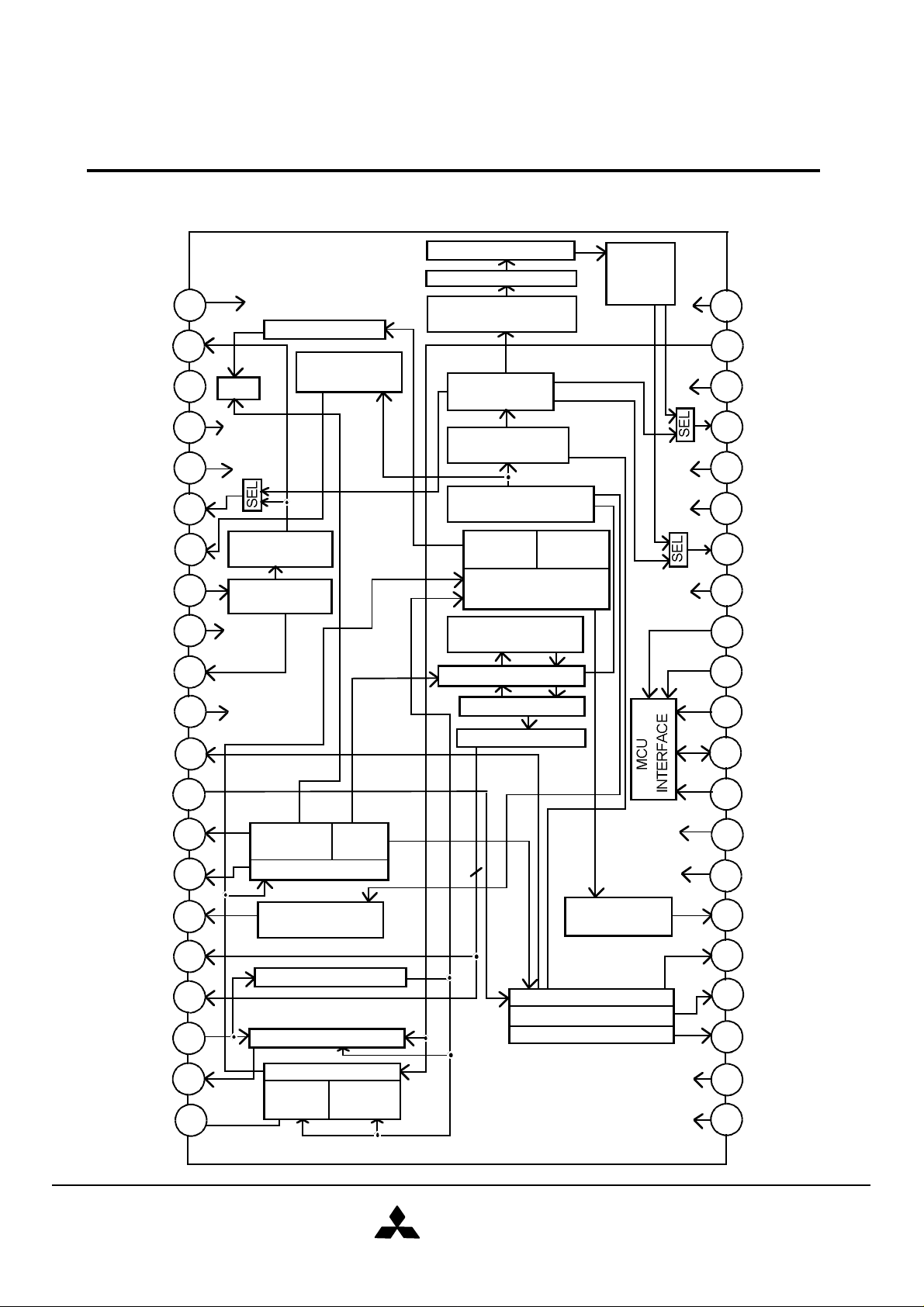

3. BLOCK DIAGRAM

AVSS

ADJCLK

LOCK/DRD

TESTI/O

ACLRB

C423/DSCK

DOTX

XI

DVSS

XO

1

2

3

4

5

6

7

8

9

10

ANALOG

GND

3/4DETECTOR

SEL

TEST

CONTROL

RESET

X'tal TIMING

GENERATOR

CLOCK

GENERATOR

DIGITAL

GND1

DIGITAL AUDIO

INTERFACE

Σ∆ MODULATOR

Dither

16fs DIGITAL

FILTER

4fs DIGITAL

FILTER

DE-EMPHASIS

FILTER

INTERPOLATION

MUTE CONTROL

FREQ

CONTROL

18K SRAM

(8bit×2400WORD

MEMORY CONTROL

PHASE

CONTROL

CLV SERVO

CONTROL

1bitD/A

LPF

L/Rch

42

AVDD

41

IREF

RAGND

40

ROUT/LRCK

39

RAVDD

38

LAVDD

37

36

LOUT/D0

35

LAGND

34

EXP2

33

EXP1

TEST

SBCO

SCCK

SYCLK

EFFK

KILLB

EST1

EST2

HF

TLC

LPF

11

12

13

14

15

16

17

18

19

20

21

TEST

CONTROL

SYNC DET.

PROTECT

EFM TIMING GEN.

DIGITAL SILENCE

DETECTOR

HFD Generate

HF COMPARATOR

VCO

FREQ

DET.

EFM

DEMOD

.

PHASE

DET.

CIRC DECODER

ERROR MONITOR

HFD CONTROL

DIGITAL

GND2

DIGITAL

VDD2

PWM

MODULATOR

SUBCODE DEMOD

SUBCODE Q CRC

SUBCODE Q REGISTER

VDD for

INTERNAL

LOGIC

DIGITAL

VDD1

32

31

30

29

28

27

26

25

24

23

22

MLAB

MSD

MCK

DVSS2

DVDD2

PWM

SCAND

CRCF

SBQS

DSPS

DVDD

MITSUBISHI

ELECTRIC

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

5

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

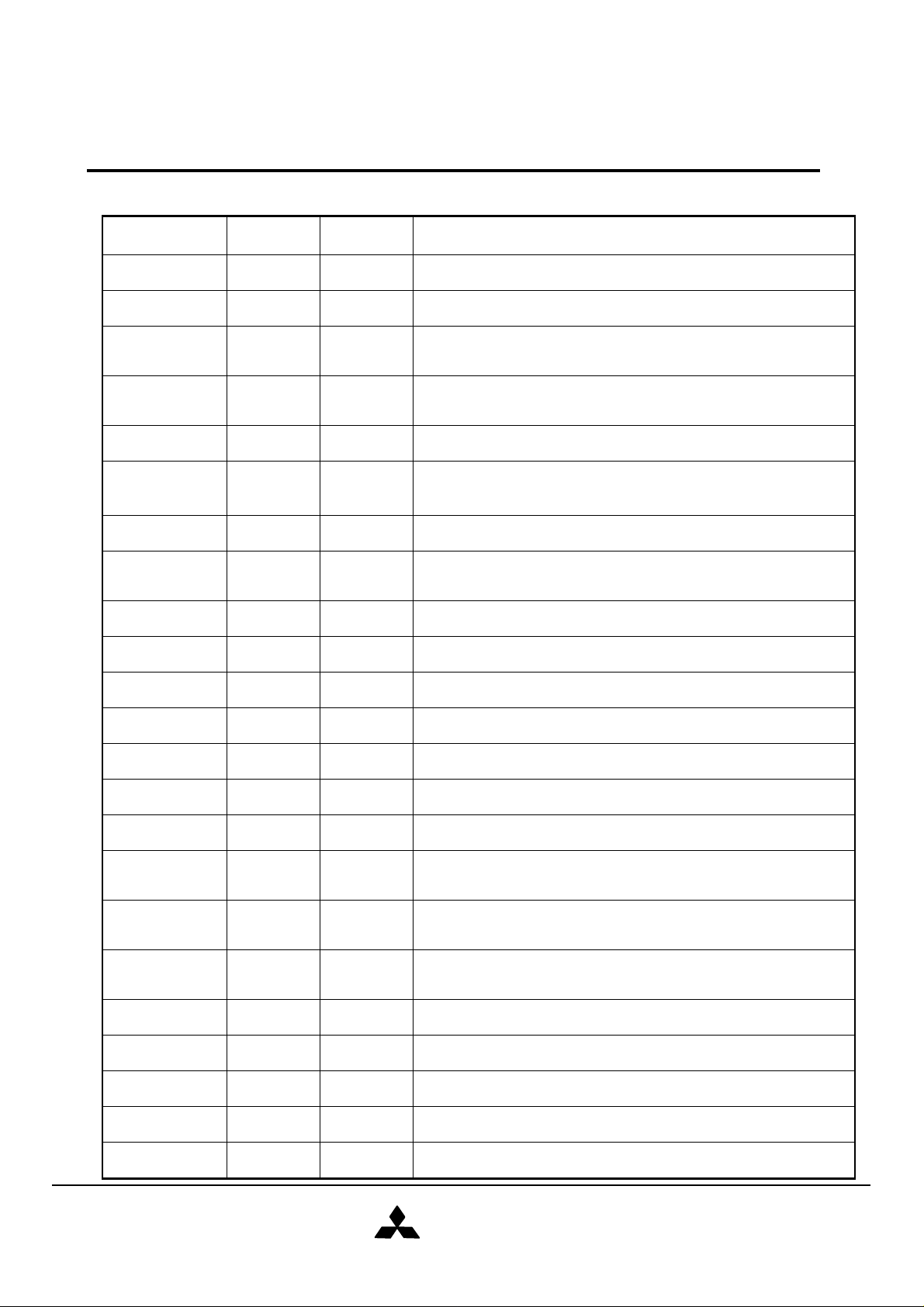

4. PIN DESCRIPTION

pin No.

Name I/O Function

1 AVSS 2 ADJCLK O

3

LOCK/DRD

4 TEST I/O I

5 ACLRB I

6

C423/DSCK

7 DOTX O

8 XI I

9 DVSS -

10 XO O

O

O

Analog system GND

Clock output for servo adjustment:f=88.2KHz

Lock monitor / low disc rotation detect

output

Test control

System reset input : reset ="L"

No pull-up

Crystal system clock output f=4.2336MHz

Ext.D/A mode: Data shift clock output

Digital out

Crystal oscillator input (with Feedback R)

f:8.4672MHz

Digital system GND

Crystal oscillator output

11 TEST I

12 SBCO O

13 SCCK I

14 SYCLK O

15 EFFK O

16 KILLB O

17 EST1 O

18 EST2 O

19 HF I

20 TLC O

21 LPF I/O

22 DVDD -

Normal/Test select input : Test"H"

Subcode serial output

Shift clock input for subcode data read

Frame lock status output : Lock="H"

EFM frame clock output : duty=50%

Digital silence : DIGITAL ZERO="L"

Opendrain output

Error status output 1

"H"When error detect at C1 decoder

Error status output 1

"H"When error detect at C2 decoder

High frequency signal input

Slice level control signal output

Loop filter for PLL

Digital interface power supply

23 DSPS -

Digital system power supply(internal logic)

MITSUBISHI

ELECTRIC

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

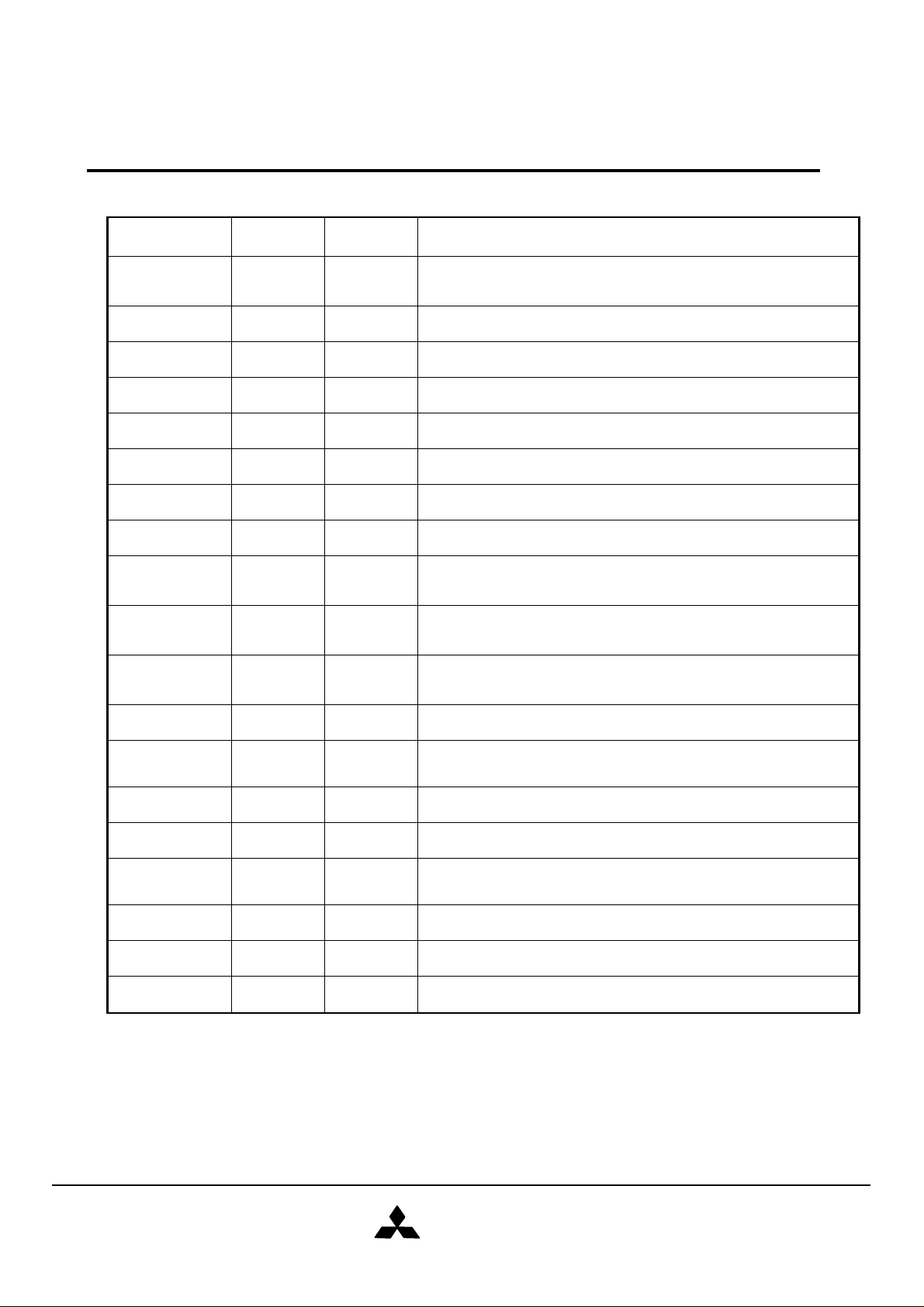

4.PIN DESCRIPTION(CONTINUANCE)

6

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

pin No.

Name I/O Function

Subcode Q register read interrupt signal

24 SBQS O

"L" for read

25 CRCF O CRC checked results of Subcode Q:CRC OK="H"

26 SCAND O Subcode sync.signal output:"H" for sync.

27 PWM O Disc motor driver PWM output(Both sides)

28 DVDD2 - Digital interface power supply2

29 DVSS2 - Digital system GND2

30 MCK I Microcomputer interface shift clock input

31 MSD I/O Microcomputer interface serial data I/O

Microcomputer interface latch clock

32 MLAB I

Built-in 22KΩ pull up resistor to DVDD

Input pin (be read via serial I/F) No.1

33 EXP1 I

Built-in 4.7KΩ pull up resistor to DVDD

34 EXP2 I

Input pin (be read via serial I/F) No.2

Built-in 4.7KΩ pull up resistor to DVDD

35 LAGND - Lch Analog GND

Audio signal output(L-ch)

36 LOUT/D0 -

Ext.D/A mode;Audio serial data output

37 LAVDD O Lch Analog power supply

38 RAVDD - Rch Analog power supply

39

ROUT/LRCK

O

Audio signal output(R-ch)

Ext.D/A mode;LR clock output

40 RAGND - Rch Analog GND

41 IREF I PLL circuit reference current setting

42 AVDD - Analog System power supply

Schmitt trigger input is the following

ACLRB(No.5),TEST(No.11),SCCK(No.13),MCK(No.30)

MLAB(No.32),EXP1(No.33),EXP2(No.34)

Reset condition for ACLRB(No.5:No pull-up resistor,Normal CMOS input)

minimum reset time :1µsec

MITSUBISHI

ELECTRIC

MITSUBISHI SOUND PROCESSOR ICs

M65824AFP

/23

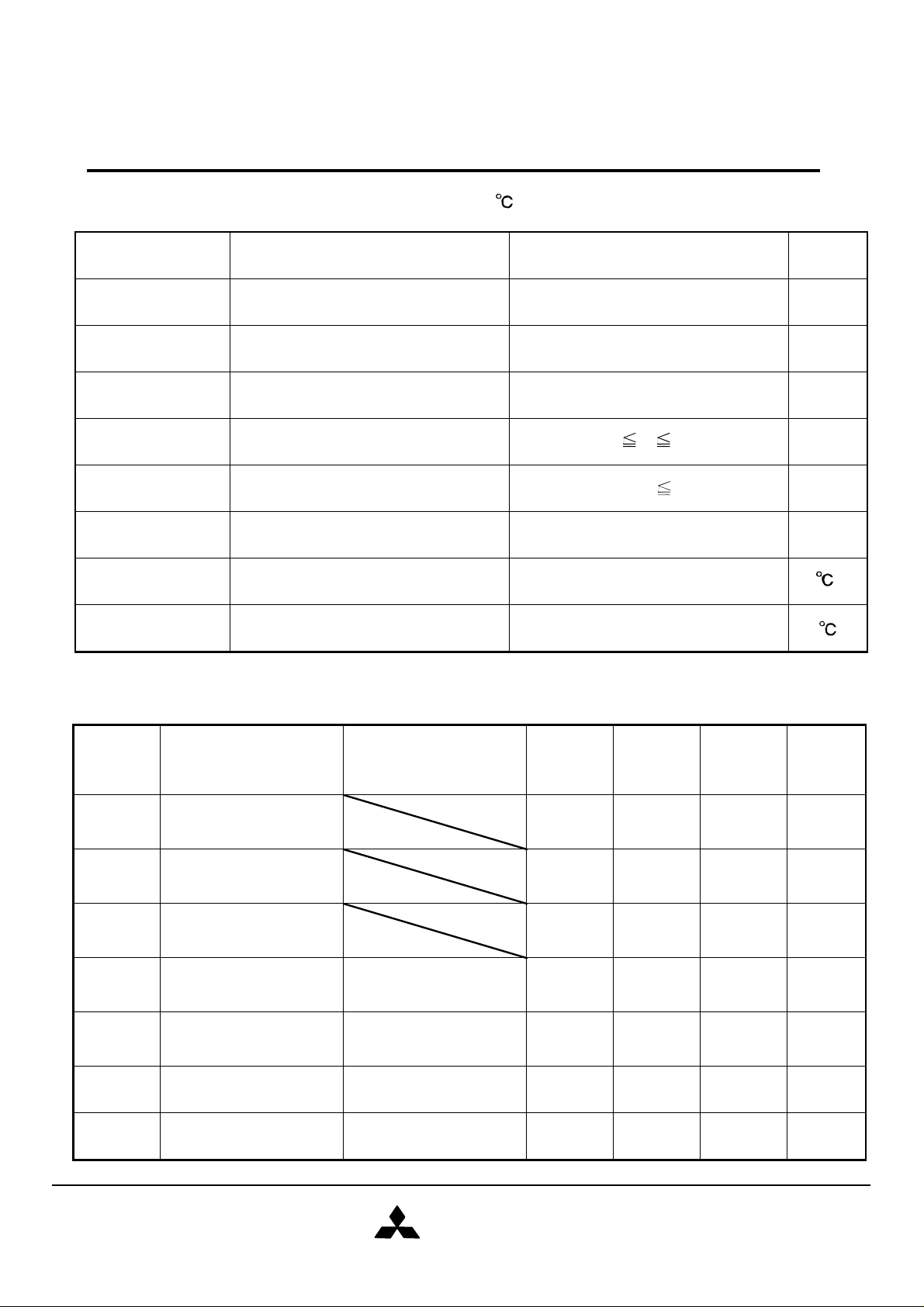

5.ABSOLUTE MAXIMUM RATINGS

(Ta=25

,unless otherwise noted)

7

×

CD PLAYER DIGITAL SIGNAL PROCESSOR WITH BUILT-IN DAC

Symbol Item Rating Unit

DVDD-DVSS Supply voltage(interface) -0.3 to +6.5 V

AVDD-AVSS Supply voltage(analog) -0.3 to +3.6 V

DSPS-DVSS Supply voltage(internal) -0.3 to +3.6 V

Vi Input voltage

DVSS-0.3 Vi DVDD+0.3

V

Vo Output voltage DVSScVo DVDD V

Pd Power dissipation 350 mV

Topr Operating temperature -10 to +70

Tstg Storage temperature -40 to +125

6.RECOMMENDED OPERATING CONDITIONS

Symbol Item conditions Min Typ Max Unit

DVDD

AVDD

Supply voltage

(interface)

Supply voltage

(analog)

2.7 5.0 5.5 V

2.7 3.0 3.3 V

Supply voltage

DSPS

VIH

VIL

(internal)

Input voltage

("H"level)

Input voltage

("L"level)

Output frequency Normal speed

fosc

fvco

Output frequency Normal speed

Except

Schmitt input

Except

Schmitt input

MITSUBISHI

ELECTRIC

2.7 3.0 3.3 V

DVDD 0.7

DVSS -

- 8.4672 - MHz

- 8.4636 - MHz

- DVDD V

×

DVDD 0.3

V

Loading...

Loading...