SPECIFICATION OF INTEGRATED CIRCUIT

)

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

1. TYPE NO.

2. FUNCTION

2.1 CIRCUIT FUNCTION

2.2 BLOCK DIAGRAM

3. APPLICATION

4. OUTLINE

4.1 PACKAGE

4.2 OUTLINE DRAWING

M65761FP

QM-Coder

see the third page

FAX, PPC etc

100 Pin Plastic Molded Quad Flat Package (Fine Pitch)

[100P6S-A]

G465181

5. CIRCUIT DIAGRAM

DRAWING

6. PIN DIAGRAM

7. OTHER SPECIFICATIONS

see the next page (2page

see cover page of specification

PIN CONFIGURATION(TOP VIEW

)

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

GND

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PD8

PD9

PD10

V

GND

PD11

PD12

PD13

PD14

PD15

PD16

PD17

PD18

PD19

PD20

PD21

V

GND

PD22

PD23

PD24

VCC

TEST0

TEST1

TOUT1

TOUT2

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

1

2

3

4

5

6

7

8

9

10

11

12

CC

CC

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

GND

PXCKO

VCCD15

M65761FP

D14

D13

D12

GND

VCCD11

D10D9D8

GND

CC

V

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

D7

D6

D5

D4

GND

CC

V

D3

D2

D1

D0

GND

CC

V

RESET

A3

A2

A1

A0

BHE

CS

MCLK

GND

CC

V

WR

RD

DMAAK

BUS16

DMARQ

INTR

XCLK

GND

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

CC

V

PD25

PD26

PD27

PD28

PD29

PD30

PD31

PDRQ

GND

PDRD

PDAK

PDWR

RVID

PRDY

SVID

Outline 100P6S-A

PTIM

PXCK

CC

V

XWAIT

BLOCK DIAGRAM

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

100

RESET

CS

68

62

–

A0

64

–––––

BHE

A3

WR

58

63

67

SWITCH

––––

D0

RD

71

57

CONTEXT TABLE RAM

CONTEXT GENERATION

D4

D3

77

74

QM-CODER

D7

80

D8

83

D11

86

HOST BUS I/F

TABLE RAM PROBABILITY ESTIMATION

D12

89

D15

92

DMARQ

DMAAK

56

54

INTR

53

BUS16

55

MCLK

61

TEST1

98

TEST0

99

Leave TOUT1 and TOUT2 open.

97

96

TOUT1,2

94

70 76 82 88

60

GND

51

14 27 40

1

TYPICAL PREDICTION

PIXEL DATA

–

28

–

PD22

LINE MEMORY

37

PD31

PD0-11=CX0-11

PD15=PEUPE

38

PDRQ

43

PDAK

41

PDRD

42

PDWR

45

PRDY

IMAGE DATA • CONTEXT I/F

47

PTIM

(=XRDY)

VCC

13 26 39 50 59 69 75 81 87 93

12

PD10

–

15

–

PD11

25

PD21

2

PD 0

–

–

CONTEXT DATA

48

PXCK

(=XTIM)

46

95

SVID

PXCKO

44

RVID

(=SPIX)

52

XCLK

(=RPIX)

49

XWAIT

9. CODING SPECIFICATION

(1) Coding Algorithm

• QM-Coder

(JBIG Standard Arithmetic Coding System)

(2) Context

(i) Built-in Context Mode

a) Template Model

• 2 or 3 line 10 pixel template (See Fig9. 1)

(This agrees with the template used with the minimum resolution of JBIG)

NOTE:The coding efficiency of the 3-line template is better than that of the 2-line template by several %.

b) Adaptive Template (AT)

• It is possible to move up to 127pixcels on the coding line.

(The position of ATgiven instruction by the MPU)

Note:It is possible to improve the coding effeciency against the dither image

by the use of AT.

• It is posible to change the position of AT line by line in the middle of coding

and decoding.

Note:It is not possible to change the template at the time when change the

position of the AT pixels.

(ii) Extenal Context Mode

• It is possible to input any context up to 12 bits.

(It is possible to interface with JBIG Progressive Coding and the Arithmatic Coding of JPEG Option Function)

X

A

A

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

XXX

XXXX?A

XX

XXXXX?A

XXX

Fig. 9. 1 Template (X, A)

(Top : 3line, Bottom : 2line)

XXX

XXXX

X?X

MAX127

X

X

X

MAX127

Fig. 9. 2 Adaptive template (A)

XXX

X?X

X

(3) Typical Prediction

• Agreement with the Typical Prediction of the lowest resolution of JBIG.

The pseudo-pixcel (SLNTP) is geneated by the symbol LNTPwhich shows whether the coding/decoding process agree with the directly

before line.If they agree, the line is not coding/decoding .

This makes it possible to shorten the time of process and rejection of the code data.

SLNTPy =! ( LNTPy + LNTPy-1 ) (y:line number, LNTPy=1; LNTPy-1=1)

(4) Deterministic Prediction

• This LSI is not equipped with the Typical Prediction.However,the DP function is realized when the DP pixels are identified and

eliminated by the extenal circuits during the external context mode.

(5) Coding Data Format

• The Stripe Data Entity (SDE)

(=Stripe coded data with byte stuffing (PSCD) + end marker (SDNORM/ SDRST)) Coding/decoding of one stripe portion os

perfformed.In case of the multi-striped (construct the multi stripes) stripes are activated one at a time.

(6) Marker Code

• The SDE end marker is supported.(SDNORM=02h, SDRST=03h, ABORT=04h)

(During coding the marker code previously set in the register is outputted.During decoding ,the marker code detected by requesting an

interrupt to MPU when the marker is detected is read out od register.)

(7) Rough Estimate of Coding and Decoding Time(T1:M65761FP as a whole,T2;Processing Time of the arithmetic coding section alone)

• The total number of clocks needed for coding and decoding 1 page (stripe)is calculates roughly using the following equations.

T1= (p ∗ Lp) + (9/8 ∗ C) + (α∗Lp)

- S ∗ ((1 - β) ∗ p ∗ Ltp - Lp) [clock]

T2= (p ∗ Lp) + (9/8 ∗ C)

- S ∗ ((p ∗ Ltp) - Lp)) [clock]

p : Number of pixcels/line β : about 0.3

Lp : Number of lines/page

Ltp : Number of TP line /page

C : Number of coded data bits/page

S= 1: TP exists 0: No TP α : about 10

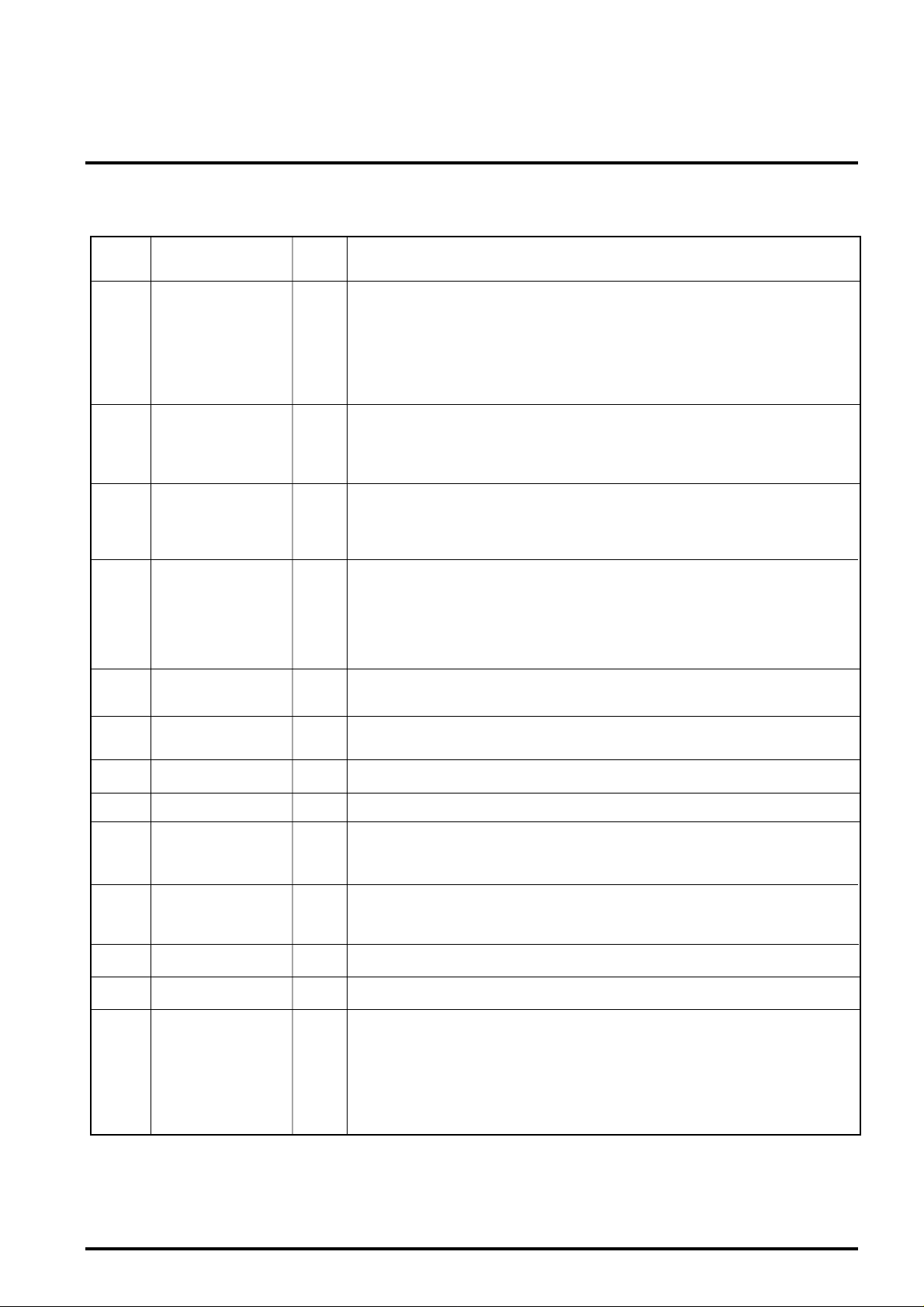

10. FUNCTIONAL DESCRIPTION OF PINS

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

Classification Pin name I/O Function

RESET

CS

A0-3

BHE

Host Bus I/F

Parallel

Image data

I/F

Serial

Context I/F

WR

RD

D0-15

DMARQ

DMAAK

INTR

BUS16

PD0-31

PDRQ

PDAK

PDRD

PDWR

PRDY

PTIM

PXCK

PXCKO

SVID

RVID

CX0-11

PEUPE

SPIX

RPIX

XCLK

XWAIT

XRDY

XTIM

I

I

I

I

I

I

IO

O

I

O

I

IO

O

I

I

I

O

I

I

O

I

O

I

I

I

O

O

I

O

I

BUF

S

H/W reset signal

Chip select signal

Internal register address select signal

High-order(D8-15)access signal

S

Write strobe signal

S

Read strobe signal

8

I/O data signal (D0-7 used on 8-bit bus)

2

Code data DMA request signal

US

Code data DMA acknowledge signal

2

Interrupt request signal

U

8-bit bus (D0-7)and 16-bit bus(D0-15)function select bus.

U2

Parallel image I/O bus (PD0-15 used on 16-bit bus)

2

Image data DMA request signal

US

Image data DMA acknowledge signal

US

Image data read strobe signal

US

Image data write strobe signal

2

Image data 1-line I/O start ready signal

US

Image data 1-line transfer section signal

US

Image data transfer clock signal

4

Image data transfer sync clock signal

U

Image data input signal

2

Image data output signal

U

Context input (CX0 can be fed back inside LSI) (=PD0-11)

U

PE RAM update enable (learning function ON/OFF) (=PD15)

U

Coded image data input signal (=SVID)

2

Decoded image data output signal (=RVID)

4

Context data transfer clock signal

US

Context data transfer wait signal

2

Context data 1-stripe I/O start ready signal (=PRDY)

US

Context data 1-stripe transfer section signal (=PTIM)

MCLK

Others

Notes:Most of the context I/F signals are used in conjunction with the image data I/F signals.

∗ The input buffers of the input terminals (I and IO) are at TTL level.

Options are as follows.

(U:with pull-up resistors,D:with pull-down resistors,S:Schmitt trigger)

∗ Numbers (2,4,8) of the BUF column of the output terminals (O and IO) indicate current value. (one of 2,4,or 8mA)

TEST0-1

Vcc/GND

I

I

–

Master clock input signal

DS

Test signal (should be connected to GND when normally used).

–

Power supply (+5V)/ground

11. REGISTER CONFIGURATION

11. 1 List of registers

Address Register Name R/W Description

• LSI H/W reset

• Coding/decoding/image data through mode selection

• Context selection(internal context/external context)

0

1

2

System setting

Parameter setting

Command

R/W

R/W

W

• Byte swap ON/OFF of coded/image data on host bus

• Bit swap ON/OFF of coded/image data on host bus

• Image data I/O I/F(parallel I/F,serial I/F)

• Image data bus bit width selection(32bits/16bits)

• Template selection (2-line/3-line template)

• Setting of AT pixel position (up to 127)(IF O is set,AT becomes

non-existent (default position))

• Latch input/through input selection in external context input mode

• Context table RAM initialization command

• Coding (decoding,through) start/end command

• Start/stop command for R/W of context table RAM

• Selection of temporary stop and terminating end

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

2

3

4,5

6,7

8,9

A,B

A,B

C

C

Status

Interrupt enable setting

Pixel count setting

Line count setting

Processed line count

Data write buffer

Data read buffer

Marker code setting

Marker code read

R

R/W

R/W

R/W

R

W

R

W

R

• Processing status (in process/end of processing)

• Coded data read/write ready (ready/busy)

• Marker code detection (SDNORM,SDRST,ABORT,others)

• Interrupt request status

• SC counter over flow

• Processing mode (stop temporary/terminating end)

• Interrupt enable setting correspondence to each of bits positions of

status register

• Setting the number of pixels on one line (in multiples of 16or32,up to

10240 pixels)

• Setting the number of lines to be coded/decoded(up to 65535 lines)

• Setting the number of coded/decoded lines (up to 65535 lines)

• Buffer for writing coded data/image data/context table RAM data from

MPU into LSI (DMA transferable)(RAM address is automatically

incremented each time data is written.)

• Buffer for reading coded data/image data/context table RAM data from

LSI into MPU (DMA transferable)(RAM address is automatically

incremented each time data is read).

• Setting a terminal marker code in coding (SDNORM/SDRST)

• Reading a marker code in decoding (SDNORM,SDRST,ABORT,others)

• Reduction in coding (1/2 reduction in horizontal and vertical directions,

horizontal OR processing)

D

Notes:When the 8bit bus is used for the data read/write buffer,use Address A only.

Scaling

Incase of the 16-bit buffer,only the word access is possible.

(The byte access is not possible).

R/W

• Magnification during decoding ( × 2 lengthwise and width)

• Select throwing away the leading 1byte of the coded data read when

decoding

• Selecting the typical prediction

• Selection of prohibiting line memory initialization

11. 2 Description of Registers

(1) System Set Up Register (W/R) (address : 0)

d0(HR) : H/W reset (0:Active, 1:Reset state)

To make a H/W reset ,set this bit to 1 then to 0.

Reset initializes the entire LSI including the group of register and Line Memory. However, the context table RAM is not

initialized.

d1-2(MOD) :This sets up the operating modes.

(d2=0,d1=0:coding, d2=1,d1=0:iage data through (Iage data I/F→Host I/F),

d2=0,d1=1:decoding, d2=1,d1=1:Iage data through (Host I/F→Iage data I/F))

d3(CX) :Context select (0:internal context, 1:Image data through)

NOTE:The internal context should be selected when the image data through mode is used.

When initializing or processing R/W of the Context table RAM and coding /decoding,

This bit must be set the same.(Because RAM configration changes depending on internal/external modes.)

d4(BS) :Select data bit swap of the host bus. (0:MSB(d7)first, 1:LSB(d0)first)

d5(BX) :Select data byte swap of the host bus.(0:Lower byte(A)first, 1:Upper byte(B)first)

NOTE:BX is valid only when the host bus is 16 bits.(BUS16=HIGH)

Table 11. 2 The coed data and image data line-up on the Host bus

Bus width

BUS16

1

16bit

0

8bit

d6(PI) :Selects the image data I/O I/F (0:Serial /F, 1:ParallelI/F)

d7(PB) :Selects the bit width of the iamge data bus (0:32bit bus (PD0-31), 1:16bit bus(PD0-15))

Table 11. 3 The image data line-up on the image data parallel bus

bit width

PB=0

PB=1

Swap

BX BS

0

0

0

1

1

0

1

1

––0

1

PD31 • • • • • • PD16

p0 • • • • • • p15

Upper address(B) Lower address(A)

d15 • • • • • • d8

b8 • • • • • • b15

b15 • • • • • • b8

b0 • • • • • • b7

b7 • • • • • • b0

–

–

PD15 • • • • • • PD0

p16 • • • • • • p31

–

p0 • • • • • • p15

d7 • • • • • • d0

b0 • • • • • • b7

b7 • • • • • • b0

b8 • • • • • • b15

b15 • • • • • • b8

b0 • • • • • • b7

b7 • • • • • • b0

SYS_REG :

p0 is the image data on the left-hand on the screen.

p31is the image data on the right-hand on the screen.

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

d7(MSB) d0

PB PI BX BS CX MOD HR

b0 is the first coded data on the time

series/the left-hand side image data on the

screen.

b15 is the last coded data on the time

series/the right-hand image data on the

screen.

(2) Parameter Setup Register (W/R) (Address:1)

d7

1) External Context Mode

d6 (LC) :Condition of taking in the input from the external context are selected.

(0:through onput, 1:latch input)

When this bit is set to 1,the CX0 to CX11 of the context input is latched once using the transfer clock.("XCLK")

d7 (C0) : When this bit is set to 1,CX0 is selected.

(0:CX0 external input, 1:CX0 internal feedback)

2) Internal Context Mode

d0-4 (AT<0>-AT<4>) :ATpixel position Lower 5bits. (See Fig.9. 2)

d5 (TM) :Template select (0:3line template, 1:2line template)

d6 -7(AT<5>-AT<6>) :AT pixel position upper 2bits (the 6th and 7th bits)

d7

Example : 3line template,AT=4 :

2line template,AT=48 :

NOTE) The AT pixel position at time of the internal context mode is set up by using all the AT<6:0> (0 to 127)

When the default position (when the AT pixels are not used) is used, At is set to 0.

When the 2-line templsate is used, AT should not be set to 1 to 4. In case of the 3-line template,

AT=1 to 2 is not allowed.

0 0 0 0 0 1 0 0

d7

0 1 1 1 0 0 0 0

d4

d4

PARA_REG :

PARA_REG :

d0

d0

C0 LC 0 0

d5

d6

d7

AT TM AT

d4

d4

d0

d0

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

(3) Command Register (W) (address : 2)

CMD_REG :

d0 (IC) :This command starts initialization of Context Table RAM (1:start initialization)

When this bit goes 1,the Context Rable RAM initialization starts.This bit returns to 0 automatically when the initialization is

completed.

d1 (JC) :Processing (Coding/Decoding/Through) start /end command (1:start processing, 0:end processing)

When this bit goes 1,processing(coding/decoding/through)starts.

This bit returns to 0 automatically when processing of the number of set lines is finished during the selection of end of

termination.

And if this JC bit is made 0 and inputting the image data is stopped during the coding porocess,the coding is stopped (flushed)

even if the set lines are not filled.Mreover,if this bit made 0 during decoding and no more coded data is coming in,it is

assumed that the '00'of the coded data came in and the preset lines have been processed.However,in case of the multistriped coding ,processing should not end by making this bit "0" except in case of last stripe.

d2 (RC) :This command starts and stops R/W of Context Table RAM. (1:R/W start, 0:R/W end)

The Context Table RAM is read out or written in by making this bit to "1".

When reading/writing is finished,this bit must have "0" on it.

d3 (JP) :This selectd temporary stop and the end of termination of coding/decoding/through processing.

(1:Temporary stop selected, 0:End of processing selected)

When the process start command d1(JC)is issued by making this JP bit to 1,the processing stops temporarily when the set

number of lines have been processed. Then, if the process satart command d1(JC) is issued,processing restarts.(See 11.4(3))

d7

d3

0 JP RC JC IC

d0

(4) Status Register (R) (address : 2)

d0 (JS) :This register indicates the status of processing in initialization,coding,decoding and through.

(0:Processing in progress(being initialized),1:End of processing)

This JS bit goes to "1"when the initialization is completed as RAM initialization command is issued.

(IC=1) This JS bit goes to "1"when all coded data has been read out during coding in case when the process start command

of the processing end is issued.(JC=1,JP=0) This JS bit goes to "1" when reading all the image data has been completed

during the image data through and decoding. Moreover,this JS bit stays "0" even when the set number of lines have been

processed when the command to start processing the process which has been stopped temporarily has been issued (JC=1,

JP=1). (However,interrupts are issued during the temporary stops.)

d1 (DS) :This is used for read and write ready of coded data.(In case of the through mode,this is used for the image data.)(1:Ready,

0:Reading no possible)

It is possible to do R/W of data by the way of the data write/read buffer when this bit is 1.

d2 (MS) :This detects the marker code during decoding.(0:not detected, 1:detected)

This bit goes to "1" if any marker is detected during decoding.

d3 (IS) :This indicates the status of the interrupt request.(0:No request, 1:Request exists)

d4(SC) :This shows the SC count over error during coding.(0:Normal, 1:There is a SC counter overflow)

NOTE:The SC counter counts the "FF" data bytes which occur duriing coding.Coding continues even when the SC counter

overflows.this means correct coding data will not be outputted.(Coding error)

d5(PS) :processing modes (Stopped temporary /End of trailer)(1:Process temporaryily stopped, 0:End of processing)

This PS bit corresponds to the temporary stop and end of processing of d3 bit (JP) processing of the command register.

STAT_REG :

d7

d5

0 PS SC IS MS DS JS

d0

MITSUBISHI ICs (LSI)

M65761FP

QM-CODER

(5) Interrupt Enable Register (W/R) (address : 3)

IENB_REG :

d0 (JE) :Temporary stop/End of trailer interrupt of initialization/coding/decoding/through .

(0:interrupt mask, 1:interrupt enable)

d1 (DE) :Coded data(Image data)read out/write in ready interrupt.

(0:interrupt mask, 1:interrupt enable)

d2 (ME) :Marker code detection interrupt during decoding. (0:interrupt mask, 1:interrupt enable)

d3 (SE) :SC count over error interrupt during coding.(0:interrupt mask, 1:interrupt enable))

This bit sets to 1 beforehand, it occurs the interruption when the SC counter is overflow during coding. Processing of coding

continues, but the correct coded data is not output.

NOTE:Bits,d0-d3,are for interrupt enable of bits d0-d2 and d4 of the Status Register.

The interrupt request signal(INTR) is asserted when any one of the status bit set in the interrupt enable (D0(JE)generates

interrupts even during the temporary stop),the status goes to "0" due to H/W reset or the INTR signal is negated when the

interrupt mask causes factors for interrupt to be lost. Moreever, the status register will not be cleared by the generation of

interrupts or the R/W of the interrupt enable register.

d7 (MP) :This specified the marker code detection time halt. (0:Continue/restart, 1:temporary halt)

Decoding will stop temporarily when the marker code is detected if this MP bit is preset to "1"during decoding. (it occures

interruption when the marker code is detected, if the ME bit preset to "1".)

if decoding is not completed during the temporary halt,it is possible to reset the line number setup

register. Next, if this MP bit is set to "0",decoding is restarted(Decoding continues to the line number set.)

d7

MP 0 SE ME DE JE

d3

d0

(6) Register used to set the number of pixels (W/R)

(address:4)

(address:5)

d0-7 (PEL_L) :Number of pixels/line is set (Lower byte)

d0-5 (PEL_H):Number of pixels/line is set (Upper byte)

It is possible to set up 8192 pixels maximum when 3-line template is used. It is used to set up 10240 pixels maximum when 2-line

template is used. The number of pixels actually coded (or decoded)should be set when reducing(or expanding).When the image

bus uses 16bits(or 32bits)in parallel I/F,multiples of 16 (or 32) should be set. In case of serial I/F,multiples of 8 should be used.

(7) Line Number Setting Register (W/R)

(Address:6)

(Address:7)

d0-7 (LSET_L):This sets the number of lines to be processed. (Lower bytes)

(1 to 65535, 0 line not used)

d0-7 (LSET_H):This sets the number of lines to be processed. (Upper bytes)

When reducing(magnification)the actual number of lines to be coded (decoded) should be set.The number of lines (relative number of

lines)from the process start command to be issued from now the immediately following temporary stop/end of trailer should be set. This

register should be set to the value specified before the process star command is issued. Moreover,this register can be rewritten during

processing as long as the following conditions are met:

• If the maximum value, (65535), is set before the process start command is issued,it can be reset once during processing.

• If a value other than maximum value (65535) is set before the process start command is issued and if resetting becomes necessary

during processing,the maximum value (65535) has to be reset once and desired value should the reset.

PEL_REG_L :

PEL_REG_H :

LSET_REG_L :

LSET_REG_H :

d7

PEL_L

d7 d0

d7

d5

PEL_H0

LSET_L

LSET_H

d0

d0

Loading...

Loading...