Mitsubishi M65664FP Datasheet

M65664FP

MITSUBISHI DIGITAL TV ICs

PICTURE-IN-PICTURE

* Internal V-chip data slicer (for sub-picture)

* Vertical filter for sub-picture ( Y signal )

* Single sub-picture ( selectable picture size : 1/9 , 1/16 )

* Sub-picture processing specification ( 1/9 , 1/16 size) :

Quantization bits Y, B-Y, R-Y : 7 bits

Horizontal sampling 229 pixels (Y), 57 pixels (B-Y, R-Y)

Vertical lines 69/ 52 lines

* Frame ( sub-picture ) on/off

* Built-in analog circuits :

One 8-bit A/D converter (for sub-picture signal)

Three 8-bit D/A converters (for Y, U and V of sub-picture)

Sync-tip-clamp, VCXO ... etc..

* IIC BUS control ( parallel/serial control) :

PIP on/off , Frame on/off ( programmable luma level),

Sub-picture size ( 1/9, 1/16 ),

PIP position ( free position ), Picture freeze ,

Y delay adjustment, Chroma level, Tint, Black level,

Contrast ...etc..

NTSC, PAL-M, PAL-N color TV

Supply voltage range ------------------------ 3.2 ~ 3.5 V

Operating frequency ----------------------- 14.32 MHz

Operating temperature ------------------------ 0 ~ 70 deg.

Input voltage (CMOS interface) "H" ----- VDD x 0.7 ~ VDD V

"L" ----- 0 ~ VDD x 0.3 V

Output current ( output buffer ) ------------ 4 mA ( MAX )

Output load capacitance ---------------------- 20 pF ( MAX ) *1

Circuit current ----------------------------------- - mA

NOTICE:

Connect a 0.1µF or larger capacitor between VDD and VSS pins.

*1 : Include pin capacitance ( 7 pF )

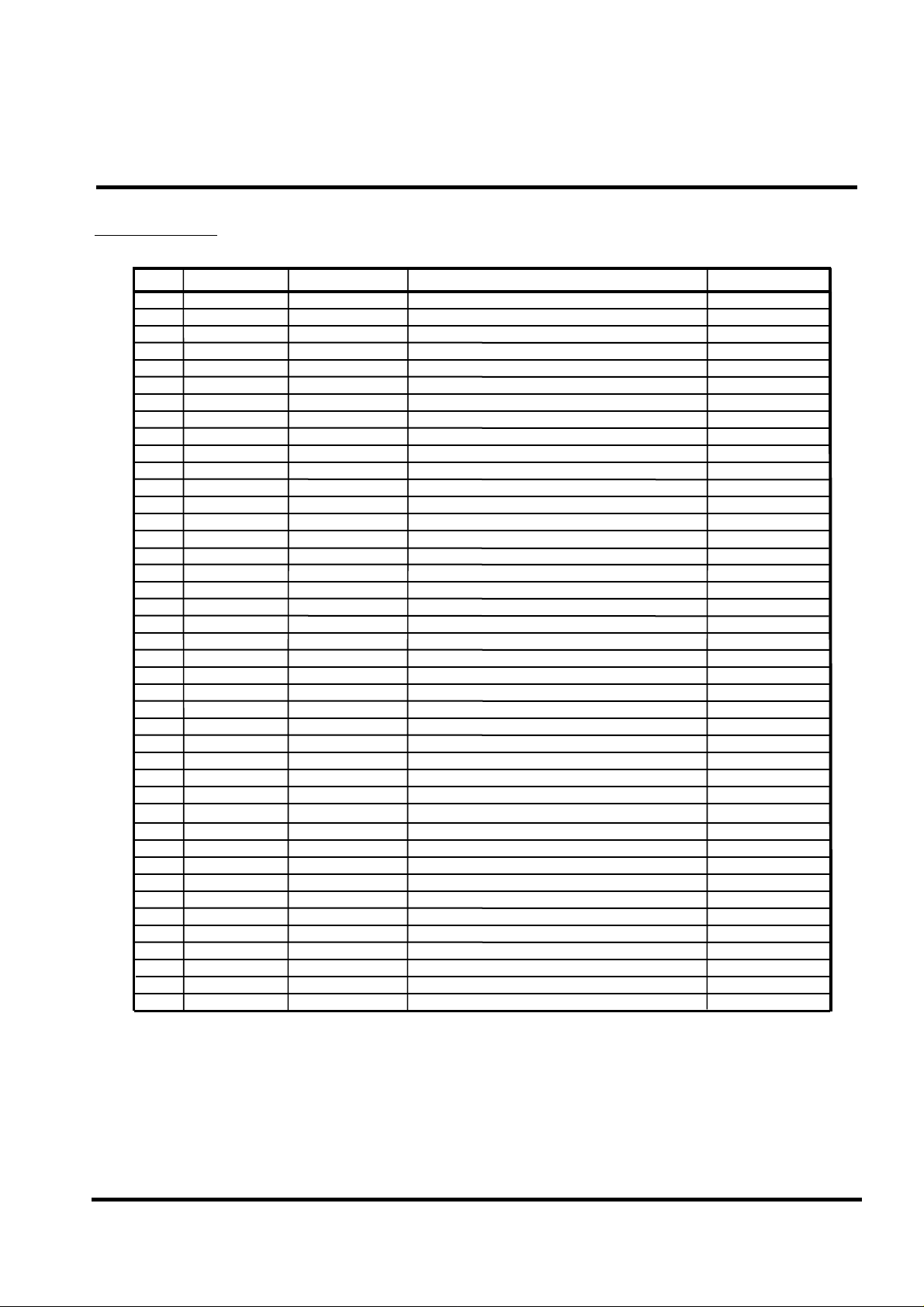

PIN CONFIGURATION (TOP VIEW)

AVss(ad)

Vrb

Vrt

Vin(ad)

Vin(Sync sepa.)

AVdd(ad)

AVdd(vcxo)

BIAS

Filter

X'tal(NT)

X'tal(P-M)

X'tal(P-N)

AVss(vcxo)

VDHDTESTEN

VOUT

ADJ_Vsub

UOUT

ADJ_Ysub

YOUT

Vdd(da)

AVss(ana)

CSYNCS

MCK

DVss

DVdd

RESET

SWMG

TEST6

TEST5

SDATA

ACK

FSC

BGPM

SCK

DVss

DVdd

SWM

SCLK

BGPS

ADJ_Usub

SIGNAL PROCESSING

DESCRIPTION

The M65664FP is a PIP (Picture in Picture) signal

processing LSI, whose sub-picture input is composite

signal for NTSC, PAL-M, and PAL-N. The built-in field

memory (168k-bit RAM) , V-chip data slicer and analog

circuitries lead the high quality PIP system low cost and

small size.

FEATURES

APPLICATION

RECOMMENDED OPERATING CONDITIONS

Outline 0.8mm pitch 42 Pin SOP Package

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

1

M65664FP

MITSUBISHI DIGITAL TV ICs

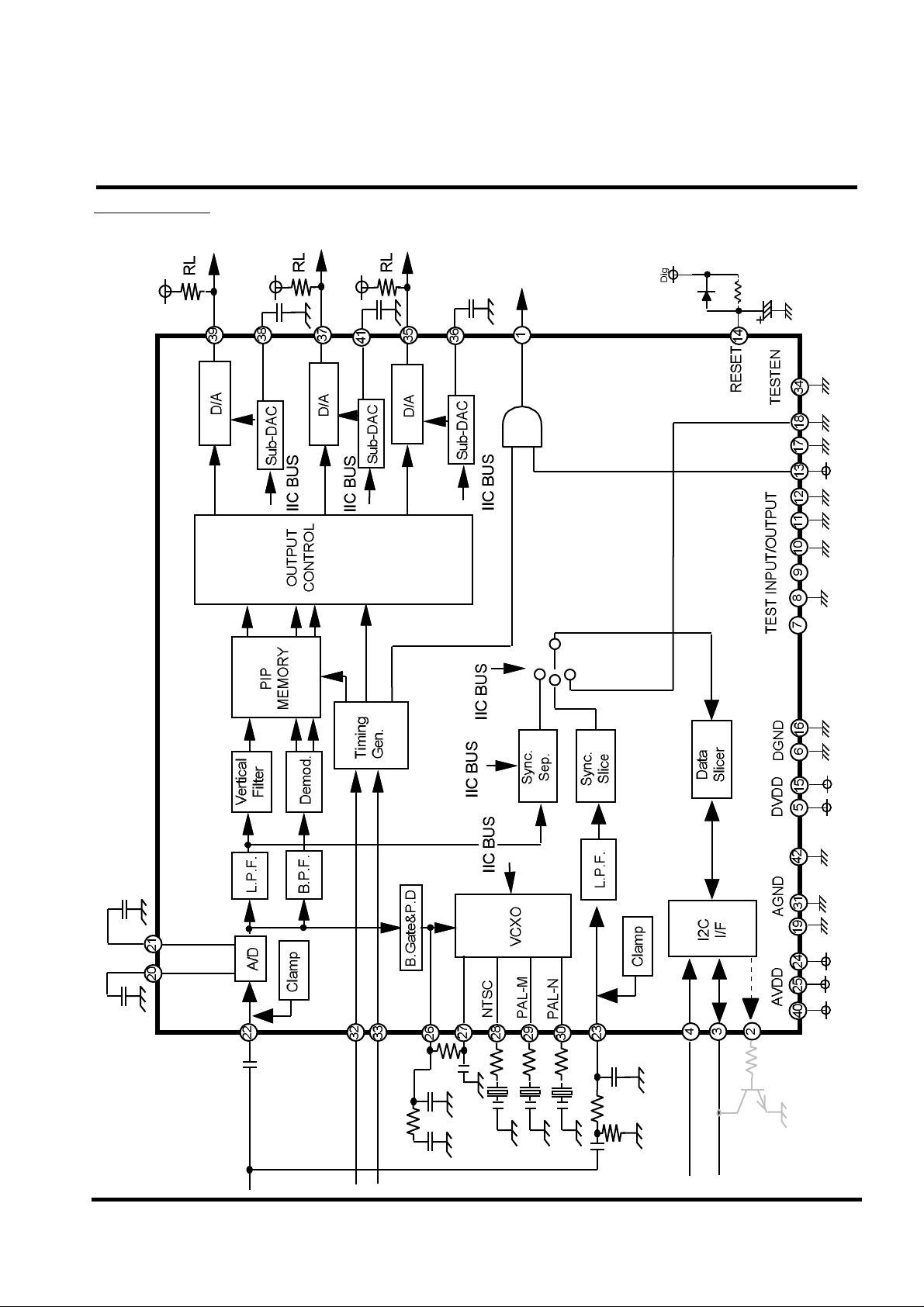

BLOCK DIAGRAM

PICTURE-IN-PICTURE

SIGNAL PROCESSING

Y OUTPUT

U OUTPUT

V OUTPUT

PIP SW

Sub picture

Main HD

Main VD

SCL

SDA

2

M65664FP

MITSUBISHI DIGITAL TV ICs

PICTURE-IN-PICTURE

SIGNAL PROCESSING

ABSOLUTE MAXIMUM RATINGS

Symbol

V

DD3

V

I

VI

V

O

I

O

P

D

Topr

Tstg

Parameter

Supply voltage (3.3V)

Input voltage(except 5V input)

Input voltage(5V input)

Output voltage

Output current (*1)

Power dissipation

Operating temperature

Storage temperature

Conditions

(*1) Output current per output terminal. But Pd limits all current.

TYPICAL CHARACTERISTICS

Limits

Min. Max.

-0.3 4.2

-0.3 V

DD3+0.3

-0.3

-0.3 V

I

OH = -4

-

DD3+0.3

IOL = 4

1200

-10

-50

5.25

70

125

(VSS=0V)

Unit

V

V

V

V

mA

mW

deg.

deg.

THERMAL DERATING (MAXIMUM RATING)

2000

1600

1200

800

400

0

0 25 50 75 100 125

AMBIENT TEMPERATURE Ta (deg.)

70

3

M65664FP

MITSUBISHI DIGITAL TV ICs

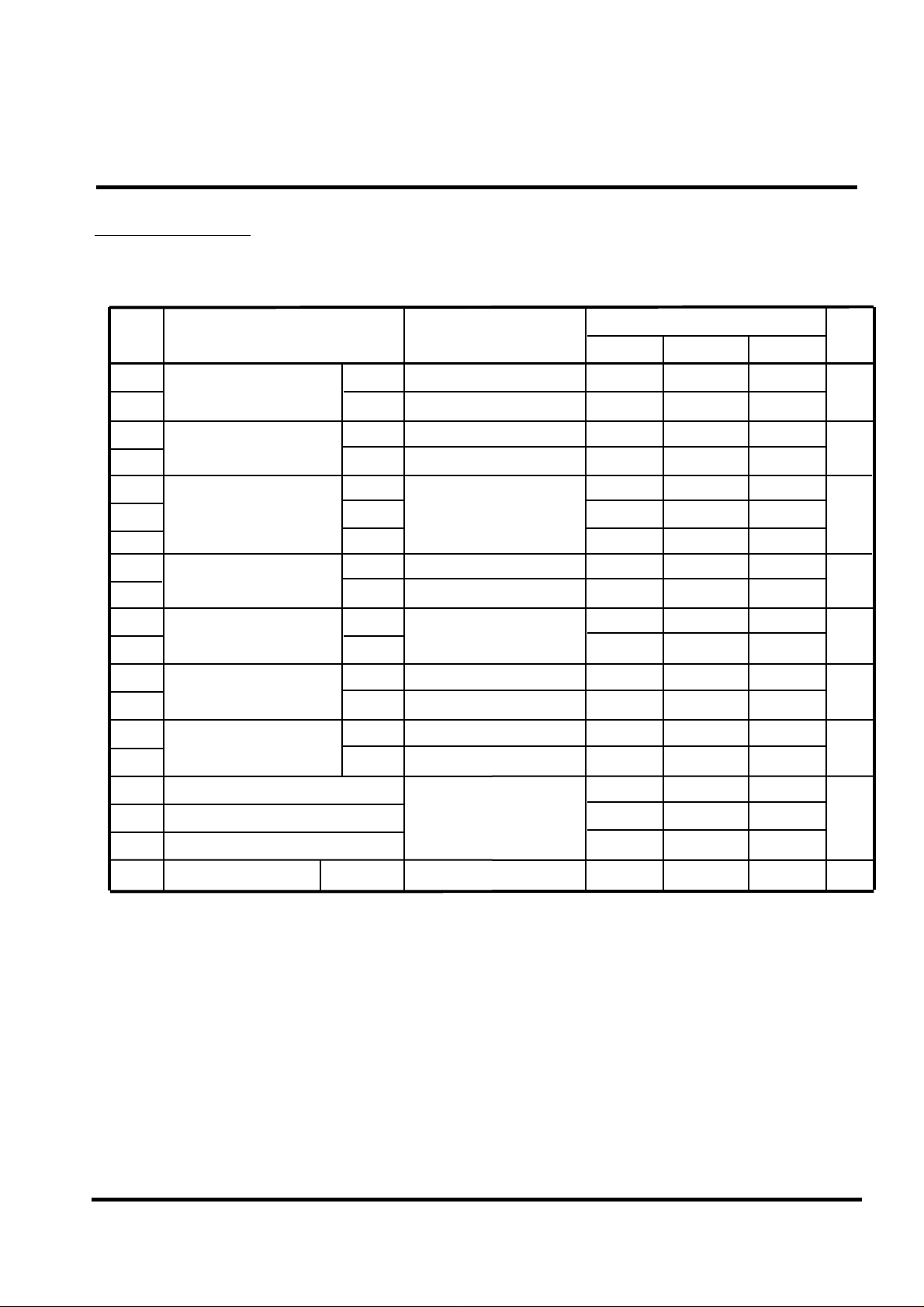

DC CHARACTERISTICS

PICTURE-IN-PICTURE

SIGNAL PROCESSING

Symbol

VIL Input voltage

V

IIH

I

VT-

V

V

IIH

I

V

V

I

I

I

IL

IL

OL

OH

OZL

(3.3V CMOS interface)

IH

Input current

(3.3V CMOS interface)

Input voltage schmitt -

(5.0V CMOS interface)

T+

H

Input current

(5.0V CMOS interface)

OL

CMOS output voltage

OH

CMOS output current

Output leakage current

IOZH

I

C

C

C

IDD

Input pin capacitance

O

Output pin capacitance f = 1MHz, VDD = 0V

IO

Bidirectional pin capacitance

Operating current 3.3V supply

(Ta = 25 deg. unless otherwise noted)

Parameter

DD = 2.7V

V

L

H V

L

DD = 3.6V

V

DD = 3.6V, VI = 0V

H VDD = 3.6V, VI = 3.6V

+

V

DD = 3.3V 1.4

Hysteresis

L

VDD = 3.6V, VI = 0V -100

V

H

DD = 3.6V, VI = 3.6V

L

V

H

L

V

DD = 3.0V, VOL = 0.4V

H

L

H

DD = 3.0V, VOH = 2.6V

V

V

DD = 3.6V, VO = 0V

V

DD = 3.6V, VO = 3.6V

Condition

DD = 3.3V, |IO| = 1µA

Limits

Min. Typ. Max.

0

2.52

-10

-10

0.8

0.3

-10

-

3.25

4

-

-10

-10

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

140

0.81

3.6

10

10

1.65

2.7

1.2

10

10

0.05

-

-

-4

10

10

7

7

7

15

15

15

-

(VSS=0V)

Unit

V

µA

V

µA

V

mA

µA

pF

mA

4

M65664FP

MITSUBISHI DIGITAL TV ICs

PIN DESCRIPTION

No.

PICTURE-IN-PICTURE

SIGNAL PROCESSING

Pin

SWM

1

ACK

2

SDATA

3

SCLK

4

DVdd1

5

DVss1

6

BGPS

7

SCK

8

BGPM

9

FSC

10

11

TEST5

TEST6

12

SWMG

13

RESET

14

DVdd2

15

16

DVss2

MCK

17

CSYNCS

18

19

AVss (ADC)

20

VRB

21

VRT

22

VIN (ADC)

23

VIN (Sync Sep.)

24

AVdd (ADC)

25

AVdd (VCXO)

FILTER

26

27

BIAS

X'tal (NTSC)

28

29

X'tal (PAL-M)

X'tal (PAL-N)

30

31

AVss (VCXO)

32

HD

33

VD

34

TESTEN

35

VOUT

36

ADJ_Vsub

37

UOUT

38

ADJ_Ysub

39

YOUT

40

AVdd (DAC)

41

ADJ_Usub

42

AVss (sub)

Name I/O Function

CMOS output

CMOS output

CMOS I/O(5V)*1

CMOS input(5V)*1

Digital Vdd

Digital Vss

CMOS output

CMOS input

CMOS output

CMOS input

CMOS input

CMOS input

CMOS input

CMOS input

Digital Vdd

Digital Vss

CMOS input

CMOS input

Analog Vss

Analog

Analog

Analog

Analog

Analog Vdd

Analog Vdd

Analog

Analog

Analog

Analog

Analog

Analog Vss

CMOS input(5V)*1

CMOS input(5V)*1

CMOS input

Analog

Analog

Analog

Analog

Analog

Analog Vdd

Analog

Analog Vss

PIP switch output

I2C SDA output

I2C SDA input/output

I2C SCL input

Vdd for digital part

Vss for digital part

Test output

Test input

Test output

Test input

Test input

Test input

Power on reset input

Vdd for digital part

Vss for digital part

Test input

Sub picture external C-sync input

Vss for internal ADC

Low level reference voltage output of ADC

High level reference voltage output of ADC

Sub picture input of ADC

Sub picture input of sync sep. for sub picture

Vdd for internal ADC

Vdd for VCXO

VCXO filter voltage connection

VXCO bias voltage connection

X'tal of NTSC connection

X'tal of PAL-M connection

X'tal of PAL-N connection

Vss for VCXO

Main picture HD input

MAIN picture VD input

Test input

Sub picture V or B output

Referece voltage connection of DAC of V

Sub picture U or G output

Referece voltage connection of DAC of Y

Sub picture Y or R output

Vdd for DAC

Referece voltage connection of DAC of U

Vss for substrate

(for high load SDA line use only)

Remarks

connect to GND

connect to GND

connect to GND

connect to GND

connect to Vdd

connect to GND

connect to GND

*1 ) (5V)means 5V I/F torelant

5

Loading...

Loading...