M65533FP

MITSUBISHI Analog ICs

16

3-0

1

4567891011121314151617181920454647484950515253545556575859606162636480252627282930313233343536373839406566676869707172737475767778792122232441424344

3ch 8-bit 80MHz A/D Converters

General Description

The M65533FP is a CMOS 3ch 8-bit 80MHz analog-to-digital converter by sub-ranging

architecture for high speed video processing. It can be realized 80MHz operation by using

2 ADCs in parallel. And it has PLL circuit generate a stable clock locked to sync signal.

It is a type of "AC" connection with internal clamp circuit and variable input range.

Features

• 3ch 8-bit high speed A-D converters

• Maximum conversion rate 80 MSPS(min.)

• Analog input Level 1.0V(Typ) : 0.5 -1.5 V

• Digital input TTL compatible [ Vinth=1.4V ]

• Digital output VoH=0.7XVcc , VoL=0.3XVcc [ Io=4mA ]

• Low power dissipation 700mW [ CL=10pF ]

• Package 80 pin QFP package, 0.80mm lead pitch

[ PKG size(without lead) =14mm x 20mm ]

• Small input capacitance 10 pF

• Built-in Reference Voltag Vref(+)=1.5V+150/-330mV(*) Vref(-)=0.5V

• Built-in Clamp circuit Vclamp=0.5V+/-250mV(*)

(*)Controllable by IIC BUS

Applications

• LCD monitor

• High speed video processing

Recommended Operating Condition

• Supply voltage range (typ.=3.3V) 3.15 to 3.45 V

• Supply voltage range (typ.=5.0V) 4.75 to 5.25 V for 5V I/F only

Pin configuration(Top View) Shown on next page

M65533FP

#XXXXXX

Ver 3.0 '99- 5- 31

1 2 3

MITSUBISHI

( / )

M65533FP

16

3-0

RCIN

NC

BCIN

NC

GCIN

NC

DVDDG(OUT)

DoR5

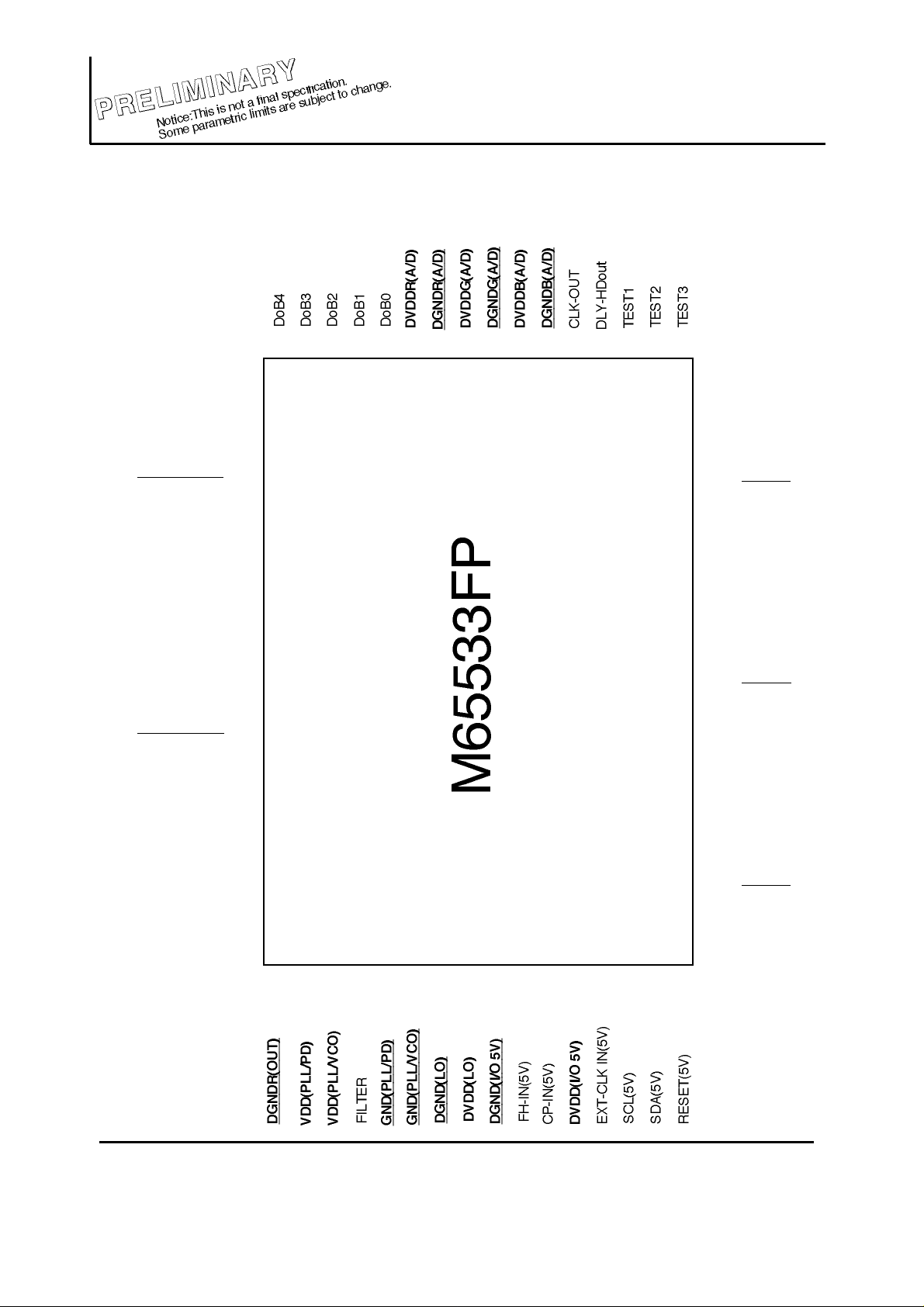

Pin Configuration

2

DoR3

DoR2

DoR1

DoR0

DoG6

DoG5

DoG4

DoG3

DoG2

DoG1

DoG0

DoB5

41

DoB6

DoB7

DVDDB(OUT)

DGNDB(OUT)

DoG7

DGNDG(OUT)

DoR4

DoR6

DoR7

DVDDR(OUT)

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

3ch 8-bit 80MHz A/D Converters

34353637383940 25272930313233 2628

71706968676665 80787675747372 7977

MITSUBISHI Analog ICs

BNB

24

23

BVRT

22

BVRM

21

AVDDB

20

AGNDB

19

18

17

BVRB

16

GNB

15

GVRT

14

GVRM

13

AVDDG

12

AGNDG

11

10

9

GVRB

8

RNB

7

RVRT

6

RVRM

5

AVDDR

4

AGNDR

3

2

RVRB

1

MITSUBISHI

( / )

M65533FP

16

3-0

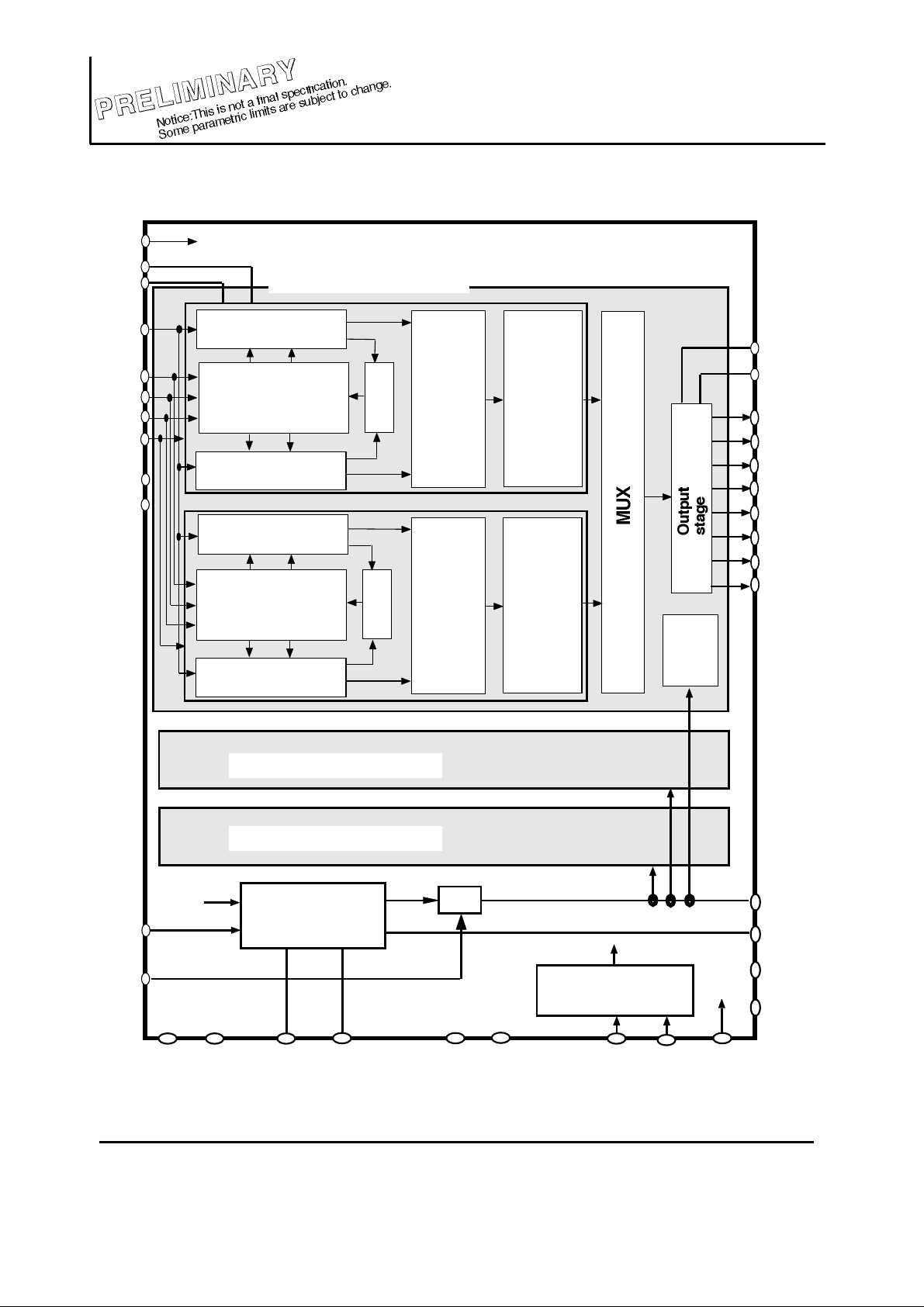

Block

Diagram

Comparators(2)

1st ADC ( R signal )

CLK-OUT

FILTER

AVDDR

3

IIC BUS

SDA

SCL

EXT-CLK IN

VDD(PLL)

GND(PLL)

SW

DVDD(I/O 5)

DGND(I/O 5)

DVDD(LO)

DGND(LO)

Test1-3

CP-IN

DLY-HDout

DoR0

DoR1

DoR2

DoR3

DoR4

DoR5

DoR6

DoR7

DVDDR(A/D)

MITSUBISHI Analog ICs

3ch 8-bit 80MHz A/D Converters

RC IN

RVRT

RVRM

RVRB

RNB

AGNDR

DGNDR

(A/D)

Comparators(1)

Ladder

Resistors

Comparators(2)

Comparators(1)

Ladder

Resistors

SW

SW

2nd ADC ( G signal )

MUX

&

DeMU

X

MUX

&

DeMU

X

Delay

&

Error

Correctio

n

Delay

&

Error

Correcti

on

DVDDR(out)

DGNDR(out)

Timing

Gen.

3rd ADC ( B signal )

fFBin

FH-IN

fH

PLL

(note) Pins for ADC is described for only R signal

fCLK

MITSUBISHI

RESET

( / )

M65533FP

MITSUBISHI Analog ICs

16

3-0

4

---------

-

3ch 8-bit 80MHz A/D Converters

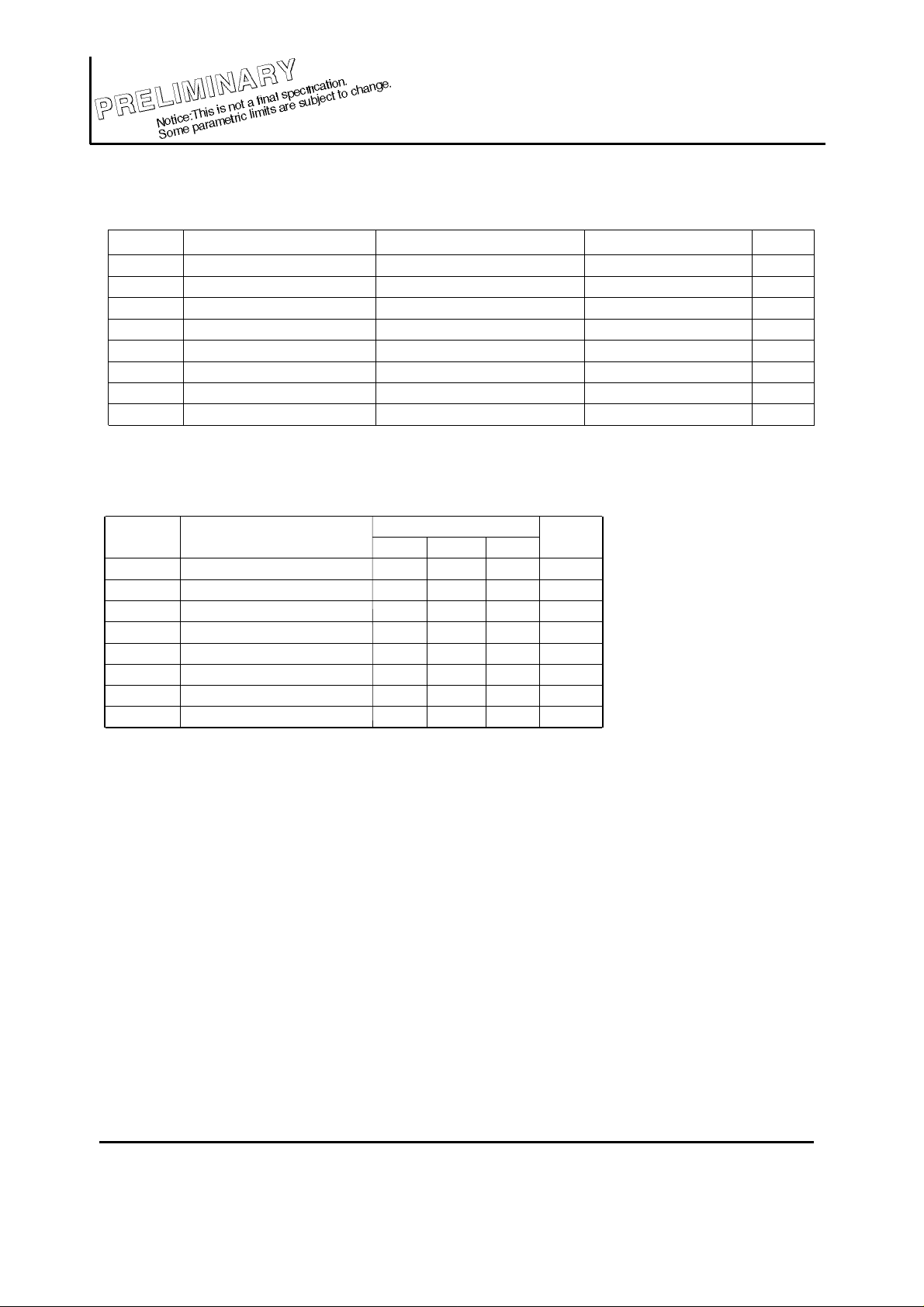

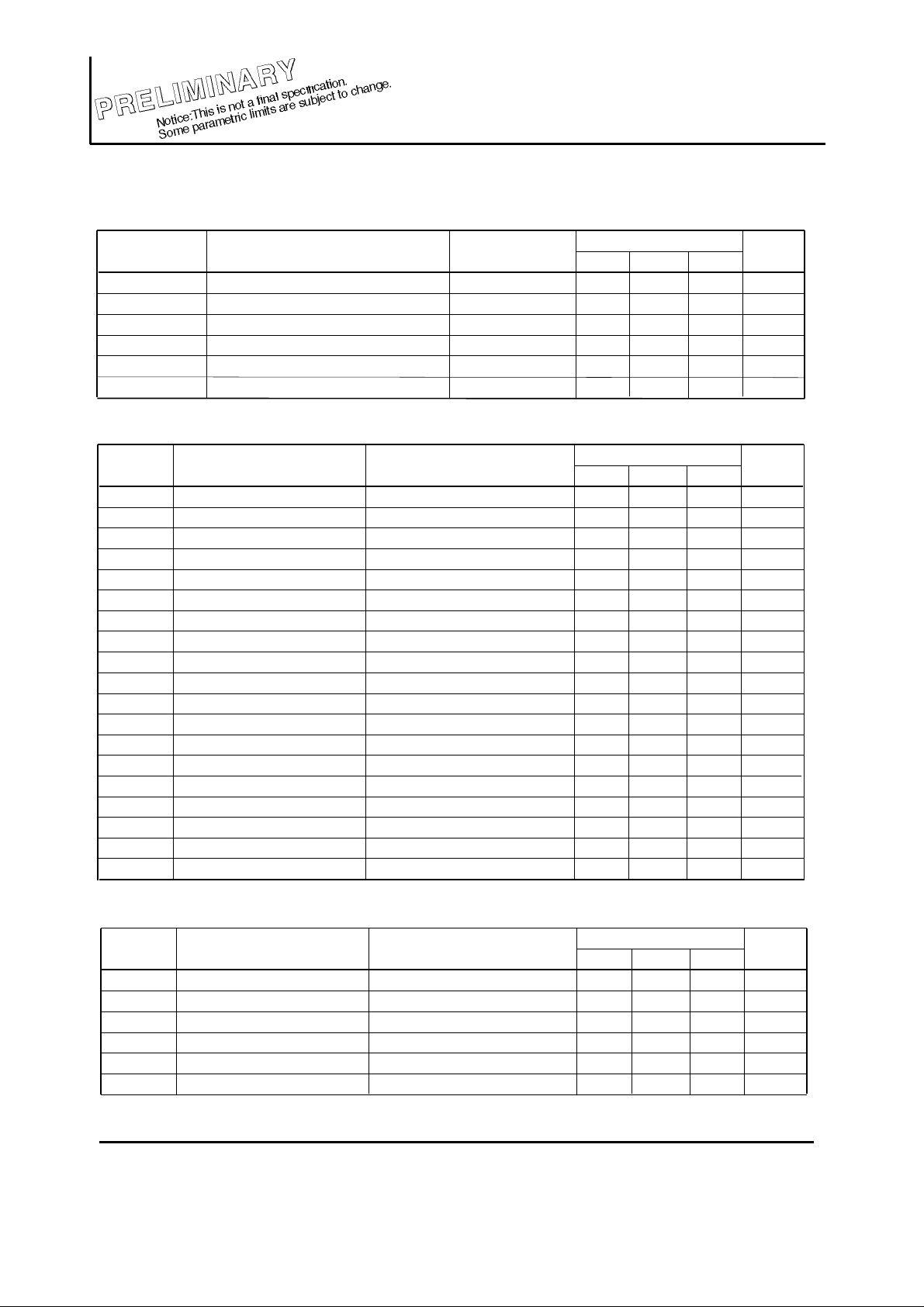

Absolute Maximum Ratings (Ta = 25°C, unless otherwise noted.)

Symbol

DVdd

AVdd

Vdd((I/O) I/O Supply Voltage

VID

IOUT

Pd

Topr Operating Temperature

Tstg

Parameter

Digital Supply Voltage

Analog Supply Voltage

Digital Input Voltage

Analog Output Current

Power Dissipation

Storage Temperature

In current measurement, (+) and (-) is corresponding to an inflow and an outflow current, respectively.

Condition

Ratings

0 to 4.0

0 to 4.0

0 to 6.0

0 to 4.0

-30 to 0

1600

0 to +70

-40 to +150

Unit

V

V

V

V

mA

mW

°C

°C

Recommended Operating Conditions (Ta = 25°C, unless otherwise noted.)

Symbol

Vdd

VIH

VIL

tWH

tWL

tsu

th

Parameter

Supply Voltage

Supply Voltage(I/O)

Digital Input Voltage (High)

Digital Input Voltage (Low)

Clock Pulse Width (High)

Clock Pulse Width (Low)

Set-up Time

Hold Time

Limits

Min. Typ.

3.15

4.75

2.4

6.25

6.25

3.30 3.45

5.0

0 0.8

5

5

Max.

5.25Vdd(I/O)

Vdd

Unit

V

V

V

V

ns

ns

ns

ns

MITSUBISHI

( / )

M65533FP

16

3-0

5

8

Electrical Characteristics

(Ta = 25°C, AVdd = DVdd = 3.30V, unless otherwise noted.)

(2) ADC Block

(3) PLL Block

(1) Overall

160

160

MITSUBISHI Analog ICs

3ch 8-bit 80MHz A/D Converters

Symbol

AIdd(AD R/G/B)

DIdd(AD R/G/G)

DIdd(I/O R/G/G)

DIdd(PLL)

DIdd(LO) Logic block Supply Current

DIdd(I/O 5)

AD(R/G/B) Analog Supply Current

AD(R/G/G) Digital Supply Current

I/O block Supply Current

PLL block Supply Current

5V I/O block Supply Current

Parameter

Symbol Parameter

Res

Vdd

NL

DNL

VOH

VOL

VinA

Cin

fCLK

Vref(+)

Vref(M)

Vref(-)

Rref

B.W

tpdLHnsOutput delay time(L->H)

tpdHL

tr

tf

Vclamp

Resolution

Supply Voltage

Integral Nonlinearity

Differential Nonlinearity

Digital output Voltage "H"

Digital output Voltage "L"

Analog input range

Input Capacitance

Max. Conversion Rate

Reference Voltgae "High"

Reference Voltgae "Middle"

Reference Resistor

Input Bandwidth

Output delay time(H->L)

Output rise time

Output fall time

Clamp Voltage

Vref(+)=1.5V, Vref(-)=0.5V

Vref(+)=1.5V, Vref(-)=0.5V

Changeable by IIC (16mV step)

-3dB input frequency

Changeable by IIC (16mV step)

Condition

For R/G/B signal

For R/G/B signal

For R/G/B signal

Condition

Min.

Min.

3.15 3.30

0.7xVdd

0

0.67

80

1.17

0.84

70

0.25

Limits

Typ.

tbf

tbf

tbf

tbf

tbf

tbf

Max.

Limits

Typ. Max.

3.45

± 1.0

± 1.0

Vdd

0.3xVdd

1.00

10

1.5

1.0

0.5

120

110

110

tbf

tbf

0.5

1.15

1.65

1.07

0.73

Unit

mA

mA

mA

mA

mA

mA

Unit

Bits

V

LSB

LSB

V

V

Vp-p

pF

MHz

V

V

VReference Voltgae "Low"

Ohms

MHz

ns

ns

ns

V

Symbol

fH

fVCO

jPLL

D.R(PLL)

Parameter

Horizontal frequency

VCO frequency

maximum jitter

PLL Divider Ratio

from 800 by 1 step

Condition

MITSUBISHI

Limits

Min. Typ.

10

20 80

800

60

0.5

1376

( / )

Max.

100

1.0

Unit

KHz

MHz

ns

-

Loading...

Loading...