MITSUBISHI <STD LINEAR ICs>

GENERAL PURPOSE C•MOS OP AMP(SINGLE/DUAL/QUAD)

M6255X Series

P

P

R

R

E

E

L

L

I

I

M

M

I

I

N

N

A

A

R

R

Y

Y

Notice:This is not a final specification.

Some parametric limits are subject to change.

DESCRIPTION

The M6255X is a single power supply system semiconductor

integrated circuit designed to be used for general-purpose

arithmetic amplifier of general electronic equipment for consumer

appliances.

This IC adopts C-MOS structure to achieve low power

consumption and is therefore optimum for the recent boom in

portable electronic equipment. The IC is also available for various

applications for its full swing in both input and output, though the IC

has a single power supply.

FEATURES

•Dissipation current………0.19/0.38/0.76mA<551/552/554> (TYP)

•Output wide……………………V

O=GND to VCC (VIN=GND to VCC)

•Slew rate…………………………………………SR=1.2V/µS (TYP)

•Small size SSOP package. (551GP/ 552GP)

APPLICATION

Various types of arithmetic circuits for ink jet printer and other

general electronic equipment

RECOMMENDED OPERATING CONDITIONS

Supply voltage………………………………………………………5V

( 1 / 3 )

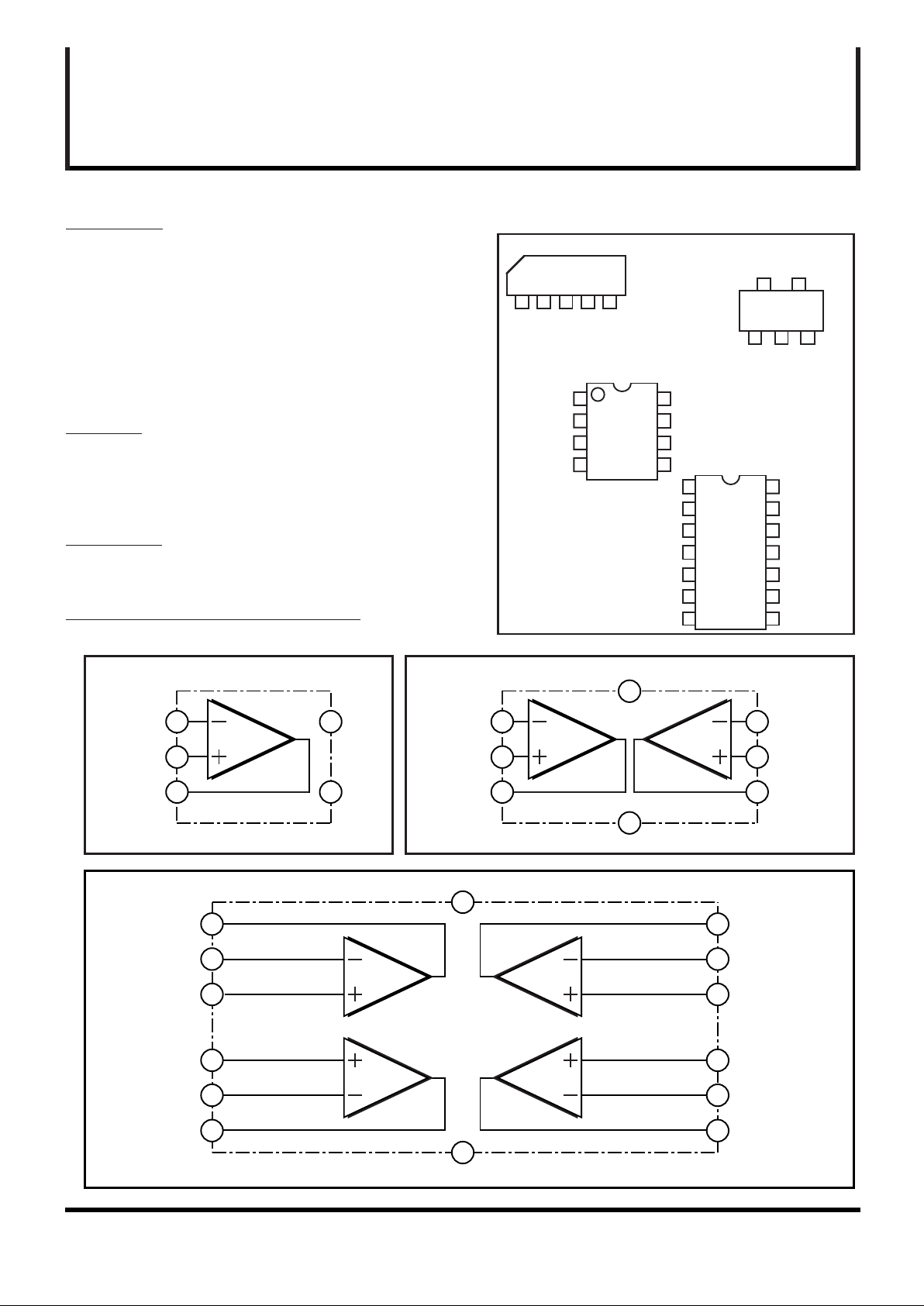

OUTLINE:

5P5T (M62551L)

SOT-25 (M62551GP)

8P4 (M62552P)

8P2S (M62552FP)

SSOP-8 (M62552GP)

14P4 (M62554P)

14P2S (M62554FP)

PIN CONFIGURATION (TOP VIEW)

12345

M62551L

11

12

13

14

4

3

2

1

M62554P/FP

VCC

OUTPUT 1

INVERTED

INPUT 4

INVERTED

INPUT 1

NON-INVERTED

INPUT 1

NON-INVERTED

INPUT 4

OUTPUT 4

10

5

GND

96

NON-INVERTED

INPUT 3

87

INVERTED

INPUT 3

NON-INVERTED

INPUT 2

INVERTED

INPUT 2

OUTPUT 2 OUTPUT 3

OUTPUT

VCC

GND

INVERTED

INPUT

NON-INVERTED

INPUT

1 2 3

45

M62551GP

OUTPUT

VCC

NON-INVERTED

INPUT

GND

INVERTED

INPUT

4

3

2

1

M62552

P/FP/GP

GND

OUTPUT 1

INVERTED

INPUT 2

INVERTED

INPUT 1

5

6

7

8

NON-INVERTED

INPUT 1

NON-INVERTED

INPUT 2

OUTPUT 2

VCC

BLOCK DIAGRAM (M62551L/GP)

1

OUTPUT

(5)

INVERTED

INPUT

(3)

4

3

5

2

NON-INVERtED

INPUT

(1)

VCC

(4)

GND

(2)

*Pin number at GP is put in parentheses.

BLOCK DIAGRAM (M62552P/FP/GP)

1

2

53

6

INVERTED

INPUT 1

NON-INVERTED

INPUT 1

OUTPUT 1

INVERTED

INPUT 2

NON-INVERTED

INPUT 2

OUTPUT 2

7

8

4

GND

VCC

BLOCK DIAGRAM (M62554P/FP)

3

1

2

CH1 CH4

CH2 CH3

INVERTED

INPUT 1

NON-INVERTED

INPUT 1

OUTPUT 1

7

OUTPUT 2

5

NON-INVERTED

INPUT 2

6

INVERTED

INPUT 2

13

INVERTED

INPUT 4

12

NON-INVERTED

INPUT 4

14

OUTPUT 4

8

OUTPUT 3

9

NON-INVERTED

INPUT 3

10

INVERTED

INPUT 3

11

4

VCC

GND

MITSUBISHI <STD LINEAR ICs>

GENERAL PURPOSE C•MOS OP AMP(SINGLE/DUAL/QUAD)

M6255X Series

P

P

R

R

E

E

L

L

I

I

M

M

I

I

N

N

A

A

R

R

Y

Y

Notice:This is not a final specification.

Some parametric limits are subject to change.

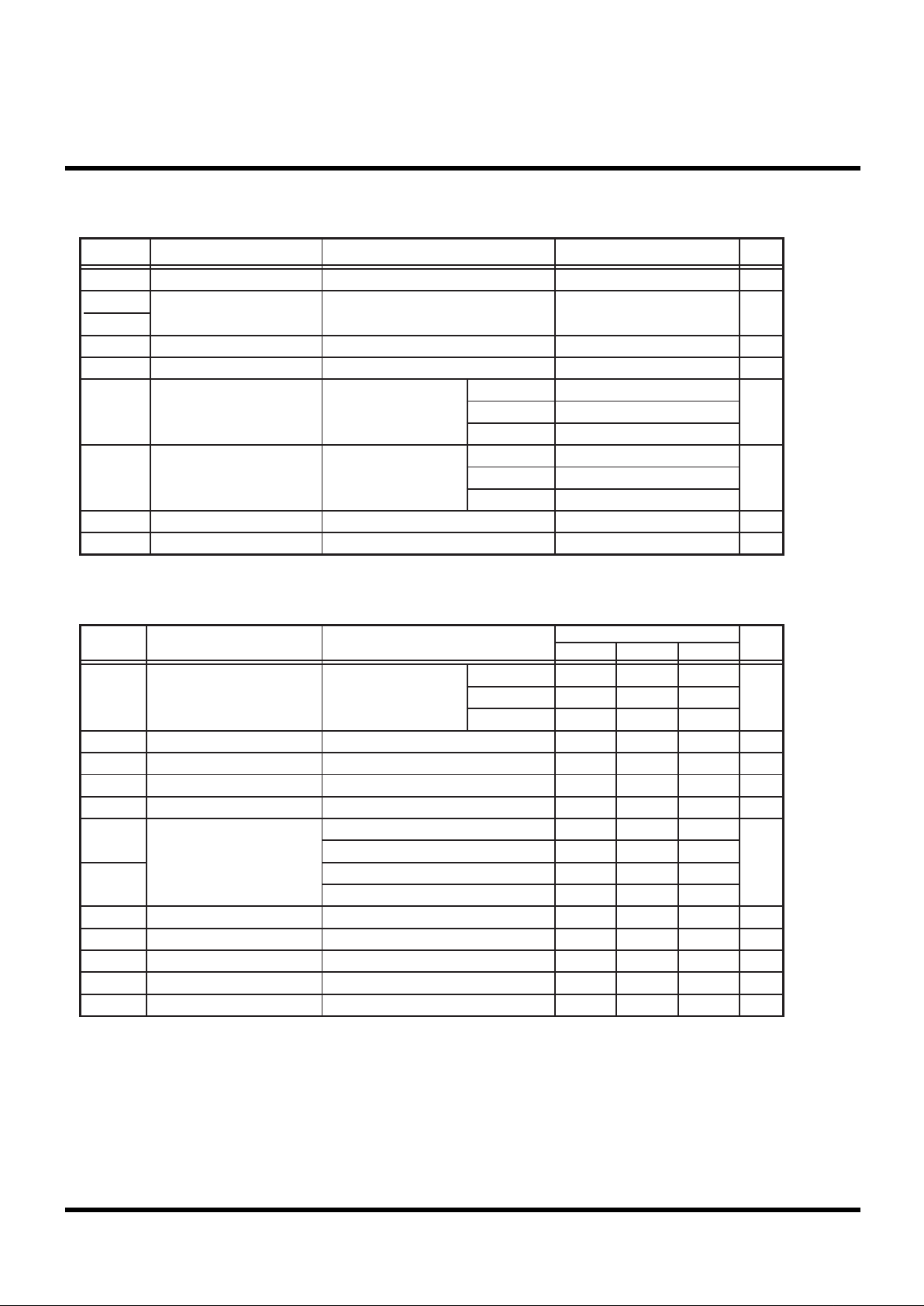

ABSOLUTE MAXIMUM RATINGS (Ta=25°C,unless otherwise noted)

ELECTRICAL CHARACTERISTICS (Ta=25°C,VCC=5V unless otherwise noted)

Symbol Parameter Test condition Unit

Limits

Circuit current

Input offset voltage

Common mode voltage range

Common mode rejection ratio

Supply voltage rejection ratio

Slew rate

0.19

Gain bandwidth product

mAICC

VIO

VICM

GVO

VOH

CMRR

SVRR

f

T

VOL

Open loop voltage gain

VNI

Output voltage swing

SR

Input conversion noise voltage

Min. Typ

Max

.

GV=0dB,RL=∞

V

IN=2.5V,RS=1KΩ,BW:10Hz,30KHz

R

L≥20KΩ

G

V=0dB,VIN=VCC,IO=+5mA

G

V=0dB,RL=∞

0.30

48

V

CC

100

VCC-0.1

0.01 0.1

65

65

1.2

1.0

10

VCC-0.5

0

80

mV

V

dB

V

dB

dB

MHz

µVrms

V/µS

IB

Input bias current

150pA

M62551

M62552

M62554

0.38 0.60

0.76 1.20

Symbol

Parameter

Conditions Unit

Ratings

Supply voltage

Load current

Power dissipation

Thermal derating

Ambient temperature

Ta=25°C

7

±10

-0.3 to 7

450(L)/200(GP)

-20 to +85

-40 to+125

mA

V

mW

mW/°C

°C

°C

Storage temperature

V

VCC

Isink

Isource

VIN

Ktheta

Topr

Tstg

Pd

Input voltage

Ta>25°C

4.5(L)2.0(GP)

M62551

M62552

M62554

625(P)/440(FP)/280(GP)

700(P)/550(FP)

6.25(P)/4.4(FP)j/2.8(GP)

7.0(P)/5.5(FP)

M62551

M62552

M62554

Vid Differential Input voltage

V

IN≤VCC

7V

GV=0dB,RL=∞

GV=0dB,VIN=VCC,IO=+1mA

G

V=0dB,VIN=VCC,IO=-5mA

G

V=0dB,VIN=VCC,IO=-1mA

V

CC-0.02

V

CC-0.1

0.05 0.25

( 2 / 3 )

5

Loading...

Loading...