Mitsubishi M62500P, M62500FP Datasheet

MITSUBISHI (Dig./Ana. INTERFACE)

(SWITCH)

M62500P/FP

SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC

DESCRIPTION

The M62500 is a semiconductor integrated circuit designed and

developed as a deflection control of the CRT display monitor.

The built-in trigger mode oscillator allows stable PWM control to be

gained against a wide range of change of external signals.

The M62500 provides a low supply voltage output malfunction

preventive circuit (UVLO) and software start function optimum to

horizontal output correction of monitor, high voltage drive and high

voltage regulator.

FEATURES

PWM output in synchronization with external signals

Wide range of PWM control frequency

15kHz to 150kHz

The PWM output phase is adjustable against external signals

Soft start

Built-in low voltage output malfunction prevention circuit

Start VCC>9V

Stop VCC<6V

APPLICATION

CRT display monitor

PIN CONFIGURATION (TOP VIEW)

GND

VREF

Tin

Delay Adj

CAGC1

DTC

IN1 (+)

IN1 (-)

FB1

COLLECTOR1

OUT1

P.GND

1

2

3

4

Outline 24P4D (P)

24

VCC

23

DRIVE OUTPUT

22

Phase Adj

21

Duty Adj

DOUBLE SPEED

205

SWITCH

196

RAGC

187

CAGC2

178

IN2 (+)

169

IN2 (-)

1510

FB2

1411

COLLECTOR2

1312

OUT2

24P2V-A (FP)

BLOCK DIAGRAM

VCC RAGC CAGC2 IN2 (+) IN2 (-) FB2 COLLECTOR2 OUT2

WIND

COMP

VREF

1 2 3 4 5 6 7 8 9 11 12

GND

DRIVE

OUTPUT

VREF Tin Delay

Phase

Adj

PHASE

CONT

DUTY

CONT

GEN

DELAY

Duty

Adj

Adj

DOUBLE

SPEED

SWITCH

2021222324 13141516171819

EDGE

DETECTION

comp

AGC

CAGC1 DTC IN1 (+) IN1 (-) FB1 COLLECTOR1 OUT1 P. GND

GEN

AGC

OUTPUT START

START (VCC>9V)

STOP (VCC<6V)

VCC

10

( / 11 )

1

SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC

ABSOLUTE MAXIMUM RATINGS (Ta=25˚C, unless otherwise noted)

Symbol Ratings UnitParameter

VCC

VOUT

IOUT

Vd

Id

VICM

VID

Pd

K

Topr

Tstg

Note. For the polarity of current, the direction in which current flows to the IC is specified positive (+),

while the direction in which current flows out from the IC is specified to be negative (-).

Supply voltage

Output voltage

Output current

Drive output voltage

Drive output current

Common mode input voltage range of

error amplifier

Common mode differential input voltage

of error amplifier

Power dissipation

Thermal derating

Operating temperature

Storage temperature

15

15

±150

15

20

-0.3 to VCC V

VCC V

P

1400

P

11.2

-20 to +75 °C

-40 to +125 °C

FP

1000

FP

8

mA

mA

mW

mW/°C

MITSUBISHI (Dig./Ana. INTERFACE)

M62500P/FP

V

V

V

2

( / 11 )

MITSUBISHI (Dig./Ana. INTERFACE)

M62500P/FP

SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC

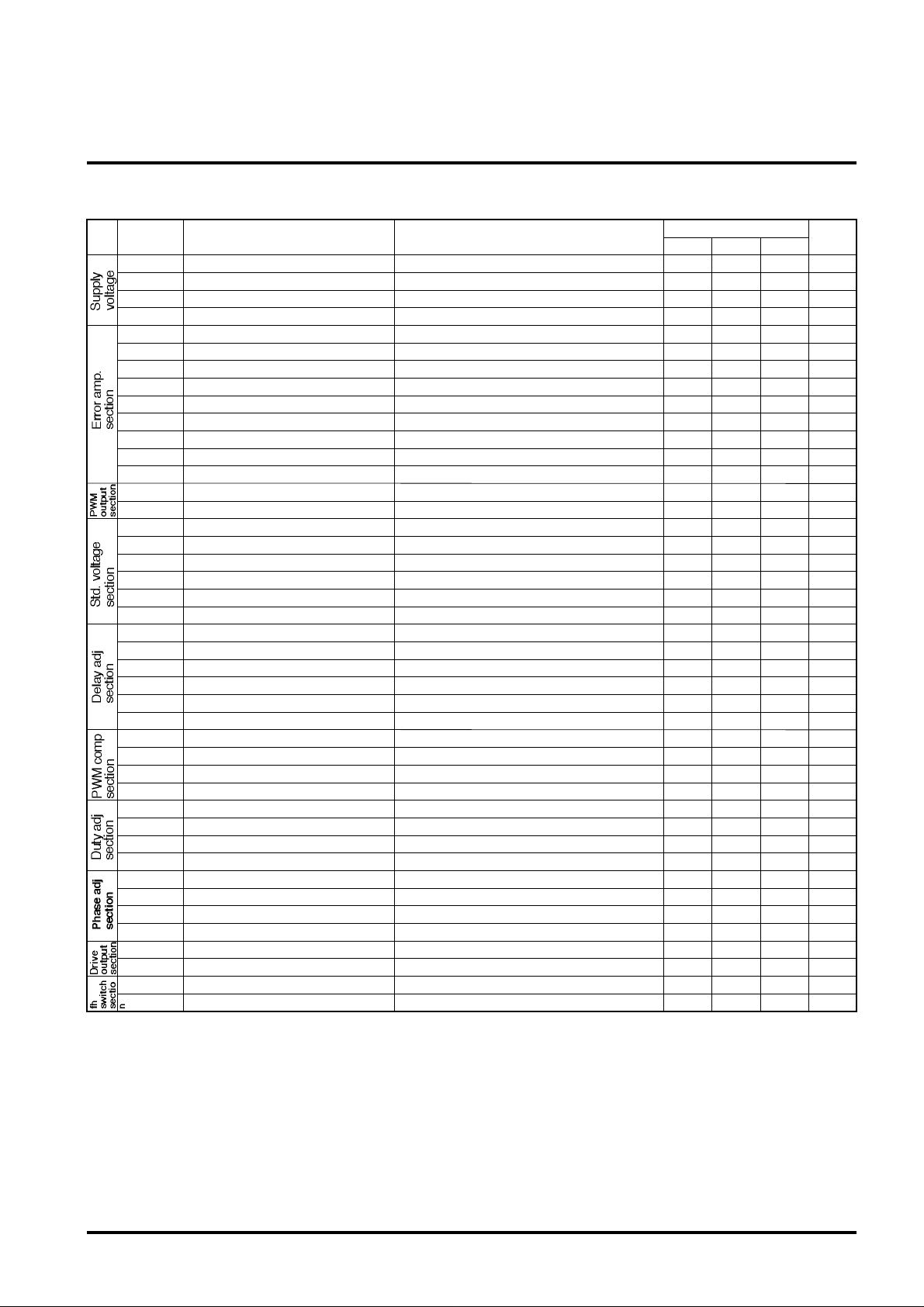

ELECTRICAL CHARACTERISTICS (VCC=12V, fIN=40kHz, Ta=25˚C, unless otherwise noted)

Block

Symbol Test conditions UnitParameter

VCC

ICC Without signal mA

VCC ON

VCC OFF

VIO

IIb

IIO

VICM

AV

SR

VOR V

Isink

Isource

VsatL IO=100mA

VsatH

VREF V

Reg-in

Reg-L

TCVREF

IREF MAX

IS

IIN

VIN L

VIN H

IDelay

TD min

TD max

IDTC

Vth U

Vth L

TDuty PWM output duty

IDuty

Duty min Minimum duty

Duty max Maximum duty

Duty

IPhase Input current

T2 min

T2 max

T2 Leading time of drive output

Vsat D Output saturation voltage

ILD

Ifh fh pin current

Vfh fh switching voltage

Note 1. Output must not be reversed with input of 0.

Range of power supply voltage

Dissipation current

Activation start voltage

Activation stop voltage

Input offset voltage

Input bias voltage

Input offset current

Common mode input range

Open loop gain

Through rate

Output voltage range 1)

Output sink current

Output source current

Output saturation voltage L

Output saturation voltage H

Reference voltage

Temperature coefficient of reference voltage

Short-circuit current

Input current

"L" input voltage

"H" input voltage

Input current

Minimum delay time

Maximum delay time

Input current

Upper limit voltage of saw tooth wave

Lower limit voltage of saw tooth wave

Input current

Duty

Minimum leading time of drive output

Minimum leading time of drive output

Output leak current

IO=-100mA

IREF=-5mA

VCC=7 to 14V IREF=-5mA

IREF=0 to -5mA

Ta=-20 to +75°C

VIN=5V

VDelay adj=0V

VDelay adj=3.0V

0.65VREF

0.28VREF

VDTC=2.5V

VDuty adj=2.5V

VDuty adj=2.5V

VPhase adj=2.5V

VPhase adj=1.0V

Id=10mA

VDO=12V

Vfh=5V

Limits

Min. Typ. Max.

20 40 70

8 9 10

-100 100

-0.3 VCC-2

0.3 VREF-1.5

0.7 1.4

4.80 5.00

-40

-70

— 200

-0.6 —

—

—

-6.5 -1.3

— 10

-3.5 -0.7

140

—

0.8

10

45 50

80 95

45

15

0.5

0.7VREF

0.3VREF

50

-10

5.20

—

1

—

0.75VREF

0.32VREF

55

—

20

—

55

—

7.0

430

VVCC off 14

V

V5.4 6.0 6.6

mV7

nA-100

nA

V

dB70 110

V/µs4

mA10

mA

V

V9.5 10.5

mV1 10Input stability

mV2 20Load voltage

%/°C0.01

mAMaximum reference current

mA

µA

V— 0.6

V2.0 —

µA-0.1

µs

µs

µA2.0

V

V

%

µA

%

%

%

µA

µs— 0.7 1.6

µs9 9.4 —

µs4.5 5.5

V0.4

µA1

µA— 330

V0.6VREF0.5VREF0.4VREF

( / 11 )

3

EXPLANATION OF TERMINALS

Pin No. Function and peripheral circuit of pinsSymbol

1

GNDGND

MITSUBISHI (Dig./Ana. INTERFACE)

M62500P/FP

SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC

VCC

2

3

VREF

Tin

5.0V reference voltage

External load of about 5mA can be taken out.

Trigger input

Read at the rising edge

Tin

2

VREF

S

Q

3

FF

R

VREF

Delay adjustment

4

5

18

Delay Adj

CAGC1

CAGC2

Delay of read trigger signal

VDelay : 0 to 3.0V

TDelay : 1µ to 10µsec

AGC capacitance

Connects capacitance between each pin

and GND and sets up AGC sensitivity

4

( / 11 )

4

VREF

5

18

Loading...

Loading...