MITSUBISHI SOUND PROCESSORS

PRELIMINARY

Notice ; This is not a final specification.

some parametric limits are subject to change.

Dolby Pro Logic Surround Decoder

Description

The M62462FP is a Single Chip Dolby Pro Logic

Surround Decoder.This LSI has all functions necessary

for Dolby Pro Logic Surround.

Dolby and the double-D symbol are trademarks of Dolby Laboratories

Licensing Corporation.San Francisco,CA94103-4813,USA.

This device available only to licensees of Dolby Lab.

Licensing and application information may be obtained from Dolby Lab.

Features

Includes all functions necessary for Dolby Pro Logic Surround

-Adaptive Matrix

-Input Auto-Balance

-Noise Sequencer

-Center Mode Control ON/OFF, WIDE/NORMAL/PHANTOM

-Modified Dolby B type Noise Reduction

-4 channel (Lch/Rch/Cch/Sch) / 3 channel (Lch/Rch/Cch)

-Digital delay Delay time:15.4 to 51.2msec

Cch/Sch Master Volume 0 to -84dB/1dB step

3-lines MCU control

Current control oscillation circuit for system clock

M62462FP

Outline

Outline 64P6N

0.8mm pich QFP

(14.0mm*14.0mm*2.8mm)

System Configuration

Lch IN

Rch IN

Delay IN

L+R

L-R

Input

AutoBalance

Control

S'

Noise

2

Sequencer

Digital Delay

Adaptive

Matrix

7kHz

LPF

L

R

C

Modified

Dolby

B-NR

S

DATA SCK REQ

MITSUBISHI

ELECTRIC

13

1

( / )

M62462FP

Center/

operating

mode

control

MCU Interface

Center

Master

Volume

Surround

Master

Volume

Lch

OUT

Rch

OUT

Cch

OUT

Sch

OUT

Master

Volume

Lch

Rch

CENTER

SURROUND

MITSUBISHI SOUND PROCESSORS

PRELIMINARY

Notice ; This is not a final specification.

some parametric limits are subject to change.

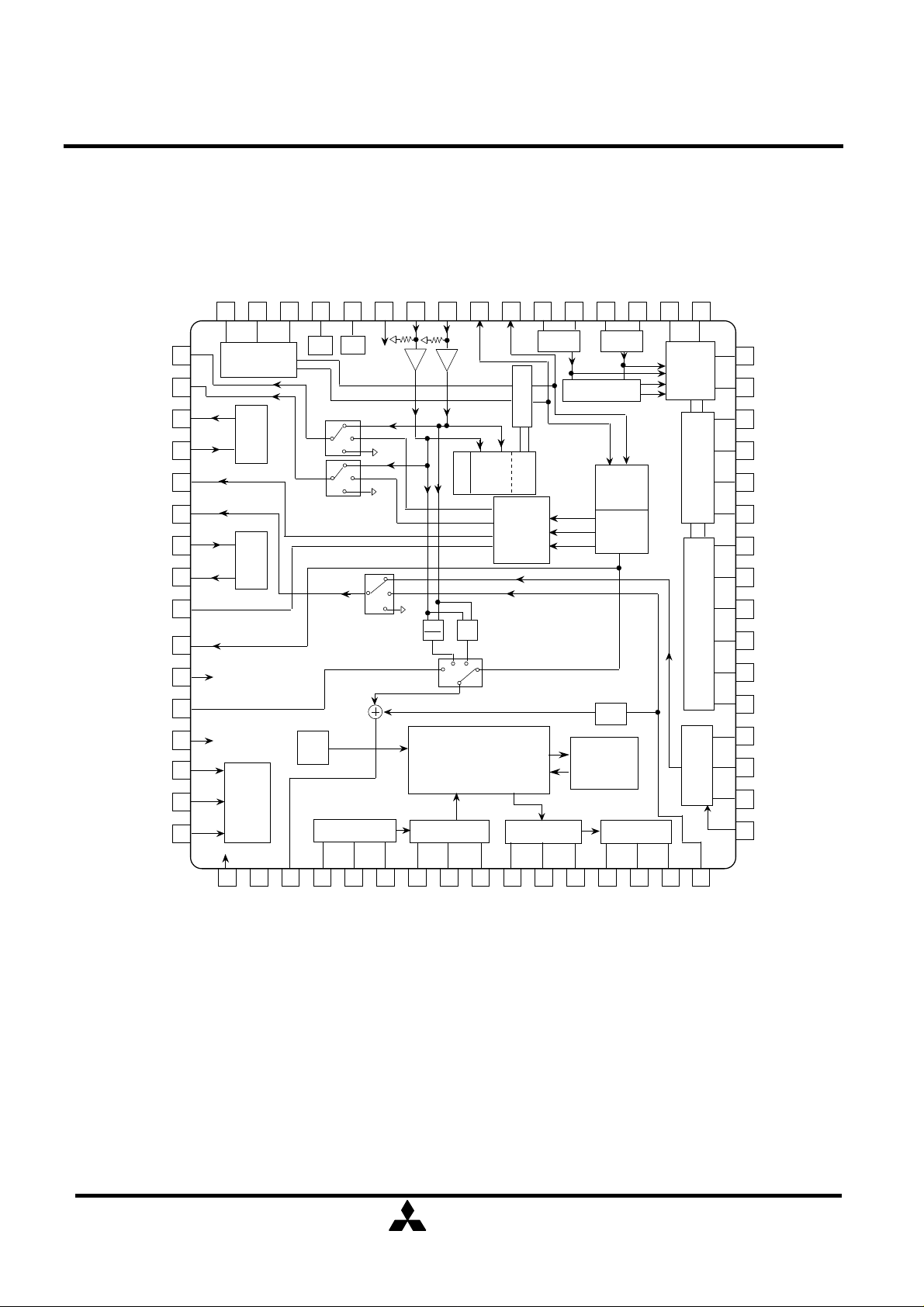

FIG.1 Pin Configuration

NGC2

LOUT

ROUT

CVOLOUT

CVOLIN

COUT

SOUT

SVOLIN

SVOLOUT

CMC

S'OUT

AGND

DIN

DVdd

DATA

SCK

REQ

NGC1

64

L

1

R

2

C

3 4

5

6

7 8

S

9

S'

10

AGND

11

12 13

DVdd

14 15

16

DATA SCK

REQ

DVss

17

DVss

NGC3

62

63

SEQUENCER

NOISE

VOL MCU INTERFACE

VOL

TEST

18

19

DSEL OUT

TEST

VREF

IREF

60

61

IREF VREF

1

2

3

1

2

3

CLK

LPF

21

20

LPF1 IN1

LPF1 IN2

AVcc

59

AVcc

SW1

SW2

1

3

SW3

22

LPF1 OUT

RIN

58

2

L+R

23

ADINT IN

Dolby Pro Logic Surround Decoder

LIN

RT

LT

56

57

SERVO

L-R

2

3

4

LOGIC

A/D D/A

24

ADINT OUT

55

VCA

L

CONTROL

R C

SW4

2

1

26

25

ADCONT

DACONT

RBPF1

54

SELECTER

BALANCE

AUTO

CENTER MODE

27

DAINT IN

RBPF2

53

28

DAINT OUT

LBPF1

52

L+R L-R

L

C R

S'

F.B.

VOL

10Kbit

SRAM

29

LPF2 IN1

LBPF2

51

BPF BPF

VCA

LPF

LPF2 IN2

M62462FP

RLC8

RLC6

50

49

FULL WAVE

RECTIFIER

RLC3

4748

RLC7

RLC4

DIFFERENCE

NETWORKS

COMBINNING

30

31

LPF2 OUT

AMPLIFIERS

AND THRESHOLD SWITCHES

NR DECODER

4546

LOG

DUAL-TIME CONSTANT

MODIFIED

B-TYPE

32

44

43

42

41

40

39

38

37

36

35

34

33

RLC1

RLC2

RLC5

PSC4

PSC1

PSC5

PSC2

PSC6

PSC3

DBC3

DBC2

DBC1

BNR IN

FBIN

MITSUBISHI

ELECTRIC

( / )

13

2

MITSUBISHI SOUND PROCESSORS

PRELIMINARY

Notice ; This is not a final specification.

some parametric limits are subject to change.

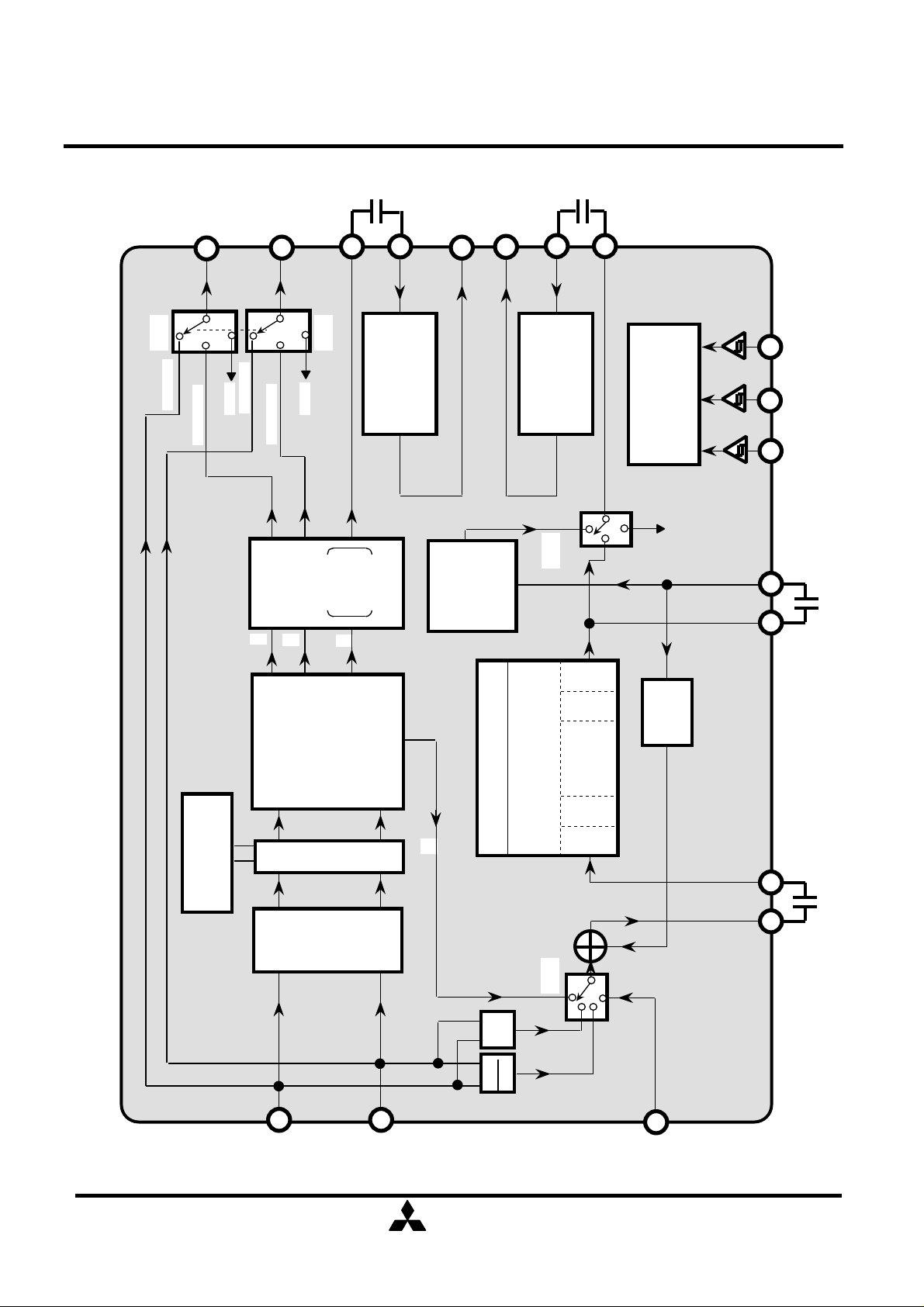

Fig.2 Block Diagram

Rout

3

2

MUTE

PROLOGIC

CENTER

MODE

CONTROL

R

1

SW1

BY-PASS

Lout

3

2

MUTE

PROLOGIC

1

BY-PASS

L

SW2

WIDE

NORMAL

C

MASTER

OFF

PHANTOM

VOLUME

Modified

M62462FP

Dolby Pro Logic Surround Decoder

Sout

Cout

MASTER

VOLUME

MCU

INTERFACE

1

3

2

SW3

BNR

LPF

DATA

SCKREQ

NOISE

SEQUENCER

ADAPTIVE

MATRIX

SELECTOR

AUTO-BALANCE

INPUT

S'

D/A

LOGIC

10Kbit SRAM

DIGITAL DELAY

SW4

L-R

2

L+R

A/D

LPF

1

4

3

2

F.B.

VOL

Lin

Rin

MITSUBISHI

ELECTRIC

3

( / )

Din

13

MITSUBISHI SOUND PROCESSORS

PRELIMINARY

Notice ; This is not a final specification.

some parametric limits are subject to change.

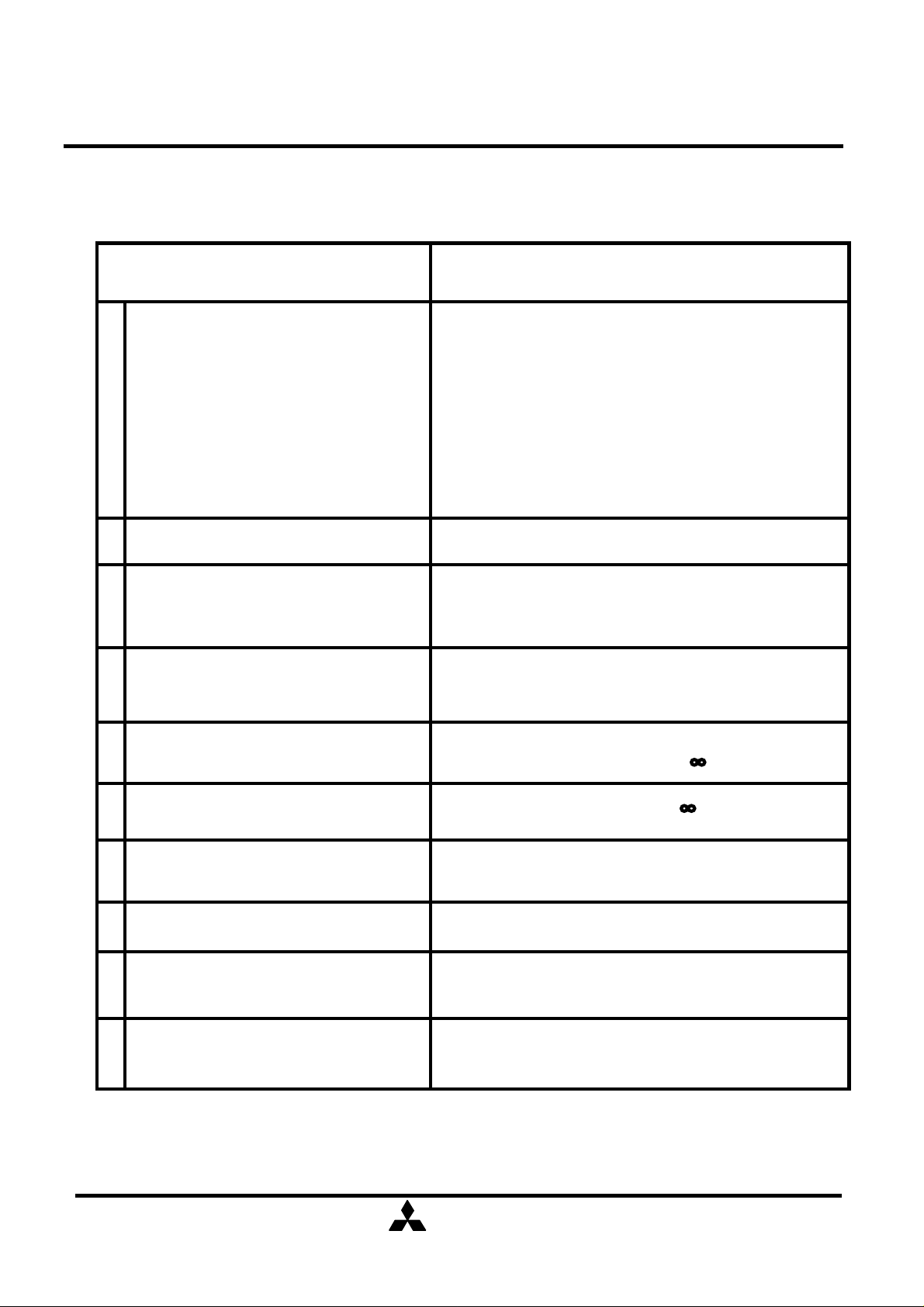

7.FUNCTIONAL DESCRIPTION

FUNCTION DESCRIPTION

Fundamental function for

1

Dolby Pro Logic Surround

Decoder

2

RAM for Digital Delay 10K-bit RAM

-Adaptive Matrix

-Input Auto-Balance

-Noise Sequencer

-Center Mode Control

ON/OFF

WIDE/NORMAL/PHANTOM

-Modified Dolby B type Noise Reduction

-4ch(L,R,C,S), 3ch(L,R,C) Mode Switch

M62462FP

Dolby Pro Logic Surround Decoder

3 Surround Delay Time

4

Circuit for Space Surround

5 Feedback Volume

Cch/Sch Master Volume6

7

Bypass Switch

Output Mute8

MCU Interface

9

15.4, 20.5, 25.6, 29.2msec

(for Dolby Pro Logic Surround)

51.2msec (for Space Surround)

Digital delay circuit can be used for

Space Surround such as a Disco, Hall or Live.

Delay Signal Feedback Volume

-3 to -21 dB/3dB step, and -

0 to -84dB/1dB step, and -

Bypass the decode circuit

Mute the Lch and Rch output

Controlled by 3-lines serial data from MCU

Including the Chip Address (2 bit)

10 Current control oscillation circuit

Including the oscillation circuit without

external parts.

MITSUBISHI

ELECTRIC

( / )

134

Loading...

Loading...