Mitsubishi M62368GP Datasheet

MITSUBISHI<Dig.Ana.INTERFACE>

combination with a microcomputer.

operational amplifiers.

resistor)

0D71234568

9

10

M62368GP

3V TYPE 8-BIT 6CH D-A CONVERTER WITH BUFFER AMPLIFIERS

DESCRIPTION

The M62368GP is a CMOS semiconductor IC, containing 6

channels of 8-bit D-A converters. It is operable with a low supply

voltage between 2.7~3.6V,and is easy to use due to serial data

input,and 3-pin(DI,CLK,LD)connection with microcomputer.

The IC also contains Do pin terminal,enabling cascade

connection,and therefore is suitable for automatic control in

FEATURES

•Operable with a low voltage between 2.7~3.6V

•12-bit serial data input(connected via 3 pins:DI,CLK,LD)

•6 channels of R-2R and segment type high-performance 8-bit

D-A converters

•6 buffer operational amplifiers with full swing of output voltage

between Vcc and GND.

•High oscillation stability against the capacitive load of buffer

APPLICATION

Digtal-analog conversion in industrial or home-use

electronic equipment.

Automatic control in combination with EEPROM and

microcomputer(Substitute for conventional semi-fixed

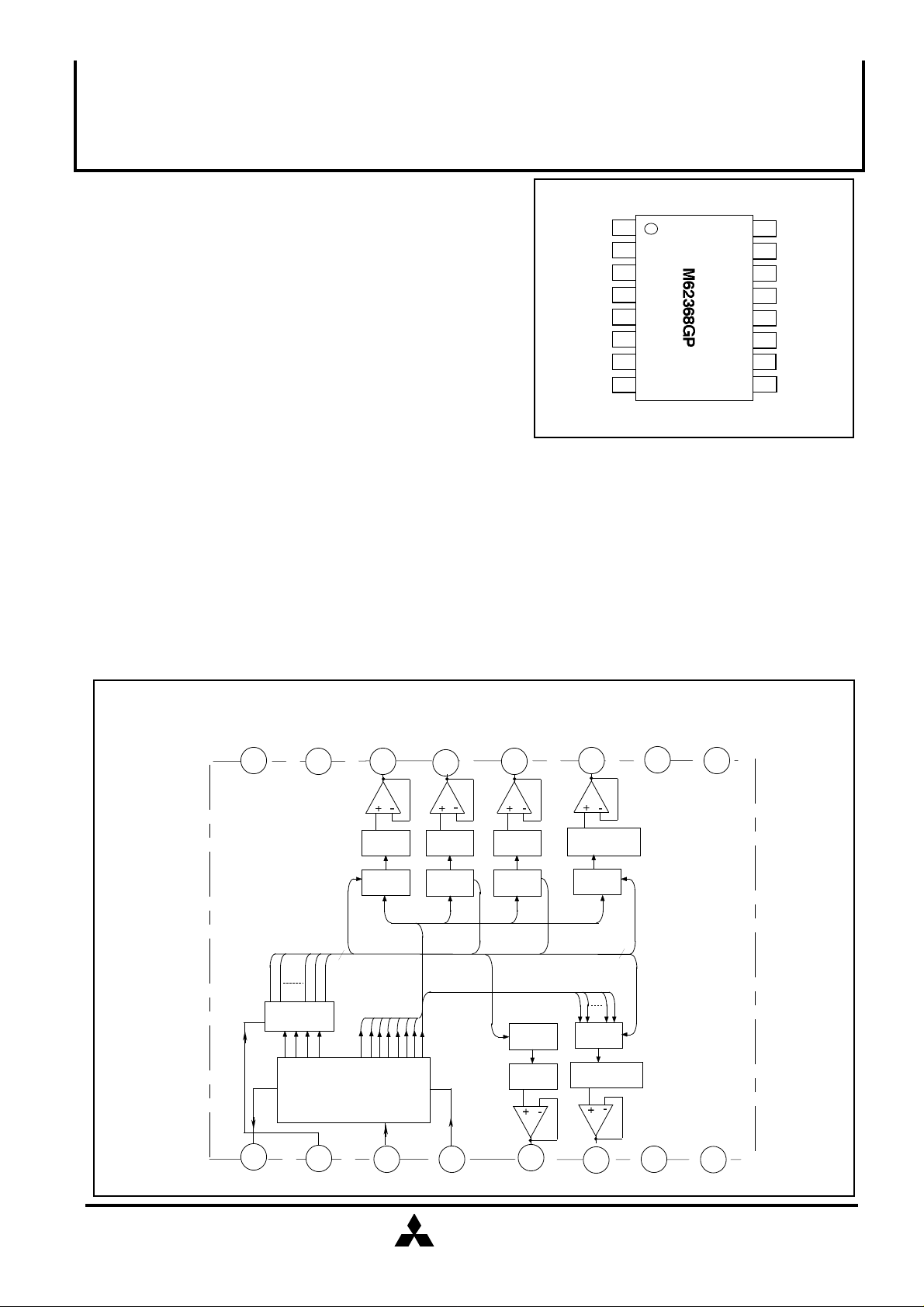

PIN CONFIGURATION (TOP VIEW)

Do

LD

CLK

DI

Ao1

Ao2

NC

GND

1

2

3

4

5

6

7

8

Outline 16P2E-A

NC:NO CONNECTION

Vcc

16

VDD

15

Ao6

14

Ao5

13

Ao4

12

Ao3

11

10

NC

VSS

9

BLOCK DIAGRAM

VCC

16

1

Do

15

CH1

(6)

ADDRESS

DECODER

D11

12-BIT SHIFT REGISTER

2

LD

14

D-A

L

Ao5Ao6VDD

13

D-A

5

L

DICLK

Ao4

12

D-A

4

L

L

CH1

D-A

5

Ao1

Ao3

8-BIT

R-2R + SEGMENT

D-A CONVERTER

3

8-BIT

LATCH

8-BIT

LATCH

2

8-BIT

R-2R + SEGMENT

D-A CONVERTER

643

Ao2

(6)

BUFFER

OPERATIONAL

AMPLIFIER

NC

10

7

NC

Vss

911

8

GND

MITSUBISHI

ELECTRIC

( / 5 )

1

3V TYPE 8-BIT 6CH D-A CONVERTER WITH BUFFER AMPLIFIERS

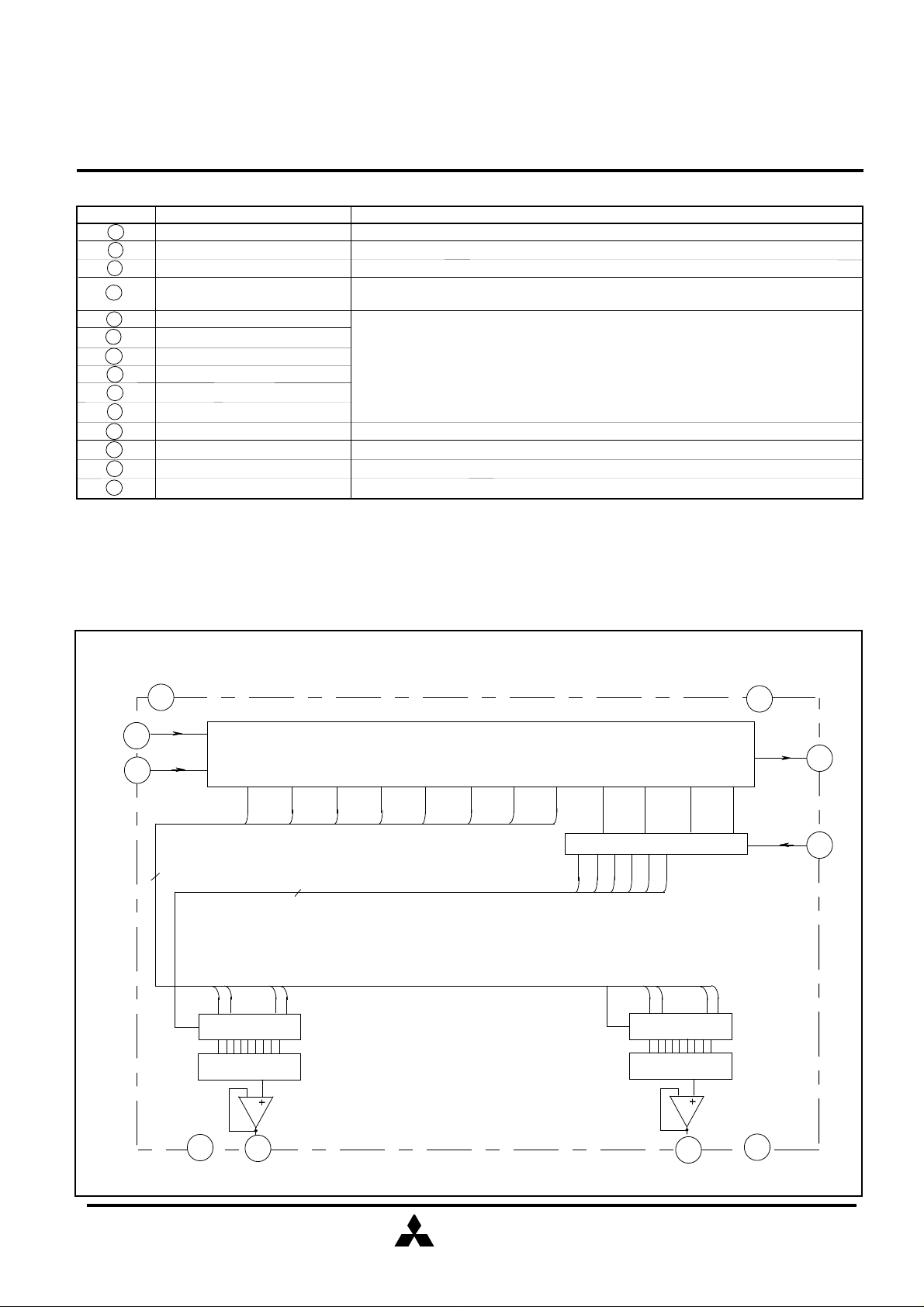

EXPLANATION OF TERMINALS

Pin No. Symbol

4

1

3

2

5

6

11

12

13

14

16

8

15

9

DI

Do

CLK

LD

Ao1

Ao2

Ao3

Ao4

Ao5

Ao6

VCC

GND

VDD

VSS

MITSUBISHI<Dig.Ana.INTERFACE>

M62368GP

Function

Serial data input terminal to input 12-bit long serial data

Terminal to output MSB data of 12-bit shift register

Shift clock input terminal.Input signal at DI pin is input to 12-bit shift register at rise of shift clock pulse

When H-level signal is input to this terminal,the value stored in 12-bit shift register is loaded

in decoder and D-A converter output register

8-bit D-A converter output terminal

Power supply terminal

GND terminal

D-A converter upper reference voltage input terminal

D-A converter lower reference voltage input terminal

BLOCK DIAGRAM FOR EXPLANATION OF TERMINALS

Vcc

16

4

DI

12-BIT SHIFT REGISTER

D4

D3

.............................................6

..............................................

D5

D6 D7

CLK

3

8

D0

8-BIT

R-2R + SEGMENT

D-A CONVERTER

D0

............

8-BIT

LATCH

-

D1

D2

6

D7

...................................................................................................

D8

D9

D10 D11

ADDRESS DECODER

3

4

21

5 6

D0

LATCH

8-BIT

R-2R + SEGMENT

D-A CONVERTER

............

8-BIT

-

GND

8

12Do

LD

D7

15

VDD

(VrefU)

5

Ao1

MITSUBISHI

ELECTRIC

12

Ao6

9

Vss

(VrefL)

( / 5 )

2

Loading...

Loading...