MITSUBISHI<Dig.Ana.INTERFACE>

The input data is a easy-to-use 3-wire serial transfer method and it

is able to cascading serial use with Do terminal.

The device is suited for use in high accuracy automatic

adjustment combination with microcomputer.

Recommend operation condition..........VDD=5V±10%

resistor.)

CONVERTER

CONVERTER

M62362P

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

DESCRIPTION

The M62362P is an integrated circuit semiconductor of CMOS

structure with 3 channels of built-in 1280 step resolution(equivalent

10.3-bit)multiplication type D-A converters.

FEATURES

•Digital data transfer method

3-wire serial data transfer method

•High resolution

Resolution is more over 10-bit and error is less than ±1 LSB

•Capable of 4 quadrant multiplication

•Short setting time

•With reset terminal

APPLICATION

Signal gain control of DISPLAY-MONITOR or CTV.

Conversion from digital control data to analog control data

for home-use and industrial equipment.

Automatic adjustment by combination with EEPROM and

microcomputer.(replacement of conventional half-fixed

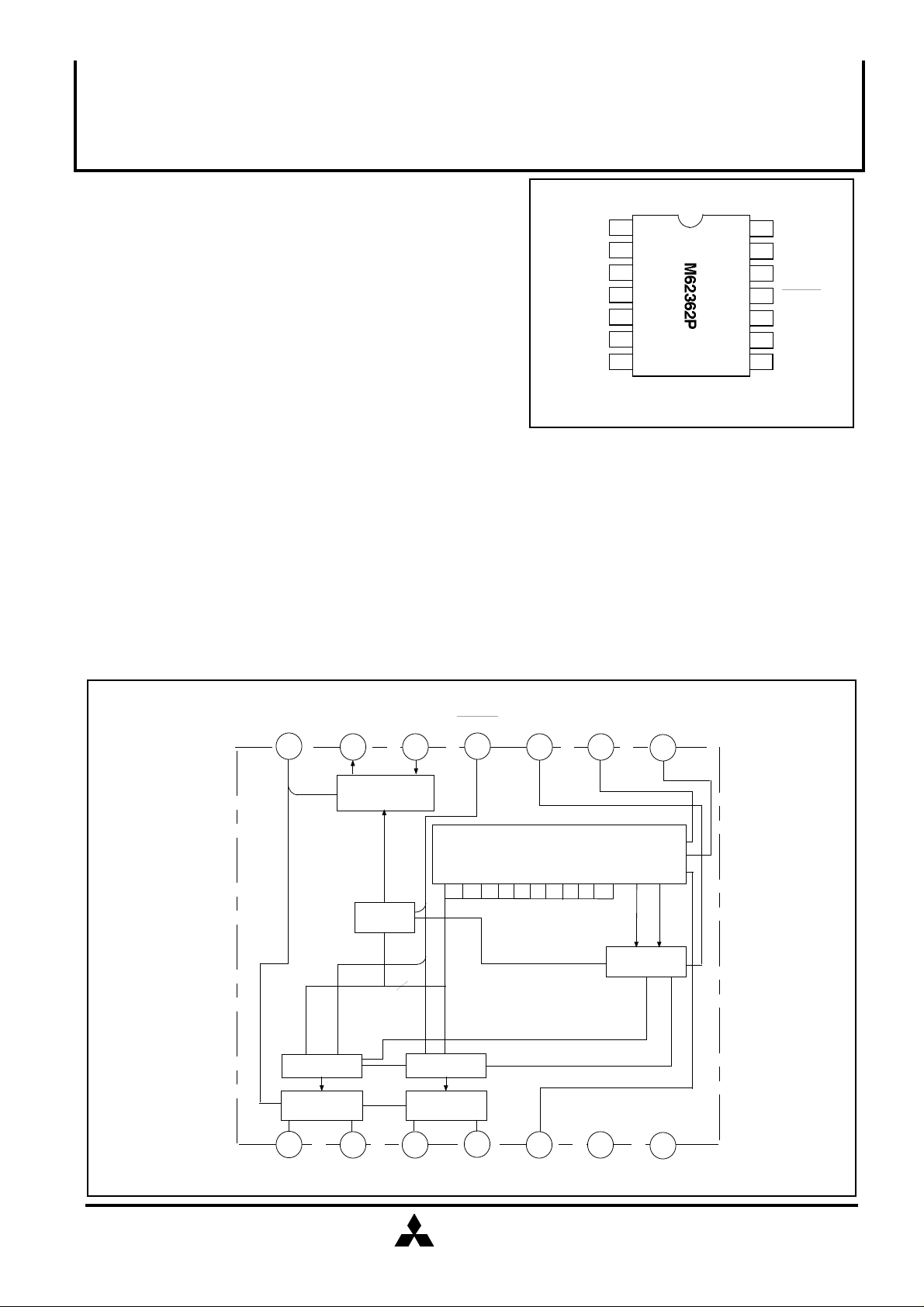

PIN CONFIGURATION (TOP VIEW)

VIN2

Vo2

VIN3

Vo3

Do

GND

VDD

1

2

3

4

5

6

7

Outline 14P4

14

13

12

11

10

9

8

VDAref

Vo1

VIN1

RESET

BS

DI

CLK

BLOCK DIAGRAM

VDAref Vo1

14

11-BIT D-A

1

VIN2 Vo2 VIN3 Vo3 Do

11-BIT

LATCH

13 12

11-BIT

DA CONVERTER

2 3

VIN1 RESET

11-BIT

LATCH

(11)

11 10

13-BIT SHIFT RESISTER

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12

11-BIT

LATCH

11-BIT D-A

4 5

BS

DI

9

ADDRESS

DECORDER

6

GND

CLK

8

7

VDD

MITSUBISHI

ELECTRIC

( / 8 )

1

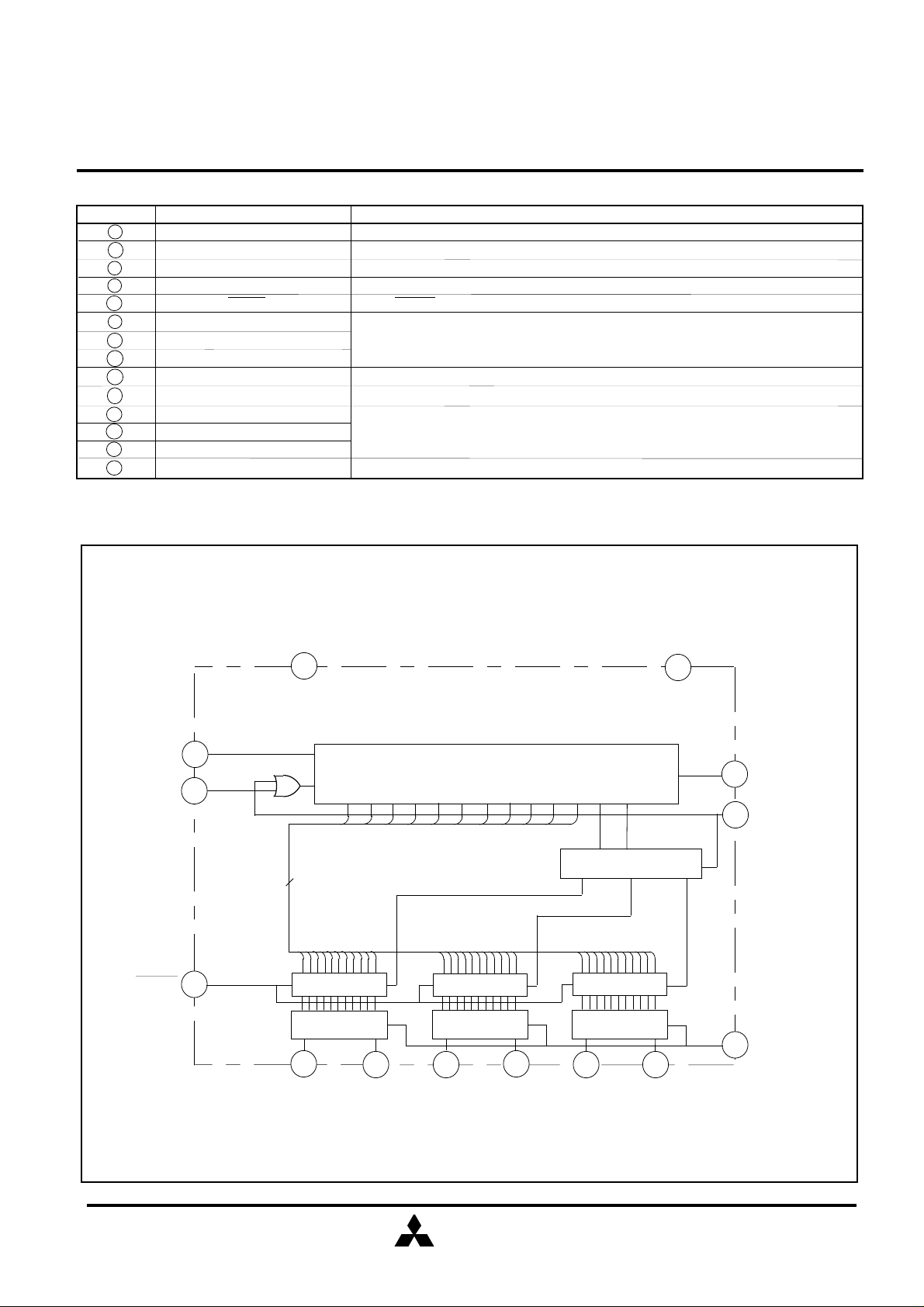

EXPLANATION OF TERMINALS

CONVERTER

CONVERTER

CONVERTER

Pin No. Symbol

9

5

8

10

11

13

2

4

7

6

1

3

12

14

DI

Do

CLK

BS

RESET

Vo1

Vo2

Vo3

VDD

GND

VIN2

VIN3

VIN1

VDAref

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

Function

Serial data input terminal

Serial data output terminal

Serial clock input terminal

When BS terminal level is "H" latch circuit data is load

When RESET terminal level is "L",all D-A output terminal became "L"

1280 resolution D-A output

Power supply terminal

GND terminal

D-A converter input terminal

D-A converter reference voltage input terminal

BLOCK DIAGRAM FOR EXPLANATION OF TERMINALS

VDD

7

9

DI

CLK

RESET

11

8

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12

11

11-BIT

LATCH

13-BIT SHIFT RESISTER

11-BIT

LATCH

ADDRESS

DECORDER

11-BIT

LATCH

GND

6

10

5

Do

BS

11-BIT D-A

12

VIN1 Vo1

13 1

11-BIT D-A

2 3

VIN2 Vo2 VIN3 Vo3

11-BIT D-A

MITSUBISHI

ELECTRIC

VDAref

14

4

( / 8 )

2

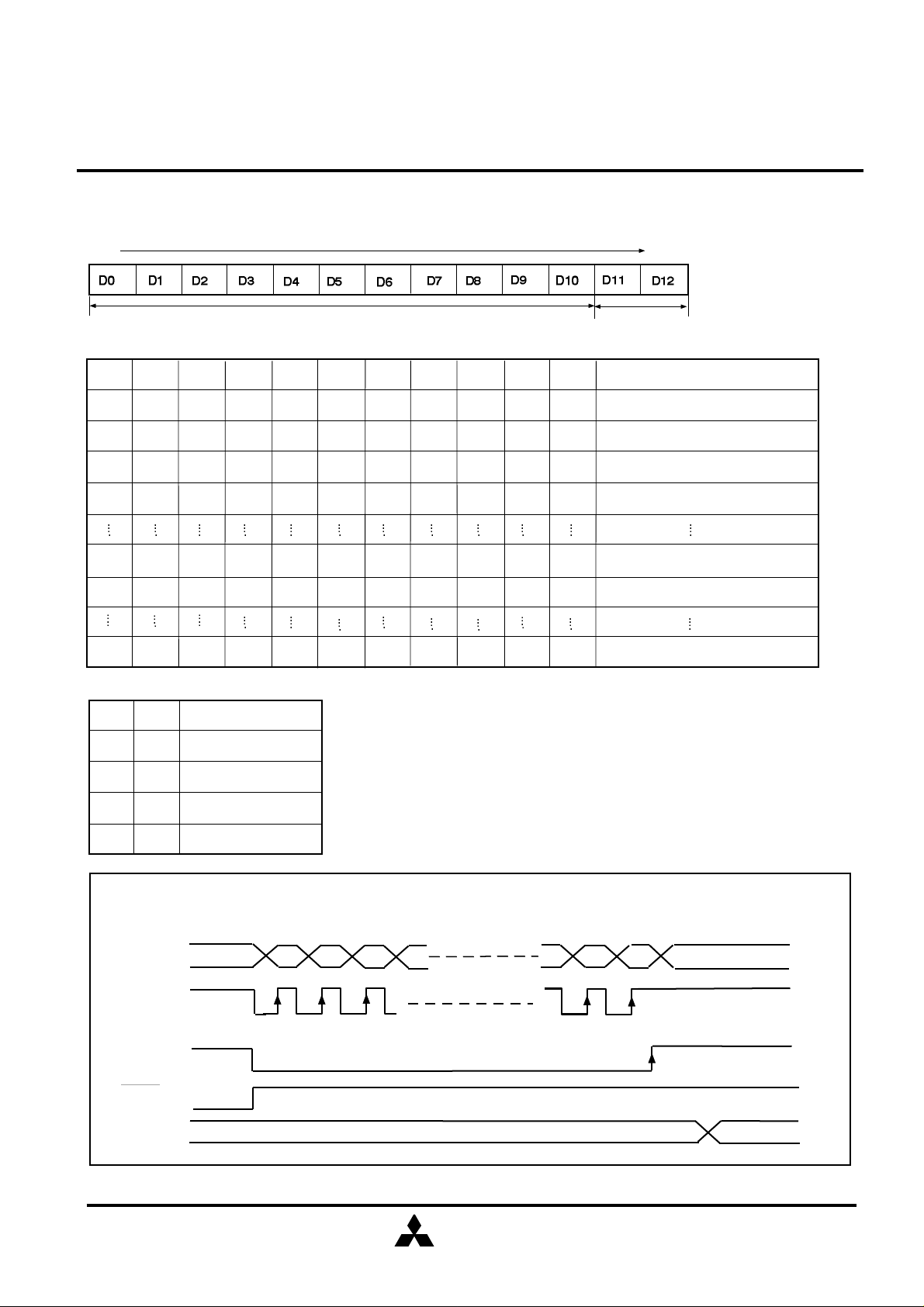

DIGITAL DATA FORMAT

LAST

LSB

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

FIRST

MSB

D0

0

1

0

1

1

0

1

D11 D12 DAC SELECTION

0

D2 D3 D4

D1

0

0

0

1

1

1

1 1 1 1 1 1 1 1 1 1

Don't care

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

1

0

D-A DATA

D5

0

0

0

0

1

0

D6 D7

0

0

0

0

1

0

ADDRESS

DATA

D9 D10

D8

0

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

(VIN-VDAref) / 1280 X 1 + VDAref

0

(VIN-VDAref) / 1280 X 2 + VDAref

0

(VIN-VDAref) / 1280 X 3 + VDAref

0

(VIN-VDAref) / 1280 X 1279 + VDAref

1

10

D-A output

VDAref

VIN

VIN

0

1

1

ch1

1

ch2

0

1

ch3

TIMING CHART (MODEL)

DI

CLK

BS

RESET

D-A

OUTPUT

*Input data is carried out BS signal "L" besides CLK signal positive edge.

CLK,BS,is keep generally "H" level.

MSB

D12 D11

D10

MITSUBISHI

ELECTRIC

D1

LSB

D0

( / 8 )

3

Loading...

Loading...