MITSUBISHI<Dig.Ana.INTERFACE>

hod and it

is able to cascading serial use with Do terminal.

The device is suited for use in high accuracy automatic

adjustment combination with microcomputer.

DD=5V±10%

CONVERTER

CONVERTER

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

DESCRIPTION

The M62362P is an integrated circuit semiconductor of CMOS

structure with 3 channels of built-in 1280 step resolution(equivalent

10.3-bit)multiplication type D-A converters.

FEATURES

•Digital data transfer method

3-wire serial data transfer method

•High resolution

Resolution is more over 10-bit and error is less than ±1 LSB

•Capable of 4 quadrant multiplication

•Short setting time

•With reset terminal

APPLICATION

Signal gain control of DISPLAY-MONITOR or CTV.

Conversion from digital control data to analog control data

for home-use and industrial equipment.

Automatic adjustment by combination with EEPROM and

microcomputer.(replacement of conventional half-fixed

PIN CONFIGURATION (TOP VIEW)

VIN2

Vo2

VIN3

Vo3

Do

GND

VDD

1

2

3

4

5

6

7

M62362P

Outline 14P4

14

13

12

11

10

9

8

VDAref

Vo1

VIN1

RESET

BS

DI

CLK

PIN CONFIGURATION (TOP VIEW)

VIN2

Vo2

VIN3

Vo3

Do

GND

VDD

N.C

1

2

3

4

5

6

7

8 9

M62362FP

Outline 16P2N

16

15

14

13

12

11

10

VDAref

Vo1

VIN1

RESET

BS

DI

CLK

N.C

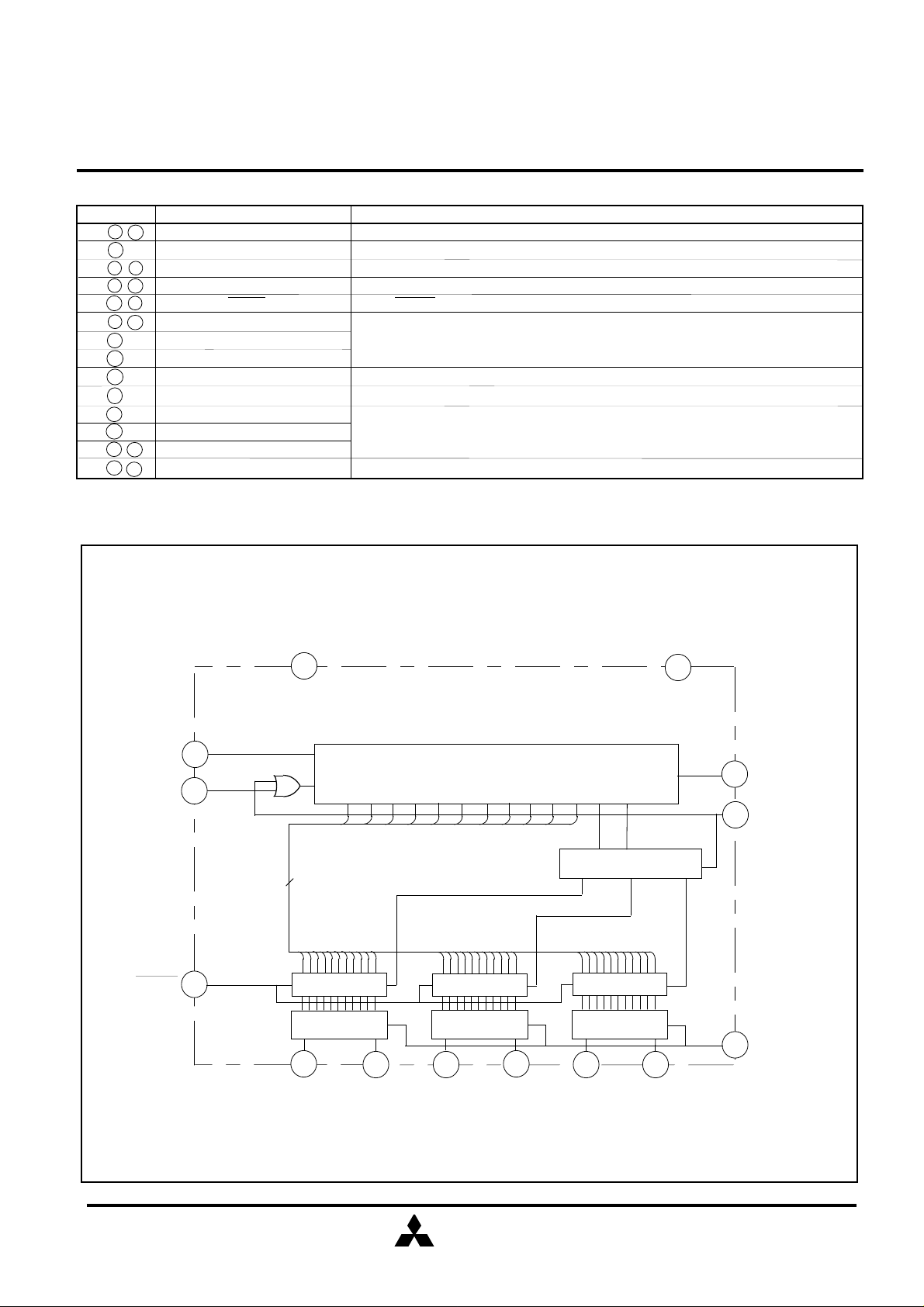

BLOCK DIAGRAM

VDAref Vo1

11-BIT

DA CONVERTER

11-BIT

LATCH

11-BIT D-A

VIN1 RESET

11-BIT

LATCH

(11)

BS

13-BIT SHIFT RESISTER

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12

11-BIT

LATCH

11-BIT D-A

DI

ADDRESS

DECORDER

CLK

VIN2 Vo2 VIN3 Vo3 Do

MITSUBISHI

ELECTRIC

GND

VDD

( / 8 )

1

EXPLANATION OF TERMINALS

CONVERTER

CONVERTER

CONVERTER

Pin No. Symbol

9

10

11

13

12

14

11

5

10

8

12

13

15

2

4

7

6

1

3

14

16

DI

Do

CLK

BS

RESET

Vo1

Vo2

Vo3

VDD

GND

VIN2

VIN3

VIN1

VDAref

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

Function

Serial data input terminal

Serial data output terminal

Serial clock input terminal

When BS terminal level is "H" latch circuit data is load

When RESET terminal level is "L",all D-A output terminal became "L"

1280 resolution D-A output

Power supply terminal

GND terminal

D-A converter input terminal

D-A converter reference voltage input terminal

BLOCK DIAGRAM FOR EXPLANATION OF TERMINALS

VDD

DI

CLK

RESET

D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12

11

11-BIT

LATCH

13-BIT SHIFT RESISTER

11-BIT

LATCH

ADDRESS

DECORDER

11-BIT

LATCH

GND

Do

BS

11-BIT D-A

VIN1 Vo1

11-BIT D-A

VIN2 Vo2 VIN3 Vo3

11-BIT D-A

MITSUBISHI

ELECTRIC

VDAref

( / 8 )

2

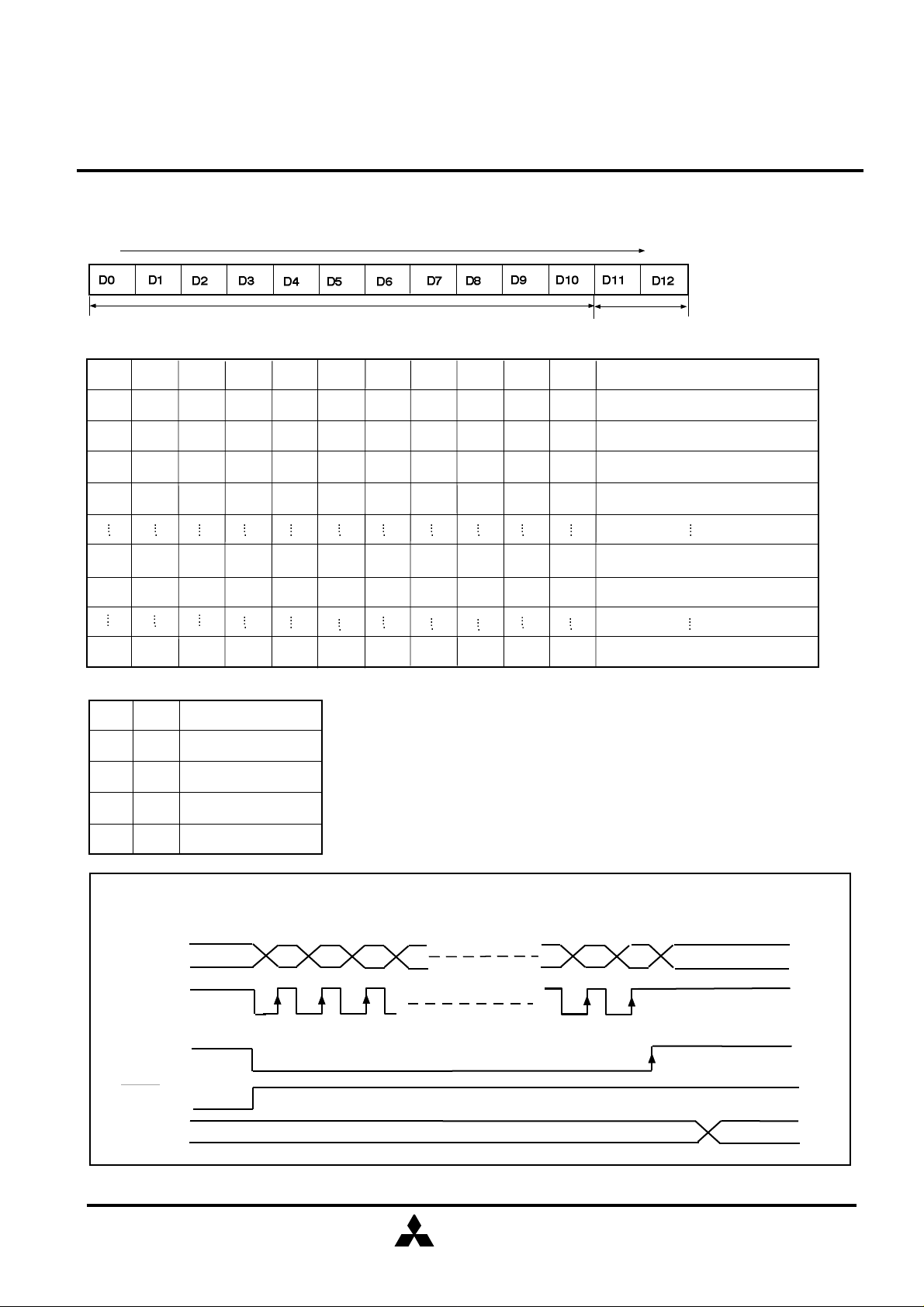

DIGITAL DATA FORMAT

LAST

LSB

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

FIRST

MSB

D0

D1

0

1

0

1

1

0

1

D11 D12 DAC SELECTION

0

D2 D3 D4

0

0

0

1

1

1

1 1 1 1 1 1 1 1 1 1

Don't care

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

1

0

D-A DATA

D5

0

0

0

0

1

0

D6 D7

0

0

0

0

1

0

ADDRESS

DATA

D9 D10

D8

0

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

(VIN-VDAref) / 1280 X 1 + VDAref

0

(VIN-VDAref) / 1280 X 2 + VDAref

0

(VIN-VDAref) / 1280 X 3 + VDAref

0

(VIN-VDAref) / 1280 X 1279 + VDAref

1

10

D-A output

VDAref

VIN

VIN

0

1

1

ch1

1

ch2

0

1

ch3

TIMING CHART (MODEL)

DI

CLK

BS

RESET

D-A

OUTPUT

*Input data is carried out BS signal "L" besides CLK signal positive edge.

CLK,BS,is keep generally "H" level.

MSB

D12 D11

D10

MITSUBISHI

ELECTRIC

D1

LSB

D0

( / 8 )

3

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

ABSOLUTE MAXIMUM RATINGS

Symbol

VDD

VIND

VIN

Vo

VDAref

Topr

Tstg Storage temperature

Supply voltage

Digital input voltage(DI,CLK,BS)

Input voltage

Output voltage

D-A reference voltage

Operating temperature

Parameter

ELECTRICAL CHARACTERISTICS

Digital part(VDD,VIN=+5V±10%, VDD≥VIN,GND=VDAref=0V,Ta=-20 ~ +85°C,unless otherwise noted)

Symbol

VDD

IILK

IIL

IIH

VOL

VOH

Supply voltage

Input leak current

Input low voltage

Input high voltage

Output low voltage

Output high voltage

Parameter

VIN=0~VDD

IOL=2.5mA

IOH=-400µA

Conditions

Test conditions

-0.3~+7.0

-0.3~+7.0

-0.3~VDD+0.3

-0.3~VDD+0.3

-0.3~VDD+0.3

-40~+125

Min.

4.5

-10 10

0.8VDD

VDD-0.4

Ratings

-20~+85

Limits

Typ.

5.0

Max.

5.5

0.2VDD

0.4

Unit

V

V

V

V

V

°C

°C

Unit

V

µA

V

V

V

V

Analog part(VDD,VIN=+5V±10%, VDD≥VIN,GND=VDAref=0V,Ta=-20 ~ +85°C,unless otherwise noted)

Symbol

VIN

VO

IIN

IDAref

IO

RO

RES

DNL

NL

∆NL

*Polarity of current, (+) is sink into IC and (-) is source from IC.

Input voltage

Output voltage

Input current

D-A reference source current

D-A output sink or source current

Output impedance

Resolution

A

C

C

U

R

A

C

Y

Parameter

VIN=0~VDD

VIN=5V,VDAref=0V,

Proportional to (VIN-VDAref)

VIN1=VIN2=VIN3=5V,

VDAref=0V,

Proportional to (VIN-VDAref)

Constant for all D-A output mode

Differential nonlinearity

Nonlinearity

Nonlinearity for channels

Test conditions

Min.

0

0

-4.5

-1.0

-1

-0.6

-0.4

Limits

Typ.

0.75

-2.25

1.8

1280

Max.

VDD

VDD

1.5

1.0

3.6

1

0.6

0.4

Unit

V

V

mA

mA

µA/LSB

kΩ

STEP

LSB

%FS

%FS

MITSUBISHI

ELECTRIC

( / 8 )

4

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

AC CHARACTERISTICS(VDD,VIN=+5V±10%, VDD≥VIN,GND=VDAref=0V,Ta=-20 ~ +85°C)

Symbol

tCKL

tCKH

tCR Clock rise time

tCF

tDCH

tCHD

tCHL

tLDC

tLDH

tDo

tLDD

Clock "L"pulse width

Clock "H"pulse width

Clock fall time

Data set up time

Data hold time

LD set up time

LD hold time

LD "H" pulse width

Data output delay time

Data output setting time

Input•Output response time

Parameter

CL≤100pF

No Load

f=10kHz

Test conditions

Min Typ

Limits

200

200

60

100

200

100

100

70 350

Max

200

200

20

5

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

TIMING CHART

CLK

DI

BS

D-A

OUTPUT

Do

OUTPUT

tCR tCF

tCKL

tDCH

tCKH

tCHD

tDo

tLDC

tLDH

tCHL

tLDD

MITSUBISHI

ELECTRIC

( / 8 )

5

TYPICAL CHARACTERISTICS

.5

.4

.3

.2

.1

-0.0

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

M62362P DIFFERENTIAL NONLINEARITY

.5

.4

.3

.2

.1

-.1

-.2

-.3

-.4

-.5

STEP NUMBER

M62362P NONLINEARITY

-0.0

-.1

-.2

-.3

-.4

-.5

STEP NUMBER

MITSUBISHI

ELECTRIC

( / 8 )

6

MITSUBISHI<Dig.Ana.INTERFACE>

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

M62362P OUTPUT RISE CHARACTERISTICS(SETTING TIME)

5V

M62362P/FP

OUTPUT

0V

5V

0V

0

M62362P OUTPUT FALL CHARACTERISTICS(SETTING TIME)

5V

0V

2 3

41µs

BS

OUTPUT

5V

0V

BS

0

2 3

MITSUBISHI

ELECTRIC

41µs

( / 8 )

7

1280 RESOLUTION 3CH MULTIPLYING D-A CONVERTER

NOTICE

M62362 have 5 terminals these are input free voltage at use.(VDD,

VIN1,VIN2,VIN3,VDAref)If Ripple and Spike is input to these terminals,accuracy of conversion is down .So,When use this device,

please connect capacitor among to each terminals and GND for

stable operation.

APPLICATION EXAMPLE

MITSUBISHI<Dig.Ana.INTERFACE>

M62362P/FP

VDD

1µF

VIN

0.1µ

0.1µ

0.1µ

CLK

DI

BS

R

VIN1

VIN2

VIN3

GND

VDD

M62362P/FP

VDAref

Do

Vo1

Vo2

Vo3

Vo

VDAref

0.1µ

MITSUBISHI

ELECTRIC

( / 8 )

8

Loading...

Loading...