MITSUBISHI<Dig.Ana.INTERFACE>

input/output.

display.

D0D7123456D8

9

10

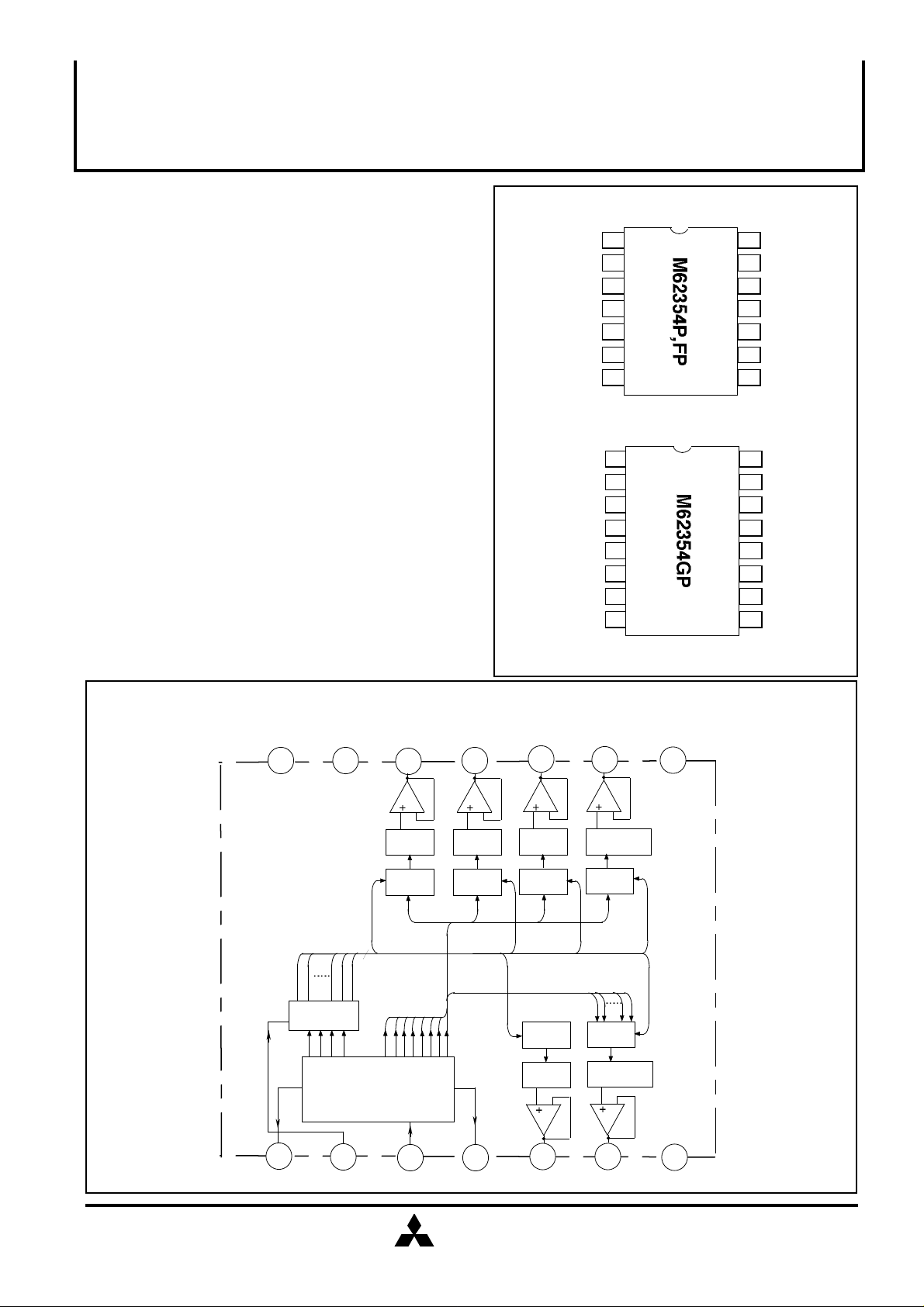

M62354P,FP,GP

8-BIT 6CH D-A CONVERTER WITH BUFFER AMPLIFIERS

DESCRIPTION

The M62354 is an integrated circuit semiconductor of CMOS

structure with 6 channels of built-in D-A converters with output

buffer operational amplifiers.

The 3-wire serial interface method is used for the transfer

format mum wiring.

It is able to cascading serial use with Do terminal.

The output buffer operational amplifier operates in the whole

voltage range from power supply to ground for both

FEATURES

•12bit serial data input(3-wire serial data transfer method)

•Highly stable output buffer operational amplifier allow operation

in the all voltage range from power supply to ground.

APPLICATION

Adjustment/control of industrial or home-use electronic

equipment,such as VTR camera,VTR set,TV,and CRT

PIN CONFIGURATION (TOP VIEW)

DO

LD

CLK

DI

Ao1

Ao2

GND

DO

LD

CLK

Ao1

Ao2

NC

GND

1

2

3

4

Outline 14P4(P)

14P2N-A(FP)

1

2

3

4

DI

5

7

14

Vcc

13

VDD

12

Ao6

11

Ao5

105

Ao4

Ao3

96

87

Vss

16

Vcc

15

VDD

Ao6

14

Ao5

13

Ao4

12

Ao3

116

NC

10

98

Vss

BLOCK DIAGRAM

Vcc

14

1

VDD

13

(6)

ADDRESS

DECODER

D11

12-BIT SHIFT REGISTER

2

LDDo

Ch6

Ao6

12

D-A

L

3

CLK

Outline 16P2E-A(GP)

NC:NO CONNECTION

Ao5

11

-

-

D-A

5

L

Ao4

10

D-A

4

L

L

Ch1

D-A

54

DI

Ao1

Ao3

9

--

8-BIT

R-2R D-A

3

8-BIT

LATCH

8-BIT

LATCH

2

8-BIT

R-2R D-A

-

-

6

Ao2

Vss

8

BUFFER

OP AMP

(6)

BUFFER

OP AMP

7

GND

MITSUBISHI

ELECTRIC

( / 6 )

1

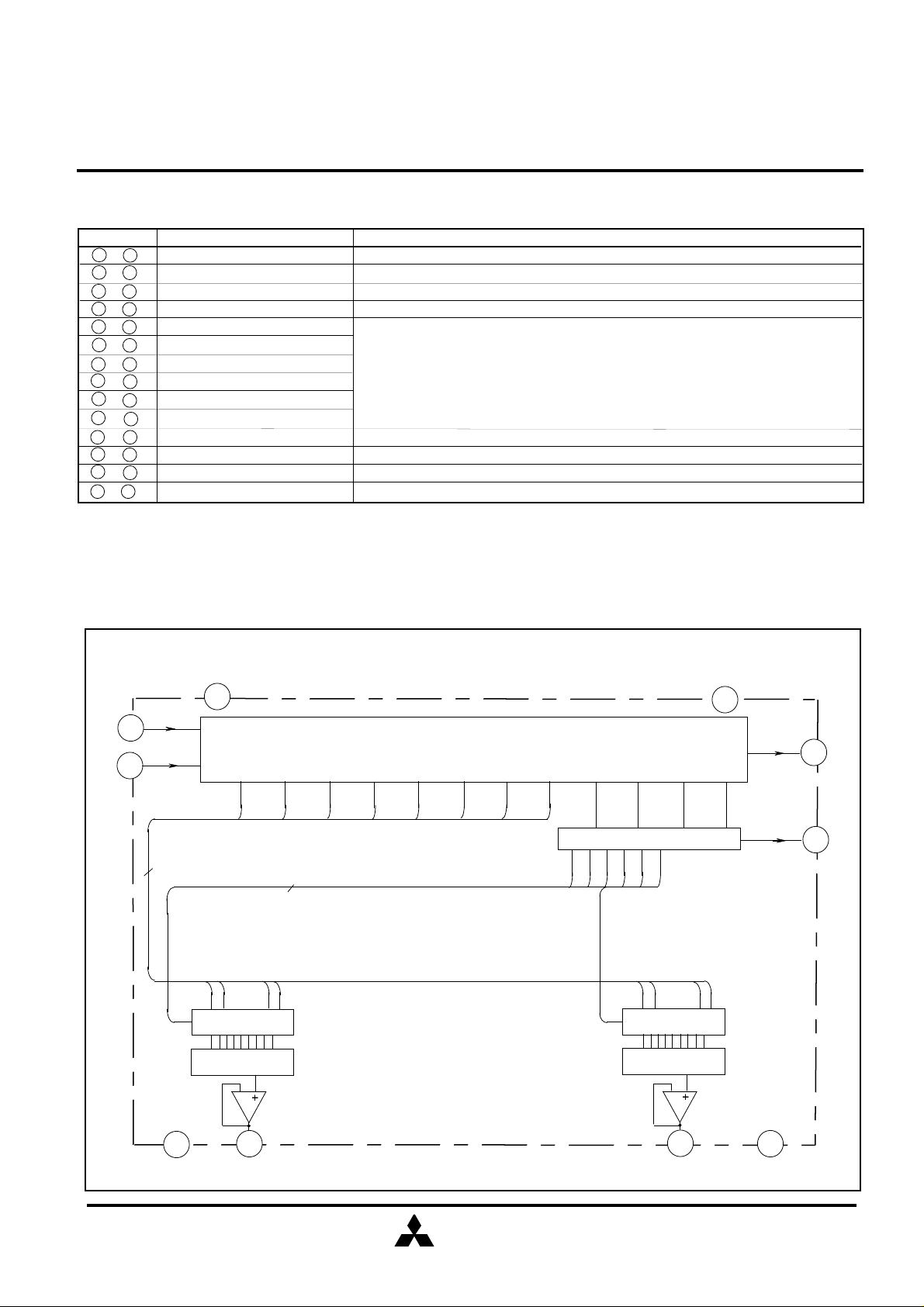

EXPLANATION OF TERMINALS

(VrefL)

Pin No. Symbol

4

4

*

10

11

12

14

13

( )

1

1

( )

3

3

( )

( )

2

2

( )

5

5

6

6

( )

( )

9

11

( )

12

( )

13

( )

14

( )

16

( )

7

8

( )

15

9

( )

8

DI

DO

CLK

LD

Ao1

Ao2

Ao3

Ao4

Ao5

Ao6

Vcc

GND

VDD

Vss

MITSUBISHI<Dig.Ana.INTERFACE>

M62354P,FP,GP

8-BIT 6CH D-A CONVERTER WITH BUFFER AMPLIFIERS

Function

Serial data input terminal

Serial data output terminal

Serial clock input terminal

LD terminal input high level than latch circuit data load

8-bit D-A converter output terminal

Power supply terminal

Digital and analog common GND

D-A converter upper reference voltage input terminal

D-A converter lower reference voltage input terminal

*( ):16P2E

BLOCK DIAGRAM FOR EXPLANATION OF TERMINALS

Vcc

14

DI

4

CLK

3

8

D0

D1

D2

6

12-BIT SHIFT REGISTER

D4

D3

D5

D6 D7

D8

D9

D10 D11

ADDRESS DECODER

3

4

21

5 6

GND

7

D0

1

LD

2

1

13

VDD

(VrefU)

D0

............

8-BIT

LATCH

8-BIT

R-2R D-A

-

5

Ao1

D7

..............................................6

..............................................

...................................................................................................

MITSUBISHI

ELECTRIC

D0

............

8-BIT

LATCH

8-BIT

R-2R D-A

-

12

Ao12

D7

VSS

2

( / 6 )

8

Loading...

Loading...