Mitsubishi M56694GP, M56694FP Datasheet

MITSUBISHI <CONTROL / DRIVER IC>

)

4

7

M56694FP/GP

Bi-CMOS & DMOS 32BIT SERIAL-INPUT LATCHED DRIVER

DESCRIPTION

The M56694 is a semiconductor integrated circuit that has a builtin, 32-bit shift register and a latch of CMOS structure with serial

input and serial/parallel output, and a 32-bit totem-pole-type

parallel output driver of high pressure proof DMOS structure.

Employed are Bi-CMOS and high pressure proof DMOS

processing technology.

FEATURES

● Serial input-serial/parallel output

● Cascade connections possible through serial output

● Latch circuit included for each stage

● Driver section supply voltage: VH=120V

● Operating temperature: -20 – 75°C

APPLICATION

Vacuum Fluorescent Display ANODE DRIVER

FUNCTION

The M56694 comprises a 32-bit D type flip-flop with 32 latches

connected to its output.

In accordance with truth table 1, inputting data to SIN and clock

pulse to CLK allows SIN signal to be put into the internal shift

register when the clock changes from “H” to “L”, and

simultaneously shift register data to be shifted sequentially.

Serial output SOUT is used by connecting to the next stage

M56694 SIN when more than one M56694 is used to expand bits

in the series.

In accordance with truth table 2, parallel output allows the latch to

pass data through if LAT input is turned to “H”, and data to be

retained if LAT input is turned to “L”. Driver output HVOn allows

data from the latch to be output if BLK input is turned to “L”, and “L”

to be output if BLK input is turned to “H”, irrespective of data from

the latch.

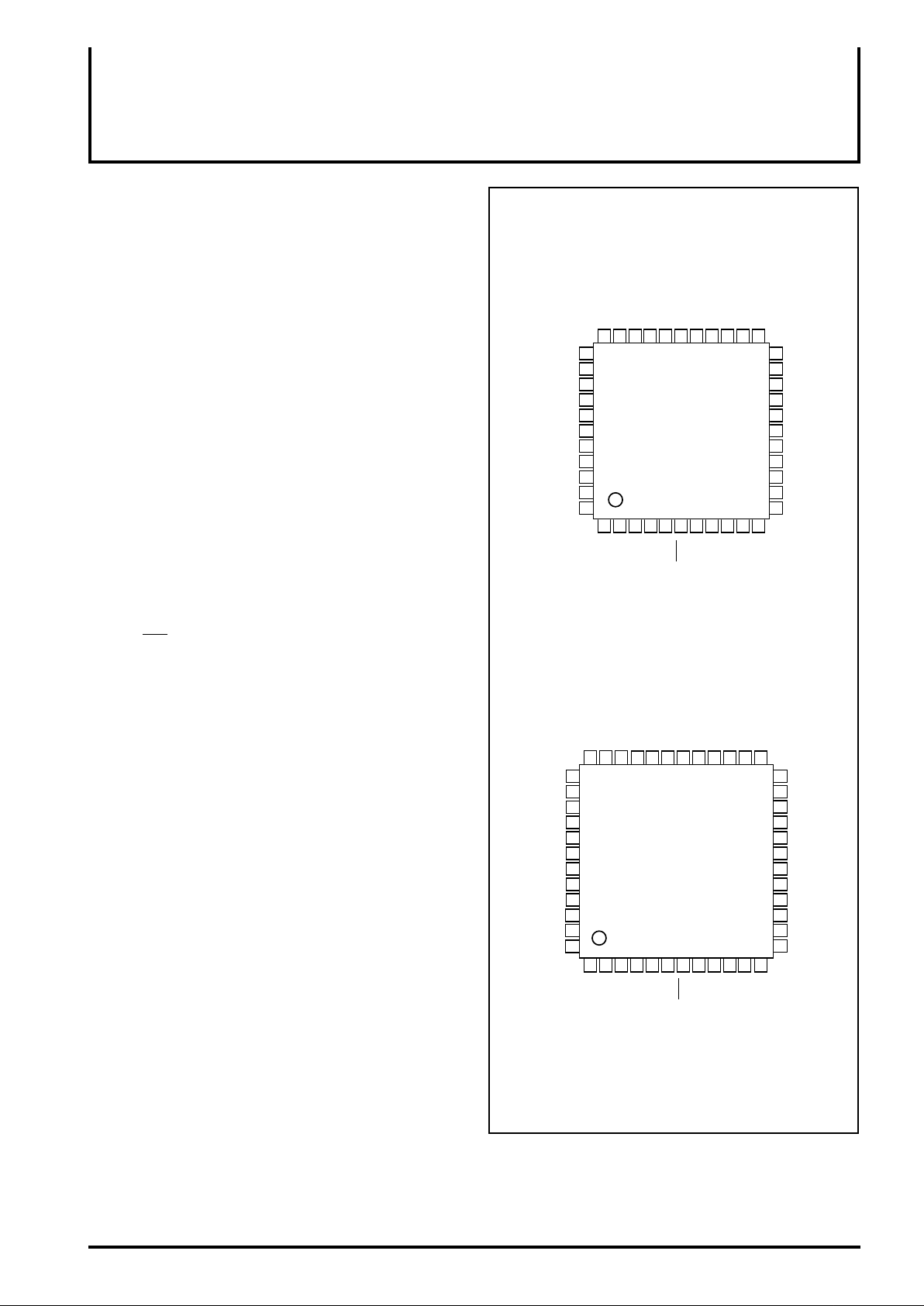

PIN CONFIGURATION(TOP VIEW

HVO12

HVO13

HVO14

HVO15

HVO16

HVO17

HVO18

HVO19

HVO20

3332313029282726252423

34

HVO11

35

HVO10

36

HVO 9

37

HVO 8

38

HVO 7

HVO 6

HVO 5

HVO

HVO 3

HVO 2

HVO 1

N.C

HVO11

HVO10

HVO 9

HVO 8

HVO

N.C

HVO 6

HVO 5

HVO 4

HVO 3

39

40

41

42

43

44

N.C

36

37

38

39

40

41

42

43

44

45

46

47

48HVO 2

123456789

HVO 1

M56694FP

123456789

VH

PGND

SIN

BLK

LAT

CLK

N.C

LGND

Outline 44P6N-A (FP)

HVO12

HVO13

HVO14

HVO15

HVO16

HVO17

HVO18

HVO19

35

34

333231302928272625

M56694GP

H

V

PGND

SIN

BLK

LAT

CLK

VDD

LGND

HVO21

DD

V

HVO20

10

SOUT

HVO22

10

11

H

V

SOUT

HVO21

HVO22

11

VH

22

21

20

19

18

17

16

15

14

13

12

24

23

22

21

20

19

18

17

16

15

14

13

12

PGND

HVO23

HVO24

HVO25

HVO26

HVO27

HVO28

HVO29

HVO30

HVO31

HVO

PGND

N.C

N.C

HVO23

HVO24

HVO25

HVO26

HVO27

HVO28

HVO29

HVO30

HVO31

HVO

32

32

Outline 48P6D-A (GP)

N.C: no connection

Bi-CMOS & DMOS 32BIT SERIAL-INPUT LATCHED DRIVER

↓

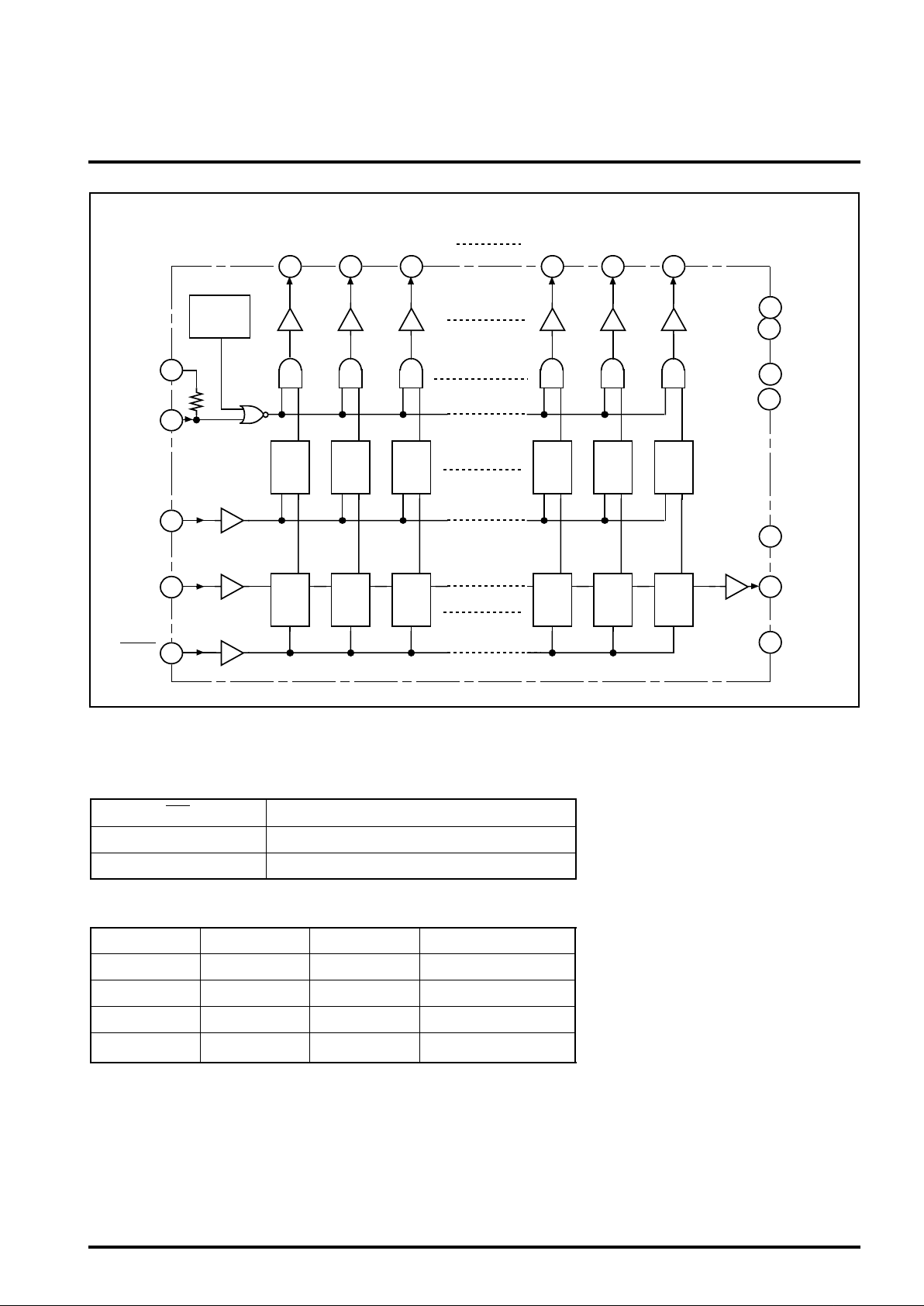

BLOCK DIAGRAM (Note : Pin No. in paretheses are of M56694GP)

(48)

Q

(47)

Q

Q

VDD

BLK

(9)

(5)

(1)

Output

protect

circuit

9

4

(15)

MITSUBISHI <CONTROL / DRIVER IC>

M56694FP/GP

HVO32HVO31HVO30HVO 3HVO 2HVO 1

(14)

14

13

(13)

2

VH

11

(3)(11)

1

PGND

(2)(12)

12

Q

Q

15424344

Q

LAT

SIN

CLK

(6)

(4)

(7)

L

5

3

D

T

6

L

D

Q

D

Q

D

T

TRUTH TABLE

Truth table 1. Shift register section

CLK

H or L

Shift register operation

Truth table 2. Latch and driver sections

L

D

Q

D

T

DATA is shifted.

No changes.

L

D

T

L

D

Q

D

T

L

D

Q

D

LGND

7

(8)

Q

D

T

10

SOUT

(10)

8

N.C

(23)(24)(36)

(37)(43)

HVOnDn LAT BLK

X

H

L

X

X

H

H

L

H

L

L

L

Output all “L”

H

L

Latch’s data output.

Dn=nth bit DFF retention data

HVOn=nth bit driver output

L=“L” level

H=“H” level

X=“L” level or “H” level

Loading...

Loading...